Professional Documents

Culture Documents

L420 OpAmpCompI

Uploaded by

Shreerama Samartha G BhattaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

L420 OpAmpCompI

Uploaded by

Shreerama Samartha G BhattaCopyright:

Available Formats

Lecture 420 Compensation of Op Amps-I (12/10/01)

Single-Loop, Negative Feedback Systems

F(s)

Block diagram:

A(s) = differential-mode voltage gain of the

op amp

Vin(s)

A(s)

+

F(s) = feedback transfer function from the

output of op amp back to the input.

Definitions:

Open-loop gain = L(s) = -A(s)F(s)

Vout(s)

A(s)

Closed-loop gain = Vin(s) = 1+A(s)F(s)

Stability Requirements:

The requirements for stability for a single-loop, negative feedback system is,

| A(j0)F(j0)| = | L(j0)| < 1

where 0 is defined as

Arg[A(j0)F(j0)] = Arg[L(j0)] = 0

Another convenient way to express this requirement is

Arg[A(j0dB)F(j0dB)] = Arg[L(j0dB)] > 0

where 0dB is defined as

| A(j0dB)F(j0dB)| = | L(j0dB)| = 1

ECE 4430 - Analog Integrated Circuits and Systems

Page 420-3

Vout(s)

Fig. 420-01

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-4

|A(j)F(j)|

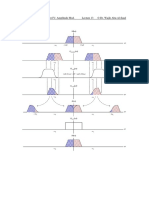

Illustration of the Stability Requirement using Bode Plots

-20dB/decade

-40dB/decade

Arg[-A(j)F(j)]

0dB

180

135

90

45

0

M

0dB

Frequency (rads/sec.)

Fig. Fig. 420-02

A measure of stability is given by the phase when |A(j)F(j)| = 1. This phase is called

phase margin.

Phase margin = M = Arg[-A(j0dB)F(j0dB)] = Arg[L(j0dB)]

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-5

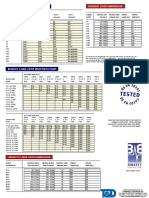

Why Do We Want Good Stability?

Consider the step response of second-order system which closely models the closed-loop

gain of the op amp.

1.4

45

50

55

1.2

1.0

60

65

70

vout(t) 0.8

Av0

0.6

0.4

0.2

0

0

5

10

ot = nt (sec.)

15 Fig. 420-03

A good step response is one that quickly reaches its final value.

Therefore, we see that phase margin should be at least 45 and preferably 60 or larger.

(A rule of thumb for satisfactory stability is that there should be less than three rings.)

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-6

Uncompensated Frequency Response of Two-Stage Op Amps

Two-Stage Op Amps:

VDD

M3 M4

VCC

Q3

M6

Q4

Q6

vout

vin

+

M1 M2

+

VBias

-

vin

+

+

VBias

-

M7

M5

Q1

vout

Q2

Q7

Q5

VSS

VEE

Fig. 420-04

Small-Signal Model:

D1, D3 (C1, C3)

+

g v

gm1vin

v1 m2 in

R1

C1

2

2

D2, D4 (C2, C4)

gm4v1

R2

C2

D6, D7 (C6, C7)

+

v2

- gm6v2

+

R3

C3

vout

Fig. 420-05

Note that this model neglects the base-collector and gate-drain capacitances for purposes

of simplification.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-7

Uncompensated Frequency Response of Two-Stage Op Amps - Continued

For the MOS two-stage op amp:

1

1

R1 gm3 ||rds3||rds1 gm3

R2 = rds2|| rds4

and R3 = rds6|| rds7

C1 = Cgs3+Cgs4+Cbd1+Cbd3

C2 = Cgs6+Cbd2+Cbd4

and C3 = CL +Cbd6+Cbd7

For the BJT two-stage op amp:

1

1

R1 = gm3 ||r3||r4||ro3 gm3

R2 = r6|| ro2|| ro4 r6 and R3 = ro6|| ro7

C1 = C3+C4+Ccs1+Ccs3

C2 = C6+Ccs2+Ccs4

and C3 = CL+Ccs6+Ccs7

Assuming the pole due to C1 is much greater than the poles due to C2 and C3 gives,

gm1vin

R2

C2

+

v2

- gm6v2

+

R3

C3

vout

-

gm1Vin

RI

CI

+

VI

- gmIIVI

RII

CII

+

Vout

Fig. 420-06

The locations for the two poles are given by the following equations

1

1

p1 = RICI and p2 = RIICII

where RI (RII) is the resistance to ground seen from the output of the first (second) stage

and CI (CII) is the capacitance to ground seen from the output of the first (second) stage.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-8

Uncompensated Frequency Response of an Op Amp

Avd(0) dB

|A(j)|

-20dB/decade

GB

log10()

0dB

Phase Shift

-40dB/decade

-45/decade

Arg[-A(j)]

180

135

-45/decade

90

45

0

|p1'|

|p2'| 0dB

log10()

Fig. 420-07

If we assume that F(s) = 1 (this is the worst case for stability considerations), then the

above plot is the same as the loop gain.

Note that the phase margin is much less than 45.

Therefore, the op amp must be compensated before using it in a closed-loop

configuration.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-9

MILLER COMPENSATION

Two-Stage Op Amp

VDD

M3

VCC

M4

Cc

vin

+

M1

+

VBias

-

Q3

M6

CM

Q6

Cc

vout

M2

CII

CI

M7

M5

Q4

CM

VSS

vin

+

Q1

+

VBias

-

vout

Q2

CII

CI

Q7

Q5

VEE

Fig. 420-08

The various capacitors are:

Cc = accomplishes the Miller compensation

CM = capacitance associated with the first-stage mirror (mirror pole)

CI = output capacitance to ground of the first-stage

CII = output capacitance to ground of the second-stage

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-10

Compensated Two-Stage, Small-Signal Frequency Response Model Simplified

Use the CMOS op amp to illustrate:

1.) Assume that gm3 >> gds3 + gds1

gm3

2.) Assume that CM >> GB

Therefore,

v1

-gm1vin

2

1

rds1||rds3 CM gm3

v2

gm2vin

2

gm4v1 C1 rds2||rds4 gm6v2

v2

+

vin gm1vin

-

CI

Cc

rds2||rds4

+

vout

-

rds6||rds7 CL

Cc

gm6v2

rds6||rds7

CII

+

vout

Fig. 420-09

Same circuit holds for the BJT op amp with different component relationships.

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-11

General Two-Stage Frequency Response Analysis

Cc

where

V2

+

+

gmI = gm1 = gm2, RI = rds2||rds4, CI = C1

Vin gmIVin

Vout

RI gmIIV2

RII CII

and

C

I

gmII = gm6, RII = rds6||rds7, CII = C2 = CL

Fig.420-10

Nodal Equations:

-gmIVin = [GI + s(CI + Cc)]V2 - [sCc]Vout and 0 = [gmII - sCc]V2 + [GII + sCII + sCc]Vout

Solving using Cramers rule gives,

Vout(s)

gmI(gmII- sCc)

Vin(s) = GIGII+s [GII(CI+CII)+GI(CII+Cc)+gmIICc]+s2[CICII+CcCI+CcCII]

Ao[1- s (Cc/gmII)]

= 1+s [R (C +C )+R (C +C )+g R R C ]+s2[R R (C C +C C +C C )]

I

I

II

II

2

c

mII 1 II c

I II

I II

c I

c II

where, Ao = gmIgmIIRIRII

1 1

s s

s2

s

s2

In general, D(s) = 1-p1 1-p2 = 1-s p1+p2+p1p2 D(s) 1-p1 + p1p2 , if |p2|>>|p1|

gmII

-1

-1

p1 = RI(CI+CII)+RII(CII+Cc)+gmIIR1RIICc gmIIR1RIICc , z = Cc

-[RI(CI+CII)+RII(CII+Cc)+gmIIR1RIICc]

-gmIICc

-gmII

p2 =

CICII+CcCI+CcCII CII , CII > Cc > CI

RIRII(CICII+CcCI+CcCII)

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-12

Summary of Results for Miller Compensation of the Two-Stage Op Amp

There are three roots of importance:

1.) Right-half plane zero:

gmII gm6

z1= Cc = Cc

This root is very undesirable- it boosts the magnitude while decreasing the phase.

2.) Dominant left-half plane pole (the Miller pole):

-(gds2+gds4)(gds6+gds7)

-1

p1 gmIIRIRIICc =

gm6Cc

This root accomplishes the desired compensation.

3.) Left-half plane output pole:

-gmII -gm6

p2 CII CL

This pole must be unity-gainbandwidth or the phase margin will not be satisfied.

Root locus plot of the Miller compensation:

Closed-loop poles, Cc0 j

Open-loop poles

Cc=0

p2

ECE 4430 - Analog Integrated Circuits and Systems

p2'

p1'

p1

z1

Fig. 420-11

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-13

|A(j)F(j)|

Compensated Open-Loop Frequency Response of the Two-Stage Op Amp

Avd(0) dB

Uncompensated

-20dB/decade

Compensated

GB

log10()

0dB

Phase Shift

-40dB/decade

Arg[-A(j)F(j)|

Uncompensated

180

-45/decade

135

-45/decade

90

45

Compensated

|p1|

No phase margin

|p2'| |p2|

|p1'|

Phase

Margin

log10()

Fig. 420-12

Note that the unity-gainbandwidth, GB, is

gmI gm1 gm2

1

GB = Avd(0)|p1| = (gmIgmIIRIRII)gmIIRIRIICc = Cc = Cc = Cc

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-14

Conceptually, where do these roots come from?

1.) The Miller pole:

VDD

RII

Cc

1

|p1| RI(gm6RIICc)

vout

RI

M6

vI

gm6RIICc

Fig. 420-13

2.) The left-half plane output pole:

VDD

Cc

gm6

|p2| CII

VDD

RII

RII

vout

M6

CII

vout

1

GBCc 0

M6

CII

Fig. 420-14

3.) Right-half plane zero (Zeros always arise from multiple

paths from the input to output):

g

m6

-R

1

II

-gm6RII(1/sCc)

RII

sCc

vout = RII + 1/sCc v + RII + 1/sCc v = RII + 1/sCc v

where v = v = v.

ECE 4430 - Analog Integrated Circuits and Systems

VDD

Cc

RII

vout

v''

M6

v'

Fig. 420-15

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-15

Influence of the Mirror Pole

Up to this point, we have neglected the influence of the pole, p3, associated with the

current mirror of the input stage. If |p2| |p3|, we have problems in compensation. This

pole is given approximately as

-gm3

p3 CM

F=1

Closed-loop poles

Cc = 0

Avd(0) dB

-p3

-6dB/octave

-p2

Cc 0

-p

Open-loop poles 1

z1

GB

log10()

0dB

Roll-off due to p3

Phase Shift

0

45

90

Cc 0

135

180

|p1|

-12dB/octave

Cc = 0

-45/decade

Cc 0

-45/decade

Cc = 0

Phase margin

due to p3

ECE 4430 - Analog Integrated Circuits and Systems

|p3| |p2|

Phase

Margin

log10()

Excess Phase

due to p3

Fig. Fig. 420-16

P.E. Allen - 2001

Lecture 420 Compensation of Op Amps-I (12/10/01)

Page 420-16

SUMMARY

Compensation

Designed so that the op amp with unity gain feedback (buffer) is stable

Types

- Miller

- Miller with nulling resistors

- Self Compensating

- Feedforward

ECE 4430 - Analog Integrated Circuits and Systems

P.E. Allen - 2001

You might also like

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- Lec2 Starting With Redhawk 0Document78 pagesLec2 Starting With Redhawk 0sathyanarainraoNo ratings yet

- KP01 Installation ManualDocument19 pagesKP01 Installation ManualDiradivo Vakaikop100% (1)

- L100 MultistageFreq II (2UP)Document6 pagesL100 MultistageFreq II (2UP)Van Nguyen Huu VanNo ratings yet

- Elec 380 Course NotesDocument210 pagesElec 380 Course NotesgranitebricksNo ratings yet

- Op Amp DesignDocument8 pagesOp Amp DesignSermalingam ChandrasekarNo ratings yet

- Feedback TopologyDocument6 pagesFeedback Topologyilg1No ratings yet

- Solutions2CMOS CircuitDesign AllenDocument509 pagesSolutions2CMOS CircuitDesign AllenAnil KumarNo ratings yet

- Smith ChartDocument14 pagesSmith ChartEmiaj LabampaNo ratings yet

- Lecture 070 - Single-Stage Frequency Response - I: (READING: GHLM - 488-504) ObjectiveDocument6 pagesLecture 070 - Single-Stage Frequency Response - I: (READING: GHLM - 488-504) ObjectiveVan Nguyen Huu VanNo ratings yet

- Chap06 (6 24 06)Document74 pagesChap06 (6 24 06)pumba1234No ratings yet

- GATE EE 2007 With SolutionsDocument62 pagesGATE EE 2007 With SolutionsAbhishek MohanNo ratings yet

- Analog CircuitsDocument52 pagesAnalog CircuitsrohanvermaaaaaNo ratings yet

- Homework SolutionsDocument46 pagesHomework SolutionsKashif AmjadNo ratings yet

- OpAmp ExampleDocument16 pagesOpAmp ExampleYi Ming Tan100% (1)

- Microelectronic Circuits: Amplifier BasicsDocument57 pagesMicroelectronic Circuits: Amplifier BasicsAkshay AnandNo ratings yet

- ProblemasDocument18 pagesProblemasAnxo Do ForteNo ratings yet

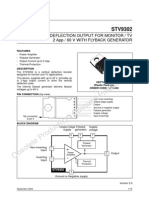

- STV 9302Document15 pagesSTV 9302krish8717No ratings yet

- B Network 09-09-16 1494Document10 pagesB Network 09-09-16 1494arunNo ratings yet

- EE-EC - RIB (W) - Control Sys - 13-08-16 - SK1-sol - 1391Document9 pagesEE-EC - RIB (W) - Control Sys - 13-08-16 - SK1-sol - 1391arunNo ratings yet

- Chapter 1Document39 pagesChapter 1ÎQbãl HãikãmNo ratings yet

- Chapter 4. Analog Building Blocks An Intuitive Approach (Analog IC Design An Intuitive Approach)Document33 pagesChapter 4. Analog Building Blocks An Intuitive Approach (Analog IC Design An Intuitive Approach)Minh Hai RungNo ratings yet

- EE: Electrical Engineering: Test Series - 1Document8 pagesEE: Electrical Engineering: Test Series - 1bhurajeshNo ratings yet

- Lecture 050 - Followers: (READING: GHLM - 344-362, AH - 221-226) ObjectiveDocument7 pagesLecture 050 - Followers: (READING: GHLM - 344-362, AH - 221-226) ObjectiveArchana RkNo ratings yet

- Chapter 3. Single-Transistor Primitives An Intuitive Approach (Analog IC Design An Intuitive Approach)Document26 pagesChapter 3. Single-Transistor Primitives An Intuitive Approach (Analog IC Design An Intuitive Approach)Minh Hai RungNo ratings yet

- Multistage AmplifierDocument22 pagesMultistage AmplifierVijay AnandhNo ratings yet

- Cmos Op Amp PDFDocument13 pagesCmos Op Amp PDFLokesh NikhadeNo ratings yet

- Common Drain Amplifier or Source Follower: 1. Low Frequency Small Signal Equivalent CircuitDocument16 pagesCommon Drain Amplifier or Source Follower: 1. Low Frequency Small Signal Equivalent CircuitPadaliya ShreyaNo ratings yet

- Samsung Plasma Training ManualDocument57 pagesSamsung Plasma Training Manualedsel72100% (2)

- Design of Phase-Lead CompensatorDocument13 pagesDesign of Phase-Lead CompensatorAsif MudgalNo ratings yet

- Lecture17 Fully Diff Amps CMFBDocument28 pagesLecture17 Fully Diff Amps CMFBmohamedNo ratings yet

- Charge PumpsDocument18 pagesCharge PumpsBLUEE009No ratings yet

- Lecture13Document5 pagesLecture13ohenri100No ratings yet

- Power Amplifier Example QuestionsDocument8 pagesPower Amplifier Example QuestionsShah IzzatNo ratings yet

- Irg4Pc50Kd: FeaturesDocument11 pagesIrg4Pc50Kd: FeaturesLUDWINGNo ratings yet

- Allen and Holberg Homework SolutionDocument121 pagesAllen and Holberg Homework SolutionNihit Varshney100% (1)

- Bipolar Junction Transistors (BJT) : NPN PNPDocument44 pagesBipolar Junction Transistors (BJT) : NPN PNPAli AhmadNo ratings yet

- Assimen Tronic 2Document23 pagesAssimen Tronic 2Shafiq HafizullahNo ratings yet

- 5 Two Port NetworksDocument14 pages5 Two Port NetworksNitinNo ratings yet

- Answers in AC MachinesDocument3 pagesAnswers in AC MachinesRonald James DiazNo ratings yet

- 3 Current SRCDocument10 pages3 Current SRCmelwyn_thomasNo ratings yet

- Electronic 2 Solved ProblemDocument8 pagesElectronic 2 Solved ProblemAbdullah S OthmanNo ratings yet

- Problem Solutions: R R R R V I R R IDocument69 pagesProblem Solutions: R R R R V I R R IAkhila RajagopalNo ratings yet

- Folded Cascode OpampDocument6 pagesFolded Cascode OpampsinamahaniNo ratings yet

- ECE102 - F12 ProSet 7 PDFDocument37 pagesECE102 - F12 ProSet 7 PDFlokeshwarrvrjcNo ratings yet

- EEEN221 Assignment 01 With Answers 01Document15 pagesEEEN221 Assignment 01 With Answers 01Lame MorupisiNo ratings yet

- EEE 241 EEE 241 Analog Electronics 1 Tutorial Tutorial DR Norlaili Mohd NohDocument42 pagesEEE 241 EEE 241 Analog Electronics 1 Tutorial Tutorial DR Norlaili Mohd NohMd Anwar HossainNo ratings yet

- ELE315 Midterm 2012 SolutionsDocument7 pagesELE315 Midterm 2012 SolutionsOsman ZenginNo ratings yet

- Introduction To Switched-Mode Converter Modeling Using MATLAB/SimulinkDocument37 pagesIntroduction To Switched-Mode Converter Modeling Using MATLAB/SimulinkAhana MalhotraNo ratings yet

- G4BC30KD-International Rectifier PDFDocument10 pagesG4BC30KD-International Rectifier PDFPablo AllosiaNo ratings yet

- Pspice Tutorial AcDocument89 pagesPspice Tutorial AcZadziorNo ratings yet

- 365 Signal ConditioningDocument29 pages365 Signal ConditioningSunilkumar ReddyNo ratings yet

- Working With Phasors and Using Complex Polar Notation in MATLAB/OctaveDocument5 pagesWorking With Phasors and Using Complex Polar Notation in MATLAB/Octaveel_ruso__83No ratings yet

- IGBT Plasma Panasonic Placa Ysus IRG4BC40UDocument8 pagesIGBT Plasma Panasonic Placa Ysus IRG4BC40UAntonio ChavezNo ratings yet

- MVLSI QB SolutionsDocument51 pagesMVLSI QB SolutionsKeependarNo ratings yet

- Lecture 250 - Introduction To Feedback Concepts: (READING: GHLM - 553-563) ObjectiveDocument8 pagesLecture 250 - Introduction To Feedback Concepts: (READING: GHLM - 553-563) ObjectiveVan Nguyen Huu VanNo ratings yet

- Irg 4 PF 50 WDocument8 pagesIrg 4 PF 50 WQuickerManNo ratings yet

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesFrom EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Fundamentals of Electronics 2: Continuous-time Signals and SystemsFrom EverandFundamentals of Electronics 2: Continuous-time Signals and SystemsNo ratings yet

- AC Question Bank-SkDocument5 pagesAC Question Bank-SkShreerama Samartha G BhattaNo ratings yet

- EE 370, Lecture 13Document4 pagesEE 370, Lecture 13Shreerama Samartha G BhattaNo ratings yet

- EENG223 Lec05 OpAmpsDocument30 pagesEENG223 Lec05 OpAmpsShreerama Samartha G BhattaNo ratings yet

- Electromagnetic NotesDocument121 pagesElectromagnetic NotesShreerama Samartha G BhattaNo ratings yet

- ElectromagneticDocument125 pagesElectromagneticShatrughna SamalNo ratings yet

- 209 Ec 1111Document49 pages209 Ec 1111Shreerama Samartha G BhattaNo ratings yet

- 2 Literature ReviewDocument17 pages2 Literature ReviewShreerama Samartha G BhattaNo ratings yet

- LM1496Document7 pagesLM1496Shreerama Samartha G BhattaNo ratings yet

- F0Document20 pagesF0Shreerama Samartha G BhattaNo ratings yet

- An Daniel KuzmenkoHow To Connect A Bluetooth With An Arduino and Transfer Values in To MATLAB.Document13 pagesAn Daniel KuzmenkoHow To Connect A Bluetooth With An Arduino and Transfer Values in To MATLAB.Putrazakki AzharNo ratings yet

- Pulse Modulation Part 1Document14 pagesPulse Modulation Part 1Shreerama Samartha G BhattaNo ratings yet

- Sample 2Document2 pagesSample 2Shreerama Samartha G BhattaNo ratings yet

- V5i2 0434Document4 pagesV5i2 0434Shreerama Samartha G BhattaNo ratings yet

- Transis DualDocument11 pagesTransis DualShreerama Samartha G BhattaNo ratings yet

- Communication Lab IDocument25 pagesCommunication Lab IShreerama Samartha G BhattaNo ratings yet

- MSP Gang ProgrammerDocument123 pagesMSP Gang ProgrammerShreerama Samartha G BhattaNo ratings yet

- D1 10Document7 pagesD1 10Shreerama Samartha G BhattaNo ratings yet

- Communication Lab 2labDocument67 pagesCommunication Lab 2labShreerama Samartha G BhattaNo ratings yet

- Integrated Circuits La ManulDocument88 pagesIntegrated Circuits La ManulShreerama Samartha G BhattaNo ratings yet

- Sampling Frequency Selector Section: : ProcedureDocument3 pagesSampling Frequency Selector Section: : ProcedureShreerama Samartha G BhattaNo ratings yet

- ElieDocument8 pagesElieShreerama Samartha G BhattaNo ratings yet

- G' Area of Sphere Area of Antenna PatternDocument7 pagesG' Area of Sphere Area of Antenna PatternShreerama Samartha G BhattaNo ratings yet

- D FF Quiz Buzzer ProjectDocument2 pagesD FF Quiz Buzzer ProjectShreerama Samartha G BhattaNo ratings yet

- Fastest Finger Press Quiz Buzzer: Block DiagramDocument1 pageFastest Finger Press Quiz Buzzer: Block DiagramShreerama Samartha G BhattaNo ratings yet

- Graversen FinalDocument20 pagesGraversen FinalShreerama Samartha G BhattaNo ratings yet

- Unit4s SIDocument8 pagesUnit4s SIShreerama Samartha G BhattaNo ratings yet

- En - DM00025071 2Document44 pagesEn - DM00025071 2Shreerama Samartha G BhattaNo ratings yet

- Sung 97 InterfaceDocument6 pagesSung 97 InterfaceShreerama Samartha G BhattaNo ratings yet

- (Fixmag - Ru) Dv514s Service ManualDocument42 pages(Fixmag - Ru) Dv514s Service ManualevgeniyvictorovNo ratings yet

- Calculation of Positive Sequence ImpedanceDocument14 pagesCalculation of Positive Sequence ImpedancesathiyaseelanNo ratings yet

- 7SR17 Rho Catalogue Sheet PDFDocument20 pages7SR17 Rho Catalogue Sheet PDFMichael Roche0% (1)

- Icest 2011 977 930Document8 pagesIcest 2011 977 93001666754614No ratings yet

- Design of An Ultracapacitor Based Dynamic Voltage Restorer For Power Quality Enhancement in The Distribution GridDocument7 pagesDesign of An Ultracapacitor Based Dynamic Voltage Restorer For Power Quality Enhancement in The Distribution GridGRD JournalsNo ratings yet

- Lecture 20 PDFDocument12 pagesLecture 20 PDFRana Zeeshan UmerNo ratings yet

- EieDocument189 pagesEieImran MohiuddinNo ratings yet

- BS-II Module 1 - Students PDFDocument53 pagesBS-II Module 1 - Students PDFmuktha mukuNo ratings yet

- Very Low Dropout 3.0 Amp Regulator With Enable: Power Management Features DescriptionDocument10 pagesVery Low Dropout 3.0 Amp Regulator With Enable: Power Management Features DescriptionmitusharmaNo ratings yet

- EE 442 Homework #1: Problem 1 Wavelengths in Radio Applications (15 Points)Document6 pagesEE 442 Homework #1: Problem 1 Wavelengths in Radio Applications (15 Points)AsadRasheedNo ratings yet

- A Generic DMM Test and CalibrationDocument11 pagesA Generic DMM Test and CalibrationrobertNo ratings yet

- Lab-2 (Tutorial) Simulation of Lna (Cadence Spectrerf) : Prepared by Rashad.M.Ramzan Rashad@Isy - Liu.SeDocument18 pagesLab-2 (Tutorial) Simulation of Lna (Cadence Spectrerf) : Prepared by Rashad.M.Ramzan Rashad@Isy - Liu.Seblue-smart1355100% (1)

- Detection and Classification of Defects in Ceramic Insulators Using RF Antenna PDFDocument8 pagesDetection and Classification of Defects in Ceramic Insulators Using RF Antenna PDFRodick GansfordNo ratings yet

- Magnetron AmplifierDocument5 pagesMagnetron AmplifierroccosanNo ratings yet

- Terminal and CordDocument4 pagesTerminal and Cordbee398No ratings yet

- EXPERIMENT NO 3 (Comparator)Document2 pagesEXPERIMENT NO 3 (Comparator)Jaideep Singh100% (2)

- Practical Electronics 2023-01Document76 pagesPractical Electronics 2023-01László JásznagyNo ratings yet

- Industrial High VoltageDocument184 pagesIndustrial High VoltageStaines84100% (6)

- Datasheet lf356 PDFDocument23 pagesDatasheet lf356 PDFAlberto Chica CardenasNo ratings yet

- 4-Channel FM Radio System: Instruction ManualDocument20 pages4-Channel FM Radio System: Instruction ManualElton Marcel PadiaNo ratings yet

- Albert Abrams For WebDocument7 pagesAlbert Abrams For Webapi-232178087100% (1)

- Network AnalysisDocument2 pagesNetwork AnalysisPandit SumitNo ratings yet

- Birkett Cable Joints PDFDocument2 pagesBirkett Cable Joints PDFtobyNo ratings yet

- Ixys P-Channel Power Mosfets and Applications Abdus Sattar, Kyoung-Wook Seok, Ixan0064Document14 pagesIxys P-Channel Power Mosfets and Applications Abdus Sattar, Kyoung-Wook Seok, Ixan0064Kikuvi JohnNo ratings yet

- Alstom's ECO 100 PlatformDocument23 pagesAlstom's ECO 100 Platformopzz_opzz100% (1)

- Design of A Photovoltaic-Wind Hybrid PowerDocument76 pagesDesign of A Photovoltaic-Wind Hybrid PowerAwgichwAsefaNo ratings yet

- The Technician's Emi HandbookDocument248 pagesThe Technician's Emi HandbookEdgarNo ratings yet

- Cs 6 P 235 PXDocument2 pagesCs 6 P 235 PXonurkaya1No ratings yet