Professional Documents

Culture Documents

3d IC's

Uploaded by

Karan RajCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

3d IC's

Uploaded by

Karan RajCopyright:

Available Formats

Introduction

There is a saying in real estate; when land get expensive, multi-storied buildings are the

alternative solution. We have a similar situation in the chip industry. For the past thirty years,

chip designers have considered whether building integrated circuits multiple layers might create

cheaper, more powerful chips.

Performance of deep-sub micrometer very large scale integrated (VLSI) circuits is being

increasingly dominated by the interconnects due to increasing wire pitch and increasing die size.

Additionally, heterogeneous integration of different technologies on one single chip is becoming

increasingly desirable, for which planar (2-D) ICs may not be suitable.

The three dimensional (3-D) chip design strategy exploits the vertical dimension to alleviate the

interconnect related problems and to facilitate heterogeneous integration of technologies to

realize system on a chip (SoC) design. By simply dividing a planar chip into separate blocks,

each occupying a separate physical level interconnected by short and vertical interlayer

interconnects (VILICs), significant improvement in performance and reduction in wire-limited

chip area can be achieved.In the 3-Ddesign architecture, an entire chip is divided into a number

of blocks, and each block is placed on a separate layer of Si that are stacked on top of each other.

Motivation For 3-D ICs

The unprecedented growth of the computer and the information technology industry is

demanding Very Large Scale Integrated ( VLSI ) circuits with increasing functionality and

performance at minimum cost and power dissipation. Continuous scaling of VLSI circuits is

reducing gate delays but rapidly increasing interconnect delays. A significant fraction of the total

power consumption can be due to the wiring network used for clock distribution, which is

usually realized using long global wires.

Furthermore, increasing drive for the integration of disparate signals (digital, analog, RF) and

technologies (SOI, SiGe, GaAs, and so on) is introducing various SoC design concepts, for

which existing planner (2-D) IC design may not be suitable.

3D Architecture

Three-dimensional integration to create multilayer Si ICs is a concept that can significantly

improve interconnect performance ,increase transistor packing density, and reduce chip area and

power dissipation. Additionally 3D ICs can be very effective large scale on chip integration of

different systems.

In 3D design architecture, and entire(2D) chips is divided into a number of blocks is placed on

separate layer of Si that are stacked on top of each other. Each Si layer in the 3D structure can

have multiple layer of interconnects(VILICs) and common global interconnects.

You might also like

- 3D ICs: A Promising Solution to Interconnect ChallengesDocument2 pages3D ICs: A Promising Solution to Interconnect ChallengesRachit ChilanaNo ratings yet

- 3D ICsDocument34 pages3D ICsapi-3827000100% (1)

- 3 D IcsDocument15 pages3 D IcsputtasatishNo ratings yet

- 3d ics-Seminar-Report - 08Document29 pages3d ics-Seminar-Report - 08Santhanu Surendran100% (1)

- 3D IC TechnologyDocument18 pages3D IC TechnologymanjushasurampalliNo ratings yet

- 3 - D ICsDocument35 pages3 - D ICsSamhith ReddyNo ratings yet

- 3D ICs Reduce Interconnect DelaysDocument24 pages3D ICs Reduce Interconnect DelaysKonara KiranNo ratings yet

- 3 - D ICsDocument35 pages3 - D ICsSano SanojNo ratings yet

- CnuDocument27 pagesCnuMahesh BejgumNo ratings yet

- 3D ICs Reduce Interconnect Delays Less Than 40 CharactersDocument35 pages3D ICs Reduce Interconnect Delays Less Than 40 CharactersJnaresh NareshNo ratings yet

- 3 - D ICsDocument35 pages3 - D ICsBibinMathewNo ratings yet

- 3D ICs Reduce Interconnect DelaysDocument31 pages3D ICs Reduce Interconnect DelaysShweta R Burli0% (1)

- 3-D ICsDocument35 pages3-D ICsNikitha GNo ratings yet

- 3D ICs Reduce Interconnect DelaysDocument35 pages3D ICs Reduce Interconnect DelaysKhusi ArnavNo ratings yet

- 3 - D ICsDocument31 pages3 - D ICsSudheesh VsNo ratings yet

- D Ics Seminar Report 10Document25 pagesD Ics Seminar Report 10Deepti BalaNo ratings yet

- 3d ChipsDocument5 pages3d ChipsVirag PatilNo ratings yet

- Seminar Report 08Document29 pagesSeminar Report 08Mounikac40% (5)

- 3-D Ics Seminar Report 2011-2012Document29 pages3-D Ics Seminar Report 2011-2012Jamsheer KpNo ratings yet

- Lords Institute of Engineering & Technology For Women, Chikani (Alwar)Document36 pagesLords Institute of Engineering & Technology For Women, Chikani (Alwar)Sandeep SharmaNo ratings yet

- Seminar ReportDocument21 pagesSeminar ReportRavikumar ParagondNo ratings yet

- PCX - ManishDocument16 pagesPCX - ManishmanishNo ratings yet

- Dept - of E&C Engg, Mce, Hassan 1Document16 pagesDept - of E&C Engg, Mce, Hassan 1Sharath RajNo ratings yet

- NileshDocument22 pagesNileshNilesh VermaNo ratings yet

- Seminar Synopsis-1 (R, P) 3dicDocument1 pageSeminar Synopsis-1 (R, P) 3dicRavikumar ParagondNo ratings yet

- 3D IC Seminar Synopsis on Performance ImprovementsDocument1 page3D IC Seminar Synopsis on Performance ImprovementsRavikumar ParagondNo ratings yet

- An Overview of 3D Integrated Circuits: Vachan Kumar Azad NaeemiDocument3 pagesAn Overview of 3D Integrated Circuits: Vachan Kumar Azad NaeemiMeghanand KumarNo ratings yet

- 3d IcDocument7 pages3d IcK HoneeyNo ratings yet

- Semi PDFDocument37 pagesSemi PDFShiva Kumar MkrNo ratings yet

- Naveen PPT 3d Ic TechnologyDocument21 pagesNaveen PPT 3d Ic TechnologyG NAVEEN KUMARNo ratings yet

- Rahul.P (3 023 PD16EI) : Seminar Report ONDocument13 pagesRahul.P (3 023 PD16EI) : Seminar Report ONRahul PawarNo ratings yet

- Cadence 3DICDocument9 pagesCadence 3DICRamakrishnaRao SoogooriNo ratings yet

- 3-Dimensional Integrated CircuitsDocument18 pages3-Dimensional Integrated CircuitsLokeshwar Reddy GajjelaNo ratings yet

- Vlsi Design - Ec - 701 - Unit - IDocument37 pagesVlsi Design - Ec - 701 - Unit - Iangelcrystl4774No ratings yet

- VLSI DesignDocument55 pagesVLSI DesignClique for Applied Research in Electronic TechnologyNo ratings yet

- 3D IC Technology: Improving Performance and Reducing PowerDocument1 page3D IC Technology: Improving Performance and Reducing PowerK HoneeyNo ratings yet

- 3D Ic Fabrication: K.ANUSHA (08W01A0402)Document1 page3D Ic Fabrication: K.ANUSHA (08W01A0402)Bhavani BommaNo ratings yet

- Report DecoderDocument84 pagesReport DecoderUmaizAhmedNo ratings yet

- Overview of 3D Architecture Design Opportunities and TechniquesDocument6 pagesOverview of 3D Architecture Design Opportunities and TechniquesPramod Reddy RNo ratings yet

- PD FlowDocument6 pagesPD FlowUTtNo ratings yet

- Development in Integrated CircuitsDocument6 pagesDevelopment in Integrated CircuitsRahul PanwarNo ratings yet

- A Survey On SoCDocument51 pagesA Survey On SoCLEE KAH YI -No ratings yet

- 3D Ics With Tsvs-Design Challenges and Requirements: Introductio NDocument11 pages3D Ics With Tsvs-Design Challenges and Requirements: Introductio NphanindrabodduNo ratings yet

- Three DIMENSIONAL-CHIPDocument6 pagesThree DIMENSIONAL-CHIPKumar Goud.KNo ratings yet

- IC Design Process, BEOL, FEOLDocument6 pagesIC Design Process, BEOL, FEOLsrijaNo ratings yet

- 3D IC Technology: Vinod Chauhan 108170Document23 pages3D IC Technology: Vinod Chauhan 108170vinodchauhannitNo ratings yet

- 3D Integrated CircuitsDocument21 pages3D Integrated CircuitssorabhNo ratings yet

- Tanner ManualDocument60 pagesTanner ManualFahim Ahmed100% (1)

- On "3D ICs"Document22 pagesOn "3D ICs"Rahul GargNo ratings yet

- A Presentation OnDocument25 pagesA Presentation OnK HoneeyNo ratings yet

- FPGA Implementation ON-Chip Communication Using Implementation of 9 Port Router For Ommunication Using V Outer For 3D VerilogDocument6 pagesFPGA Implementation ON-Chip Communication Using Implementation of 9 Port Router For Ommunication Using V Outer For 3D VerilogPraveen Kumar RNo ratings yet

- Design and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesFrom EverandDesign and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesNo ratings yet

- VlsiDocument12 pagesVlsiJaya SwaroopNo ratings yet

- VLSI Design FlowDocument3 pagesVLSI Design FlowMari SuganthiNo ratings yet

- VLSI Design Fault Tolerant Network On Chip: IPASJ International Journal of Electronics & Communication (IIJEC)Document3 pagesVLSI Design Fault Tolerant Network On Chip: IPASJ International Journal of Electronics & Communication (IIJEC)IPASJNo ratings yet

- Design for High Performance, Low Power, and Reliable 3D Integrated CircuitsFrom EverandDesign for High Performance, Low Power, and Reliable 3D Integrated CircuitsNo ratings yet

- Digital Electronics, Computer Architecture and Microprocessor Design PrinciplesFrom EverandDigital Electronics, Computer Architecture and Microprocessor Design PrinciplesNo ratings yet

- Three Dimensional System Integration: IC Stacking Process and DesignFrom EverandThree Dimensional System Integration: IC Stacking Process and DesignNo ratings yet

- 1 s2.0 S136403211930423X MainDocument13 pages1 s2.0 S136403211930423X MainWei WangNo ratings yet

- Geospatial Assessment of Climatic Variability and Aridity in Katsina State, NigeriaDocument11 pagesGeospatial Assessment of Climatic Variability and Aridity in Katsina State, NigeriaInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Strings: - A String Is A Sequence of Characters Treated As A Group - We Have Already Used Some String LiteralsDocument48 pagesStrings: - A String Is A Sequence of Characters Treated As A Group - We Have Already Used Some String LiteralsJNUNo ratings yet

- UEM Sol To Exerc Chap 097Document11 pagesUEM Sol To Exerc Chap 097sibieNo ratings yet

- A Case Study On Strategies To Deal With The Impacts of COVID-19 Pandemic in The Food and Beverage IndustryDocument13 pagesA Case Study On Strategies To Deal With The Impacts of COVID-19 Pandemic in The Food and Beverage IndustryPeyman KazemianhaddadiNo ratings yet

- UNDERSTANDING FOOD HYGIENEDocument22 pagesUNDERSTANDING FOOD HYGIENESahilDalalNo ratings yet

- Blue Ocean Strategy: A SummaryDocument21 pagesBlue Ocean Strategy: A SummaryDeshandra Afga NagaraNo ratings yet

- Learner's Module in Grade 7 Mathematics Pages 1 - 4 Global Mathematics, Page 2 - 18 Synergy For Success in Mathematics, Pages 2 - 13Document12 pagesLearner's Module in Grade 7 Mathematics Pages 1 - 4 Global Mathematics, Page 2 - 18 Synergy For Success in Mathematics, Pages 2 - 13Maricel Tarenio MacalinoNo ratings yet

- Seaskills Maritime Academy: Purchase OrderDocument8 pagesSeaskills Maritime Academy: Purchase OrderSELVA GANESHNo ratings yet

- BBVA OpenMind Book Change 19 Key Essays On How Internet Is Changing Our Lives Technology Internet InnovationDocument7 pagesBBVA OpenMind Book Change 19 Key Essays On How Internet Is Changing Our Lives Technology Internet InnovationSissiErricoNo ratings yet

- How Do I Create An Import DC ApplicationDocument10 pagesHow Do I Create An Import DC ApplicationPeter CheungNo ratings yet

- đề 3Document12 pagesđề 3Vi CầmNo ratings yet

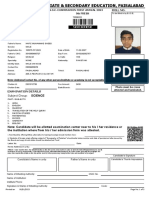

- Roll No. Form No.: Private Admission Form S.S.C. Examination First Annual 2023 9th FRESHDocument3 pagesRoll No. Form No.: Private Admission Form S.S.C. Examination First Annual 2023 9th FRESHBeenish MirzaNo ratings yet

- Ahu KitDocument37 pagesAhu KitLaurentiu LapusescuNo ratings yet

- Shading DevicesDocument4 pagesShading DevicesAyush TyagiNo ratings yet

- Y12 - Hand - Book - 2019 2Document22 pagesY12 - Hand - Book - 2019 2tiagoNo ratings yet

- Ch2 MCQ PDFDocument6 pagesCh2 MCQ PDFPratibha BhondeNo ratings yet

- Polycab PVCDocument32 pagesPolycab PVCshilpidangiNo ratings yet

- Breaking Into Software Defined Radio: Presented by Kelly AlbrinkDocument40 pagesBreaking Into Software Defined Radio: Presented by Kelly AlbrinkChris Guarin100% (1)

- SMEDA (Small and Medium Enterprises Development Authority)Document29 pagesSMEDA (Small and Medium Enterprises Development Authority)Salwa buriroNo ratings yet

- Safety Budget PlannerDocument12 pagesSafety Budget Plannersidhant nayakNo ratings yet

- PTE Academic Lesson Plan Ideas: Test Taking Strategies: Vikki Weston, Vessela GasperDocument2 pagesPTE Academic Lesson Plan Ideas: Test Taking Strategies: Vikki Weston, Vessela GasperStanley AlexNo ratings yet

- Best Clinical Embryology Courses in MaduraiDocument8 pagesBest Clinical Embryology Courses in MaduraiVaramreprogenesisNo ratings yet

- Counting Discrete Math ChoicesDocument2 pagesCounting Discrete Math ChoicesAfizah NazatulNo ratings yet

- E'Lyn Joyce Taylor: EducationDocument1 pageE'Lyn Joyce Taylor: EducationE'Lyn TaylorNo ratings yet

- Campus Event ReflectionDocument2 pagesCampus Event ReflectiondntbenfordNo ratings yet

- 2008 ALS AE SL October 0Document452 pages2008 ALS AE SL October 0James Paulo RefrescaNo ratings yet

- Tamil Nadu Govt Form for Testing Lab EMDocument4 pagesTamil Nadu Govt Form for Testing Lab EMPraveenNo ratings yet

- Common Phrasal VerbsDocument2 pagesCommon Phrasal VerbsOscar LasprillaNo ratings yet

- Eike Batista BiographyDocument9 pagesEike Batista BiographyGEORGEGeekNo ratings yet