0% found this document useful (0 votes)

196 views7 pagesCMOS Pass Gate Analysis

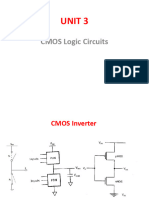

The document discusses the CMOS pass gate, which is a switch made from an NMOS and PMOS transistor connected in parallel. It operates in different regions depending on the input signal, with both transistors saturating to provide good switching. The pass gate introduces only a small delay but does not provide any power gain. Long chains of pass gates should be broken up with buffers to reduce the proportional N^2 delay.

Uploaded by

Bruno SilvaCopyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

196 views7 pagesCMOS Pass Gate Analysis

The document discusses the CMOS pass gate, which is a switch made from an NMOS and PMOS transistor connected in parallel. It operates in different regions depending on the input signal, with both transistors saturating to provide good switching. The pass gate introduces only a small delay but does not provide any power gain. Long chains of pass gates should be broken up with buffers to reduce the proportional N^2 delay.

Uploaded by

Bruno SilvaCopyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd