Professional Documents

Culture Documents

Powerblock 50 Fpga-4600/4110 Module: Datasheet

Uploaded by

Ali AhmadOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Powerblock 50 Fpga-4600/4110 Module: Datasheet

Uploaded by

Ali AhmadCopyright:

Available Formats

DATASHEET

PowerBlock 50 FPGA-4600/4110 Module

Real-Time Signal Processing and I/O Engine

Ultra-compact, rugged form factor with innovative conductioncooled design for harsh environments Features Xilinx Virtex-4 FX Series FPGA Gigabit Ethernet connection for external front-panel I/O High-bandwidth PCI Express interface to system backplane for inter-processor communication Customizable I/O capability

The PowerBlock 50 FPGA-4600/4110 Module from Mercury Computer Systems is a real-time signal processing and I/O card specifically designed for use in PowerBlock 50 ultra-compact embedded computers. Featuring either a Xilinx Virtex-4 FX60 or FX100 FPGA (field-programmable gate array) device, the module is ideal for demanding real-time sensor interfacing and signal processing applications. An integrated I/O daughtercard provides external I/O. The standard daughtercard provides support for two Gigabit Ethernet connections and an RS-232 serial connection. The standard internal chassis interconnection module allows only a single Ethernet and RS-232 connection to be routed to the chassis front-panel bulkhead plate. The FPGA4600/4110 can support up to 28 single-ended GPIO connections and 7 LVDS connections via a customized daughtercard and interconnection module. The FPGA-4600/4110, when integrated as part of a complete PowerBlock 50 system, can load onboard flash under the control of the chassis root-complex processor module.

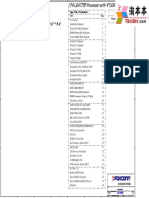

Processing Engine

The Xilinx Virtex FX Series features dual integrated 405 Power Architecture cores for optional use, and can provide up to 60 or 100 thousand logic blocks, depending on the device chosen. The FPGA is supported by a 64-bit bank of DDR2-400 SDRAM for high-speed data memory accesses and an additional bank of NOR flash memory for self-boot and persistent memory store.

Flexible I/O Subsystem

The FPGA-4600/4110s flexible daughtercard architecture allows the I/O for the board to be customized to meet specific application needs. The fully integrated module has three components: Main card houses the Xilinx FPGA device. Heat spreader is an aluminum heat sink used to spread the heat to the chassis walls. I/O daughtercard connects to a flex-circuit for carrying I/O signals to and from the PowerBlock 50 chassis front panel.

I/O Architecture

The PowerBlock 50 FPGA-4600/4110 Module connects to the PowerBlock 50 system backplane via four PCI Express lanes, providing 8 Gbps of full-duplex data bandwidth as the primary interconnect to other components in the system. A standard I2C serial bus is also brought off-board for system management, allowing the FPGA-4600/4110 to be monitored from the chassis root-complex processor module.

EEPROM Temp Sensor DDR2 256/512 MB Daughtercard Daughtercard Connector Backplane Connector #1 I2C

100 MHz PCIe x1 PCIe x4

EEPROM I2C RS-232 Buffer External I/O Connector

Backplane Connector #2

PCIe x3

Virtex-4 FX-60/100 (FF1152 Package)

100 MHz 250 MHz

28x GPIO 7x LVDS IO MGT MGT

Dual Gigabit Ethernet PHY

Transformer

PPL

Local Bus 16b

250 MHz 100 MHz

CPLD

Intel NOR Flash 32/64 MB

Not used on standard daughtercard

Figure 1. PowerBlock 50 FPGA-4600/4110 Module block diagram

Figure 2. Integrated I/O daughtercard architecture

www.mc.com

The I/O subsystem of the PowerBlock 50 system is designed for easy customization, depending on the I/O requirements of the target application. This is done through the modification of the individual processing module daughtercards, the I/O flex circuit, and, if required, the front-panel connector bulkhead plate. This design allows the PowerBlock 50 to be easily configured and tailored to meet the needs of virtually any high-performance signal processing application.

Backplane Interconnect Switch fabric 4-lane PCI Express serial interconnect, 10 Gbps, full-duplex System management I2C-based system management bus (SMBus) Integrated I/O Ethernet I/O Two Gigabit Ethernet ports on standard I/O daughtercard Serial I/O RS-232 on standard I/O daughtercard General-purpose I/O (for use with custom I/O daughtercard) 28x single-ended, LVTTL GPIO pins 7x LVDS (or 14x single-ended) GPIO pins Software Development tools Network-based FPGA flash upload capability Operating System Support Linux via proxy control from the root complex card Custom Engineering I/O daughtercard design kit and custom services available on request.

Mercury Professional Services

Customized configurations for the I/O subsystem are possible in addition to other customized system offerings at the board or system level. Consult with Mercurys professional services team to discuss your unique needs and requirements. With over 25 years of experience in addressing real-time multiprocessing complexities, Mercury can work with you to develop a custom solution, as required by your application. Our areas of expertise include embedded hardware design, algorithm optimization, and middleware framework development, as well as experience in meeting difficult environmental requirements.

Software Environment

The FPGA-4600/4110, when integrated as part of a complete system, comes with Linux BSP support.

Configurations

The PowerBlock 50 is sold only as a complete, fully configured system. The PowerBlock 50 FPGA-4600/4110 Module is not sold as a stand-alone module.

Environmental* Temperature Operating Storage Humidity 0 to 55C per VITA-47 CC1 -40C to +85C per VITA-47 CC1 15-90% RH, non-condensing

Specifications

Mechanical Size with daughtercard 100 mm x 89 mm x 15 mm (3.9 in x 3.4 in x 0.59 in) Weight Main card 83 g (2.93 oz) Fully integrated module 174 g (6.85 oz) Processing Engine FPGA Xilinx Virtex-4 FX60 or FX100 device FX60 60k logic block, 128 DSP slices, 4.2 Mb RAM FX100 100k logic block, 160 DSP slices, 6.8 Mb RAM External Memory SDRAM DDR2-400 64-bit SDRAM FX60 256 MB FX100 512 MB NOR flash FX60 32 MB FX100 64 MB

*The environmental parameters listed are for the system as currently qualified using the supported components as specified in the engineering development kit (EDK). Qualification in your application is dependent upon the heat exchange unit chosen, as well as the cooling fluid used. For further details, consult factory.

Electrical Input voltage 12V DC 2.5A (maximum) 3.3V DC 1.5A (maximum) Power consumption Absolute maximum 35W (application dependent) Typical 13-18W (application dependent)

Some of Mercurys products are subject to the jurisdiction of the U. S. International Traffic in Arms Regulations (ITAR). Please contact your Mercury sales representative for more information. PowerBlock ia a registered trademark and Challenges Drive Innovation is a trademark of Mercury Computer Systems, Inc. Other products mentioned may be trademarks or registered trademarks of their respective holders. Mercury Computer Systems, Inc. believes this information is accurate as of its publication date and is not responsible for any inadvertent errors. The information contained herein is subject to change without notice. Copyright 2008 Mercury Computer Systems, Inc. 1640.03E-DS-0908-PB50_fpga4600

Worldwide Locations Mercury Computer Systems has R&D, support and sales locations in France, Germany, Japan, the United Kingdom and the United States. For office locations and contact information, please call the corporate headquarters or visit our Web site at www.mc.com.

Corporate Headquarters 201 Riverneck Road Chelmsford, MA 01824-2820 USA +1 (978) 967-1401 +1 (866) 627-6951 Fax +1 (978) 256-3599 www.mc.com

Challenges Drive Innovation

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- GEK - 91741 Dynamic Retarding AssemblyDocument10 pagesGEK - 91741 Dynamic Retarding AssemblyKJDNKJZEFNo ratings yet

- Rajalakshmi Engineering College, Thandalam Department of Ece Lesson PlanDocument2 pagesRajalakshmi Engineering College, Thandalam Department of Ece Lesson PlanNassrinThibautNo ratings yet

- The Purpose of Business Activity: LECTURE # 01 & 02Document9 pagesThe Purpose of Business Activity: LECTURE # 01 & 02Ali AhmadNo ratings yet

- PH Alkalinity ExplainedDocument4 pagesPH Alkalinity ExplainedDean DsouzaNo ratings yet

- Lecture 2 - 30-01-08Document17 pagesLecture 2 - 30-01-08Ali AhmadNo ratings yet

- Electrical Theory: Howard W Penrose, PH.D., CMRP InstructorDocument79 pagesElectrical Theory: Howard W Penrose, PH.D., CMRP InstructorSandun LakminaNo ratings yet

- The Purpose of Business Activity: LECTURE # 01 & 02Document9 pagesThe Purpose of Business Activity: LECTURE # 01 & 02Ali AhmadNo ratings yet

- AC MaintenanceDocument21 pagesAC MaintenanceAli AhmadNo ratings yet

- Matlab Training - SIMULINKDocument8 pagesMatlab Training - SIMULINKAtta RehmanNo ratings yet

- Matlab Training - SIMULINKDocument8 pagesMatlab Training - SIMULINKAtta RehmanNo ratings yet

- Lectrue # 12 and 13 - 30-04-08Document26 pagesLectrue # 12 and 13 - 30-04-08Ali AhmadNo ratings yet

- Matlab Training Session Vii Basic Signal Processing: Frequency Domain AnalysisDocument8 pagesMatlab Training Session Vii Basic Signal Processing: Frequency Domain AnalysisAli AhmadNo ratings yet

- Matlab Training - Basic Control TheoryDocument10 pagesMatlab Training - Basic Control TheoryhamedNo ratings yet

- System On Chips Soc'S & Multiprocessor System On Chips MpsocsDocument42 pagesSystem On Chips Soc'S & Multiprocessor System On Chips MpsocsAli AhmadNo ratings yet

- Jan 2008 Course Outline FinanceDocument5 pagesJan 2008 Course Outline FinanceAli AhmadNo ratings yet

- Printing The Model:: SimulinkDocument8 pagesPrinting The Model:: SimulinkAli AhmadNo ratings yet

- Introduction To VHDL: AIR University AU, E-9, IslamabadDocument29 pagesIntroduction To VHDL: AIR University AU, E-9, IslamabadAli AhmadNo ratings yet

- Matlab Training Session Iii Numerical Methods: Solutions To Systems of Linear EquationsDocument14 pagesMatlab Training Session Iii Numerical Methods: Solutions To Systems of Linear EquationsAli AhmadNo ratings yet

- Matlab Training Session Iv Simulating Dynamic Systems: Sampling The Solution EquationDocument9 pagesMatlab Training Session Iv Simulating Dynamic Systems: Sampling The Solution EquationAli AhmadNo ratings yet

- Lecture 2Document26 pagesLecture 2Ali AhmadNo ratings yet

- Introduction To: Artificial IntelligenceDocument31 pagesIntroduction To: Artificial IntelligenceAli AhmadNo ratings yet

- Matlab Training - Writing M-Files - Scripts and FunctionsDocument6 pagesMatlab Training - Writing M-Files - Scripts and Functionsederdiego2709No ratings yet

- Operators: Introduction To ASIC DesignDocument6 pagesOperators: Introduction To ASIC DesignAli AhmadNo ratings yet

- 2-Level Logic ( 0', 1') .: Introduction To ASIC DesignDocument8 pages2-Level Logic ( 0', 1') .: Introduction To ASIC DesignAli AhmadNo ratings yet

- Example 5.1: Multiplexer #1 Using OperatorsDocument10 pagesExample 5.1: Multiplexer #1 Using OperatorsAli AhmadNo ratings yet

- Matlab Training Session Ii Data Presentation: 2-D PlotsDocument8 pagesMatlab Training Session Ii Data Presentation: 2-D PlotsAli AhmadNo ratings yet

- Acknowledgement - 2Document11 pagesAcknowledgement - 2Ali AhmadNo ratings yet

- Sequential Code in VHDLDocument42 pagesSequential Code in VHDLAli Ahmad0% (1)

- Small Neural Nets LabDocument6 pagesSmall Neural Nets LabAli AhmadNo ratings yet

- Introduction To ASIC Design: Lab Report StandardsDocument1 pageIntroduction To ASIC Design: Lab Report StandardsAli AhmadNo ratings yet

- Multiply and Accumulate Circuits LabDocument5 pagesMultiply and Accumulate Circuits LabAli AhmadNo ratings yet

- Introduction To ASIC Design: Lab Report InstructionsDocument1 pageIntroduction To ASIC Design: Lab Report InstructionsAli AhmadNo ratings yet

- Apl 2.1 IbmDocument584 pagesApl 2.1 IbmNisarg DaveNo ratings yet

- The Right Way To Install Windows XPDocument14 pagesThe Right Way To Install Windows XPlucleblanc442No ratings yet

- (Scientific and Engineering Computation) William Gropp, Ewing Lusk, Anthony Skjellum-Using MPI - Portable Parallel Programming With The Message-Passing Interface-The MIT Press (2014)Document330 pages(Scientific and Engineering Computation) William Gropp, Ewing Lusk, Anthony Skjellum-Using MPI - Portable Parallel Programming With The Message-Passing Interface-The MIT Press (2014)Favio90No ratings yet

- Definition and Scope of Gis: Geographic DataDocument18 pagesDefinition and Scope of Gis: Geographic DataKhan HarisNo ratings yet

- Mod 5Document3 pagesMod 5ganesh_karanamNo ratings yet

- ASR 9000 Series - Command ReferenceDocument936 pagesASR 9000 Series - Command ReferencekiennaNo ratings yet

- Foxconn 915m08 Rev 2.1 SCHDocument40 pagesFoxconn 915m08 Rev 2.1 SCHiskenderbeyNo ratings yet

- Overview of HP Compaq nx9000Document15 pagesOverview of HP Compaq nx9000Adrian Chua DaepNo ratings yet

- Computer Hardware Purchase and Sales SystemDocument2 pagesComputer Hardware Purchase and Sales SystemRDGAC CSDepartmentNo ratings yet

- CH340G USB To UART Interface DatasheetDocument2 pagesCH340G USB To UART Interface DatasheetDavid MoodyNo ratings yet

- AVR222: 8-Point Moving Average Filter: 8-Bit Microcontroller With Downloadable Flash Application NoteDocument3 pagesAVR222: 8-Point Moving Average Filter: 8-Bit Microcontroller With Downloadable Flash Application NoteAnonymous h87K4sTNo ratings yet

- Recommended Psu TableDocument2 pagesRecommended Psu TableFaisal Fikri HakimNo ratings yet

- Thyristor Power Control by IR RemoteDocument22 pagesThyristor Power Control by IR Remotevivek100% (1)

- Commodore 64 ArchitectureDocument4 pagesCommodore 64 ArchitectureKangyerka AndrásNo ratings yet

- A Windows Client Backup Does Not Cross A Mount Point Volume.Document3 pagesA Windows Client Backup Does Not Cross A Mount Point Volume.jeetmajum007No ratings yet

- MD 100T00 ENU PowerPoint - M01Document38 pagesMD 100T00 ENU PowerPoint - M01CourageMarumeNo ratings yet

- JetblueDocument5 pagesJetblueYasir QureshiNo ratings yet

- R20 MPMC Unit IiiDocument25 pagesR20 MPMC Unit IiiMaddineni TejaNo ratings yet

- MI2012-W User's ManualDocument70 pagesMI2012-W User's ManualAlex ZXNo ratings yet

- Debugger Ppc400Document72 pagesDebugger Ppc400carver_uaNo ratings yet

- Lisa 20 ControllerDocument22 pagesLisa 20 ControllerkieranNo ratings yet

- APPTB106B Electronic Schematic UpdateDocument14 pagesAPPTB106B Electronic Schematic UpdateJorge RomaNo ratings yet

- Dell M8428-k Converged Network Switch For M1000e Enclosures March 2011Document26 pagesDell M8428-k Converged Network Switch For M1000e Enclosures March 2011Ryan BelicovNo ratings yet

- LogDocument26 pagesLogNuru MohammedNo ratings yet

- Threads & Concurrency: Lecture 23 - CS2110 - Fall 2018Document34 pagesThreads & Concurrency: Lecture 23 - CS2110 - Fall 2018VishGovNo ratings yet

- C6930-0040 - Control Cabinet Industrial PC: VariantsDocument3 pagesC6930-0040 - Control Cabinet Industrial PC: VariantsĐậu Ngọc NgãiNo ratings yet

- Cryptocurrency System Using Body Activity Data Wo2020060606 2 of 6Document1 pageCryptocurrency System Using Body Activity Data Wo2020060606 2 of 6Nemo NemoNo ratings yet

- Allen & Heath M-Waves Card: User GuideDocument19 pagesAllen & Heath M-Waves Card: User GuideTokioNo ratings yet