Professional Documents

Culture Documents

Change Request 5.0.0: 25.211 CR 157 Rev 1

Uploaded by

Wind StormOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Change Request 5.0.0: 25.211 CR 157 Rev 1

Uploaded by

Wind StormCopyright:

Available Formats

3GPP TSG RAN Meeting #16 Marco Island, FL, U.S.A.

, 4 7, June 2002

R1-02-0812

CR-Form-v5

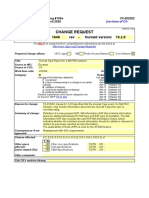

CHANGE REQUEST

25.211 CR 157

rev

Current version:

5.0.0

For HELP on using this form, see bottom of this page or look at the pop-up text over the symbols. Proposed change affects: Title: Source: (U)SIM ME/UE X Radio Access Network X Core Network

Clarification for uplink HS-DPCCH/HS-PDSCH timing TSG RAN WG1 Date: 15th May, 2002 Release: REL-5

Work item code: HSDPA-Phys Category: F

Use one of the following categories: Use one of the following releases: F (correction) 2 (GSM Phase 2) A (corresponds to a correction in an earlier release) R96 (Release 1996) B (addition of feature), R97 (Release 1997) C (functional modification of feature) R98 (Release 1998) D (editorial modification) R99 (Release 1999) Detailed explanations of the above categories can REL-4 (Release 4) be found in 3GPP TR 21.900. REL-5 (Release 5)

Reason for change:

With current specification of uplink HS-DPCCH/HS-PDSCH timing, there is the possibility that the UE changes the start of the HS-DPCCH relative to the start of the UL DPCCH without the Node B having the possibility of doing the same change.

Summary of change: Statement added clarifying that the UE shall only modify the start of HS-DPCCH relative to Ul DPCCH when downlink signalling on timing adjustment takes place. Consequences if not approved: Clauses affected: Other specs affected: Node B risks losing slot synchronisation of HS-DPCCH. 7.7 Other core specifications Test specifications O&M Specifications

Other comments:

How to create CRs using this form:

Comprehensive information and tips about how to create CRs can be found at: http://www.3gpp.org/3G_Specs/CRs.htm. Below is a brief summary: 1) Fill out the above form. The symbols above marked contain pop-up help information about the field that they are closest to. 2) Obtain the latest version for the release of the specification to which the change is proposed. Use the MS Word "revision marks" feature (also known as "track changes") when making the changes. All 3GPP specifications can be downloaded from the 3GPP server under ftp://ftp.3gpp.org/specs/ For the latest version, look for the directory name with the latest date e.g. 2001-03 contains the specifications resulting from the March 2001 TSG meetings.

CR page 1

3) With "track changes" disabled, paste the entire CR form (use CTRL-A to select it) into the specification just in front of the clause containing the first piece of changed text. Delete those parts of the specification which are not relevant to the change request.

CR page 2

Release 5

47

3GPP TS 25.211 V5.0.0 (2002-03)

Uplink/downlink timing at UE

At the UE, the uplink DPCCH/DPDCH frame transmission takes place approximately T 0 chips after the reception of the first detected path (in time) of the corresponding downlink DPCCH/DPDCH frame. T0 is a constant defined to be 1024 chips. The first detected path (in time) is defined implicitly by the relevant tests in [14]. More information about the uplink/downlink timing relation and meaning of T0 can be found in [5].

7.7 Uplink DPCCH/HS-DPCCH/HS-PDSCH timing at the UE

Figure 37 shows the timing offset between the downlink associated uplink DPCCH, the HS-PDSCH and the uplink HSDPCCH at the UE. The code-multiplexed uplink HS-DPCCH sub-frame starts m*256 m 256 chips after the start of thean uplink DPCCH slot with m selected by the UE such that the ACK/NACK transmission starts within the first 0255 chips after 7.5 slots following the end of the received HS-PDSCH sub-frame. UE and Node B shall only update m in connection to UTRAN reconfiguration of downlink timing. Note that due to autonomous adjustments of the DPDCH/DPCCH transmission time instant by the UE described in [5], the relationships described in this section may cease to be valid. More information about the uplink timing adjustments can be found in [5].

Tslot 2560 chips Uplink DPCCH 3Tslot 7680 chips HS-PDSCH at UE UEP (7.5Tslot = 19200 chips) HS-DPCCH m256 chips 3Tslot 7680 chips 0-255 chips

Figure 37: Timing structure at UE for UL HS-DPCCH control signalling

CR page 3

You might also like

- UNISAB II Profibus DP Protocol Extented - 16112005Document22 pagesUNISAB II Profibus DP Protocol Extented - 16112005Ubeda Juan67% (3)

- From GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandFrom EverandFrom GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandNo ratings yet

- How To Convert A Project From IAR To CCS - Texas Instruments WikiDocument11 pagesHow To Convert A Project From IAR To CCS - Texas Instruments Wikiteomondo100% (1)

- AAMA Updates Paint Specifications To 2017Document2 pagesAAMA Updates Paint Specifications To 2017uocmogiandi_aNo ratings yet

- Change Request 2 6.1.0: Tdoc NP-030347Document19 pagesChange Request 2 6.1.0: Tdoc NP-030347DũngNguyễnNo ratings yet

- Change Request 5.0.0: 25.211 CR 147 Rev 3Document4 pagesChange Request 5.0.0: 25.211 CR 147 Rev 3Wind StormNo ratings yet

- TP 030180Document13 pagesTP 030180Kranthi Kumar GuduruNo ratings yet

- RP 020427 PDFDocument18 pagesRP 020427 PDFMuhammad ZainNo ratings yet

- Change Request - 7.3.0: 25.321 CR 0315 RevDocument6 pagesChange Request - 7.3.0: 25.321 CR 0315 RevAshok GuptaNo ratings yet

- 3Gpp TSG Ran Wg1#12 Tdoc R1 - (00) 0490: 2 PCPCH Propagation Delay DefinitionDocument6 pages3Gpp TSG Ran Wg1#12 Tdoc R1 - (00) 0490: 2 PCPCH Propagation Delay DefinitionRZNo ratings yet

- 3GPP Meeting Discusses Single Sided RLC Re-establishmentDocument4 pages3GPP Meeting Discusses Single Sided RLC Re-establishmentmi007flexNo ratings yet

- Procedure for confirming SMS interworking agreementDocument20 pagesProcedure for confirming SMS interworking agreementsudhindraNo ratings yet

- Change Request - 9.2.0: 32.425 CR 0014 RevDocument5 pagesChange Request - 9.2.0: 32.425 CR 0014 RevTimmy ChengNo ratings yet

- CP 050098 PDFDocument48 pagesCP 050098 PDFJane GoodwinNo ratings yet

- MOCN Rerouting FunctionDocument9 pagesMOCN Rerouting FunctionAshok GuptaNo ratings yet

- User Plan & Control PlanDocument4 pagesUser Plan & Control PlanUsman ArshadNo ratings yet

- PDP Request-Response PDFDocument7 pagesPDP Request-Response PDFPurn Prakash TripathiNo ratings yet

- C4-203408 v3 29502 CR0343 CIoT MOdataDocument40 pagesC4-203408 v3 29502 CR0343 CIoT MOdataSayed A. HadeiNo ratings yet

- GP-101048 CR 45004 0017 VamosDocument4 pagesGP-101048 CR 45004 0017 Vamosalivelim44No ratings yet

- 3GPP TS 25.215 CR Clarifies GSM Time DifferenceDocument3 pages3GPP TS 25.215 CR Clarifies GSM Time DifferencevietlamvanNo ratings yet

- C-Simulator For Bluetooth ModemDocument12 pagesC-Simulator For Bluetooth ModemMuhammad AttiqueNo ratings yet

- Changes To Stage 2 Descriptions: RLC/MAC PDU Formats: Source: EricssonDocument4 pagesChanges To Stage 2 Descriptions: RLC/MAC PDU Formats: Source: EricssonAnonymous uUFj1s48nNo ratings yet

- 3GPP TSG CN Plenary Meeting #21 NP-030392 17 - 19 September 2003 Frankfurt, GERMANYDocument51 pages3GPP TSG CN Plenary Meeting #21 NP-030392 17 - 19 September 2003 Frankfurt, GERMANYfouad boutatNo ratings yet

- CTRL ACK in PCADocument3 pagesCTRL ACK in PCAIwan S SantosoNo ratings yet

- RP 020545Document102 pagesRP 020545Achour AnisNo ratings yet

- S2-200xxxx 23501 IIoT PTP r9Document22 pagesS2-200xxxx 23501 IIoT PTP r9abhishekinfoNo ratings yet

- Liaison on Mandatory UMTS AMR2 Support in Dual Mode TerminalsDocument14 pagesLiaison on Mandatory UMTS AMR2 Support in Dual Mode TerminalsViệt Trần LâmNo ratings yet

- CR1025 (Rel-11) R2-124258Document22 pagesCR1025 (Rel-11) R2-124258asfvNo ratings yet

- R2-1906688 TS 36.331 Propagating Changes Due To TS 38.331 R2-1902709Document50 pagesR2-1906688 TS 36.331 Propagating Changes Due To TS 38.331 R2-1902709Mini PourNo ratings yet

- MiCOM Alstom P54x Ver47 - 57K Addendum GBDocument186 pagesMiCOM Alstom P54x Ver47 - 57K Addendum GBSukant BhattacharyaNo ratings yet

- S5-201137rev1 Rel-16 CR TS 28.552 Correction of Packet Drop Rate MeasurementsDocument3 pagesS5-201137rev1 Rel-16 CR TS 28.552 Correction of Packet Drop Rate MeasurementsGlb manishNo ratings yet

- Change Request 3.4.1: 3GPP TSG-RAN3 Meeting #19Document49 pagesChange Request 3.4.1: 3GPP TSG-RAN3 Meeting #19Evgenia PetkovaNo ratings yet

- Clarifying PDP context activationDocument8 pagesClarifying PDP context activationsyrish2622No ratings yet

- T1-041852 (Correction To HSDPA RF TC 9.3.1)Document10 pagesT1-041852 (Correction To HSDPA RF TC 9.3.1)umtsrfNo ratings yet

- Introduction of Late Drop CapabilitiesDocument106 pagesIntroduction of Late Drop CapabilitiesThang DangNo ratings yet

- FLO-2D Porting Document (PRO Model)Document5 pagesFLO-2D Porting Document (PRO Model)Jason ChupicaNo ratings yet

- NP 010655 PDFDocument9 pagesNP 010655 PDFMinh Long ĐặngNo ratings yet

- Gprs Measurements Temsproducts 2Document33 pagesGprs Measurements Temsproducts 2Subrata SenNo ratings yet

- Change Request: 23.501 CR 2108 Rev 1 Current Version: 16.3.0Document8 pagesChange Request: 23.501 CR 2108 Rev 1 Current Version: 16.3.0sayondeepNo ratings yet

- CR0572R1 (Rel-11) R2-124361Document14 pagesCR0572R1 (Rel-11) R2-124361asfvNo ratings yet

- R1-143486 - 25.214 - CR0715R2 - (Rel-12, B) - Introduction of DCH EnhancementsDocument116 pagesR1-143486 - 25.214 - CR0715R2 - (Rel-12, B) - Introduction of DCH EnhancementsevolvingsatNo ratings yet

- 3Gpp TSG Ran Wg1 Berlin, Germany, 22 - 25 August, 2000: TSGR1#15 (00) 1099Document7 pages3Gpp TSG Ran Wg1 Berlin, Germany, 22 - 25 August, 2000: TSGR1#15 (00) 1099Avik ModakNo ratings yet

- TRW-24G 2.4GHz RF Tranceiver Module Data Sheet EDocument59 pagesTRW-24G 2.4GHz RF Tranceiver Module Data Sheet Ephongphat100% (1)

- Change Request - 9.5.0: 36.321 CR 0538 RevDocument3 pagesChange Request - 9.5.0: 36.321 CR 0538 RevonidaNo ratings yet

- Restriction for SF512 in UTRA FDD DownlinkDocument4 pagesRestriction for SF512 in UTRA FDD Downlinkhamadashraf301No ratings yet

- RL DeletionDocument5 pagesRL DeletionShejin RaghavanNo ratings yet

- 3GPP TS 24.072Document8 pages3GPP TS 24.072santanameroNo ratings yet

- JP-3GA-27.003 (R99) Terminal Adaptation Functions (TAF) For Services Using Synchronous Bearer CapabilitiesDocument27 pagesJP-3GA-27.003 (R99) Terminal Adaptation Functions (TAF) For Services Using Synchronous Bearer Capabilitiesatul_potdarNo ratings yet

- CRs update 3GPP specs listsDocument41 pagesCRs update 3GPP specs listsKiron HamiNo ratings yet

- CR0451 (Rel-10) R2-111564Document3 pagesCR0451 (Rel-10) R2-111564asfvNo ratings yet

- CR 25214-350r3 - HHO FailDocument6 pagesCR 25214-350r3 - HHO FailWind StormNo ratings yet

- S5-211053rev1 Rel-17 CR TS 28.552 Add PLMN Granularity For Packet Delay MeasurementsDocument7 pagesS5-211053rev1 Rel-17 CR TS 28.552 Add PLMN Granularity For Packet Delay MeasurementsGlb manishNo ratings yet

- D1532v3r4b-At Attachment With Packet Interface - 7 Volume 3Document304 pagesD1532v3r4b-At Attachment With Packet Interface - 7 Volume 3Randal OhlgartNo ratings yet

- Icon Database MainDocument138 pagesIcon Database MainmichetraviNo ratings yet

- Guía de Ubicación de La Literatura Técnica Del 3GGPDocument16 pagesGuía de Ubicación de La Literatura Técnica Del 3GGPdmarcanoNo ratings yet

- Ecp FormDocument3 pagesEcp FormPendurti SuryanarayanaNo ratings yet

- Draft C3-202252 - r2Document16 pagesDraft C3-202252 - r2Dante Eka SevilianaNo ratings yet

- Silcopac D Hardware & Software ManualDocument304 pagesSilcopac D Hardware & Software ManualSerge RinaudoNo ratings yet

- Rab SubflowDocument3 pagesRab SubflowBilal RaoNo ratings yet

- Change Request 7.13.0: 25.433 CR 1699 RevDocument58 pagesChange Request 7.13.0: 25.433 CR 1699 Revwijaya_dnyNo ratings yet

- Source: TSG-RAN WG2 Title: CR To 25.304 Rel-6 On H Criterion in HCS High-MobilityDocument7 pagesSource: TSG-RAN WG2 Title: CR To 25.304 Rel-6 On H Criterion in HCS High-Mobilitynguyenhien10No ratings yet

- Radio Link Timeout in AMRDocument6 pagesRadio Link Timeout in AMRWind Storm100% (2)

- BSC6900 UMTS V900R011C00SPC700 Parameter ReferenceDocument1,261 pagesBSC6900 UMTS V900R011C00SPC700 Parameter ReferenceOmarShakeelNo ratings yet

- RAN16.0 Capacity Monitoring Guide (BSC6910-Based) (01) (PDF) - enDocument58 pagesRAN16.0 Capacity Monitoring Guide (BSC6910-Based) (01) (PDF) - enKhiem Tran0% (1)

- HSPA SystemsDocument69 pagesHSPA Systemstonybinh2011No ratings yet

- LTE PCI EricssonDocument5 pagesLTE PCI Ericssonamstereo0% (1)

- BBU3900 Description 01 - 20120730 PDFDocument22 pagesBBU3900 Description 01 - 20120730 PDFDerrick WhiteNo ratings yet

- Handover (GBSS14 0)Document438 pagesHandover (GBSS14 0)Wind StormNo ratings yet

- BBU3900 Description 01 - 20120730 PDFDocument22 pagesBBU3900 Description 01 - 20120730 PDFDerrick WhiteNo ratings yet

- LTE PCI EricssonDocument5 pagesLTE PCI Ericssonamstereo0% (1)

- HSPA SystemsDocument69 pagesHSPA Systemstonybinh2011No ratings yet

- Cell Selection & ReselectionDocument35 pagesCell Selection & ReselectionVugar AliNo ratings yet

- 1.WCDMA RNO Power Control Algorithm Analysis and Parameter Configuration Guidance-20050316-A-1.0Document69 pages1.WCDMA RNO Power Control Algorithm Analysis and Parameter Configuration Guidance-20050316-A-1.0Hazem MaherNo ratings yet

- Hand OverDocument253 pagesHand OverAgung SetiyobudiNo ratings yet

- WCDMA RNO Handover Procedure Analysis GuidanceDocument92 pagesWCDMA RNO Handover Procedure Analysis GuidanceWind StormNo ratings yet

- W PS Service Problem Optimization Guide 20060723 A 3.1Document136 pagesW PS Service Problem Optimization Guide 20060723 A 3.1fireincitadelNo ratings yet

- 1 571 - PLMNDocument2,984 pages1 571 - PLMNWind StormNo ratings yet

- 25212CR130r5 (R1-02-0856)Document13 pages25212CR130r5 (R1-02-0856)Wind StormNo ratings yet

- 1.WCDMA RNO Power Control Algorithm Analysis and Parameter Configuration Guidance-20050316-A-1.0Document69 pages1.WCDMA RNO Power Control Algorithm Analysis and Parameter Configuration Guidance-20050316-A-1.0Hazem MaherNo ratings yet

- CRs On HSDPA (Part1) - RP020316-tableDocument1 pageCRs On HSDPA (Part1) - RP020316-tableWind StormNo ratings yet

- 3G Set URRCtrlswitchDocument29 pages3G Set URRCtrlswitchEfosa Aigbe100% (1)

- How To Analyze From 3G CouterDocument19 pagesHow To Analyze From 3G CouterWind StormNo ratings yet

- Change Request - 5.0.0: 25.211 CR 155 RevDocument2 pagesChange Request - 5.0.0: 25.211 CR 155 RevWind StormNo ratings yet

- CR 25214-350r3 - HHO FailDocument6 pagesCR 25214-350r3 - HHO FailWind StormNo ratings yet

- 25211CR150r1 (R1-02-0700)Document7 pages25211CR150r1 (R1-02-0700)Wind StormNo ratings yet

- 25212CR131r2 (R1-02-0768)Document6 pages25212CR131r2 (R1-02-0768)Wind StormNo ratings yet

- HSDPA Basic PrinciplesDocument39 pagesHSDPA Basic Principlesbigpack1982100% (2)

- Am85c30 10PCDocument68 pagesAm85c30 10PCDrykolosNo ratings yet

- Frampton - The Case For The TectonicDocument13 pagesFrampton - The Case For The Tectonicshou_eng0% (1)

- BCC ProfileDocument24 pagesBCC Profileveera149100% (1)

- Risk Management GuidelinesDocument16 pagesRisk Management GuidelinesG_RanjithNo ratings yet

- Coa Unit Test QP 1Document7 pagesCoa Unit Test QP 1Sagar K DedhiaNo ratings yet

- Purlinxxxxxss 222222Document9 pagesPurlinxxxxxss 222222Mc Tyler Reyes YuntingNo ratings yet

- BV Rules For The Classification and The Certification of Yachts Feb 08 Edition v1Document65 pagesBV Rules For The Classification and The Certification of Yachts Feb 08 Edition v1فضيلة عبدالرحمنNo ratings yet

- Floor Tiling-Method StatementDocument5 pagesFloor Tiling-Method StatementamroNo ratings yet

- Diameter Command CodesDocument157 pagesDiameter Command CodeslaoaaNo ratings yet

- 601 Layne BLVD - LandscapeDocument7 pages601 Layne BLVD - LandscapeSergio GonzálezNo ratings yet

- Evolution of Computers Through GenerationsDocument21 pagesEvolution of Computers Through Generationssiva prasadNo ratings yet

- Codigos de KotlinDocument497 pagesCodigos de KotlinDiego Vasquez VasquezNo ratings yet

- Azure Landing Zone Deployment - EnglishDocument2 pagesAzure Landing Zone Deployment - Englishrobi89stefanNo ratings yet

- EPD Laminas BituminosasDocument43 pagesEPD Laminas BituminosasRubiiKzzNo ratings yet

- Chilled beams: An efficient HVAC convection systemDocument1 pageChilled beams: An efficient HVAC convection systemrkibNo ratings yet

- Class Note Concrete Moddified 10 01 2069 PDFDocument63 pagesClass Note Concrete Moddified 10 01 2069 PDFPratik Babu GhimireNo ratings yet

- Concrete Beam DesignDocument4 pagesConcrete Beam DesignpetersiglosNo ratings yet

- 17th CenturyDocument32 pages17th CenturyhariniNo ratings yet

- WMS (Method Statement For Pouring Concrete On Slab On Grade)Document4 pagesWMS (Method Statement For Pouring Concrete On Slab On Grade)PUI CHEE KHIANNo ratings yet

- Cost of Doing BusinessDocument5 pagesCost of Doing BusinessmysubicbayNo ratings yet

- Curtain Wall System From Technal - Geode-BrochureDocument38 pagesCurtain Wall System From Technal - Geode-BrochurebatteekhNo ratings yet

- Measurement and Estimating of Internal and External Brick WallsDocument24 pagesMeasurement and Estimating of Internal and External Brick WallsaremyulNo ratings yet

- Quick Setup Domain Name System (DNS) For Solaris 10Document4 pagesQuick Setup Domain Name System (DNS) For Solaris 10biafranNo ratings yet

- PhoneView Install GuideDocument13 pagesPhoneView Install Guideozair_cisNo ratings yet

- AWS Certified Developer Associate ExamsampleDocument2 pagesAWS Certified Developer Associate ExamsampleTechMediaIncorpNo ratings yet

- Wayside ArtsTrail LeafletDocument2 pagesWayside ArtsTrail LeafletsteNo ratings yet

- Sqlmap - NewDocument19 pagesSqlmap - NewLuis Odar ZambranoNo ratings yet

- Item P-152 Excavation and Embankment: UnclassifiedDocument16 pagesItem P-152 Excavation and Embankment: UnclassifiedebherlinNo ratings yet