Professional Documents

Culture Documents

BSIM4 Gate Leakage Model Including Source-Drain Partition

Uploaded by

alokjadhavOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BSIM4 Gate Leakage Model Including Source-Drain Partition

Uploaded by

alokjadhavCopyright:

Available Formats

BSIM4 Gate Leakage Model Including Source-Drain Partition

K. M. Cao, W.-C. Lee

*

, W. Liu, X. Jin, P. Su, S. K. H. Fung

#

, J. X. An

+

, B. Yu

+

, and C. Hu

Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720, USA

Tel: 510-643-2639 Fax: 510-643-2636 Email: kcao@cory.eecs.berkeley.edu

*

Present addr: Intel Corp., Portland, OR,

#

IBM Corp., Fishkill, NY,

+

AMD Corp., Sunnyvale, CA

Abstract

Gate dielectric leakage current becomes a serious

concern as sub-20 gate oxide prevails in advanced

CMOS processes. Oxide this thin can conduct

significant leakage current by various direct-tunneling

mechanisms and degrade circuit performance. While

the gate leakage current of MOS capacitors has been

much studied, little has been reported on compact

MOSFET modeling with gate leakage. In this work, an

analytical intrinsic gate leakage model for MOSFET

with physical source/drain current partition is

developed. This model has been implemented in

BSIM4.

Introduction

As the gate length of MOSFETs is reduced to the sub-

100nm regime, gate oxide thickness of sub-20

prevails in CMOS processes [1]. Besides the benefits of

high drive current and low DIBL effect, such thin oxide

yields significant gate leakage current by various direct

tunneling mechanisms [2], with undesirable effects on

standby current and memory operation [3]. Comparing

to the compact leakage current models for MOS

capacitors [4,5], less research has been conducted on

the compact MOSFET models. C.-H. Choi [6]

proposed a gate leakage model for MOSFET but the

model is not accurate under low bias condition (in

direct-tunneling regime) and the current partition

scheme is unphysical. In this work, a physical gate

leakage model for MOSFET is developed and

implemented in BSIM4. Firstly, we propose an accurate

gate leakage model for the MOS capacitor. Then a

physical source-drain current partition model is

introduced. The model is verified with experimental

data and 2D simulation.

MOS Capacitor Leakage Model

Lee and Hu proposed an accurate dielectric leakage

model for MOS capacitors [5]. A simplified version of

this model with little compromises on accuracy is

the basis of the MOSFET gate leakage model.

There are three major leakage mechanisms for a

MOS structure, namely, electron conduction-band

tunneling (ECB), electron valence-band tunneling

(EVB), and hole valence-band tunneling (HVB), as

illustrated in Fig. 1. Each mechanism is dominant

or important in different regions of operation for

PMOS and NMOS as shown in Table 1. For each

J

ECB

J

EVB

ECB,SiO2

= 3.1 eV

J

HVB

J

ECB

J

EVB

ECB,SiO2

= 3.1 eV

J

HVB

Figure 1 Three mechanisms of gate dielectric direct

tunneling leakage.

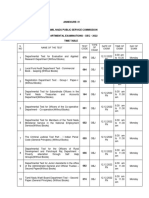

Table 1 Major mechanisms (as shown in Fig.1)

contributing to current components illustrated in Fig. 2.

The mechanism governing I

gso

and I

gdo

under all bias

conditions is ECB.

Current

Component

Igc

Igb

Region of

Operation

inversion

V

g

>0

V

g

<0

PMOS

HVB

ECB

EVB

NMOS

ECB

ECB

EVB

0-7803-6441-4/00/$10.00 (C) 2000 IEEE

mechanism, the leakage current density can be modeled

by:

( )( )

ox ox ox

t V V B

ox

aux g

ntox

ox

oxref

g

e

t

V V

t

T

A J

+

,

_

1

2

where

b

h q A 8

2

, h qm B

b ox

3 2 8

2 / 3

, m

ox

is the

effective carrier mass in oxide,

b

is the tunneling

barrier height (shown in Fig. 1),

ox

t is the oxide

thickness, T

oxref

is the reference oxide thickness at

which all the parameters are extracted, ntox is a fitting

parameter that defaults to 1, and

aux

V is an auxiliary

function which approximates the density of tunneling

carriers as well as available states and tabulated in

Table 2.

MOSFET Gate Leakage Model

As illustrated in Fig. 2, the gate tunneling current is

composed of several components. I

gb

is the gate-to-

substrate leakage current; I

gso

and I

gdo

are parasitic

leakage currents through gate-to-S/D extension overlap

region; and I

gc

is the gate-to-inverted channel tunneling

current. Part of I

gc

is collected by the source (I

gcs

) while

the rest goes to the drain (I

gcd

). I

gb

, I

gso

, I

gdo

, and I

gc

can

be easily determined from the MOS capacitor model

introduced in the previous section. The remaining

challenge is modeling I

gc

for nonzero V

ds

and

partitioning I

gc

into I

gcs

and I

gcd

.

To derive I

gcs

and I

gcd

, current continuity equation is

solved for the voltage along the channel as a function

of x, which is 0 at the source and L at the drain.

From drift equation, the channel current density in

source-drain direction is

( ) dx dV V V V C

th gs ox

.

Current continuity requires:

( ) ( )

( ) 0 +

ox g

th gs

C x J

dx

dx dV V V V d

where V(x) is the channel potential relative to the

source. The gate tunneling current density at x can

be approximated with

( ) V B

g

V V BT

oxs

E B

ox g

e J e AE e AE J

oxs ox ox

*

0

2 2

where J

go

is the gate tunneling current density with

V

ds

=0 (can be modelled by Eq. 1),

2

gcd

*

oxs ox i

V BT P B and

gs oxs

V V is the voltage

across the gate oxide at x=0. P

igcd

is a fitting

parameter added for flexibility with a default value

of 1.

Assuming the gate leakage current is small

compared to the drain current, the perturbation of

J

g

on V(x) is small,

( ) ( ) ( ) x V x V x V

1 0

+

where V

0

(x) is the solution of Eq. (2) with J

g

(x)=0

and V

0

(x)>>V

1

(x). V

0

(x) can be solved and

approximated to be:

( ) ( ) ( )

x K

L x V V V V V V V V x V

ds ds th gs th gs th gs

2 2

2

where

( )L V V V V V V K

th gs ds ds th gs

) 2 (

. This approximation

is not very accurate when x and V

ds

are both large

compared to L and V

gs

-V

th

respectively. However,

in that case J

g

is large only at small x, where the

approximation is accurate. Therefore, the

simplification is reasonable.

(1)

(2)

(3)

(4)

(5)

Table 2 The V

aux

function, which models the density of

tunneling carriers and available states.

Region of

Operation

Current V

aux

acc. I

gb

,

_

,

_

+

tm

fb gb

tm

V nigbacc

V V

V nigbacc exp 1 log

I

gb

,

_

,

_

+

tm

oxdepinv

tm

V nigbinv

eigbinv V

V nigbinv exp 1 log

inv.+dep.

I

gc

,

_

,

_

+

tm

th eff gs

tm

V nigc

V V

V nigc

0 _

exp 1 log

both I

gso

gs

V

both I

gdo

gd

V

Igso Igdo

Igb

Igcs Igcd

Igc

Figure 2 Components of tunneling current. I

gso

and I

gdo

are parasitic tunneling currents through gate-

source/drain overlap regions. I

gb

flows between gate and

substrate. I

gc

is the gate-to-channel tunneling current. It

is partitioned into I

gcs

, which flows to the source, and

I

gcd

, which flows to the drain.

0-7803-6441-4/00/$10.00 (C) 2000 IEEE

Eq. (2) can be further simplified considering

V

0

(x)>>V

1

(x).

( )

0 ) ( ) 0 (

, 0 2

1 1

0 1 0

2

0

2

1

2

1

2

0

0

*

+

L V V

C e J dx dV dx dV dx V d V dx V d V V

ox

V B

g gst

V

1

can then be solved as

( ) ( )

( ) Kx V K B C

e

L

x

e J

V

gst ox

KL B Kx B

g

'

+

2

2

*

0

1

* *

1 1

and I

gcs

and I

gcd

can be derived as:

( )

( )

( )

2 2

2

*

*

0 1

gcd

2 2

2

*

*

0

0

1

1

1

* *

*

L K B

e KLe B WL J

dx

dV

W KL V C I

L K B

e KL B WL J

dx

dV

W V C I

KL B KL B

g

L x

gst ox

KL B

g

x

gst ox gcs

+

+

Using the same derivation, better accuracy but more

complex equation can be obtained by including the

second order term in the exponent of Eq. (3).

From Eq. (8), the I

gc

-V

ds

function can then be easily

calculated as:

( )

KL B

e WL J

I

KL B

g

gc

*

0

*

1

Parameter extraction can follow two steps. The first

step is to extract the parameters in Eq. 1 from the

tunneling currents I

gc

(from shorted source and drain)

and I

gb

. The second step is to extract P

igcd

from the

gate-to-channel tunneling current as a function of drain

and gate bias using Eq. (9). Afterwards, the gate-to-

channel current partition can be calculated using Eq.

(8) without any parameter. The proposed partition

model is based on physical derivation and requires no

empirical parameters. This is especially important

because the partition ratio is extremely difficult or

impossible to measure.

Verification of the Model

We found that the proposed tunneling model (Eq. 1) for

MOS capacitors works well for all major mechanisms

(Fig. 3) and for a wide range of oxide thickness (Fig.

8). Our simple I

gc

-V

ds

model (Eq. 9) also agrees with

simulation results and experimental data very well as

shown in Fig. 4,5, and 11. The proposed partition

model (Eq. 8) is verified by simulation data as a

function of V

gs

(Fig. 6) and oxide thickness (Fig. 7). Fig.

9 shows the model agrees well with I

gc

-V

ds

data for

different V

gs

.

Summary

We have developed a simple gate dielectric leakage

current model suitable for compact MOSFET

models. This model considers all three major

leakage components and is accurate in direct-

tunneling regime with excellent T

ox

scaling

capability. Physical gate-to-channel current

partition models are developed for the first time.

With its great accuracy and satisfying test results

from the member companies of the Compact

Modeling Council (CMC), the proposed models

have been implemented into the BSIM4 and can

already help to address the impacts of gate leakage

current on circuit performance.

Acknowledgement: The work is supported by SRC

under Contract 98-SJ-417 and TI, Mentor

Graphics, Xilinx under MICRO program.

References

[1] 1999 International Technology Roadmap for Semiconductors.

[2] H. S. Momose et al., 1.5nm direct-tunneling gate oxide Si

MOSFETs, IEEE Trans. Elec. Dev., vol.43(8), pp. 1233, Aug. 1996.

[3] P. J. Wright and K. C. Saraswat, Thickness limitations of SiO2

gate dielectrics for MOS ULSI, IEEE Trans. Elec. Dev., vol.37(8),

pp. 1884, Aug. 1990.

[4]K. F. Schuegraf and C. Hu, Hole injection SiO2 breakdown model

for very low voltage lifetime extrapolation, IEEE Trans. Elec. Dev.,

vol. 41(5), pp.761, May 1994.

[5] W.-C. Lee and C. Hu, Modeling gate and substrate currents due

to conduction- and valence-band electron and hole tunneling, 2000

Symp. on VLSI Tech., pp.198, 2000.

[6] C.-H. Choi et al., Direct tunneling current model for circuit

simulation, IEDM Technical Digest pp.735, 1999.

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5

10

-8

10

-7

10

-6

10

-5

10

-4

10

-3

10

-2

10

-1

10

0

10

1

T

ox

=24.8 A

W/L=10/10

NMOS I

gc

(ECB)

NMOS I

gb

(EVB)

PMOS I

gc

(HVB)

Model

J

g

(

A

/

c

m

2

)

|V

g

| (V)

Figure 3 The proposed MOS model agrees with

measured data for tunneling mechanisms ECB, EVB,

and HVB.

(6)

(7)

(8)

(9)

0-7803-6441-4/00/$10.00 (C) 2000 IEEE

0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

0.0

0.2

0.4

0.6

0.8

1.0

V

gs

=1.5V

V

gs

=2.0V

Model

I

g

c

/

I

g

c

(

V

d

s

=

0

)

V

ds

(V)

Figure 4 The model and normalized I

gc

-V

ds

2D

simulation data at different V

gs

.

0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

0.0

0.2

0.4

0.6

0.8

1.0

T

ox

=20A

T

ox

=15A

Model

I

g

c

/

I

g

c

(

V

d

s

=

0

)

V

ds

(V)

Figure 5 The model and normalized I

gc

-V

ds

2D

Simulation data at different oxide thickness.

0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

0.0

0.1

0.2

0.3

0.4

0.5

V

gs

=1.5V

V

gs

=2.0V

Model

I

g

c

d

/

I

g

c

V

ds

(V)

Figure 6 The current partition model agrees with

simulation data at different V

gs

bias.

0.0 0.2 0.4 0.6 0.8 1.0 1.2

1.0x10

-9

1.5x10

-9

2.0x10

-9

2.5x10

-9

3.0x10

-9

V

gs

=0.6V x10

V

gs

=0.9V x3

V

gs

=1.2V x1

Experimental Data

Model

T

ox

=20A W/L=10m/2.7m

I

g

(

A

)

V

ds

(V)

Figure 9 Agreement of the model with experimental I

g

-

V

ds

data at different V

gs

bias.

0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

0.0

0.1

0.2

0.3

0.4

0.5

T

ox

=20A

T

ox

=15A

Model

I

g

c

d

/

I

g

c

V

ds

(V)

Figure 7 The current partition model agrees with

simulation data at different oxide thickness.

0.0 0.2 0.4 0.6 0.8 1.0 1.2

10

-4

10

-3

10

-2

10

-1

10

0

10

1

10

2

10

3

10

4

20A

18A

16A

12A

Data

Model

I

g

c

(

J

/

c

m

2

)

V

gs

(V)

Figure 8 The proposed MOS tunneling model is

scalable with oxide thickness (NMOS).

0-7803-6441-4/00/$10.00 (C) 2000 IEEE

You might also like

- Gate Tunneling Current and Quantum Effects in Deep Scaled MosfetsDocument5 pagesGate Tunneling Current and Quantum Effects in Deep Scaled Mosfetsashishj1083No ratings yet

- Device and Circuit Modeling Using Novel 3-State Quantum Dot Gate FETs PDFDocument2 pagesDevice and Circuit Modeling Using Novel 3-State Quantum Dot Gate FETs PDFyashreyNo ratings yet

- High Performance CMOS Four Quadrant Analog Multiplier in 45 NM TechnologyDocument6 pagesHigh Performance CMOS Four Quadrant Analog Multiplier in 45 NM TechnologyInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Analysis of Subthreshold Conduction in MOSFETs FronczakDocument20 pagesAnalysis of Subthreshold Conduction in MOSFETs FronczakJyotirmay SarkarNo ratings yet

- CMOS Modeling 1Document20 pagesCMOS Modeling 1telguardNo ratings yet

- FrereDocument4 pagesFrereShufan ChanNo ratings yet

- Low-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationDocument4 pagesLow-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationwhamcNo ratings yet

- Impact of MOSFET parameters on parasitic capacitancesDocument5 pagesImpact of MOSFET parameters on parasitic capacitancesNava KrishnanNo ratings yet

- Bilotti 1966Document3 pagesBilotti 1966dycsteiznNo ratings yet

- GaAs MESFET CharacteristicsDocument4 pagesGaAs MESFET CharacteristicsManogya SharmaNo ratings yet

- Spice Computation of MOSDocument10 pagesSpice Computation of MOSJaymee LalbhaiNo ratings yet

- Chapter 8Document43 pagesChapter 8CarolineNo ratings yet

- (NAAC Accredited "A++" Grade University) : Koneru Lakshmaiah Education FoundationDocument13 pages(NAAC Accredited "A++" Grade University) : Koneru Lakshmaiah Education FoundationLakshmi JagupillaNo ratings yet

- M B - P V C S G (CSG) Mosfet: Odeling of Uilt IN Otential Ariations OF Ylindrical Urrounding ATE SDocument11 pagesM B - P V C S G (CSG) Mosfet: Odeling of Uilt IN Otential Ariations OF Ylindrical Urrounding ATE SAnonymous e4UpOQEPNo ratings yet

- Analog Cmos Ic Design Unit-1Document50 pagesAnalog Cmos Ic Design Unit-1anil kumarNo ratings yet

- Dual Gate BucketDocument8 pagesDual Gate BucketVigneswaran VigneshNo ratings yet

- MOSFET High Frequency Model and Amplifier Frequency ResponseDocument17 pagesMOSFET High Frequency Model and Amplifier Frequency ResponseSunil JainNo ratings yet

- Effect of gate bias on SiC MOSFET short-circuit performanceDocument4 pagesEffect of gate bias on SiC MOSFET short-circuit performance刘锦成No ratings yet

- Inductance Leakage CalculationDocument6 pagesInductance Leakage Calculationnuswanggono1994No ratings yet

- 1990 Richard Alpha Power Law Mosfet Model PDFDocument11 pages1990 Richard Alpha Power Law Mosfet Model PDFrahmanakberNo ratings yet

- Vlsi Mod3 QnADocument24 pagesVlsi Mod3 QnAsri krishnaNo ratings yet

- Microelectronic CircuitDocument696 pagesMicroelectronic CircuitImtiaz AhmedNo ratings yet

- Q L A M Q W B Swsfet: Uaternary Ogic and Pplications Using Ultiple Uantum ELL Ased SDocument16 pagesQ L A M Q W B Swsfet: Uaternary Ogic and Pplications Using Ultiple Uantum ELL Ased SAnonymous e4UpOQEPNo ratings yet

- Pn-Junction: Excess Minority Carrier Charge Space ChargeDocument28 pagesPn-Junction: Excess Minority Carrier Charge Space ChargePrashant Kumar SinghNo ratings yet

- Compact Modeling of Parasitic Internal Fringe Capacitance Effects On The Threshold Voltage of High-K Gate Dielectric Nanoscale SOI MOSFETsDocument26 pagesCompact Modeling of Parasitic Internal Fringe Capacitance Effects On The Threshold Voltage of High-K Gate Dielectric Nanoscale SOI MOSFETsMamidala Jagadesh KumarNo ratings yet

- Exercise 2Document3 pagesExercise 2momolololilo4No ratings yet

- EE3408E Project Design A Two-Stage Operational AmplifierDocument4 pagesEE3408E Project Design A Two-Stage Operational AmplifierLaSo ASNo ratings yet

- CMOS Translinear CellsDocument4 pagesCMOS Translinear CellsSumitChoudharyNo ratings yet

- EC3058D-VLSI Circuits and Systems Winter Semester-2020-21Document2 pagesEC3058D-VLSI Circuits and Systems Winter Semester-2020-21Gamer AnonymousNo ratings yet

- Tunneling Leakage Current of Gate-All-AroundDocument3 pagesTunneling Leakage Current of Gate-All-AroundMahdi KarimiNo ratings yet

- Evaluation of Modern MOSFET Models For Bulk-Driven ApplicationsDocument4 pagesEvaluation of Modern MOSFET Models For Bulk-Driven Applications1zxcNo ratings yet

- Ece-V-fundamentals of Cmos Vlsi (10ec56) - SolutionDocument41 pagesEce-V-fundamentals of Cmos Vlsi (10ec56) - SolutionSanthosh Chandu C100% (2)

- High Speed, Low Power Current Comparators With Hysteresis: Neeraj K. ChastaDocument12 pagesHigh Speed, Low Power Current Comparators With Hysteresis: Neeraj K. ChastanengsintanovitaNo ratings yet

- Effect of Substrate Bias in The Capacitive Coupling of SOI UTBB MOSFETsDocument4 pagesEffect of Substrate Bias in The Capacitive Coupling of SOI UTBB MOSFETs浜本毅司No ratings yet

- Layout ExamplesDocument13 pagesLayout Examplesnazibhd786No ratings yet

- Lec03 AE MS14Document43 pagesLec03 AE MS14Mohsin Abbas ZafarNo ratings yet

- A Gm-Id Based Methodology For CMOS Analog DesignDocument6 pagesA Gm-Id Based Methodology For CMOS Analog DesignDeep SaxenaNo ratings yet

- Mosfet CharacteristicsDocument12 pagesMosfet CharacteristicsNavaneethaan NathamoorthyNo ratings yet

- High-Frequency Response Modelling of Continuous-Time Current MirrorsDocument7 pagesHigh-Frequency Response Modelling of Continuous-Time Current Mirrorsaiace00No ratings yet

- Design of XNOR Gate Using SET Based Linear Threshold GateDocument7 pagesDesign of XNOR Gate Using SET Based Linear Threshold GateInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Ultra Low Capacitance Measurements in Multilevel Metallisation CMOS by Using Built-In Electron-MeterDocument4 pagesUltra Low Capacitance Measurements in Multilevel Metallisation CMOS by Using Built-In Electron-MeterAlex WongNo ratings yet

- Eee-Vii-Vlsi Circuits and Design (10ee764) - NotesDocument225 pagesEee-Vii-Vlsi Circuits and Design (10ee764) - Notessammy100% (1)

- Design and Implementation of Hybrid CMOS-SET Half Adder and Full Adder CircuitsDocument9 pagesDesign and Implementation of Hybrid CMOS-SET Half Adder and Full Adder CircuitsInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Advance Vlsi Devices and Technology Project ReportDocument14 pagesAdvance Vlsi Devices and Technology Project ReportDileep MalgireddyNo ratings yet

- Vlsi ModuleDocument2 pagesVlsi ModuleAshwini kumarNo ratings yet

- 4727-Article Text-8485-1-10-20130718Document15 pages4727-Article Text-8485-1-10-20130718M4gne7icNo ratings yet

- Ultra-Low-Power 2.4 GHZ Colpitts Oscillator Based On Double Feedback TechniqueDocument4 pagesUltra-Low-Power 2.4 GHZ Colpitts Oscillator Based On Double Feedback TechniqueCamila DamascenoNo ratings yet

- 1 s2.0 S1386947703006325 Main PDFDocument4 pages1 s2.0 S1386947703006325 Main PDFDjo Ko VichNo ratings yet

- Quantum Cost Optimization For Reversible Sequential CircuitDocument7 pagesQuantum Cost Optimization For Reversible Sequential CircuitAlak MajumderNo ratings yet

- P 103Document7 pagesP 103An HoaNo ratings yet

- A Linear Programming Based Static Power Optimization Scheme For Digital CMOS Circuits AMSC 662 - Project ProposalDocument3 pagesA Linear Programming Based Static Power Optimization Scheme For Digital CMOS Circuits AMSC 662 - Project ProposalSatish Babu BodakuntaNo ratings yet

- Wideband Dual Posts Waveguide Band Pass FilterDocument7 pagesWideband Dual Posts Waveguide Band Pass FilterAmador Garcia IIINo ratings yet

- Unit-I VLSI & CDDocument39 pagesUnit-I VLSI & CD21EC17- JAYA PRASAD.PNo ratings yet

- DDDC87ECAA084E5DA4D2D77F7DC80391Document5 pagesDDDC87ECAA084E5DA4D2D77F7DC80391Sameer NandagaveNo ratings yet

- Lecture - MOS & MOSFET-1Document21 pagesLecture - MOS & MOSFET-1Kartika MunirNo ratings yet

- Compact Analytical Drain Current Model of Gate-All-Around Nanowire Tunneling FETDocument5 pagesCompact Analytical Drain Current Model of Gate-All-Around Nanowire Tunneling FETKadava R N Karthik 20PHD7152 (SENSE)No ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyFrom EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo ratings yet

- Electrochemical Processes in Biological SystemsFrom EverandElectrochemical Processes in Biological SystemsAndrzej LewenstamNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Common Source Amplifier: Experiment Date: 4 October 2011 Name: P.JAGADEESH (11MVD0015)Document11 pagesCommon Source Amplifier: Experiment Date: 4 October 2011 Name: P.JAGADEESH (11MVD0015)alokjadhavNo ratings yet

- Nmos Configuration ImplementationDocument7 pagesNmos Configuration ImplementationalokjadhavNo ratings yet

- PCS - Communication Systems - Linear ModulationDocument111 pagesPCS - Communication Systems - Linear Modulationaccessgm0% (1)

- Exp D - FFDocument5 pagesExp D - FFalokjadhavNo ratings yet

- Pmos Configuration ImplementationDocument7 pagesPmos Configuration ImplementationalokjadhavNo ratings yet

- Post Layout Delay Calculation Using RCXDocument6 pagesPost Layout Delay Calculation Using RCXalokjadhavNo ratings yet

- Custom IC Design Lab Post Layout Delay CalculationDocument6 pagesCustom IC Design Lab Post Layout Delay CalculationalokjadhavNo ratings yet

- RFICDocument9 pagesRFICalokjadhavNo ratings yet

- OxidationDocument69 pagesOxidationalokjadhavNo ratings yet

- FALLSEM2013 14 CP2782 21 Aug 2013 RM01 Power Efficiency of Modulation SchemesDocument7 pagesFALLSEM2013 14 CP2782 21 Aug 2013 RM01 Power Efficiency of Modulation SchemesalokjadhavNo ratings yet

- EpitaxyDocument23 pagesEpitaxyalokjadhavNo ratings yet

- FALLSEM2013 14 CP2782 21 Aug 2013 RM01 Power Efficiency of Modulation SchemesDocument7 pagesFALLSEM2013 14 CP2782 21 Aug 2013 RM01 Power Efficiency of Modulation SchemesalokjadhavNo ratings yet

- 1 3Document7 pages1 3Gaurav MittalNo ratings yet

- 1 10Document63 pages1 10Gaurav GoyalNo ratings yet

- CH 04 POCADocument36 pagesCH 04 POCAalokjadhavNo ratings yet

- Noise AnalysisDocument9 pagesNoise AnalysisalokjadhavNo ratings yet

- Pipelined ProcessorsDocument17 pagesPipelined Processorsalokjadhav100% (1)

- 1 Modeling TutorialDocument13 pages1 Modeling TutorialalokjadhavNo ratings yet

- CMOS Question FN-3Document3 pagesCMOS Question FN-3alokjadhavNo ratings yet

- Pipelined ProcessorsDocument17 pagesPipelined Processorsalokjadhav100% (1)

- Cov LetterDocument4 pagesCov LetteralokjadhavNo ratings yet

- 1 10Document63 pages1 10Gaurav GoyalNo ratings yet

- 1 3Document7 pages1 3Gaurav MittalNo ratings yet

- Testing Lab Assignment IIDocument25 pagesTesting Lab Assignment IIalokjadhav100% (1)

- DFT IntroDocument14 pagesDFT IntroalokjadhavNo ratings yet

- Testing Lab Assignment IIDocument25 pagesTesting Lab Assignment IIalokjadhav100% (1)

- Analog Lab 6Document4 pagesAnalog Lab 6alokjadhavNo ratings yet

- Testing Lab Assignment IIDocument25 pagesTesting Lab Assignment IIalokjadhav100% (1)

- Practice ProblemsDocument48 pagesPractice ProblemsalokjadhavNo ratings yet

- Water Booster Pump Calculations - Plumbing Engineering - Eng-TipsDocument3 pagesWater Booster Pump Calculations - Plumbing Engineering - Eng-TipsNeal JohnsonNo ratings yet

- 2020-Effect of Biopolymers On Permeability of Sand-Bentonite MixturesDocument10 pages2020-Effect of Biopolymers On Permeability of Sand-Bentonite MixturesSaswati DattaNo ratings yet

- English 3 PDFDocument177 pagesEnglish 3 PDFÇèrela ĆlavəcillasNo ratings yet

- Test Bank For Pediatric Nursing The Critical Components of Nursing Care 2nd Edition Kathryn Rudd Diane KociskoDocument36 pagesTest Bank For Pediatric Nursing The Critical Components of Nursing Care 2nd Edition Kathryn Rudd Diane Kociskolaurencelittlehdcj100% (25)

- Reference Interval For CeruloplasminDocument3 pagesReference Interval For CeruloplasminGawri AbeyNo ratings yet

- Ultra FXDocument17 pagesUltra FXmanikumar0No ratings yet

- Giáo Trình LPTD 2Document40 pagesGiáo Trình LPTD 2Hưng Trịnh TrọngNo ratings yet

- Kafka Netdb 06 2011 PDFDocument15 pagesKafka Netdb 06 2011 PDFaarishgNo ratings yet

- Root Cause Analysis: Identifying Factors Behind Patient Safety IncidentsDocument5 pagesRoot Cause Analysis: Identifying Factors Behind Patient Safety IncidentsPrabhas_Das7No ratings yet

- USA Gas TurbineDocument4 pagesUSA Gas TurbineJustin MercadoNo ratings yet

- Air Brake System For Railway CoachesDocument40 pagesAir Brake System For Railway CoachesShashwat SamdekarNo ratings yet

- CFPA E Guideline No 2 2013 FDocument39 pagesCFPA E Guideline No 2 2013 Fmexo62No ratings yet

- Project Report On Stock ExchangeDocument11 pagesProject Report On Stock Exchangebhawna33% (3)

- Transferring Maps To Your Mobile Device (Avenza PDF Maps) : For Apple Products (Ipad, Iphone, Ios)Document2 pagesTransferring Maps To Your Mobile Device (Avenza PDF Maps) : For Apple Products (Ipad, Iphone, Ios)m.naufal nurrahmanNo ratings yet

- FSA&V Case StudyDocument10 pagesFSA&V Case StudyAl Qur'anNo ratings yet

- The Guide To Modern Event PlanningDocument31 pagesThe Guide To Modern Event Planningsilversurfer123No ratings yet

- Consumer PerceptionDocument61 pagesConsumer PerceptionPrakhar DwivediNo ratings yet

- Get TRDocDocument209 pagesGet TRDoc10131No ratings yet

- ANNEXURE IV Dec 2022 enDocument17 pagesANNEXURE IV Dec 2022 enadvocacyindyaNo ratings yet

- Las Cookery 1Document3 pagesLas Cookery 1Loli Gonzales ArtiagaNo ratings yet

- (Nano and Energy) Gavin Buxton - Alternative Energy Technologies - An Introduction With Computer Simulations-CRC Press (2014) PDFDocument302 pages(Nano and Energy) Gavin Buxton - Alternative Energy Technologies - An Introduction With Computer Simulations-CRC Press (2014) PDFmarcosNo ratings yet

- Introduction To Human Anatomy & Physiology: Prepared by Mr. Abhay Shripad Joshi Yash Institute of Pharmacy AurangabadDocument18 pagesIntroduction To Human Anatomy & Physiology: Prepared by Mr. Abhay Shripad Joshi Yash Institute of Pharmacy AurangabadMourian AmanNo ratings yet

- Hele 4 PPT - 2nd QT - Week 1Document47 pagesHele 4 PPT - 2nd QT - Week 1jerico juarezNo ratings yet

- Ndeb Bned Reference Texts 2019 PDFDocument11 pagesNdeb Bned Reference Texts 2019 PDFnavroop bajwaNo ratings yet

- SW - Simulation - Product MatrixDocument2 pagesSW - Simulation - Product Matrixsamar2011No ratings yet

- Electrical Experimenter 1915-08Document1 pageElectrical Experimenter 1915-08GNo ratings yet

- Laser Beam Machining (LBM)Document10 pagesLaser Beam Machining (LBM)RAMAKANT RANANo ratings yet

- Performance Evaluation of Root Crop HarvestersDocument15 pagesPerformance Evaluation of Root Crop HarvestersIJERDNo ratings yet

- Continuous Improvement Strategies in TQMDocument28 pagesContinuous Improvement Strategies in TQMSimantoPreeomNo ratings yet

- Gen - Biology 2 Module 2Document12 pagesGen - Biology 2 Module 2Camille Castrence CaranayNo ratings yet