Professional Documents

Culture Documents

High-k Gate Dielectric Seminar Report

Uploaded by

amitgayaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

High-k Gate Dielectric Seminar Report

Uploaded by

amitgayaCopyright:

Available Formats

High-k gate dielectric

Seminar ID: 564

A Technical Seminar Report

submitted in partial fulfillment of

the requirement for the B.Tech.

under Biju Patnaik University of Technology, Rourkela.

Submitted By

AMIT RANJAN Roll No. ECE201110040

AUG - 2014

Under the guidance of

Mr. Chandan Kumar Pandey

APEX INSTITUTE OF TECHNOLOGY & MANAGEMENT

Pahala, Bhubaneswar, Odisha 752101, India

APEX INSTITUTE OF TECHNOLOGY & MANAGEMENT

Pahala, Bhubaneswar, Odisha 752101, India

CERTIFICATE

This is to certify that the seminar work entitled High-K Gate

Dielectric is a bonafide work being done by Mr. Amit Ranjan bearing

Registration No. 1101314076 of ECE branch.

This seminar report is submitted in partial fulfillment for the requirement

of the B.Tech. degree under Biju Patnaik University of Technology,

Rourkela, Odisha.

(Mr. CHANDAN KUMAR PANDEY )

Seminar Guide

(Mrs. T.Mita Kumari) (Prof. R.C. Das)

B .Tech Seminar Coordinator PRINCIPAL

i

ABSTRACT

The term high- dielectric refers to a material with a high dielectric constant (as

compared to silicon dioxide). High- dielectrics are used in semiconductor

manufacturing processes where they are usually used to replace a silicon dioxide gate

dielectric or another dielectric layer of a device. The implementation of high- gate

dielectrics is one of several strategies developed to allow further miniaturization of

microelectronic components, colloquially referred to as extending Moore's Law.

ii

ACKNOWLEDGEMENT

I would like to express my immense sense of gratitude to my guide, Mr. Chandan

Kumar Pandey, for his valuable instructions, guidance and support throughout my

seminar.

I again owe my special thanks to Mrs. T.Mita Kumari, Technical Seminar

Coordinator for giving me an opportunity to do this report.

And finally thanks to Prof. R.C. Das, Principal, APEX Institute Of Technology and

Management for his continued drive for better quality in everything that happens at

APEX Institute Of Technology and Management. This report is a dedicated

contribution towards that greater goal.

(Amit Ranjan)

ECE201110040

iii

TABLE OF CONTENTS

ABSTRACT ................................................................................................................... i

ACKNOWLEDGEMENT ........................................................................................... ii

List of figures ............................................................................................................... iv

List Of tables ................................................................................................................ v

1. Introduction .............................................................................................................. 1

2.Brief History of the High-k gate dielectric ............................................................. 2

3. Relevance of High-k materials in Microelectronics ..................................... 3

4. Needs For High-K gate Dielectric ........................................................................... 5

First principles ....................................................................................................... 5

Gate capacitance impact on drive current ............................................................... 6

5. High-k materials....................................................................................................... 7

6. Materials reqirement for high-k gate dielectrics ............................................... 10

6.1 Thermodynamic stability...........................................................................11

6.2 Kinetic stability..........................................................................................11

6.3 High quality interface................................................................................12

6.4 Amorphous to crystalline transition temperature..........................................12

7. Latest Development in Hf-Based High-k Oxides ..................................... 14

7.1 Nitrogen doped Hf-based oxides..............................................................14

7.2 Silicon doped Hf-based oxides.................................................................15

8. Application of high k dielectrics in CMOStechnology and emerging new

technology ................................................................................................................... 16

9. Conclusion .............................................................................................................. 18

References ................................................................................................................... 19

iv

List of figures

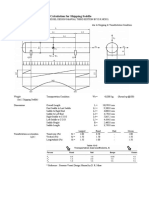

Figure 4.1 Conventional silicon dioxide gate dielectric structure compared to

a potential high-k dielectric

structure............................................................................05

Figure6.1 xrd spectra for the Hfo2 and HfoxNy

films.......................................................................................................14

v

List Of tables

Table 5.1 Leading high-k candidates with their properties ...................9

High-k gate dielectric

1

1. Introduction

Microelectronics has undergone enormous development in recent years with an ever

increasing performance of integrated circuits. This development has been made

possible by modern CMOS technology, notably the down-scaling of transistor

dimensions that leads to an exponential increase in the number of transistors on a

chip. The downscaling and performance improvement of transistors have so far

followed a trend predicted by Gorden. E. Moore, the Intel cofounder, in 1960s.

However this may become difficult in the very near future due to a number of issues

related to excessive power consumption and heat generation in integrated circuits.

Therefore, the semiconductor industry is looking for alternate performance boosters,

in particular by introducing new materials and new device architecture in place of

traditional, standard silicon CMOS technology.

In order to be well-prepared with options to continue scaling during such a scenario,

nearly a decade of research and development has been conducted by various groups.

The different approaches include, introduction of high - k gate dielectric, low-k

interconnects, replacement of bulk silicon with strained silicon-on-insulator (sSOI),

high mobility channel material like germanium, GaAs, graphene etc. and non planar

CMOS device structures like FinFET. As the scaling has clearly reached fundamental

material limits, especially for gate oxide, further scaling can be realized only by

introducing new materials with higher k values. If the thickness of the standard

2

SiO

based gate dielectric drops below the tunneling limit, gate leakage current will

increase tremendously. For an oxide thickness of 1.5 nm at 1.5 V the leakage current

density would be 100A/cm2 which is obviously undesirable for low power

applications . To prevent tunneling currents, physically thicker dielectric layers are

required. As the gate dielectric become physically thicker, transistor requires a

material with high dielectric constant to maintain its electrical characteristics. In 2007

a hafnium based high-k dielectric material was introduced for the first time by Intel.

High-k gate dielectric

2

2.Brief history of the high-k gate dielectric

To overcome gate leakage problems, incorporation of nitrogen into

2

SiO has been

adopted. There are several ways to introduce nitrogen into

2

SiO , such as post

deposition annealing in nitrogen ambient and forming a nitride/oxide stack structure.

By incorporating nitrogen into

2

SiO , it not only increases the dielectric constant but

also acts as a better barrier against boron penetration. In addition, a nitride/oxide stack

structure maintains the benefits of good interface quality between the oxide and

substrate . Despite the immense development with

2

SiO , these oxynitrides still have

low k values and so a relatively thick layer is required to prevent direct tunneling

current. Therefore, alternative materials with a higher k than

2

SiO are needed to

achieve the required capacitance without tunneling currents. A lot of oxides have been

proposed, unfortunately due to limitations dictated by low power applications,

scalability, or serious reactions with the Si substrate. The choice of alternative gate

dielectrics has been narrowed to

2

HfO ,

2

ZrO and their silicates due to their excellent

electrical properties and high thermal stability in contact with Si.

However, another problem associated with Hf-based and Zr-based oxides is low

crystallization temperature. They can easily crystallize during standard CMOS

processes. Hf-based oxides are preferred over Zr-based oxides for its relative higher

crystalline temperature. These crystalline structures can increase the gate leakage

which providing pathways for diffusion of dopants and dielectric breakdown. Many

focused on the improvement of the crystallization temperature of these oxides, such as

N, Si, Al, Ta and La have been incorporated into these Hf-based high-k oxides.

High-k gate dielectric

3

3. Relevance of high-k materials in

microelectronics

The dramatic performance improvements in microelectronics over the past few

decades have been accomplished by severe reduction in the size of memory and logic

devices. The capacitance density (C/A) is directly proportional to k value and

inversely propositional to thickness of the dielectric layer as given by the equation:

ox

t

k

A

C

0

c

=

.........................................................(1)

where

ox

t

and k are the thickness and relative dielectric constant of

the high-k material respectively.

Scaling demanded drastic decrease of the

2

SiO thickness to achieve never-higher

capacitance densities. Fundamental limits of

2

SiO as a dielectric material, imposed by

electron tunneling, will be reached as the film thickness approaches ~1 nm. This

thickness is already at a level where severe problems start to occurring .At thickness

the dielectric will not be able to effectively withstand voltages and tunneling current.

Another problem related to the

2

SiO scaling is reliability; the requirements for

reliability are even more difficult to meet than the leakage current requirements. The

solution for the aforementioned problems related to

2

SiO scaling is to select a gate

dielectric with a higher permittivity than that of

2

SiO (k =3.9) which can provide a

lower equivalent oxide thickness at higher physical thickness.

The equivalent oxide thickness (EOT ) of a material is defined as the thickness of the

2

SiO layer that would be required to achieve the same capacitance density as the

high-k material in consideration. EOT is thus given by

ox

t

k

EOT *

9 . 3

|

.

|

\

|

=

.......................................................(2)

High-k gate dielectric

4

Numerous high-k materials ranging from

3 2

O Al (k ~ 9) to perovskites (k ~ 102104)

are being actively investigated, in order to identify a long term promising material.

However, finding a suitable high-k material is a major challenge because the selected

material must have a higher resistivity, act as a good barrier layer, be thermally stable,

and form an ideal interface with silicon.

2

SiO films can be conveniently formed via

oxidation of the silicon substrate. In contrast, high-k materials must be formed by

deposition. Atomic layer deposition (ALD) has emerged as a very promising

technique for depositing high-k thin films for the microelectronics industry.

High-k gate dielectric

5

4. Needs for high-k gate dielectric

Silicon dioxide has been used as a gate oxide material for decades. As transistors have

decreased in size, the thickness of the silicon dioxide gate dielectric has steadily

decreased to increase the gate capacitance and thereby drive current, raising device

performance. As the thickness scales below 2 nm, leakage currents due to tunneling

increase drastically, leading to high power consumption and reduced device

reliability. Replacing the silicon dioxide gate dielectric with a high- material allows

increased gate capacitance without the associated leakage effects.

. First principles

The gate oxide in a MOSFET can be modeled as a parallel plate capacitor. Ignoring

quantum mechanical and depletion effects from the Si substrate and gate,

the capacitance Cof this parallel plate capacitor is given by

t

A k

C

0

c

=

..........................(3)

fig.4.1 Conventional silicon dioxide gate dielectric structure compared to a

potential high-k dielectric structure[4]

Where

- A is the capacitor area

- is the relative dielectric constant of the material (3.9 for silicon dioxide)

High-k gate dielectric

6

-

0

c is the permittivity of free space

- t is the thickness of the capacitor oxide insulator

Since leakage limitation constrains further reduction of t, an alternative method

to increase gate capacitance is alter by replacing silicon dioxide with a high-

material. In such a scenario, a thicker gate oxide layer might be used which can

reduce the leakage current flowing through the structure as well as improving

the gate dielectric reliability.

Gate capacitance impact on drive current

The drain current ID for a MOSFET can be written (using the gradual channel

approximation) as

( )

2

2

,

th G

inv sat D

V V

C

L

W

I

=

.........................................(4)

Where

- W is the width of the transistor channel

- L is the channel length

- is the channel carrier mobility (assumed constant here)

-

inv

C is the capacitance density associated with the gate dielectric when the

underlying channel is in the inverted state

-

G

V is the voltage applied to the transistor gate

-

D

V is the voltage applied to the transistor drain

-

th

V is the threshold voltage

The term

G

V

th

V is limited in range due to reliability and room temperature

operation constraints, since a too large

G

V would create an undesirable, high electric

field across the oxide. Furthermore, Vth cannot easily be reduced below about 200

mV, because leakage currents due to increased oxide leakage (that is, assuming high-

dielectrics are not available) and subthreshold conduction raise stand-by power

consumption to unacceptable levels. Thus, according to this simplified list of factors,

High-k gate dielectric

7

an increased ID,sat requires a reduction in the channel length or an increase in the gate

dielectric capacitance.

5. High-k materials

High-k gate dielectric

8

The choice of a material with higher dielectric constant than silicon dioxide can give

the same equivalent oxide thickness with a higher gate oxide but many of them did

not have all the desired properties. High-k materials under investigation include

3 2

O Al ,

3 2

O Y ,

2

CeO ,

2

HfO ,

2

ZrO ,

3 2

O La . The dielectric constants of these ALD

grown films vary from 3.9 to 300. Searching for the best high-k candidate is not an

easy task since each of these materials does impose some challenges. Table 5.1 lists

the major high-k candidates and their properties.

Material (ev) E

g

k-value ( ) ev E

c

A ( ) ev E

V

A Stability

with si

Crystal

structure

High-k gate dielectric

9

2

SiO

9 3.9 3.5 4.4 yes Amorphous

4 3

N Si 5 7.5 2.4 1.8 yes Amorphous

3 2

O Al 8.7 8.5-10.5 2.8 4.9 yes Amorphous

5 2

O Ta 4-4.5 20-35 0.3 3.1 no Orthorhombic

2

Tio

3-3.5 30-100 1.2 1.2 yes Tetragonal

3 2

O La 4.3 27 2.3 0.9 yes Hexagonal,

cubic

3 2

O Y 5.6 12-20 2.3 2.6 yes Cubic

2

HfO

5.7 35 2.5 3.4 yes Cubic,

Tetragoal

2

ZrO

5.8 25 1.4 3.3 yes Monoclinic

5 2

O Gd 5.4 12-23 3.2 3.9 yes Amorphous

Table 5.1: Leading high-k candidates with their properties[1]

High-k gate dielectric

10

6. Materials reqirement for high-k gate

dielectrics

There is a set of material and electrical requirements for a viable alternate high-k gate

dielectric material . Major requirements include:

Larger energy band gap with higher barrier height to Si substrate and metal

gate to reduce the leakage current.

Large k value.

Good thermodynamic stability on Si to prevent the formation of a low-k

2

SiO

interface.

Good kinetic stability.

High amorphous-to-crystalline transition temperature to maintain a stable

morphology after heat treatment.

Low oxygen diffusion coefficients to control the formation of a thick low-k

interface layer.

Low defect densities in high-k bulk films and at the high-k/Si interface with

negligible C-V hysteresis (< 30 mV).

Low fixed charge density (~1010cm-2eV-1).

Low high-k/Si interface state density (~1010cm-2eV-1).

High enough channel carrier mobility (~90% of SiO2/Si system).

Good reliability and a long life time.

High-k gate dielectric

11

In addition, the new high-k gate dielectric material must be compatible with current

CMOS fabrication process flow and other materials used in the CMOS integrated

circuits. In the following sections the most important high-k requirements are

discussed in detail.

6.1 Thermodynamic stability

A potential gate oxide insulator must be thermodynamically stable on silicon surface.

Current microprocessor device fabrication process usually take place at high

temperatures (>10000 C). During this process the dielectric must remain in a solid

state. If a thin high-k gate dielectric material is thermodynamically unstable on

Silicon, it tends to react with Si at an elevated temperature and an interface layer will

be formed between the high- k layer and Si substrate. This interface layer usually has

a low k value and acts as a series capacitor with the high-k dielectric layer. This low-k

interface will deteriorate the electrical properties of the final high-k gate stack

structure.

6.2 Kinetic stability

The new high-k material should be compatible with existing process conditions.

Assuming we choose an amorphous oxide material , this requires that the oxide

remains amorphous when annealed up to 1000C for 5 seconds. This is strenuous

condition in that

2

SiO is an excellent glass former but most other high-k materials are

not. Aluminium Oxide (

3 2

O Al ) is a reasonably good glass former and is the best.

5 2

O Ta is moderately good glass former, but was eliminated because it is reactive. All

other oxides crystallize bellow 1000C. This problem can be overcome by alloying

the desired oxide with a glass former like

2

SiO or

3 2

O Al giving either a silicate or

aluminate. This is how the industry now retain the stability against crystallization

close to 1000C .

High-k gate dielectric

12

6.3 High quality interface

2

SiO -Si interface offers the best interface quality (interface trap density Dit~1010eV-

1cm-2) for the Si channel area of the MOSFETs. A comparable interface quality will

be expected between the high-k gate dielectric and Si. However, almost all high-k

materials exhibit one or two orders of magnitude high interface state density and

significant flat band voltage shift (WVFB), mainly due to a high fixed charge density.

The origin of the high interface defect density is still under intensive investigation.

Lucovsky et al. reported that bonding constraints of the high-k materials may play a

significant role in determining high-k/Si interface quality. Experimental results

showed that if the average number of bonds per atom is over 3 for a metal oxide, an

over-constrained high-k/Si interface will form and the Dit will increase exponentially.

Similarly, a metal oxide with a low coordination number will form an under-

constrained high-k/Si interface, which will also lead to a high interface state density

and poor device performance. In addition, formation of metal silicide at the interface

will also generate unfavorable bonding conditions to the device characteristics.

Ideally, no metal oxide or silicide should be present at or close to the

2

SiO /Si

interface. In addition, the gate oxide/Si substrate interface must have minimum oxide

fixed charges and interface trap charges to minimize carrier scattering at the channel

(to maximize mobility). Amorphous layers are generally preferred for gate oxides to

minimize electrical and mass transport along the grain boundaries and therefore to

minimize the gate leakage current.

6.4 Amorphous-to-crystalline transition

temperature

A polycrystalline gate dielectric layer will suffer a high leakage current because their

grain boundaries may serve as a leaky path. Variation in the grain size and crystal

orientation of the polycrystalline films may also cause a non-uniform dielectric

property within the dielectric films, which will become a reliability concern for

practical application. Although single crystal oxides may theoretically solve the

High-k gate dielectric

13

problems caused by grain boundaries and provide films with good quality, at present

they can only be grown by molecular beam epitaxy (MBE) deposition method . It will

be a great challenge to incorporate MBE deposition into the traditional CMOS

fabrication process flow due to the inherent low throughput. In contrast, high quality

amorphous high-k gate dielectrics can be easily deposited by commercial ALD

equipment. Amorphous high-k gate dielectric layers will also offer reproducible and

isotropic dielectric properties. Almost all metal oxides of interest tend to crystallize

either during deposition or after heat treatment. For traditional CMOS fabrication

process flow, heat treatment above 1000C will be needed for the source/drain and

poly-Si dopant activation after ion implantation. Therefore, an amorphous-to-

crystalline transition temperature above 1000C will be required. For example,

2

HfO

and

2

ZrO will crystallize at very low temperature (~500C) . Of all the high-k

candidate materials, only

3 2

O Al can stay amorphous at 10008 temperature. However,

3 2

O Al does not have a sufficient high dielectric constant (k) value, adding a third

element into the material may increase the amorphous-to-crystalline transition

temperature. For example adding a small layer of

3 2

O Al with

2

HfO layer will

enhance crystallization temperature of

2

HfO .

High-k gate dielectric

14

7. Latest development in Hf-based high-k

oxides

Crystallization of pure

2

HfO occurs at only about 4004500 C causing grain

boundary leakage current and non-uniformity of the film thickness. As a result,

impurities such as O, B, and P can penetrate the grain boundaries during high

temperature post processing. It causes equivalent oxide thickness (EOT) scaling and

reliability concerns when Hf-based high-k ultrathin gate oxides are integrated into

high temperature CMOS processes.

7.1 Nitrogen doped Hf-based high-k oxides

Nitrogen introduction into

2

HfO films has significantly improved the electric

properties as well as crystallinity but nitrogen doping leads to decreased band gap.

Despite the disadvantages, the introduced nitrogen can suppress the growth of

microstructure and interfacial layer. When N is added to

2

HfO , it is expected to

distort the equilibrium of the lattice and produce disordered states. Researches have

demonstrated that adding nitrogen results in the reduction of the mobility of Hf and O

atoms as well as increase in the nucleation temperature and consequently the

crystalline temperature. All these indicate that nitrogen acts as a crystallization

inhibitor and causes an increase in the crystallization temperature in Hf-based gate

dielectrics.

fig.6.1 XRD spectra for the

2

HfO and HfOxNy films.[1]

High-k gate dielectric

15

7.2 Silicon doped Hf-based high-k oxides

The interfacial layer between the high-k dielectrics and Si substrate is one of the key

factors determining the performance and reliability of a MOS transistor. Hence, it is

extremely crucial to fabricate a

2

SiO /Si like interface. A

2

SiO interfacial layer is

often grown between Hf-based oxide and Si by thermal oxidation,

2

HfO /

2

SiO gate

dielectric stack usually introduces an additional EOT increase due to the low k SiOx

interfacial layer, whereas addition of Si into Hf-based oxide to form Hf silicate will

improve interface quality and foster the formation of amorphous structures. A

negative effect is the reduction in the k value, the k value decreases inversely with

increasing Si concentration in Hf-based oxides. By using nitrogen incorporated

HfSiO films, HfSiON is thermally stable compared to

2

HfO due to the Si-N bonds

that are created by the nitridation step, and thus HfSiON has the potential for

implementation in a conventional gate-first process with high temperature activation

annealing.

High-k gate dielectric

16

8. Application of high-k dielectrics in CMOS

technology and

emerging new technology

High K dielectric for DRAM capacitor

DRAM capacitor must have a minimum capacitance of ~ 30 fF per cell in order to

provide enough sensing margin and data retention time. When devices scale, the area

occupied by the capacitor must scale in order to obtain a small cell size even when

the capacitance stays fixed. For trench capacitor, the capacitor surface area must be

increased by etching deeper trenches. For stacked capacitor, it is difficult to increase

the surface area indefinitely and high K dielectric must be used to obtain smaller cell

sizes. To achieve high capacitance, the equivalent oxide thickness must be 1nm or

lower. Unlike gate dielectric, the DRAM capacitor is very sensitive to leakage. The

data retention time suffers greatly if the capacitor leakage exceeds ~ 1 fA/cell. The

most commonly selected high K dielectrics are

5 2

O Ta ,

3 2

O Al , or BST (Ba-Sr-

Titanate) in order to ensure low leakage. These high K dielectrics also contain fixed

charges that manifest into displacement current that degrades the access speed. High

K dielectric capacitors may be constructed using either polysilicon electrodes or metal

electrodes. Polysilicon electrode has the advantage of simpler processing, but the

disadvantage of high resistance which adversely impact the access speed of DRAM.

Metal electrode, on the other hand, has low resistance but may interact strongly with

both high K material and Si. Consequently, expensive noble metal such as Ir and Ru

are used. Metal oxides (high K) are extremely sensitive to plasma and hydrogen

damage and thus need to be either protected or isolated from hydrogen and plasma.

Recently,

2

IrO and

2

RuO electrodes are adopted because of their stabilizing effects

on high K dielectric. The successful application of high K dielectric will be the key to

future high speed DRAM technology.

High-k gate dielectric

17

High k ferroelectrics for FeRAM capacitor

Most ferroelectrics have very high permittivity in the order of 500 1000. These

dielectrics contain permanent dipoles that can be oriented by applying an electric

field, and thus are suitable for non-volatile data storage. The memory cell is very

similar to DRAM, consisted of a capacitor and an access MOS transistor. The storage

node is usually in the form of a ferroelectric capacitor, with PZT or SBT as the

dielectric. FeRAM not only is non-volatile, but also consumes little power during

switching because it is a voltage device and not a current device. The datum is stored

in the form of dipole polarization and thus requires no current to charge and discharge

the capacitor. It is also very fast (< 100 ns access time) compared to other non-volatile

memories for the same reason. Consequently, it becomes an ideal memory for

embedded and SoC (System-on-Chip) applications the most important being hand-

held devices such as cellular phone, and contactless smart card which requires both

high speed and low power. High K ferroelectrics for FeRAM, however, face

several daunting challenges. Both PZT and SBT require high temperature (650C

700C) to form ferroelectric phase and even when noble metal electrode (Pt, Ru, Ir) is

used it interacts with the ferroelectric. They also are extremely sensitive to plasma and

hydrogen induced damage. In addition, oxygen vacancy at electrode interface causes

severe fatigue degradation. Recent progress in using

2

IrO electrodes has greatly

alleviated the above problems and large array up to 32 Mb is demonstrated . In

addition, epitaxial growth of PZT on

3

LaNiO electrode at < 400C further allows the

embedding of FeRAM in SoC using capacitor over interconnect (COI) modular

concept .

High-k gate dielectric

18

9. Conclusion

Extensive R & D Efforts for High-k Gate Dielectrics Are Needed to Realize

- EOT<<1nm

- Low Gate Leakage Current

- Good Thermal stability

- Desired Vt for Both Channels

- High Drive Current and Transconductance

- Good Reliability

High-k gate dielectric

19

References

[1]. M. Houssa, High-k Gate Dielectrics, Institute of Physics Publishing, Bristol, UK

(2004).

[2]. S. M. Sze, Physics of Semiconductor Devices, 2nd ed., John Wiley & Sons, New

York (1981).

[3]. J. P. Chang, in High-k Gate Dielectric Deposition Techniques, High Dielectric

Constant Materials, H. R. Huff and D. C. Gilmer, Editors, p. 379, Springer-Verlag,

New York (2005).

[4]. G.D Wilk, R.M Wallace, and J.M Anthony, J. Appl. Phys. 89, 5243 (2001).

[5]. Robertson, J. (2005). Interfaces and defects of high-K oxides on silicon, vol. 49,

pp. 283-293, Solid-State Electronics.

[6]. Huang, A.P; Yang, Z.C; Chu, P.K, Hafnium-based High-k Gate Dielectrics.

[7]. T. Hori, Gate Dielectrics and MOS ULSIs: Principles, Technologies,

and Applications, Springer, Berlin, Germany (1997).

[8]. N. A. Chowdhury, P. Srinivasan, D. Misra, R. Choi, and B. H. Lee, Paper

presented at the SEMATECH International Workshop on Electrical Characterization

and Reliability for High-k Devices, Austin, TX, p. 143 (2004).

You might also like

- Plasma Etching Processes for Interconnect Realization in VLSIFrom EverandPlasma Etching Processes for Interconnect Realization in VLSINicolas PossemeNo ratings yet

- Pub06 286 SPT NDT 097Document10 pagesPub06 286 SPT NDT 097rafaelNo ratings yet

- Thin Dielectric Layers Characterization Using Corona-Oxide-Semiconductor Measurement TechniqueDocument54 pagesThin Dielectric Layers Characterization Using Corona-Oxide-Semiconductor Measurement TechniqueTejpreet Singh BediNo ratings yet

- Recent Advances in NM-OSCILLATOR Design With CMOS Technology: An OverviewDocument6 pagesRecent Advances in NM-OSCILLATOR Design With CMOS Technology: An OverviewInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- High-K Dielectric Materials in MicroelectronicsDocument31 pagesHigh-K Dielectric Materials in MicroelectronicsAadil ShNo ratings yet

- A Technical Seminar Report 19q91a0429 Ece ADocument32 pagesA Technical Seminar Report 19q91a0429 Ece ASushmaNo ratings yet

- CAF Article PDFDocument4 pagesCAF Article PDFZetocha MilanNo ratings yet

- Fabricating P-N Junction DiodesDocument4 pagesFabricating P-N Junction DiodesRishav SainiNo ratings yet

- Chapter 5 Fabrication of Microelectronic DevicesDocument26 pagesChapter 5 Fabrication of Microelectronic Devicesmuhamadsaidi100% (2)

- PHD Thesis - Dalong Zhao-ZnO TFT Thin Film Passivation - Noise Analysis, Hooge ParameterDocument169 pagesPHD Thesis - Dalong Zhao-ZnO TFT Thin Film Passivation - Noise Analysis, Hooge Parameterjiaxin zhangNo ratings yet

- (Alexander A. Demkov, Alexandra Navrotsky) Materials Fundamentals of Gate DielectricsDocument477 pages(Alexander A. Demkov, Alexandra Navrotsky) Materials Fundamentals of Gate Dielectricsemmanuel799No ratings yet

- A Technical Seminar Report On New Technologies Used in The Maintainences of Uderground CablesDocument24 pagesA Technical Seminar Report On New Technologies Used in The Maintainences of Uderground Cablesmohd aamirNo ratings yet

- ReliabilityIssuesofSiCMOSFETs ATechnologyforHigh TemperatureEnvironmentsDocument10 pagesReliabilityIssuesofSiCMOSFETs ATechnologyforHigh TemperatureEnvironmentssezgin bayramNo ratings yet

- Fabrication of Microelectronic DevicesDocument26 pagesFabrication of Microelectronic DevicesAbid YusufNo ratings yet

- NanotechnologyDocument8 pagesNanotechnologyChinmay KulkarniNo ratings yet

- EE6303-Linear Integrated Circuits and Applications Q&ADocument24 pagesEE6303-Linear Integrated Circuits and Applications Q&AY RohitNo ratings yet

- MaterialDocument32 pagesMaterialanujsuryaNo ratings yet

- Review and PerspectiveDocument11 pagesReview and PerspectiveSandeep GaanNo ratings yet

- Implementation of High-k/Metal Gates in High-Volume ManufacturingDocument5 pagesImplementation of High-k/Metal Gates in High-Volume ManufacturingA J AYNo ratings yet

- Die Attach Materials For High Temperature Applications - A ReviewDocument22 pagesDie Attach Materials For High Temperature Applications - A ReviewHanLe DuyNo ratings yet

- Materials Science and Engineering - R - Reports Volume 72 Issue 6 2011 (Doi 10.1016/j.mser.2010.12.001) J.H. Choi Y. Mao J.P. Chang - Development of Hafnium Based High-K Materials-A Review PDFDocument40 pagesMaterials Science and Engineering - R - Reports Volume 72 Issue 6 2011 (Doi 10.1016/j.mser.2010.12.001) J.H. Choi Y. Mao J.P. Chang - Development of Hafnium Based High-K Materials-A Review PDFRajesh VermaNo ratings yet

- Packaging Reliability Threat of MiniaturizationDocument4 pagesPackaging Reliability Threat of Miniaturizationasamadh100% (1)

- Master Thesis: Tasuku KanedaDocument77 pagesMaster Thesis: Tasuku Kanedamkali345No ratings yet

- Cap III-Advanced Materials - 2021 - Shi - Wide Bandgap Oxide Semiconductors From Materials Physics To Optoelectronic DevicesDocument30 pagesCap III-Advanced Materials - 2021 - Shi - Wide Bandgap Oxide Semiconductors From Materials Physics To Optoelectronic Devicessalvador monsalvoNo ratings yet

- Smart Packaging of Electronics and Integrated MEMS Devices Using LTCCDocument6 pagesSmart Packaging of Electronics and Integrated MEMS Devices Using LTCCgoutham ezhilarasuNo ratings yet

- High-Temperature Cuprate Superconductors Get To Work: Physics Today April 2005Document8 pagesHigh-Temperature Cuprate Superconductors Get To Work: Physics Today April 2005mangla bhullarNo ratings yet

- Progress Report I Mohamad Aliff 7697 ElectrolyzerDocument34 pagesProgress Report I Mohamad Aliff 7697 ElectrolyzerggleichgesinntenNo ratings yet

- Aurora's Engineering College: Transparent ElectronicsDocument40 pagesAurora's Engineering College: Transparent ElectronicsNarasimha TejaNo ratings yet

- Thin-Film-Silicon Solar Cells: J. Cárabe and J.J. GANDIA CIEMAT, 22 Avda. Complutense, E-28040 Madrid, SpainDocument6 pagesThin-Film-Silicon Solar Cells: J. Cárabe and J.J. GANDIA CIEMAT, 22 Avda. Complutense, E-28040 Madrid, SpainLong HoàngNo ratings yet

- Muralidharetal IEEE Vol23pp36015042013 PDFDocument5 pagesMuralidharetal IEEE Vol23pp36015042013 PDFGianc87No ratings yet

- Accepted Manuscript: Materials Today NanoDocument98 pagesAccepted Manuscript: Materials Today NanocobianNo ratings yet

- Nanotecnologia ArticuloDocument4 pagesNanotecnologia ArticuloAndresNo ratings yet

- Project Report On Integrated CircuitDocument20 pagesProject Report On Integrated CircuitSushil Kumar67% (6)

- Silver Thick Film Pastes For Low Temperature Co-Fired Ceramics: Impact of Glass Frit VariationDocument7 pagesSilver Thick Film Pastes For Low Temperature Co-Fired Ceramics: Impact of Glass Frit Variationmap vitcoNo ratings yet

- Jlpea 12 00043Document13 pagesJlpea 12 00043RAZNo ratings yet

- Engineering Encyclopedia: Metallic Communications CableDocument45 pagesEngineering Encyclopedia: Metallic Communications CableMahmoud AlwasifNo ratings yet

- I-V Characteristic of Cdo/Ps HeterojunctionDocument6 pagesI-V Characteristic of Cdo/Ps HeterojunctionInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Ch22-Materials Selection and Design ConsiderationDocument29 pagesCh22-Materials Selection and Design ConsiderationBryan de GuiaNo ratings yet

- IM02 Basic Electronics 2023Document10 pagesIM02 Basic Electronics 2023Simon DeracoNo ratings yet

- Final Report-1Document5 pagesFinal Report-1ISANI VENKATESHWAR REDDY 210146265No ratings yet

- An Industrial Training Report On-1Document35 pagesAn Industrial Training Report On-1rigeldewNo ratings yet

- Ee2254 Lica QBDocument0 pagesEe2254 Lica QBnjparNo ratings yet

- ME - MTECH III Sem Dissertation Akram KhanDocument25 pagesME - MTECH III Sem Dissertation Akram KhanHarish MahoreNo ratings yet

- Planar LTCC Transformers For High-Voltage Flyback ConvertersDocument15 pagesPlanar LTCC Transformers For High-Voltage Flyback Convertersигорь сидоренкоNo ratings yet

- Advanced Ceramics - 4th Year - Lecture NotesDocument44 pagesAdvanced Ceramics - 4th Year - Lecture Notesdrsaadbhf100% (1)

- Seminar Report on Digital Light Processing TechnologyDocument30 pagesSeminar Report on Digital Light Processing TechnologylittlerasikanNo ratings yet

- Breakdown Performance of Compound StructureDocument4 pagesBreakdown Performance of Compound StructureTrầnHữuHòaNo ratings yet

- Extremly ScaledDocument14 pagesExtremly ScaledeleenaamohapatraNo ratings yet

- Pun2018 Article LatestAdvancementOfFullyAdditi (3391)Document13 pagesPun2018 Article LatestAdvancementOfFullyAdditi (3391)tl xNo ratings yet

- Ion Implantation in Silicon TechnologyDocument4 pagesIon Implantation in Silicon TechnologyMehdi NaderiNo ratings yet

- Trends in Semiconductor Devices IndustryDocument6 pagesTrends in Semiconductor Devices IndustryEmanuel NicolaeNo ratings yet

- HV BushingsDocument5 pagesHV BushingssabrahimaNo ratings yet

- Synthesis and Electrochemical Properties of Nanoporous CRN Thin FilmDocument11 pagesSynthesis and Electrochemical Properties of Nanoporous CRN Thin FilmXXX RanceNo ratings yet

- Introduction To IC Fabrication Techniques-1Document5 pagesIntroduction To IC Fabrication Techniques-1gezaegebre1No ratings yet

- Wang - 2019 - IOP - Conf. - Ser. - Mater. - Sci. - Eng. - 612 - 042025Document8 pagesWang - 2019 - IOP - Conf. - Ser. - Mater. - Sci. - Eng. - 612 - 042025Rangga Pratama PutraNo ratings yet

- Se Doc 16131Document13 pagesSe Doc 16131haivikramreddyNo ratings yet

- Published Wjet - 2022092816035603Document10 pagesPublished Wjet - 2022092816035603Michael NgoieNo ratings yet

- LED Chip Manufacturing Process ExplainedDocument5 pagesLED Chip Manufacturing Process ExplainedECEK85A0409No ratings yet

- A Study of VLSI Technology, Wafers and Impact On NanotechnologyDocument3 pagesA Study of VLSI Technology, Wafers and Impact On NanotechnologyNiraj JoshiNo ratings yet

- Nmos and PmosDocument2 pagesNmos and PmosamitgayaNo ratings yet

- Stick DiagramDocument16 pagesStick DiagramamitgayaNo ratings yet

- Nmos and PmosDocument2 pagesNmos and PmosamitgayaNo ratings yet

- Stick DiagramDocument16 pagesStick DiagramamitgayaNo ratings yet

- Stick DiagramDocument16 pagesStick DiagramamitgayaNo ratings yet

- Applying A Drain Voltage To An NMOS DeviceDocument10 pagesApplying A Drain Voltage To An NMOS DeviceamitgayaNo ratings yet

- ANODIZING (Autosaved)Document17 pagesANODIZING (Autosaved)Sonu JajamNo ratings yet

- 20ft T75 Spec 18barDocument6 pages20ft T75 Spec 18barlucholadeNo ratings yet

- Modul 3 Teori Elektron BebasDocument32 pagesModul 3 Teori Elektron BebasRivaldo tumbelakaNo ratings yet

- Module 5: Centrifugal PumpsDocument24 pagesModule 5: Centrifugal PumpsJoy CharlesNo ratings yet

- IAL Physics WPH15-01 January 2021 Question PapersDocument32 pagesIAL Physics WPH15-01 January 2021 Question PapersSnip x Hunt manNo ratings yet

- Water Treatment With Körting Ejectors: Energy-Efficient Solutions - Low Maintenance and Long Service LifeDocument16 pagesWater Treatment With Körting Ejectors: Energy-Efficient Solutions - Low Maintenance and Long Service LifeFREDDDNo ratings yet

- Quikport - ResultsDocument34 pagesQuikport - Resultsjohnsmith1980No ratings yet

- Detailed Explanations For TrendsDocument2 pagesDetailed Explanations For TrendsBRITNEY ALEXANDRA VERMINSHUNo ratings yet

- 1423 Brief Info Components Refrigerant R744 BHS ENDocument3 pages1423 Brief Info Components Refrigerant R744 BHS ENArtur MkrtchyanNo ratings yet

- PWM DFMEA Power Window MotorDocument14 pagesPWM DFMEA Power Window Motoravmr67% (3)

- ANSYS Theory Reference For The Mechanical APDL and Mechanical Applications R13 PDFDocument0 pagesANSYS Theory Reference For The Mechanical APDL and Mechanical Applications R13 PDFfrancisco_gil_510% (1)

- Api 570 PDFDocument2 pagesApi 570 PDFK U Masood Ahmad100% (1)

- Pressure Vessels - DmeDocument47 pagesPressure Vessels - DmeSumitNo ratings yet

- Thermal TorchesDocument610 pagesThermal TorcheszbdjahuNo ratings yet

- Manual de V6A60-BDocument38 pagesManual de V6A60-BLuis Romero100% (1)

- Air Valves For Offshore and Seawater ApplicationsDocument4 pagesAir Valves For Offshore and Seawater ApplicationsSergio MuñozNo ratings yet

- Centrifugal Pump FormulaDocument2 pagesCentrifugal Pump FormulaeduardoNo ratings yet

- Chap2 (B) Fits and TolerancesDocument20 pagesChap2 (B) Fits and TolerancesjojoNo ratings yet

- Phy PPT FinalDocument29 pagesPhy PPT FinalReck OnNo ratings yet

- Design Two-Way Slabs Using Coefficient MethodDocument8 pagesDesign Two-Way Slabs Using Coefficient MethodSL SPNo ratings yet

- Fiitjee: Admission TestDocument3 pagesFiitjee: Admission TestKAPIL SHARMANo ratings yet

- Moles and StoichiometryDocument46 pagesMoles and StoichiometryInspector Chulbul PandayNo ratings yet

- 3D Printed Concrete Applications Performance and ChallengesDocument39 pages3D Printed Concrete Applications Performance and ChallengesDieguiz100% (1)

- Foundrax BRINscopeDocument2 pagesFoundrax BRINscopeSantosh KumarNo ratings yet

- Hydrotest Saddle - 2 Saddle Tail Gas DRMDocument13 pagesHydrotest Saddle - 2 Saddle Tail Gas DRMSu Kil SungNo ratings yet

- DPPS-5 Chemical BondingDocument3 pagesDPPS-5 Chemical BondingshubhamNo ratings yet

- Physical Chemistry I (Gases) : Maxwell and Boltzmann (1859) Developed A MathematicalDocument51 pagesPhysical Chemistry I (Gases) : Maxwell and Boltzmann (1859) Developed A MathematicalDina GaranNo ratings yet

- Physics 1 Code PH-101 Contacts 3+1 Credits 4Document2 pagesPhysics 1 Code PH-101 Contacts 3+1 Credits 4Dr. Pradeep Kumar SharmaNo ratings yet

- Structural data for wet well designDocument328 pagesStructural data for wet well designHarsh BhavsarNo ratings yet

- PDFDocument2 pagesPDFbhavesh patelNo ratings yet

- Periodic Tales: A Cultural History of the Elements, from Arsenic to ZincFrom EverandPeriodic Tales: A Cultural History of the Elements, from Arsenic to ZincRating: 3.5 out of 5 stars3.5/5 (137)

- Is That a Fact?: Frauds, Quacks, and the Real Science of Everyday LifeFrom EverandIs That a Fact?: Frauds, Quacks, and the Real Science of Everyday LifeRating: 4.5 out of 5 stars4.5/5 (3)

- The Disappearing Spoon: And Other True Tales of Madness, Love, and the History of the World from the Periodic Table of the ElementsFrom EverandThe Disappearing Spoon: And Other True Tales of Madness, Love, and the History of the World from the Periodic Table of the ElementsRating: 4 out of 5 stars4/5 (146)

- Organic Chemistry for Schools: Advanced Level and Senior High SchoolFrom EverandOrganic Chemistry for Schools: Advanced Level and Senior High SchoolNo ratings yet

- Guidelines for Asset Integrity ManagementFrom EverandGuidelines for Asset Integrity ManagementRating: 5 out of 5 stars5/5 (1)

- Meltdown: Nuclear disaster and the human cost of going criticalFrom EverandMeltdown: Nuclear disaster and the human cost of going criticalRating: 5 out of 5 stars5/5 (5)

- The Periodic Table of Elements - Post-Transition Metals, Metalloids and Nonmetals | Children's Chemistry BookFrom EverandThe Periodic Table of Elements - Post-Transition Metals, Metalloids and Nonmetals | Children's Chemistry BookNo ratings yet

- Chemistry: a QuickStudy Laminated Reference GuideFrom EverandChemistry: a QuickStudy Laminated Reference GuideRating: 5 out of 5 stars5/5 (1)

- Chemistry at Home - A Collection of Experiments and Formulas for the Chemistry EnthusiastFrom EverandChemistry at Home - A Collection of Experiments and Formulas for the Chemistry EnthusiastNo ratings yet

- Essential Oil Chemistry Formulating Essential Oil Blends that Heal - Aldehyde - Ketone - Lactone: Healing with Essential OilFrom EverandEssential Oil Chemistry Formulating Essential Oil Blends that Heal - Aldehyde - Ketone - Lactone: Healing with Essential OilRating: 5 out of 5 stars5/5 (1)

- Chemistry for Breakfast: The Amazing Science of Everyday LifeFrom EverandChemistry for Breakfast: The Amazing Science of Everyday LifeRating: 4.5 out of 5 stars4.5/5 (14)

- An Introduction to the Periodic Table of Elements : Chemistry Textbook Grade 8 | Children's Chemistry BooksFrom EverandAn Introduction to the Periodic Table of Elements : Chemistry Textbook Grade 8 | Children's Chemistry BooksRating: 5 out of 5 stars5/5 (1)

- Coating and Drying Defects: Troubleshooting Operating ProblemsFrom EverandCoating and Drying Defects: Troubleshooting Operating ProblemsRating: 5 out of 5 stars5/5 (1)

- Science Goes Viral: Captivating Accounts of Science in Everyday LifeFrom EverandScience Goes Viral: Captivating Accounts of Science in Everyday LifeRating: 5 out of 5 stars5/5 (1)

- The Elements We Live By: How Iron Helps Us Breathe, Potassium Lets Us See, and Other Surprising Superpowers of the Periodic TableFrom EverandThe Elements We Live By: How Iron Helps Us Breathe, Potassium Lets Us See, and Other Surprising Superpowers of the Periodic TableRating: 3.5 out of 5 stars3.5/5 (22)

- The Regenerative Grower's Guide to Garden Amendments: Using Locally Sourced Materials to Make Mineral and Biological Extracts and FermentsFrom EverandThe Regenerative Grower's Guide to Garden Amendments: Using Locally Sourced Materials to Make Mineral and Biological Extracts and FermentsRating: 5 out of 5 stars5/5 (3)

- Gas-Liquid And Liquid-Liquid SeparatorsFrom EverandGas-Liquid And Liquid-Liquid SeparatorsRating: 3.5 out of 5 stars3.5/5 (3)

- Monkeys, Myths, and Molecules: Separating Fact from Fiction in the Science of Everyday LifeFrom EverandMonkeys, Myths, and Molecules: Separating Fact from Fiction in the Science of Everyday LifeRating: 4 out of 5 stars4/5 (9)

- Stuff Matters: Exploring the Marvelous Materials That Shape Our Man-Made WorldFrom EverandStuff Matters: Exploring the Marvelous Materials That Shape Our Man-Made WorldRating: 4 out of 5 stars4/5 (289)

- The Periodic Table: A Very Short IntroductionFrom EverandThe Periodic Table: A Very Short IntroductionRating: 4.5 out of 5 stars4.5/5 (3)

- Guidelines for Integrating Process Safety into Engineering ProjectsFrom EverandGuidelines for Integrating Process Safety into Engineering ProjectsNo ratings yet

- Chemical Elements Pocket Guide: Detailed Summary of the Periodic TableFrom EverandChemical Elements Pocket Guide: Detailed Summary of the Periodic TableNo ratings yet