Datasheet

The PrimeTime Static Timing Analysis (STA)

Golden Timing Sign-Off Solution and Environment

Overview

Timing closure in todays advanced designs remains the number one challenge for designers today,

especially at 90-nanometers (nm) and below. A trusted timing sign-off solution that accurately models

and predicts silicon behavior is required to enable designers to quickly achieve timing closure.

The PrimeTime STA Solution

Minimum pulse width checks

The Synopsys PrimeTime static timing analysis solution is the

Maximum fanout and capacitance checks

most trusted and advanced timing sign-off solution for gate-level

User-defined maximum and minimum delay checks

designs. It is the industrys de-facto gold standard for gate-level

Input/output delay, input transition, port driving cell, output

static timing analysis and is a key component of the Galaxy

Design Platform.

load support

Multi-clock support

Multi-cycle and false path exception support

With a wide breadth of sign-off analysis capabilities, the

Transparent latch and time borrowing support

PrimeTime STA solution provides a comprehensive and

Generated or derived clock support

unmatched environment for timing sign-off and serves as an

Clock latency, clock skew, clock uncertainty support

industry yardstick for timing analysis and sign-off. It delivers to

Pulse clock support

designers extensive timing analysis checks, advanced analysis

Case analysis

techniques, golden delay calculator, advanced modeling,

Mode analysis

unmatched productivity and ease of use, a graphical user

Analysis coverage report of timing checks

interface, and industry-wide ASIC vendor sign-off and foundry

Parasitic or SDF delay annotations

support.

User-defined delay and transition annotations

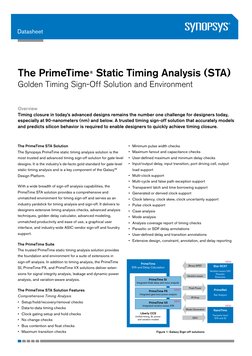

The PrimeTime Suite

Extensive design, constraint, annotation, and delay reporting

The trusted PrimeTime static timing analysis solution provides

the foundation and environment for a suite of extensions in

sign-off analysis. In addition to timing analysis, the PrimeTime

SI, PrimeTime PX, and PrimeTime VX solutions deliver exten-

NEW

PrimeTime

STA and Delay Calculation

sions for signal integrity analysis, leakage and dynamic power

analysis, and variation-aware analysis.

The PrimeTime STA Solution Features

Comprehensive Timing Analysis

Setup/hold/recovery/removal checks

Data-to-data timing checks

Clock gating setup and hold checks

No change checks

Binary SPEF

Star-RCXT

Variation-aware

Variation-aware (VX)

Parasitic

Extraction

PrimeTime SI

Integrated Xtalk delay and noise analysis

PrimeTime PX

NEW

Peak Power

Integrated gate-level power analysis

IR Drop

PrimeTime VX

NEW

NEW

Integrated variation-aware STA

Model Generation

NanoTime

SDC

Transistor-level

STA and SI

Liberty CCS

Unified timing, SI, power

and variation models

Bus contention and float checks

Maximum transition checks

PrimeRail

Rail Analysis

Figure 1: Galaxy Sign-off solutions

�PrimeTime

PrimeTime

STA and Delay Calculation

PrimeTime SI

Xtalk delay and noise analysis

PrimeTime PX

Gate-level power analysis

PrimeTime VX

Variation-aware STA

CCS

Unified timing, SI, power,

and variation models

Figure 2: PrimeTime suite

Advanced Analysis Techniques

CCS and NLDM Liberty library support

On-chip-variation (OCV) analysis

SDF output and custom SDF mapping

Clock reconvergence pessimism removal

SPICE deck output

Multiple clocks per register

Worst-arrival slew propagation

Automatic false path detection

Multi-voltage support

Dynamic feedback loop breaking

Instance-specific rail voltages

Worst arrival slew propagation

Global and net-specific parasitic scaling

Path-specific recalculation and analysis

Voltage scaling between libraries

Bottleneck analysis

Temperature scaling between libraries

What-if ECO analysis

Library-specific delay and slew and thresholds

ECO netlist editing

Pin-specific delay and slew thresholds

Global and instance-specific timing derating

Extensive delay calculation and parasitic annotation reporting

Global and net-specific timing derating

Instance location (x,y) coordinates from SPEF

Advanced Modeling

Exclusive and asynchronous clock groups

Interface Logic Models (ILM) for hierarchical static timing

Timing exception optimization

User-defined operation conditions (PVT)

PrimeTime SI for signal integrity analysis

analysis and sign-off

Extracted Timing Models (ETM) in .lib format for cell-based

reusable IP and physical design flows

PrimeTime PX for dynamic and leakage power analysis

Quick Timing Models (QTM) for top-down design

PrimeTime VX for variation-aware analysis

Automatic model validation

ETM debugging

Golden Delay Calculator

ETM model merging

Built-in RC delay calculation uses parasitics information for

Hierarchical block scope analysis

accurate interconnect analysis

SPEF, DSPF, and RSPF file format support

SBPF (Synopsys Binary Parasitic Format) support

�PrimeTime

Productivity and Ease of Use

ASIC vendor sign-off and foundry support

64-bit architecture for full-chip timing analysis of

Agere

100-million gates

Fujitsu

Incremental timing engine

LSI Logic

Save and restore

NEC

Distributed multi-scenario analysis with intelligent

Renesas

merged reporting

Samsung

What-if ECO analysis

STMicroelectronics

Exception and constraint analysis for debugging

Texas Instruments

Tcl shell with command line editing

Toshiba

Tcl support (collections, scripting, etc.)

TSMC

Direct reading and writing of gzip compressed files

UMC

Extensive reporting options

Chartered Semiconductor Manufacturing

Extensive built-in attributes for custom scripting and reporting

IBM Foundry

User-defined attributes

SMIC

Graphical User Interface

Input/Output Formats

Timing analysis and design visualization using schematics,

Netlists: Verilog, VHDL, Synopsys DDC format

histograms, tables, and tree graphs

Constraints: PrimeTime constraints, SDC

Full hierarchical schematic

Parasitics and Delay: SPEF, DSPF, RSPF, SBPF, SDF

Timing path schematic, table, and profiler

Libraries: CCS and NLDM in Synopsys db format

Clock network schematic and table

Clock domain interaction matrix table

Timing bottleneck identification and visualization

Path recalculation table

Design attribute table

Slack and design data histograms

Customizable histograms

Start-up from Tcl shell

Synopsys, Inc.

700 East Middlefield Road

Mountain View, CA 94043

www.synopsys.com

2007 Synopsys, Inc. Synopsys, the Synopsys logo and PrimeTime are registered trademarks and Galaxy is a trademarks of Synopsys, Inc. All other products or service names mentioned

herein are trademarks of their respective holders and should be treated as such. Printed in the U.S.A. 01/07.KF.07-15189.WO