Professional Documents

Culture Documents

D Driven by Another Stage Q Will Not Change Any Faster Than 200ns For The CD4006b

Uploaded by

pqwertyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

D Driven by Another Stage Q Will Not Change Any Faster Than 200ns For The CD4006b

Uploaded by

pqwertyCopyright:

Available Formats

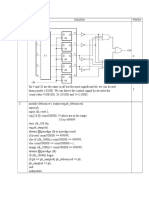

The following data was extracted from the CD4006b data sheet for operation at 5VDC,

which serves as an example to illustrate timing.

[*]

tS=100ns

tH=60ns

tP=200-400ns typ/max

tS is the setup time, the time data must be present before clock time. In this case data must

be present at D 100ns prior to the clock. Furthermore, the data must be held for hold time

tH=60ns after clock time. These two conditions must be met to reliably clock data from D

to Q of the Flip-Flop.

There is no problem meeting the setup time of 60ns as the data at D has been there for the

whole previous clock period if it comes from another shift register stage. For example, at

a clock frequency of 1 Mhz, the clock period is 1000 s, plenty of time. Data will

actually be present for 1000s prior to the clock, which is much greater than the

minimum required tS of 60ns.

The hold time tH=60ns is met because D connected to Q of another stage cannot change

any faster than the propagation delay of the previous stage tP=200ns. Hold time is met as

long as the propagation delay of the previous D FF is greater than the hold time. Data at

D driven by another stage Q will not change any faster than 200ns for the CD4006b.

To summarize, output Q follows input D at nearly clock time if Flip-Flops are cascaded

into a multi-stage shift register.

You might also like

- Navigation & Voyage Planning Companions: Navigation, Nautical Calculation & Passage Planning CompanionsFrom EverandNavigation & Voyage Planning Companions: Navigation, Nautical Calculation & Passage Planning CompanionsNo ratings yet

- Negative and Positive Clock SkewDocument27 pagesNegative and Positive Clock SkewSupriya AggarwalNo ratings yet

- Significance of Contamination Delay: Nima Afraz Advisor: DR - Jahanian For The Advanced VLSI CourseDocument7 pagesSignificance of Contamination Delay: Nima Afraz Advisor: DR - Jahanian For The Advanced VLSI CourseNima AfrazNo ratings yet

- Numerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityFrom EverandNumerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityNo ratings yet

- Setup and Hold - PDF Version 1Document15 pagesSetup and Hold - PDF Version 1naniNo ratings yet

- Understanding Sequential Circuit TimingDocument8 pagesUnderstanding Sequential Circuit Timingchuku7No ratings yet

- Sequential & Combinational Timing AnalysisDocument8 pagesSequential & Combinational Timing AnalysisSahil SharmaNo ratings yet

- What Is Setup and Hold Time?Document12 pagesWhat Is Setup and Hold Time?Minu MathewNo ratings yet

- Lagranto TutorialDocument17 pagesLagranto Tutorialrohaniarman99No ratings yet

- Assignment 1: Sourav Sarkar February 1, 2017Document12 pagesAssignment 1: Sourav Sarkar February 1, 2017Sourav SarkarNo ratings yet

- Race Hazards, Clock Skew, Cross Simulation & Intra-Assignment DelaysDocument4 pagesRace Hazards, Clock Skew, Cross Simulation & Intra-Assignment Delaysश्रेयस देशमुखNo ratings yet

- Sequential Logic and Memory ComponentsDocument9 pagesSequential Logic and Memory ComponentsShashank MishraNo ratings yet

- TimingDocument15 pagesTimingSameer BadachiNo ratings yet

- Setup and Hold TimeDocument6 pagesSetup and Hold TimeShobhit GargNo ratings yet

- Hiểu Về Khái Niệm POIDocument6 pagesHiểu Về Khái Niệm POIDoan HoaNo ratings yet

- Timing Analysis: Supplementary NotesDocument6 pagesTiming Analysis: Supplementary NotesSRINIKHIL GollaNo ratings yet

- Setup & Hold ViolationDocument20 pagesSetup & Hold ViolationdeepaNo ratings yet

- Static Timing Analysis in VLSI CircuitsDocument16 pagesStatic Timing Analysis in VLSI CircuitseeshgargNo ratings yet

- Timing Issues: by Deepa .BDocument21 pagesTiming Issues: by Deepa .BdeepaNo ratings yet

- Hydraulic Analysis Versus Piping Stress Analysis ApproachDocument1 pageHydraulic Analysis Versus Piping Stress Analysis Approachalan172081100% (1)

- Set Hold BasicsDocument17 pagesSet Hold BasicsMelissa AdamsNo ratings yet

- Consider N Processes Sharing The CPU in A Round-RobinDocument2 pagesConsider N Processes Sharing The CPU in A Round-RobinCSnotesNo ratings yet

- Dap An Nwc203c Fall 2022 UpdateDocument27 pagesDap An Nwc203c Fall 2022 Updatethienlpce181788No ratings yet

- HW2 SolutionDocument5 pagesHW2 Solutionblackbat35No ratings yet

- Set Up DelayDocument15 pagesSet Up DelayNathan BrooksNo ratings yet

- Pe 1Document27 pagesPe 1tín nguyễnNo ratings yet

- Contadores STEP7Document14 pagesContadores STEP7Rodrigo SudarioNo ratings yet

- Tele Traffic LectureDocument18 pagesTele Traffic LectureDramane BonkoungouNo ratings yet

- NWC203c NewDocument49 pagesNWC203c NewHa Gia Khanh (K17 HCM)No ratings yet

- NWC203c NewDocument26 pagesNWC203c NewDương Gia BìnhNo ratings yet

- A BAW Based Transceiver Used As Wake-Up Receiver: T T T T TDocument6 pagesA BAW Based Transceiver Used As Wake-Up Receiver: T T T T TKhaled AggourNo ratings yet

- Q.No Solution Marks 1Document4 pagesQ.No Solution Marks 1avinash_yuvarajNo ratings yet

- Keeping The Clock Pure: Review of Timing Properties of Flip-FlopsDocument32 pagesKeeping The Clock Pure: Review of Timing Properties of Flip-FlopsShwetabhAsthanaNo ratings yet

- STI - FSM - SolutionsDocument6 pagesSTI - FSM - SolutionsAishwarya GajendrulaNo ratings yet

- Time and Standard Frequency Station DCF77Document7 pagesTime and Standard Frequency Station DCF77irfankhanoml7No ratings yet

- NWC SolutionDocument22 pagesNWC SolutionThái ĐoànNo ratings yet

- Solution: 4 ScannersDocument3 pagesSolution: 4 ScannersArnab PalNo ratings yet

- Source Synchronous Interface Timing ClosureDocument5 pagesSource Synchronous Interface Timing ClosureaanbalanNo ratings yet

- PAGE10Document4 pagesPAGE10praveenmorampudi42No ratings yet

- 0 Encoding 1 0 1 0 1 1 1: Indian Institute of Information Technology Design and Manufacturing, KancheepuramDocument6 pages0 Encoding 1 0 1 0 1 1 1: Indian Institute of Information Technology Design and Manufacturing, KancheepuramDark SlayerNo ratings yet

- NWC Solu (Uutien)Document20 pagesNWC Solu (Uutien)Hoàng PhạmNo ratings yet

- Adaptive-Reliable Medium Access Control Protocol For Wireless Body Area NetworksDocument3 pagesAdaptive-Reliable Medium Access Control Protocol For Wireless Body Area NetworksMadigani PrasannakumarNo ratings yet

- Distance Relay SettingDocument2 pagesDistance Relay SettingbillymcrealNo ratings yet

- Pico Second Labs PDFDocument5 pagesPico Second Labs PDFVenkatesh KarriNo ratings yet

- Static Timing AnalysisDocument32 pagesStatic Timing AnalysisShantanu Sarkar100% (1)

- Digital Control Systems Unit IDocument18 pagesDigital Control Systems Unit Iyanith kumarNo ratings yet

- Setup HoldDocument22 pagesSetup HoldAnuja BagdiNo ratings yet

- Decoding Upper Air DataDocument13 pagesDecoding Upper Air DataSenior Manager Meteorology HAL NASIKNo ratings yet

- ScriptDocument5 pagesScriptGhiffar Hidathe JirhochosenseiNo ratings yet

- Pulse Modulation: Analog-To-Digital ConversionDocument4 pagesPulse Modulation: Analog-To-Digital ConversionskarthikmtechNo ratings yet

- Timers and Counters For Radio Resource ManagementDocument5 pagesTimers and Counters For Radio Resource ManagementAmit Singh TomarNo ratings yet

- Quiz SolutionDocument9 pagesQuiz SolutionelectrolicsNo ratings yet

- GSM TimerDocument11 pagesGSM TimerSana KhanNo ratings yet

- Setup1 1210Document32 pagesSetup1 1210Akhila PurushothamanNo ratings yet

- SI7b TimingDocument14 pagesSI7b Timingkulkarn7No ratings yet

- Lecture-2 I&PCDocument16 pagesLecture-2 I&PCisrarahmed1103No ratings yet

- Ambika Cotton Mills LTD VisionDocument4 pagesAmbika Cotton Mills LTD VisionpqwertyNo ratings yet

- S34ml01g200tfi000 PDFDocument71 pagesS34ml01g200tfi000 PDFpqwertyNo ratings yet

- Embedded System DesignDocument17 pagesEmbedded System DesignpqwertyNo ratings yet

- Embedded System DesignDocument1 pageEmbedded System DesignpqwertyNo ratings yet

- Munnar ItineraryDocument2 pagesMunnar ItinerarypqwertyNo ratings yet

- ValueResearchFundcard MiraeAssetTaxSaverFund DirectPlan 2019mar08Document4 pagesValueResearchFundcard MiraeAssetTaxSaverFund DirectPlan 2019mar08pqwertyNo ratings yet

- Emotional Intelligence - Cognitive Behavioural Therapy - How To Sell YourselfDocument43 pagesEmotional Intelligence - Cognitive Behavioural Therapy - How To Sell Yourselfpqwerty50% (2)

- 7851.PCIe Designguides PDFDocument32 pages7851.PCIe Designguides PDFpqwertyNo ratings yet

- Planning and Goal-Setting - It Is The People Around You Who Are Going To Contribute To Your Success or Failure. - Begin With The End in The MindDocument1 pagePlanning and Goal-Setting - It Is The People Around You Who Are Going To Contribute To Your Success or Failure. - Begin With The End in The MindpqwertyNo ratings yet

- Good ThoughtsDocument1 pageGood ThoughtspqwertyNo ratings yet

- 30 Challenges For 30 Days of GrowthDocument5 pages30 Challenges For 30 Days of GrowthpqwertyNo ratings yet

- Power of Habit: The Ultimate Guide to Forming Positive Daily Habits, Learn How to Effectively Break Your Bad Habits For Good and Start Creating Good OnesFrom EverandPower of Habit: The Ultimate Guide to Forming Positive Daily Habits, Learn How to Effectively Break Your Bad Habits For Good and Start Creating Good OnesRating: 4.5 out of 5 stars4.5/5 (21)

- The Complete HVAC BIBLE for Beginners: The Most Practical & Updated Guide to Heating, Ventilation, and Air Conditioning Systems | Installation, Troubleshooting and Repair | Residential & CommercialFrom EverandThe Complete HVAC BIBLE for Beginners: The Most Practical & Updated Guide to Heating, Ventilation, and Air Conditioning Systems | Installation, Troubleshooting and Repair | Residential & CommercialNo ratings yet

- Electric Motor Control: DC, AC, and BLDC MotorsFrom EverandElectric Motor Control: DC, AC, and BLDC MotorsRating: 4.5 out of 5 stars4.5/5 (19)

- Shorting the Grid: The Hidden Fragility of Our Electric GridFrom EverandShorting the Grid: The Hidden Fragility of Our Electric GridRating: 4.5 out of 5 stars4.5/5 (2)

- Well Integrity for Workovers and RecompletionsFrom EverandWell Integrity for Workovers and RecompletionsRating: 5 out of 5 stars5/5 (3)

- Well Control for Completions and InterventionsFrom EverandWell Control for Completions and InterventionsRating: 4 out of 5 stars4/5 (10)

- Building Energy Management Systems and Techniques: Principles, Methods, and ModellingFrom EverandBuilding Energy Management Systems and Techniques: Principles, Methods, and ModellingNo ratings yet

- The Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidenceFrom EverandThe Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidenceNo ratings yet

- Air Cooled Heat Exchanger Handbook: Fundamentals, Calculations, Design and Q&AFrom EverandAir Cooled Heat Exchanger Handbook: Fundamentals, Calculations, Design and Q&ANo ratings yet

- Handbook on Battery Energy Storage SystemFrom EverandHandbook on Battery Energy Storage SystemRating: 4.5 out of 5 stars4.5/5 (2)

- Renewable Energy: Physics, Engineering, Environmental Impacts, Economics and PlanningFrom EverandRenewable Energy: Physics, Engineering, Environmental Impacts, Economics and PlanningRating: 5 out of 5 stars5/5 (4)

- Renewable Energy Finance: Theory and PracticeFrom EverandRenewable Energy Finance: Theory and PracticeRating: 4 out of 5 stars4/5 (1)

- Introduction to Power System ProtectionFrom EverandIntroduction to Power System ProtectionRating: 5 out of 5 stars5/5 (1)

- Nigerian Public Discourse: The Interplay of Empirical Evidence and HyperboleFrom EverandNigerian Public Discourse: The Interplay of Empirical Evidence and HyperboleNo ratings yet

- Thermal Power Plant: Design and OperationFrom EverandThermal Power Plant: Design and OperationRating: 4.5 out of 5 stars4.5/5 (23)

- Electric Motors and Drives: Fundamentals, Types and ApplicationsFrom EverandElectric Motors and Drives: Fundamentals, Types and ApplicationsRating: 4.5 out of 5 stars4.5/5 (12)

- Asset Integrity Management for Offshore and Onshore StructuresFrom EverandAsset Integrity Management for Offshore and Onshore StructuresNo ratings yet

- The Truth About Solar Panels The Book That Solar Manufacturers, Vendors, Installers And DIY Scammers Don't Want You To ReadFrom EverandThe Truth About Solar Panels The Book That Solar Manufacturers, Vendors, Installers And DIY Scammers Don't Want You To ReadRating: 4.5 out of 5 stars4.5/5 (10)

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet