Baker Ch.

20 Current Mirrors Introduction to VLSI

Chapter 20

Current Mirrors

Basics

Long Channel

Matching

Biasing

Short Channel

Temperature

Subthreshold

Cascoding

Simple

Low Voltage, Wide Swing

Wide Swing, Short Channel

Regulated Drain

Biasing Circuits

Long Channel Biasing

Short Channel Biasing

Joseph A. Elias, Ph.D. Adjunct Professor, University of Kentucky; Modeling Principal, Cypress Semiconductor 1

� Baker Ch. 20 Current Mirrors Introduction to VLSI

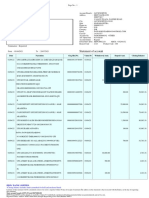

Current Mirrors - Basics LONG CHANNEL DERIVATION

IDEAL OUTPUT RESISTANCE=OO

OUTPUT CURRENT INDEPENDENT

OF VOLTAGE ACROSS SOURCE

Ids1 Ids2

ASSUME M1, M2 SAME W, L

D1 SHORTED TO G1

VGS1=VDS1=VGS2

Vgs1 Vgs2

DUE TO SAME Vgs, SAME Ids

IF RES EQUAL, M2 VD=M1 VD

THEREFORE: VGS1=VDS1=VGS2 =VDS2

CURRENT IN M1:

IREF = ID1 = (KPN/2) (W1/L1) (VGS1-Vtn)2

KNOWN:

VGS1= VGS2

VDS1,SAT = VGS1-Vtn (WHERE VDG=Vtn)

CURRENT IN M2:

IO = ID2 = (KPN/2) (W2/L2) (VGS1-Vtn)2

MARTIN RATIO OF THE CURRENTS:

IO / IREF = (W2/L2) / (W1/L1)

IF L1=L2, THEN:

IO / IREF = W2 / W1

Joseph A. Elias, Ph.D. Adjunct Professor, University of Kentucky; Modeling Principal, Cypress Semiconductor 2

� Baker Ch. 20 Current Mirrors Introduction to VLSI

Current Mirrors - Basics LONG CHANNEL DERIVATION

IO / IREF = W2 / W1

SCALE W TO GET VARIOUS IO

WHAT IS THE RESISTOR VALUE?

FOR IREF=20uA,

IREF=(VDD-VGS1)/R R=(5-1.05)/20uA

R=200k OHMS

HOW IS VGS1=1.05 FOUND?

SWEEP VO TO FIND WHERE IREF=IO

SOLVE THE EQUATION:

IREF = ID1 = (KPN/2) (W1/L1) (VGS1-Vtn)2

KNOW IREF, KP, W, L, Vt

WHY DOES IO DROP BELOW 250mV?

CURRENT SOURCE RANGE:

VDS,SAT < VO < VDD

IMPORTANT IDEAS:

IO = IREF WHEN VO=VDS1=VGS1

IREF , VGS1 NOT DEPENDENT ON VO

Joseph A. Elias, Ph.D. Adjunct Professor, University of Kentucky; Modeling Principal, Cypress Semiconductor 3

� Baker Ch. 20 Current Mirrors Introduction to VLSI

PROCESS CAUSE

Current Mirrors - Basics

FIRST-ORDER PROCESS ISSUES:

GATE OXIDE THICKNESS

LATERAL DIFFUSION

OXIDE ENCROACHMENT

OXIDE CHARGE DENSITY

THRESHOLD MISMATCH

MISMATCH IN Vt LEADS TO:

IO/IREF ~

REDUCED 1 [2 Vt / (VGS-Vt) ] =

RESISTANCE

1 [2 Vt / (VDS,SAT) ]

WANT LARGE VGS

REDUCES MISMATCH

TRANSCONDUCTANCE MISMATCH

MISMATCH IN KP LEADS TO:

IO/IREF ~ 1 + [KPN / KPN ]

WANT LARGE AREA, KP INCR

VDS MISMATCH

ETCHED MORE IO/IREF ~

ON OUTER POLY

[1 + 2VO] / [1+ 1VDS1]

CAP REDUCED BY (n+1)/2n

VDS VARIES W/ RESISTANCE

DO NOT USE SHORT CHANNEL

Joseph A. Elias, Ph.D. Adjunct Professor, University of Kentucky; Modeling Principal, Cypress Semiconductor 4

� Baker Ch. 20 Current Mirrors Introduction to VLSI

Current Mirrors - Basics LAYOUT CONSIDERATIONS

DO NOT CHANGE ORIENTATION

IMPLANTS ARE ORIENTED

INTERDIGITIZE FINGERS

AVERAGES PROCESS VARIATIONS

COMMON

GATE DIFFERING WIDTHS ISSUES

LATERAL DIFFUSION LDIFF

OXIDE ENCROACHMENT WENC

IO/IREF =

(W2,DRAWN-2WENC)(L1,DRAWN-2LDIFF) /

(W1,DRAWN-2WENC)(L2,DRAWN-2LDIFF)

FIX L1=L2 , MINIMIZE MISMATCH

WIDTHS DETERMINE OFFSET

BUILT IN MISMATCH

USE FOLDING

TO REDUCE

MISMATCH

Joseph A. Elias, Ph.D. Adjunct Professor, University of Kentucky; Modeling Principal, Cypress Semiconductor 5

� Baker Ch. 20 Current Mirrors Introduction to VLSI

Current Mirrors - Basics BIASING

DO NOT WANT TO USE RES

VARIES WITH TEMPERATURE

WANT IREF VDD-INDEPENDENT

REPLACE RES WITH XTOR

USE EITHER M1 OR M3

WANT VDS IND OF VDD, GND

EXAMPLE CHANGE VS. VDD:

IO ~ 8nA / mV

IREF (XTOR) ~ 12nA / mV

IREF (RES) ~ 5nA / mV

USING MODELS

FROM BOOK

Joseph A. Elias, Ph.D. Adjunct Professor, University of Kentucky; Modeling Principal, Cypress Semiconductor 6

� Baker Ch. 20 Current Mirrors Introduction to VLSI

Current Mirrors - Basics SUPPLY INDEPENDENT BIAS

WANT IREF VDD-INDEPENDENT

LAST EXAMPLES 5-12nA/mV

MOVE RESISTOR FROM DS

DRAWBACK: VGS2!=VGS5

ADD M1 CAN USE M1 AS DIODE

DIODE MIRROR M1 CURRENT TO M5

NEED M2=M1 CURRENT

ADD PMOS CURRENT MIRROR

DERIVE IREF AS A FNCT OF VDD

MOVE RES VGS1=VGS2+(IREF)(R)

TO SOURCE

MAKES SENSE IF VGS1>VGS2

DONE BY MAKING W2>W1

ADD PMOS

RESULT:

CURRENT

MIRROR IREF= [ 2 / (R2KPNW1L1) ] [ 1-(1/(K)1/2) ]2

IREF INDEPENDENT OF VDD

CONSTANT-GM BIAS CIRCUIT

K=4, EVALUATE EQUATION

gm=[ 2KPN(W/L) IREF ]1/2 = 1/R

Joseph A. Elias, Ph.D. Adjunct Professor, University of Kentucky; Modeling Principal, Cypress Semiconductor 7

� Baker Ch. 20 Current Mirrors Introduction to VLSI

BIASING-USING STARTUP

Current Mirrors - Basics

VDD<VG<VDD-Vtp UNWANTED STATE

NMOS SWITCH

M1, M2 GATES AT GND

M3, M4 GATES AT VDD

1

NO CURRENT FLOWS

NEED STARTUP

0 0

X IN THE ZERO-CURRENT STATE

PARASITIC MSU1 VG=0

CAP

MSU2 VG>=VDD-Vtp

MSU3 TURNS ON

VDD @ M3/4 M1/2

M1/2 RISE, CIRCUIT WORKS

MSU3 GATE GOES TO GND

POSITIVE FEEDBACK ISSUES

STABLE IF GAIN < 1

RESISTOR SMALL, GAIN>1

M2 PARASITIC CAP, R0

CIRCUIT WILL OSCILLATE

RESULTS

VDDMIN=VDS3,SAT+VGS1~1.3V

IREF / VDD ~ 800pA / mV

COMPARE TO 5-12nA / mV

Joseph A. Elias, Ph.D. Adjunct Professor, University of Kentucky; Modeling Principal, Cypress Semiconductor 8