Professional Documents

Culture Documents

Birla Institute of Technology & Science, Pilani Hyderabad Campus Second Semester 2018-2019 Course Handout (Part-II) 07-01-2019

Uploaded by

Pri0 ratings0% found this document useful (0 votes)

18 views3 pagesHandout

Original Title

Microprocessors

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentHandout

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

18 views3 pagesBirla Institute of Technology & Science, Pilani Hyderabad Campus Second Semester 2018-2019 Course Handout (Part-II) 07-01-2019

Uploaded by

PriHandout

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 3

Birla Institute of Technology & Science, Pilani

Hyderabad Campus

Second Semester 2018-2019

Course Handout (Part-II)

07-01-2019

In addition to Part I (General Handout for all courses appended to the Time Table), this

portion gives further specific details regarding the course.

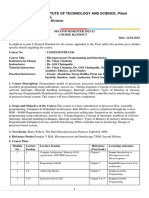

Course No. : CS/ECE/EEE/INSTR F241

Course Title : Microprocessor Programming & Interfacing

Instructor-in-charge : Soumya J

Team of Instructors : Suvadip batabyal, Syed Ershad Ahmed, Karumbaiah C Nanaiah,

Manish Narwaria, Ramakant, Sandeep Kumar, Anil Kumar U, G

Jayeshkumar Pintubhai, Pavankumar Reddy B, Pranjali

Gajbhiye, Samala Jagadheesh, Sanjay Vidhyadharan, Swapna

Challagundla

Course Description : 8086 - 80486 Programmers model, processor architecture; Instruction

set, modular assembly programming using subroutines, macros etc.; Timing diagrams ;

Concept of interrupts: hardware & software interrupts, Interrupt handling techniques,

Interrupt controllers; Types of Memory & memory interfacing; Programmable Peripheral

devices and I/O Interfacing ; DMA controller and its interfacing: Design of processor based

system.

Text Book:

T1: Barry B Brey, The Intel Microprocessors .Pearson, Eight Ed. 2009.

Reference book:

R1: Douglas V Hall, Microprocessor and Interfacing, TMH, Second Edition.

R2. Lyla B Das, The x86 Microprocessors: 8086 to Pentium, Multicores, Atom and the 8051

Microcontroller: Architecture, Programming and Interfacing, Second Edition

R3: 8086 family User Manual, Intel Corporation

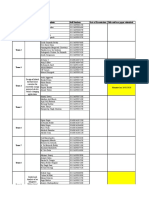

Detailed Course Plan:

Lect. Learning Objectives Topics to be covered Reference to Text

No.

1. Introduction to Compute Architecture, Chapter 1 (T1), Chapter 1 (R1)

Microprocessor and Memory & I/O organization,

Microcomputers CISC/RISC processors

2-3 Microprocessor & its 8086 Microprocessor Chapter 2 (T1), Chapter 2

architecture (R1)

4-6 Assembly Addressing Modes Chapter 3 (T1)

Programming

7-12 Assembly Instruction Set & ALP Chapter 4-6, 8 (T1)

Programming

13-15 8086/8088 Hardware Pin Out, Modes of operation, Chapter 9 (T1)

Specifications Clocking, Buses

16-19 Memory Interface Memory Devices, Address Chapter -10 (T1)

Decoding- Memory

Interface

20-23 I/O Interfacing Basic I/O interfacing (I/O 11.1, 11.2 (T1)

mapped I/O and Memory

mapped I/O)

I/O port address decoding

24-26 Interrupts Types of interrupts, Vector 12.1, 12.2, (T1)

tables, Priority Schemes

27-29 Programmable 8255,8254,ADC,DAC, 8259 11.3-11.6 & 12.3 -12.6 (T1)

Peripheral Devices

30-31 DMA controller Basic Operation, 8237, Chapter -13 (T1)

Shared Bus, Disk Memory

Systems, Video Displays

32-33 Bus Interface ISA, PCI, Com, USB,AGP Chapter 15 (T1)

34-36 Advanced Processors 80186-80286 Chapter 16 (T1), Chapter 15

(R1)

37-39 Advanced Processors 80386-80486 Chapter 17 (T1), Chapter 15

(R1)

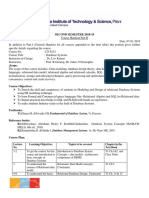

Evaluation Scheme:

Weightage (%) Nature of

Component Duration Date & Time

and Marks Component

1 ½ Hour 11/3 Closed Book

Midsem Test 25% (75) 11.00 -12.30 PM

---- Will be announced Closed Book

Quizzes (3) 15% (45)

Demo/Practicals/

Day to Day

2hrs/week 10% (30) Evaluation

(Open Book)

LAB component

LAB Exam 10% (30) Will be announced Closed Book

Closed+Open

Comprehensive Exam 3 Hours 01/05 AN

20% +20%(120) Book

TOTAL 100% (300)

Make-up Policy: There will no make-ups unless for genuine reasons. Prior Permission of the Instructor-in-

Charge is required to take a make-up for any component. A make-up test shall be granted only in genuine cases

as per institute guidelines.

NO make-up is allowed for quizzes.

Chamber Consultation Hour: Will be announced in the class.

Notices: Notices concerning to this course will be on CMS.

Academic Honesty and Integrity Policy: Academic honesty and integrity are to be

maintained by all the students throughout the semester and no type of academic dishonesty is

acceptable.

Dr. Soumya J

Instructor-in-charge

(CS/EEE/ECE/INSTR F241)

You might also like

- English Conversation Examples For 60 DaysDocument20 pagesEnglish Conversation Examples For 60 DaysKarunamoorthy Periasamy100% (1)

- CSS10 Week6Document16 pagesCSS10 Week6Jevan Hope BaltazarNo ratings yet

- Manual de Servicio Cama AdvanceDocument698 pagesManual de Servicio Cama AdvanceAbner MorenoNo ratings yet

- Métodos numéricos aplicados a Ingeniería: Casos de estudio usando MATLABFrom EverandMétodos numéricos aplicados a Ingeniería: Casos de estudio usando MATLABRating: 5 out of 5 stars5/5 (1)

- Ece F215 Digital Design - HandoutDocument3 pagesEce F215 Digital Design - HandoutRishiNo ratings yet

- BITS Course Handout: Introduction to MEMSDocument5 pagesBITS Course Handout: Introduction to MEMSParth SoodanNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document3 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Deepti MishraNo ratings yet

- CHHATTISGARH SWAMI VIVEKANAND TECHNICAL UNIVERSITY, BHILAI DIPLOMA PROGRAMME IN INFORMATION TECHNOLOGYDocument20 pagesCHHATTISGARH SWAMI VIVEKANAND TECHNICAL UNIVERSITY, BHILAI DIPLOMA PROGRAMME IN INFORMATION TECHNOLOGYshriram1082883No ratings yet

- 18EC2028 Teaching Plan in FormatDocument5 pages18EC2028 Teaching Plan in FormatMerin JohnNo ratings yet

- Chhattisgarh Swami Vivekanand Technical University, BhilaiDocument22 pagesChhattisgarh Swami Vivekanand Technical University, Bhilaibheshram janghelNo ratings yet

- Syllabus V Sem CS DipDocument25 pagesSyllabus V Sem CS DipSK BeharNo ratings yet

- Department Electronics Communication Course PlanDocument4 pagesDepartment Electronics Communication Course PlansarvanmeNo ratings yet

- Individual Report Evaluation Form: No Name Student ID Group No Remark 1Document3 pagesIndividual Report Evaluation Form: No Name Student ID Group No Remark 1firdausNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document4 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24f20220264No ratings yet

- RTS SyllabusDocument3 pagesRTS SyllabusthejasNo ratings yet

- New SyllabusDocument5 pagesNew SyllabusAmit KumarNo ratings yet

- SyllabusDocument3 pagesSyllabusTHAI XIN PING ROSEMONDNo ratings yet

- National Institute of Technology, RaipurDocument11 pagesNational Institute of Technology, RaipurAjeet KumarNo ratings yet

- First Semester 2022-2023Document4 pagesFirst Semester 2022-2023PPNo ratings yet

- Faculty Group Report Evaluation Form for Welding/Metrology LabDocument3 pagesFaculty Group Report Evaluation Form for Welding/Metrology LabIzzam HarithNo ratings yet

- Lab Report Evaluation Form Mem564 (Session 4)Document3 pagesLab Report Evaluation Form Mem564 (Session 4)Fadhli HashimNo ratings yet

- Format For Course Curriculum: Course Level: UG Course ObjectivesDocument4 pagesFormat For Course Curriculum: Course Level: UG Course ObjectivesabcdNo ratings yet

- Birla Institute of Technology and Science, Pilani: Pilani Campus AUGS/ AGSR DivisionDocument2 pagesBirla Institute of Technology and Science, Pilani: Pilani Campus AUGS/ AGSR DivisionADITYA MATHURNo ratings yet

- Government Polytechnic, Nagpur. Course Curriculum: Teaching SchemeDocument41 pagesGovernment Polytechnic, Nagpur. Course Curriculum: Teaching SchemeAkhilesh PandeNo ratings yet

- Module Descriptor NWC304-Industrial Data NetworkDocument4 pagesModule Descriptor NWC304-Industrial Data NetworkShankar Raj GiriNo ratings yet

- Mumbai University SyllabusDocument30 pagesMumbai University SyllabusjcijosNo ratings yet

- BITS Pilani Microprocessor Programming Course DetailsDocument3 pagesBITS Pilani Microprocessor Programming Course DetailsASHLESHA KUMARNo ratings yet

- BITS Pilani Microprocessor Programming Course DetailsDocument3 pagesBITS Pilani Microprocessor Programming Course DetailsASHLESHA KUMARNo ratings yet

- PEC-MIRA101B - Embedded System Application For Robotics - M.Tech RA - 2023-25 - MLPDocument5 pagesPEC-MIRA101B - Embedded System Application For Robotics - M.Tech RA - 2023-25 - MLPSUDIPTA CHATTERJEENo ratings yet

- Ae305 Microprocessors Microcontrollers PDFDocument2 pagesAe305 Microprocessors Microcontrollers PDFCharlotte DunkenNo ratings yet

- Lab Report SW AzarDocument9 pagesLab Report SW AzarAZAR DANFUDI NAMAZINo ratings yet

- 00 OverviewDocument25 pages00 OverviewSara GomezNo ratings yet

- Birla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionDocument3 pagesBirla Institute of Technology and Science, Pilani Pilani Campus Instruction Divisionsaurjyesh nayakNo ratings yet

- Course Outline of CSE 211 PDFDocument4 pagesCourse Outline of CSE 211 PDFSafialIslamAyonNo ratings yet

- Mumbai University (Sem-6 (Rev) ) SyllabusDocument13 pagesMumbai University (Sem-6 (Rev) ) Syllabusamit_sutar14100% (2)

- Course Objectives:: L T P/S SW/F W Total Credit UnitsDocument4 pagesCourse Objectives:: L T P/S SW/F W Total Credit UnitslalaNo ratings yet

- DD HandoutDocument3 pagesDD HandoutAsdgjkNo ratings yet

- Format For Course Curriculum Course Title: Credit Units: 5 Course Code: CSE207Document5 pagesFormat For Course Curriculum Course Title: Credit Units: 5 Course Code: CSE207aditya bNo ratings yet

- MICROPROCESSORS-Ktunotes inDocument10 pagesMICROPROCESSORS-Ktunotes inAdinath SNo ratings yet

- Deco Amity SyllabiDocument4 pagesDeco Amity SyllabiAyush JNo ratings yet

- Deco PDFDocument4 pagesDeco PDFTabish ZaidiNo ratings yet

- 18 P 19 Curriculum CO Semester IVDocument45 pages18 P 19 Curriculum CO Semester IVvayobo1203No ratings yet

- CSE 315 - COurseOutlineDocument11 pagesCSE 315 - COurseOutlineMustafizur Rahman RafeeNo ratings yet

- COE301 Lab Syllabus T-232Document3 pagesCOE301 Lab Syllabus T-232modyzombie82No ratings yet

- Microcontroller Weightage Revised 2019-20Document4 pagesMicrocontroller Weightage Revised 2019-20lalaNo ratings yet

- CS F111 Course Handout 2023 24 NikumaniDocument3 pagesCS F111 Course Handout 2023 24 Nikumanilsaidheeraj9No ratings yet

- 1 Introduction 10 Jul 2018 - Reference Material I - Day 1Document11 pages1 Introduction 10 Jul 2018 - Reference Material I - Day 1Adarsh RajNo ratings yet

- CS F111_Handout-NikumaniDocument3 pagesCS F111_Handout-NikumaniNikhilNo ratings yet

- Birla Institute of Technology and Science, Pilani: Pilani Campus AUGS/ AGSR DivisionDocument2 pagesBirla Institute of Technology and Science, Pilani: Pilani Campus AUGS/ AGSR DivisionVibgyor SinghviNo ratings yet

- State Council For Technical Education and Vocational Training, OdishaDocument17 pagesState Council For Technical Education and Vocational Training, OdishaSWARNA LATANo ratings yet

- Chhattisgarh Swami Vivekanand Technical University, BhilaiDocument26 pagesChhattisgarh Swami Vivekanand Technical University, BhilaiSK BeharNo ratings yet

- Course Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentDocument6 pagesCourse Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentAbdullah SohailNo ratings yet

- Worksheet 1.1Document2 pagesWorksheet 1.1ndjndoe4d6No ratings yet

- Bachelor of Technology (CSE) Semester V SubjectsDocument31 pagesBachelor of Technology (CSE) Semester V SubjectsAD THE GR8No ratings yet

- 21RA43 MicrocontrollerDocument4 pages21RA43 MicrocontrollerSamvrudh NagarajNo ratings yet

- Embedded System & Microcontroller Application Course Code: 4351102Document8 pagesEmbedded System & Microcontroller Application Course Code: 4351102Raggy TannaNo ratings yet

- COMPUTER Engineering - DEC2018 New-MinDocument163 pagesCOMPUTER Engineering - DEC2018 New-MinAdhara MukherjeeNo ratings yet

- Rancangan Pengajaran KV Unit Teknologi Elektronik: Semester 1 DVM/ 2016Document20 pagesRancangan Pengajaran KV Unit Teknologi Elektronik: Semester 1 DVM/ 2016Elisbeth MurugasNo ratings yet

- Legends: L-Lecture T - Tutorial/Teacher Guided Theory Practice P - Practical C - Credit, ESE - EndDocument6 pagesLegends: L-Lecture T - Tutorial/Teacher Guided Theory Practice P - Practical C - Credit, ESE - EndbhattparthivNo ratings yet

- Dae31203 Lab3 Sem2sesi22-23Document14 pagesDae31203 Lab3 Sem2sesi22-23Arief Musta'in Bin Mohammad Ilyas SahuriNo ratings yet

- EC8691 Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesEC8691 Lesson Plan Microprocessor and Micro COntrollerlauro eugin brittoNo ratings yet

- 17 P 19 Curriculum CO Semester III 2Document28 pages17 P 19 Curriculum CO Semester III 2vayobo1203No ratings yet

- Teams Mini Project title and Roll NumbersDocument3 pagesTeams Mini Project title and Roll NumbersPriNo ratings yet

- Teams Mini Project title and Roll NumbersDocument3 pagesTeams Mini Project title and Roll NumbersPriNo ratings yet

- WelcomeDocument5 pagesWelcomeCatNo ratings yet

- Database Systems Course OverviewDocument3 pagesDatabase Systems Course OverviewPriNo ratings yet

- BITS Pilani Hyderabad Biology Exam QuestionsDocument2 pagesBITS Pilani Hyderabad Biology Exam QuestionsSajithNo ratings yet

- Lyla B Das 0 & 1 PDFDocument53 pagesLyla B Das 0 & 1 PDFAnkit Sethia100% (4)

- Signals & Systems: EEE & ECE Department BITS-Pilani, Hyderabad CampusDocument82 pagesSignals & Systems: EEE & ECE Department BITS-Pilani, Hyderabad CampusPriNo ratings yet

- Test 1 Question BIO F111 Set A (Sem1, 2014-15) PDFDocument4 pagesTest 1 Question BIO F111 Set A (Sem1, 2014-15) PDFSajithNo ratings yet

- Abdullahi Abubakar Kaka 212140715 Sociology of Media Representation/ Encoding and DecodingDocument11 pagesAbdullahi Abubakar Kaka 212140715 Sociology of Media Representation/ Encoding and DecodingPriNo ratings yet

- SS Quiz-1 Notice PDFDocument1 pageSS Quiz-1 Notice PDFPriNo ratings yet

- Tirumala Lakshmi ThesisDocument103 pagesTirumala Lakshmi ThesisnloskutovaNo ratings yet

- Machine Learning NotesDocument135 pagesMachine Learning NotesPriNo ratings yet

- Microprocessor Programming & Interfacing: Tutorial 3Document6 pagesMicroprocessor Programming & Interfacing: Tutorial 3PriNo ratings yet

- Machine Learning NotesDocument135 pagesMachine Learning NotesPriNo ratings yet

- Block Diagram TranformationsDocument1 pageBlock Diagram TranformationsPriNo ratings yet

- Numpy Python Cheat Sheet PDFDocument1 pageNumpy Python Cheat Sheet PDFnyh rmoNo ratings yet

- PC4000 6Document8 pagesPC4000 6Sergio Velarde RomayNo ratings yet

- Move201910 Install Guide PDFDocument10 pagesMove201910 Install Guide PDFLambok ManurungNo ratings yet

- User's Manual - NAS EnclosureDocument28 pagesUser's Manual - NAS Enclosuredziama100% (2)

- Windows 95 ManualDocument111 pagesWindows 95 ManualAlonso CarlosNo ratings yet

- High Voltage Insulation Oil TesterDocument5 pagesHigh Voltage Insulation Oil TesterErAkashAryanNo ratings yet

- Rab StudioDocument29 pagesRab StudioMuhammad Ridwan AkbarNo ratings yet

- ATS-33 Automatic Transfer Switch Controller Operator's ManualDocument39 pagesATS-33 Automatic Transfer Switch Controller Operator's Manualalexmuchmure2158No ratings yet

- DxdiagDocument42 pagesDxdiagSeven PayneNo ratings yet

- 6ra24 Manual UsaDocument406 pages6ra24 Manual UsaBernd ReuterNo ratings yet

- TBC FordDocument3 pagesTBC FordPepe AlonzoNo ratings yet

- EC 2354 VLSI Design PDFDocument144 pagesEC 2354 VLSI Design PDFAbd Arief KhanNo ratings yet

- CatalogoDocument4,776 pagesCatalogoStefanoNo ratings yet

- Dell EMC Unity - CRU Procedures-Replacing 2.5 Inch DriveDocument19 pagesDell EMC Unity - CRU Procedures-Replacing 2.5 Inch DriveabcNo ratings yet

- ADTRAN - Gigabit Service Overview PDFDocument38 pagesADTRAN - Gigabit Service Overview PDFEndri MemaNo ratings yet

- IcarosDesktop ManualDocument56 pagesIcarosDesktop ManualayranayranNo ratings yet

- Smart Dustbin System Using IotDocument48 pagesSmart Dustbin System Using Iotsamruddhi100% (1)

- Cooler Master Casing - Power Supply - AccessoriesDocument4 pagesCooler Master Casing - Power Supply - AccessoriesSimlim SqNo ratings yet

- 2023-06-28 RR Kabel PricelistDocument12 pages2023-06-28 RR Kabel PricelistCpgeorge JohnNo ratings yet

- Smart Cane ProposalDocument5 pagesSmart Cane ProposalSethbaldovinoNo ratings yet

- Virtual KeyboardDocument3 pagesVirtual KeyboardGarner MitchellNo ratings yet

- 23 Sensor Pressure SwitchDocument28 pages23 Sensor Pressure SwitchموهاجيرينNo ratings yet

- A 300 W Power Amplifier For The 88 To 108 MHZ - HFE0408 - EguizabalDocument5 pagesA 300 W Power Amplifier For The 88 To 108 MHZ - HFE0408 - EguizabalfulperNo ratings yet

- Welcome To Politeknik Tuanku Sultanah Bahiyah.: For PLC and CX-Programmer Training CourseDocument33 pagesWelcome To Politeknik Tuanku Sultanah Bahiyah.: For PLC and CX-Programmer Training CoursemajitraNo ratings yet

- CFM M MUX - Tech DescriptionDocument63 pagesCFM M MUX - Tech DescriptionFrankJoeNo ratings yet

- Catalogo VC Came 2013 enDocument20 pagesCatalogo VC Came 2013 enDobre FlorinNo ratings yet

- Boq of Solu Hydro Power Project PKG 1Document37 pagesBoq of Solu Hydro Power Project PKG 1vijayNo ratings yet

- MGS100 Technical Datasheet Final Rev-A ABBDocument2 pagesMGS100 Technical Datasheet Final Rev-A ABBRicardo MartinsNo ratings yet