Professional Documents

Culture Documents

Digital Switching Design Using Verilog

Uploaded by

Shrikant JotawarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Switching Design Using Verilog

Uploaded by

Shrikant JotawarCopyright:

Available Formats

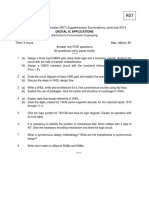

Jain College of Engineering, Belagavi

Department of Electronics and Communication Engineering

Bloom’s

Q. No. Questions COs’ Cognitive

Levels

Explain flash ADc and successive approximation ADC with the help of diagram.

1 4 L2

Design and develop a verilog code for an input controller that has 8 bit

binary coded input from sensor. The value can be read from an 8 bit input

2 register. The controller should interrupt embedded Gumnut core when the 4 L2

input values changes. The controller is the only interrupt source in the

system.

3 Explain any four serial interface standards. 4 L2

4 Explain Digital-to-Analog Converters using R/2R ladder DAC. 4 L2

Write a verilog assignment that represents a tri-state bus driver for an 8 bit 4

5 L2

bus.

6 Explain the design flow of hardware/software co-design. 4 L3

7 Explain the logical partitioning and physical partitioning of system. 5 L2

8 What aspects of the design flow does a verification plan cover? 5 L1,L2

9 Explain Built-in self test (BIST) techniques 5 L2

10 Explain the terms scan design and boundary scan. 5 L2

Assignment

Semester: VI Date:9/05/2019

Subject with code: Digital system design using Verilog (15EC663)

You might also like

- 18cs441 MC-1 PDFDocument2 pages18cs441 MC-1 PDFM.A rajaNo ratings yet

- HDL Lab Manual: Anandanagar, Bangalore-24Document81 pagesHDL Lab Manual: Anandanagar, Bangalore-24Abinet ArbaNo ratings yet

- Rns Institute of Technology: Electronics and Communication EngineeringDocument1 pageRns Institute of Technology: Electronics and Communication EngineeringVinaykumar ANo ratings yet

- 18CS44 Microcontroller Embedded Systems Model Question Paper 3Document2 pages18CS44 Microcontroller Embedded Systems Model Question Paper 3Prince AdnanNo ratings yet

- 18CS44 Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Document2 pages18CS44 Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)M.A rajaNo ratings yet

- 18CS44 Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Document2 pages18CS44 Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Mansi R UNo ratings yet

- Fpga Bases VLSI Design and Implementation: Course OverviewDocument4 pagesFpga Bases VLSI Design and Implementation: Course OverviewSarthak KumarNo ratings yet

- Institute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringDocument40 pagesInstitute of Aeronautical Engineering (Autonomous) : Electronics and Communication EngineeringMano HarNo ratings yet

- IoT QBDocument2 pagesIoT QBsohumnaidu121No ratings yet

- I - IA - VHDL - 18EC56 (18 Batch)Document1 pageI - IA - VHDL - 18EC56 (18 Batch)NithiyaNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (1)

- Verilog IaDocument2 pagesVerilog IarajNo ratings yet

- Verilog LabDocument70 pagesVerilog Labhkes rcrNo ratings yet

- Prelim Module1 - BDocument11 pagesPrelim Module1 - BCelimen, John Renz C.No ratings yet

- 3 FPGA ModulesDocument2 pages3 FPGA ModulesAbhimanyuNo ratings yet

- HDL Lab Manual Final 2017Document65 pagesHDL Lab Manual Final 2017eshwar_worldNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.rajkumarsacNo ratings yet

- Course Material Verilog ModuleDocument86 pagesCourse Material Verilog Modulevr46shreyasNo ratings yet

- Se, All Branches. C A - oDocument2 pagesSe, All Branches. C A - oanuragnair377No ratings yet

- WWW - Manaresults.co - In: Set No. 1Document4 pagesWWW - Manaresults.co - In: Set No. 1Machine BatteryNo ratings yet

- KalyanakumarDocument2 pagesKalyanakumarkalyanakumarkgNo ratings yet

- Computer OrganizationDocument1 pageComputer OrganizationsubbuNo ratings yet

- Lab Manual - VlsiDocument121 pagesLab Manual - VlsiDev SejvaniNo ratings yet

- ECT 206 Computer Organization and Microcontroller-SyllabusDocument8 pagesECT 206 Computer Organization and Microcontroller-SyllabusVilayil jestinNo ratings yet

- VLSIDDocument40 pagesVLSIDrutujaakadamNo ratings yet

- Research Paper 1 Decoder 7 Segment PDFDocument7 pagesResearch Paper 1 Decoder 7 Segment PDFAshutosh Meena0% (1)

- Smart Distribution Research Center, Korea Electrotechnology Research Institute (KERI)Document1 pageSmart Distribution Research Center, Korea Electrotechnology Research Institute (KERI)Manuel LezcanoNo ratings yet

- Submitted in Partial Fulfillment of The Requirement For The Award ofDocument100 pagesSubmitted in Partial Fulfillment of The Requirement For The Award ofYogeshNo ratings yet

- 16bt70402 - Embedded SystemsDocument1 page16bt70402 - Embedded SystemsS KkNo ratings yet

- San Ia 1Document2 pagesSan Ia 1Hanu MNo ratings yet

- Advanced Electronic Design AutomationDocument314 pagesAdvanced Electronic Design Automationmax51sNo ratings yet

- Experiment 7 Concurrent CodeDocument3 pagesExperiment 7 Concurrent CodeMohamd barcaNo ratings yet

- Anjan Report CtsDocument100 pagesAnjan Report CtschandrahasNo ratings yet

- Computer Architecture LU Lab Notes/Assignments: Wpuffits@mail - Tuwien.ac - atDocument15 pagesComputer Architecture LU Lab Notes/Assignments: Wpuffits@mail - Tuwien.ac - atአንድነት togetherNo ratings yet

- COMSATS Institute of Information Technology Abbottabad: GoalsDocument2 pagesCOMSATS Institute of Information Technology Abbottabad: GoalsSohail MashwaniNo ratings yet

- Design of LDPC Decoder Using FPGA: Review of Flexibility: Asisa Kumar Panigrahi, Ajit Kumar PandaDocument6 pagesDesign of LDPC Decoder Using FPGA: Review of Flexibility: Asisa Kumar Panigrahi, Ajit Kumar PandaresearchinventyNo ratings yet

- Digital System Design Functional Design: Register Transfer Level Design (RTL)Document3 pagesDigital System Design Functional Design: Register Transfer Level Design (RTL)Trần Duy QuậnNo ratings yet

- Erts - Model 1Document3 pagesErts - Model 1Ece DeptNo ratings yet

- CN Assignment IIDocument1 pageCN Assignment IIHarsha RampurNo ratings yet

- LDPCFPGASurveyDocument26 pagesLDPCFPGASurveyJamil AhmadNo ratings yet

- 8051 Programming Using Embedded CDocument44 pages8051 Programming Using Embedded Crenukaprasadj6No ratings yet

- R05411002 PcbasedinstrumentationDocument4 pagesR05411002 PcbasedinstrumentationSamiullah MohammedNo ratings yet

- 9D08104 Protocol Software EngineeringDocument1 page9D08104 Protocol Software EngineeringsubbuNo ratings yet

- Fundamentals of IoT SET 1Document1 pageFundamentals of IoT SET 1Manjot KaurNo ratings yet

- Verilog IntroDocument11 pagesVerilog IntroJossan EleazarEDENNo ratings yet

- MODEL ANSWER KEY VLSI-converted-compressedDocument28 pagesMODEL ANSWER KEY VLSI-converted-compressedPradeep ravichanderNo ratings yet

- SKEE1233 Project UTMDocument4 pagesSKEE1233 Project UTMmuhammadridwanjaafarNo ratings yet

- Spring 2021: Digital System Design Lab 1Document22 pagesSpring 2021: Digital System Design Lab 1SHAHZAIB AHMAD QURESHINo ratings yet

- Embedded SoPC Design with Nios II Processor and Verilog ExamplesFrom EverandEmbedded SoPC Design with Nios II Processor and Verilog ExamplesNo ratings yet

- DSDV Lesson PlanDocument2 pagesDSDV Lesson PlanPADMA RNo ratings yet

- Practical Programmable Circuits: A Guide to PLDs, State Machines, and MicrocontrollersFrom EverandPractical Programmable Circuits: A Guide to PLDs, State Machines, and MicrocontrollersNo ratings yet

- Circular - Open Electives EC - TCDocument12 pagesCircular - Open Electives EC - TCarjun5005No ratings yet

- Digital Electronics and Logic Design: CET203ADocument96 pagesDigital Electronics and Logic Design: CET203ASorab KhoslaNo ratings yet

- LSI Logic Design Chapter 3Document79 pagesLSI Logic Design Chapter 3Ngân NguyễnNo ratings yet

- LAB Manual Updated 2018Document127 pagesLAB Manual Updated 2018usmanzahidNo ratings yet

- Department of Software Engineering: Lab1: Familiarization of Basic Gates and Digital IcsDocument14 pagesDepartment of Software Engineering: Lab1: Familiarization of Basic Gates and Digital IcsMuhammad RehanNo ratings yet

- R7310404 Digital IC Applications2Document1 pageR7310404 Digital IC Applications2subbuNo ratings yet

- Lec01 Verilog Combinational Circuits Design 2022 SpringDocument64 pagesLec01 Verilog Combinational Circuits Design 2022 Springyanjia8161100No ratings yet

- BuchblockDocument103 pagesBuchblockRafiqul IslamNo ratings yet

- Blended VLSI-RN Maven-SiliconDocument4 pagesBlended VLSI-RN Maven-SiliconBharathNo ratings yet

- DC Mod-3&4Document46 pagesDC Mod-3&4Shrikant JotawarNo ratings yet

- Arm Module 4Document17 pagesArm Module 4Shrikant JotawarNo ratings yet

- DC Mod5 PDFDocument20 pagesDC Mod5 PDFShrikant JotawarNo ratings yet

- CCN AssignmentDocument26 pagesCCN AssignmentShrikant JotawarNo ratings yet

- Digital Switching Design Using VerilogDocument1 pageDigital Switching Design Using VerilogShrikant JotawarNo ratings yet