Professional Documents

Culture Documents

Research Paper 1 Decoder 7 Segment PDF

Uploaded by

Ashutosh MeenaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Research Paper 1 Decoder 7 Segment PDF

Uploaded by

Ashutosh MeenaCopyright:

Available Formats

International Journal of Electronics and Electrical Engineering Vol. 3, No.

1, February, 2015

IC Layout Design of Decoder Using Electric

VLSI Design System

Soh Hong Teen and Li Li Lim

Tunku Abdul Rahman University College, Kuala Lumpur, Malaysia

Email: {teensh, lllim}@acd.tarc.edu.my

Jia Hui Lim

Sheffield Hallam University, United Kingdom

Email: inu_chan_91@hotmail.com

Abstract—This paper discusses the design of an Integrated drawing, textual hardware description language, and

Circuit (IC) layout for a decoder. The layout was designed other features [1]. By using this software, a micrometer

by using an open source software namely Electric VLSI sized IC can be easily designed due to the availability of

Design System as the Electronic Design Automation (EDA) various features that can be used to design and check the

tool. In order to produce the layout, the basic knowledge of

IC layout. Moreover, Electric VLSI Design System also

fabrication process and IC design rules are expounded. The

complete layout of the decoder was designed based on its allows the schematic and layout design to be done in a

schematic circuit, which consists of NOT gates, 2-input systematic and efficient manner, thus saving time and

NAND gates, 3-input NAND gates, 4-input NAND gates, 2- reducing the production cost of the IC chip.

input AND gates and 3-input AND gates. The layout had There are different technologies to construct integrated

undergone Design Rule Check (DRC) set by the Electric circuits such as bipolar integrated technology, NMOS

VLSI Design System to check for any design rule error. technology and CMOS technology. In this project,

Both layout and schematic circuit of the decoder were then

CMOS technology is used. The main reason in using

simulated through Layout versus Schematic (LVS) to ensure

they were identical. LTspice is used as simulator to carry CMOS technology is due to its scalable high noise

out the simulation work and verify the validity of the immunity and low power consumption. Basically, CMOS

function. The simulation output indicated that results of the technology uses both NMOS and PMOS, which means

layout and schematic circuit for decoder were essentially only either one of both types of transistors will be ON at

identical and matches the theoretical results. a time during the operation. Thus, CMOS IC consumes

less power as power is used only when the NMOS and

Index Terms—decoder, schematic circuit, IC layout, electric

VLSI Design System, NAND gates, AND gates and

PMOS transistors are switching between on and off states

simulation output [2].

II. LITERATURE REVIEW

I. INTRODUCTION A. 7-Segments Decoder

Electronic devices have been widely used in many A 7-segments decoder is able to convert the logic

different fields and the size of these devices has been states of inputs into seven bits of outputs and displays in

gradually reduced. An example of this is the mobile 7-segments display. It is used widely in devices where its

phone which is made smaller to enhance user’s mobility main function is to display numbers from a digital

and usage time. These are the contribution of integrated circuitry. Examples of these devices includes calculators,

circuit (IC) technology. With this technology, the modern displays in elevator, digital timers, digital clocks and etc.

devices have been reduced to convenient sizes. Besides There are many types of decoders such as 2-4 decoder, 3-

that, mass production of IC has lowered the cost of 8 decoder and 4-16 decoder. Since there are ten decimal

production and made most electronic devices affordable. numerals (0–9) to be displayed in the 7-segments display,

Today, an IC is smaller than a coin and can hold millions

a 4-16 decoder was used.

of transistors. Hence, further research in the design of IC

The structure of a 7-segments display is shown in Fig.

is important to enhance the production of a more efficient

1. It is used to display decimal numerals in seven

and viable IC.

segments and each segment is represented by an alphabet

The main objective of this paper is to design an IC

‘a’ to ‘g’. By setting the required segments to be turned

layout of a 7-segments decoder by Electric VLSI Design

on, the desired decimal numeral can be displayed on the

System. It is a free open source EDA system that

7-segments display. The logic diagram of 7-segments

provides service in handling IC layout, schematic

decoder is shown in Fig. 2.

Manuscript received October 30, 2013; revised March 15, 2014.

©2015 Engineering and Technology Publishing 54

doi: 10.12720/ijeee.3.1.54-60

International Journal of Electronics and Electrical Engineering Vol. 3, No. 1, February, 2015

(Layout Versus Schematic) and ERC (Electrical Rule

Check). These are important procedures in IC layout

design and cannot be treated lightly.

i) Design Rule Check (DRC)

DRC is a verification process that determines whether

the physical layout of a chip design satisfies the Design

Rules or not. It ensures that all the polygons and layers

meet the manufacturing process rules that defines the

limits of a manufacturing design such as the width and

space rules. DRC is the first level of verification once the

layout is ready. In this verification stage, the connectivity

Figure 1. Structure of a 7-segments display

and guidelines rules will be checked as well. DRC will

not only check the designs that are created by the

designers, but also the design placed within the context in

which it is going to be used. Therefore, the possibility of

errors in the design will be greatly reduced and a high

overall yield and reliability of design will be achieved.

ii) Layout Versus Schematic (LVS)

LVS is a process to check if a particular IC layout

corresponds to the original schematic circuit of the design.

The schematic acts as the reference circuit and the layout

will be checked against it. In this process, the electrical

connectivity of all signals, including the input, output and

power signals to their corresponding devices are checked.

Besides that, the sizes of the device will also be checked

including the width and length of transistors, sizes of

resistors and capacitors. The LVS will also identify the

extra components and signals that have not been included

in the schematic, for example, floating nodes. In Electric

VLSI Design System, this type of checking is known as

the Network Consistency Checking (NCC) as is able to

compare any two circuits, which includes two layouts or

two schematics.

iii) Electrical Rules Check (ERC)

ERC is usually used to check the errors in connectivity

or device connection. It is an optional choice of checking

and seldom used as an independent verification step.

Figure 2. The logic diagram of a 7-segments decoder [3]

ERC is usually used to check for any unconnected, partly

connected or redundant devices. Also, it will check for

B. IC Design

any disabled transistors, floating nodes and short circuits.

IC layouts are built from three basic components ERC is very useful in accelerating debugging problems

which are the transistors, wires and vias. During the such as short circuits as can speed up the design process.

design of the layouts, the design rule has to be considered.

Design rules govern the layout of individual components III. METHODOLOGY

and the interaction between those components. When

designing an IC, designers tend to make the components The schematic circuit of the 7-segments decoder was

as small as possible enabling implementation of as many drawn and debugging process had been carried out to

functions as possible onto a single chip. However, since ensure the design is error free. In this project, the layout

the transistors and wires are extremely small, errors may of the 7-segments decoder was designed using Electric

happen during the fabrication process. Hence, design VLSI Design System to exploit its powerful editing tools.

rules are created and formulated to minimise problems Electric VLSI Design System is a high performance

during fabrication process and helps to increase the yield EDA tool that provides complete aids in designing the IC

of correct chips to a suitable level. Therefore, it is layout. It integrates the schematic editor, circuit simulator,

important to adhere to the design rules during layout schematic driven layout generator, layout editor, layout

design. verification and parasitic extraction. Another advantage

to Electric VLSI Design System is that it allows

C. Physical Verification of Design [1], [4] swapping between the designs data with other standard

Physical verification is a process where an IC layout EDA tools in the industry. [1]

design will be checked via EDA tools to ensure it meets Besides that, LTspice IV simulation software was also

design criteria and rules. The verification process used in used in this project. It is a high performance SPICE

this project involves DRC (Design Rule Check), LVS simulator that provides a schematic capture and

©2015 Engineering and Technology Publishing 55

International Journal of Electronics and Electrical Engineering Vol. 3, No. 1, February, 2015

waveform viewer. It is used to simulate the outputs of components can be placed side by side without any space

both schematic circuit and layout during DRC and LVS. in between. There is also no minimum distance between

There are basic design rules to be followed in order to vias or with other components listed in the table. This is

design an IC layout successfully. These rules uses a because the vias available in Electric VLSI Design

universal parameter, λ. Fig. 3 shows the basic design System are combined with 2 metals, covering every side

rules commonly used in Electric VLSI Design System. of the vias. Therefore, before the vias can be placed

nearer to each other, the metal surrounding it will connect

TABLE I. LIST OF FUNDAMENTAL RULE OF DESIGNING AN IC each other first. The distance between the metal of vias

LAYOUT [5]

has to obey the rules before the vias have the chance of

Well contact. In other words, it also indicates that the

Minimum well size 12 minimum distance between vias or with other

Between wells 6 components can be determined through the metal’s rule.

Between N-well and P-well 0

Minimum well area 1442

Polysilicon1

Polysilicon1 width 2

Between polysilicon1s 3

Between polysilicon1 and metal N/A

Minimum polysilicon1 area 42

Polysilicon2

Polysilicon2 width 7

Between polysilicon2s 3

Between polysilicon2 and metal N/A

Minimum polysilicon2 area 492

Metal1,2,3,4,5 Figure 3. Fundamental rule of designing an IC layout (All values are

in lambda) [5]

Metal width 3

Between metals 3 IV. FINDINGS

Between metal and other metal N/A

In this project, an IC layout of a decoder that displays

Minimum metal area 92

the decimal numeral in 7-segments display was designed.

It consists of NOT gates, 2-input NAND gates, 3-input

Via1,2,3,4 NAND gates, 4-input NAND gates, 2-input AND gates

Via width 2 and 3-input AND gates. The schematic circuits and

Minimum via area 42 layouts of all these gates were drawn and simulated using

Electric VLSI Design System. Also, LTSpice was used as

Metal6 external simulator to generate the simulation waveforms.

Metal6 width 5 A. 2-Input NAND Gates

Between metal6s 5

Fig. 4 and Fig. 5 shows the schematic diagram and

Between metal6 and other metal N/A layout design of a 2-input NAND gate using Electric

Minimum metal6 area 252 VLSI Design System.

Via5

Via5 width 3

Minimum via5 area 92

Table I shows the basic design rule in a list. As shown

in Fig. 3, the minimum distance between two same

metals or polysilicons must be at least 3λ. Besides, the

width of metal from 1 to 5 must be at least 3λ wide.

Notice that in Table I, some parameter’s rule are labelled

as ‘N/A’. This is because there are not such spacing rules.

In other words, the respective components can be placed

overlapping each other. Also, there are rules where the

parameter is 0λ. This indicates that the respective Figure 4. Schematic diagram of a 2-input NAND gate

©2015 Engineering and Technology Publishing 56

International Journal of Electronics and Electrical Engineering Vol. 3, No. 1, February, 2015

Figure 5. Layout design of 2-input NAND gate

Figure 8. Schematic diagram of 4-input NAND gate

B. 3-Input NAND Gates

Fig. 6 and Fig. 7 show the schematic diagram and

layout of a 3-input NAND gate.

Figure 9. Layout design of 4-input NAND gate

Fig. 10 shows the 4-input NAND gate symbol and

Figure 6. Schematic diagram of a 3-input NAND gate spice code. The code was required and used to complete

the simulation process. The input wire are named as ‘a’,

‘b’, ‘c’ and ‘d’; whereas output wire is named as ‘y’.

Simulation result of the 4-input NAND gate is shown in

Fig. 11. If all the inputs of the 4-input NAND gate are ‘1’,

the output will be ‘0’. Meanwhile, whenever there is ‘0’

among the inputs, the output will be ‘1’. In addition, due

to the capacitance, the fall in the waveform actually

indicates a logic ‘0’ whereas the rise in waveform

indicates a logic ‘1’. From the waveform generated, as

shown in Fig. 11, the results are match with the

theoretical 4-input NAND gate. It can be deduced that the

4-input NAND gate drawn by using Electric VLSI

Design System operates correctly.

Figure 7. Layout design of a 3-input NAND gate

C. 4-Input NAND Gates

Fig. 8 and Fig. 9 show the schematic diagram and

layout of a 4-input NAND gate, respectively. Figure 10. Icon of 4-input NAND gate and spice code

©2015 Engineering and Technology Publishing 57

International Journal of Electronics and Electrical Engineering Vol. 3, No. 1, February, 2015

D. 7-Segment Decoder

All the schematic diagrams and layouts of the basic

gates drawn have to go through the physical verification

process before simulation. These are the essential

procedures to ensure the validity outputs results of the

system.

Based on the logic diagram of 7-segment decoder, the

schematic circuit and its IC layout was designed using

Electric VLSI Design System tool, as shown in Fig. 12

Figure 11. Simulation result of the 4-input NAND gate

and Fig. 13, respectively.

Figure 12. Schematic diagram of a 7-segments decoder

Figure 13. IC layout design of decoder

However, Fig. 14 shows the icon view of the decoder ‘out_g’. Notice that there is a ‘sw’ input which represents

with spice code, which is ready for simulation. It shows the switch. When the switch is to ‘0’, no matter what

the inputs and outputs port and also the spice code that other inputs are, the outputs will always be ‘0’. When the

specifies the input pulses of the decoder for simulation. switch is to ‘1’, the outputs will be varied according to

There are five inputs: ‘in_0’, ‘in_1’, ‘in_2’, ‘in_3’ and the binary combination of the inputs.

‘sw’, where ‘in_0’ is the least significant bit and ‘in_3’ is Fig. 15 is the simulation waveform generated with

the most significant bit. Since it is a 7-segment decoder, different inputs. It is known that as long as the ‘sw’ is off,

seven outputs will be needed. These outputs are labelled the outputs will be ‘0’. This figure shows simulation

as ‘out_a’, ‘out_b’, ‘out_c’, ‘out_d’, ‘out_e’, ‘out_f’ and waveform for when the ‘sw’ is off. In reference to the

©2015 Engineering and Technology Publishing 58

International Journal of Electronics and Electrical Engineering Vol. 3, No. 1, February, 2015

truth table of the binary-convert-decimal, as shown in simulator of LTSpice, setting of spice engine and its path,

Table II, the designed decoder is match with the technology and scale used.

theoretical work and said to function as expected.

B. Verification Process

As mentioned earlier, physical verification process is

an essential procedure. The schematic diagram and layout

design can be checked through DRC. It is recommended

that the schematic diagram is free of warning and error

before designing its layout.

LVS is used to ensure that the schematic diagram and

its layout are identical. This process will check the

number of exports, ports, transistor size between

schematic and the layout. Error may occur if they are not

consistent.

While running the LVS, the library names for both

schematic and layout have to be same and place under the

same group. This is to ensure that the software compares

the correct library.

Figure 14. Icon of decoder and spice code C. Spice Code

In Electric VLSI Design System, spice code is used as

function to be read by LTspice in order to simulate the

waveform. A proper and correct spice code will generate

correct waveform through this simulator. Spice code is

written and inserted in the icon view of the decoder

before running simulation. It specifies the input pulses

and all the ports of decoder. The code written must be

consistent with the icon drawn.

VI. CONCLUSION

In conclusion, 7-segments decoder IC is to display the

numbers in 7 segments. It converts the binary input to 7

bits according to the input. The IC layout of the decoder

is designed and successfully proves that the output

Figure 15. Simulation result of the 7-segments decoder waveforms generated matches the theoretical decoder.

In addition, the open source Electric VLSI Design

TABLE II. TRUTH TABLE OF BINARY-CONVERT-DECIMAL (BCD)

System is a user friendly software to be used in designing

INPUT OUTPUT a layout of 7-segments decoder. It is expected that the

No in_3 in_2 in_1 in_0 a b c d e f g software is able to cope with more complex digital IC

0 0 0 0 0 1 1 1 1 1 1 0

design with its suite of verification and design tools.

1 0 0 0 1 0 1 1 0 0 0 0

REFERENCES

2 0 0 1 0 1 1 0 1 1 0 1

[1] About Electric. (May 2013). [Online]. Available:

3 0 0 1 1 1 1 1 1 0 0 1

www.staticfreesoft.com/electric.html

4 0 1 0 0 0 1 1 0 0 1 1 [2] R. J. Baker, CMOS: Circuit Design, Layout, and Simulation, John

5 0 1 0 1 1 0 1 1 0 1 1 Wiley & Sons, 2010, pp. 6-12.

[3] M. M. Forrest, Understanding Digital Computers, Radio Shack,

6 0 1 1 0 0 0 1 1 1 1 1 1987.

7 0 1 1 1 1 1 1 0 0 0 0 [4] S. H. Teen and S. Y. Lee, “CMOS IC layout design: 7-segments

counter,” Lecture Notes on Photonics and Optoelectronics, vol. 1,

8 1 0 0 0 1 1 1 1 1 1 1 no. 2, pp. 52-55, December 2013.

9 1 0 0 1 1 1 1 1 0 1 1 [5] A. P. Douglas and E. Kamran, Basic VLSI Design, 3rd ed.,

Prentice Hall, 1994, pp. 72-76.

V. TROUBLESHOOTING

In order to avoid inability to run the simulation, the Soh Hong Teen graduated with a bachelor degree

following steps have to be taken: in Computational Physics and Electronics from

University of Malaya, Malaysia in year 2000. She

A. Setting and Installation joined Tunku Abdul Rahman College as a lecturer

in year 2001. She continued her studies in year

Before start drawing the schematic circuit, all the 2003 and was awarded Master of Science degree

setting of the Electric VLSI Design System must be done from University of Malaya in year 2006.

properly. These include the installation of external Currently, she is a full time academic staff in

Tunku Abdul Rahman University College and has

©2015 Engineering and Technology Publishing 59

International Journal of Electronics and Electrical Engineering Vol. 3, No. 1, February, 2015

been assigned to teach subjects related to Solid State Electronics and Li Li Lim graduated with an Advanced Diploma

Electromagnetic Fields. in Technology (Electronic Engineering) from

Tunku Abdul Rahman College in 2004 and was

Jia Hui Lim graduated with Advanced Diploma subsequently awarded a MSc. in Electronics from

in Technology (Electronic Engineering) from Queen’s University Belfast in 2005. She is now a

Tunku Abdul Rahman University College in full time academic staff at the Faculty of

2013. She continued her degree in Sheffield Engineering and Built Environment at Tunku

Hallam University, United Kingdom and will be Abdul Rahman (TAR) University College and a

graduating in year 2014. member of the Centre for Multimodal Signal

Processing under the Advanced Engineering Research Centre at TAR.

Her current research interest includes channel coding, MIMO symbol

detection and statistical signal processing for a wide application area.

©2015 Engineering and Technology Publishing 60

You might also like

- Electrical Power and Machines IntroductionDocument7 pagesElectrical Power and Machines Introductionshakeeb mana0% (1)

- Xmitip GuideDocument61 pagesXmitip Guidesamkolkin100% (1)

- 8051-CH6-ArithLigic InstructnsDocument114 pages8051-CH6-ArithLigic Instructnsshivaspy100% (1)

- EEB443 Test 1 & Solutions - April 6, 2023-1Document7 pagesEEB443 Test 1 & Solutions - April 6, 2023-1Jakisee Kavezeri100% (1)

- DLD Lab Report #9Document10 pagesDLD Lab Report #9waleedNo ratings yet

- 7 Segment Display IntroductionDocument2 pages7 Segment Display IntroductionMrmouzinho100% (1)

- Seven Segment Display Document PDFDocument16 pagesSeven Segment Display Document PDFRekha MudalagiriNo ratings yet

- Performance of 8-Psk Modulation Scheme Using Rayleigh Fading Channel For Wcdma SystemDocument7 pagesPerformance of 8-Psk Modulation Scheme Using Rayleigh Fading Channel For Wcdma SystemANIKNo ratings yet

- BCD To 7 Segment Display ProjectnewDocument5 pagesBCD To 7 Segment Display ProjectnewSaeed Ali ShahaniNo ratings yet

- BCD to 7-Segment Decoder Converts NumbersDocument7 pagesBCD to 7-Segment Decoder Converts NumbersBOMMA SRI MUKHINo ratings yet

- LOGIC DESIGN LAB MANUAL EXPERIMENTSDocument80 pagesLOGIC DESIGN LAB MANUAL EXPERIMENTSabhinav kumarNo ratings yet

- Ece-Vii-dsp Algorithms & Architecture (10ec751) - AssignmentDocument9 pagesEce-Vii-dsp Algorithms & Architecture (10ec751) - AssignmentMuhammadMansoorGohar100% (1)

- Build a 4-bit parity generator and checker circuitDocument9 pagesBuild a 4-bit parity generator and checker circuitsaloniNo ratings yet

- DSP Chapter 1Document4 pagesDSP Chapter 1Anupam SharmaNo ratings yet

- LCD and KEYBORD Interfacing Part 1Document25 pagesLCD and KEYBORD Interfacing Part 1Prathamesh AmateNo ratings yet

- Sample Question Paper Applied ElectronicsDocument4 pagesSample Question Paper Applied Electronicssachin barge100% (1)

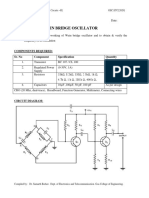

- Expt 5 - Wein Bridge Oscillator (2020)Document3 pagesExpt 5 - Wein Bridge Oscillator (2020)samarthNo ratings yet

- The Digital Encoder: 4-To-2 Bit Binary EncoderDocument10 pagesThe Digital Encoder: 4-To-2 Bit Binary EncoderJohn Brix BalisterosNo ratings yet

- EE8552 Power ElectronicsDocument13 pagesEE8552 Power ElectronicsAbhishekNo ratings yet

- Tma 1Document5 pagesTma 1zihawNo ratings yet

- Software Design For Low PowerDocument20 pagesSoftware Design For Low PowerGokul B S MandyaNo ratings yet

- HDL Model QPDocument5 pagesHDL Model QPSubramanyaAIyerNo ratings yet

- Ec8361-Adc Lab ManualDocument118 pagesEc8361-Adc Lab ManualmuminthajNo ratings yet

- Smart Shopping Cart IEEE PDFDocument4 pagesSmart Shopping Cart IEEE PDFradz248100% (3)

- ALU 8 BIT Group NaminDocument23 pagesALU 8 BIT Group NaminChrisEmilsonHernaezNo ratings yet

- MSDFFDocument20 pagesMSDFFShweta KumariNo ratings yet

- Choosing Between DSP, FPGA and ASIC for Digital Hardware in Software Defined RadioDocument13 pagesChoosing Between DSP, FPGA and ASIC for Digital Hardware in Software Defined RadioKAMRAN12345786No ratings yet

- Embedded Systems Lab Manual Exp. 1-4Document18 pagesEmbedded Systems Lab Manual Exp. 1-4Akshit Jain100% (1)

- Practical File: Optoelectronics and Optical Communications LabDocument21 pagesPractical File: Optoelectronics and Optical Communications Labyogesh sharmaNo ratings yet

- Microprocessor All Experiment IT PDFDocument22 pagesMicroprocessor All Experiment IT PDFSuraj KumarNo ratings yet

- A-Law and U-Law CompandingDocument4 pagesA-Law and U-Law CompandingAchyut Dev50% (2)

- Communication Stream (Traffic Light) PDFDocument9 pagesCommunication Stream (Traffic Light) PDFZelalem BirhanuNo ratings yet

- Digital Logic Design CourseDocument1 pageDigital Logic Design CourseVinay PasiNo ratings yet

- Digital Storage OscilloscopeDocument9 pagesDigital Storage OscilloscopeamrithaNo ratings yet

- ECD Lab EEC 752Document17 pagesECD Lab EEC 752juhi99360% (5)

- Wavelength Routing Testbeds: Presented By, Bibi Mohanan M.Tech, OEC Roll No:7Document30 pagesWavelength Routing Testbeds: Presented By, Bibi Mohanan M.Tech, OEC Roll No:7Bibi Mohanan100% (1)

- Ec8361 Adc Lab SyllabusDocument2 pagesEc8361 Adc Lab SyllabusNandha KumarNo ratings yet

- A Minor Project Report Traffic Light Controller Using 555 TimerDocument15 pagesA Minor Project Report Traffic Light Controller Using 555 TimerSarvesh Vk100% (1)

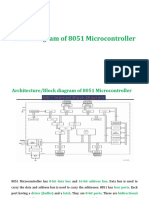

- Block Diagram of 8051 MicrocontrollerDocument18 pagesBlock Diagram of 8051 Microcontrollermd Sadikul IslamNo ratings yet

- Closed Loop DC Motor Speed ControlDocument3 pagesClosed Loop DC Motor Speed ControlKhayaz KunhabduNo ratings yet

- Ap7102 AdsdDocument5 pagesAp7102 AdsdshankarNo ratings yet

- DC Motor Speed Control Using PWMDocument4 pagesDC Motor Speed Control Using PWMInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- 16x2 LCDDocument3 pages16x2 LCDShailesh Ranaware0% (1)

- EE8461-Linear and Digital Integrated Circuits-Lab ManualDocument96 pagesEE8461-Linear and Digital Integrated Circuits-Lab ManualSETNHILNo ratings yet

- Long Report Lab 7Document15 pagesLong Report Lab 7Saragadam Naga Shivanath RauNo ratings yet

- 2-Bit Magnitude Comparator Design Using Logic StylesDocument12 pages2-Bit Magnitude Comparator Design Using Logic StylesSunith CkNo ratings yet

- 555 Timer Final ReportDocument36 pages555 Timer Final ReportRavi Dubey100% (1)

- STLD Lab Manual ExperimentsDocument42 pagesSTLD Lab Manual ExperimentssaikiranNo ratings yet

- Verilog CodeDocument60 pagesVerilog CodePriyanka JainNo ratings yet

- Experiment No 6: Implementation of Instruction Fetch Unit: Team Details: Terminal No: SL No Name Id No 1 2 3Document6 pagesExperiment No 6: Implementation of Instruction Fetch Unit: Team Details: Terminal No: SL No Name Id No 1 2 3Shreenath VyasNo ratings yet

- EC8095-VLSI DesignDocument11 pagesEC8095-VLSI DesignfayikaliNo ratings yet

- Record Electrical Quantities Over TimeDocument9 pagesRecord Electrical Quantities Over TimeManoj PatchiyanNo ratings yet

- LIC Lab ManualDocument65 pagesLIC Lab ManualBala Subramanian0% (1)

- EC 3353 Electronic Devices and Circuits: Unit 1: Semi Conductor DevicesDocument57 pagesEC 3353 Electronic Devices and Circuits: Unit 1: Semi Conductor DevicesAnusha PadmavathiNo ratings yet

- TTL Encoder-Decoder LabDocument3 pagesTTL Encoder-Decoder LabDuaa Al-HasanNo ratings yet

- Social Responsibilities of BusinessDocument23 pagesSocial Responsibilities of BusinessHarishNo ratings yet

- VLSI Design Lab NewDocument48 pagesVLSI Design Lab NewJubin JainNo ratings yet

- VLSI Design Lab NewDocument45 pagesVLSI Design Lab NewmtariqanwarNo ratings yet

- Tanner ManualDocument60 pagesTanner ManualFahim Ahmed100% (1)

- DSD LABDocument45 pagesDSD LABkumarravi955rNo ratings yet

- Introduction To: System-on-ChipDocument34 pagesIntroduction To: System-on-ChipNguyen Van ToanNo ratings yet

- Chapter 2 Lexical AnalysisDocument26 pagesChapter 2 Lexical AnalysisElias HirpasaNo ratings yet

- Husnain Sarfraz: Q No 1: Explain The Value of Studying ManagementDocument4 pagesHusnain Sarfraz: Q No 1: Explain The Value of Studying ManagementRadey32167No ratings yet

- 988H DIGNOSTIC Techdoc Print PageDocument5 pages988H DIGNOSTIC Techdoc Print Pagerao abdul bariNo ratings yet

- Premiere Pro Keyboard Shortcuts Cheatsheet Print Ready A4Document2 pagesPremiere Pro Keyboard Shortcuts Cheatsheet Print Ready A4David dazaNo ratings yet

- Web ADI PersonalizationDocument7 pagesWeb ADI PersonalizationsmohammedsaadNo ratings yet

- E. B. Magalona National High School Summative Test in CSS 10 Quarter 1 Week 1 Multiple Choice. Choose The Letter of The Correct AnswerDocument2 pagesE. B. Magalona National High School Summative Test in CSS 10 Quarter 1 Week 1 Multiple Choice. Choose The Letter of The Correct Answerric jason pedralNo ratings yet

- Iec 61439Document3 pagesIec 61439Chithra Babu0% (3)

- Consecutive Calculations!: Consecutive Numbers Follow One After Another, E.G. 5, 6, 7Document12 pagesConsecutive Calculations!: Consecutive Numbers Follow One After Another, E.G. 5, 6, 7Nikki Mayor-OngNo ratings yet

- 9399PLC5UMDocument542 pages9399PLC5UMneoflashNo ratings yet

- Iq-Lite: User ManualDocument77 pagesIq-Lite: User ManualBoba CurguzNo ratings yet

- Data Communications Networks Network Types Protocol LayeringDocument48 pagesData Communications Networks Network Types Protocol LayeringiotNo ratings yet

- Homo Conexus - The Connected HumansDocument238 pagesHomo Conexus - The Connected Humanssplinter2000No ratings yet

- 1 s2.0 S0747563219303711 MainDocument6 pages1 s2.0 S0747563219303711 MainKarla BallesterosNo ratings yet

- Cummins Serie K Calibracion de ValvulasDocument63 pagesCummins Serie K Calibracion de Valvulasfrank_16100% (1)

- Full download book Digital Systems Design Using Vhdl 3Rd Edition Pdf pdfDocument41 pagesFull download book Digital Systems Design Using Vhdl 3Rd Edition Pdf pdfphillip.kettner341100% (13)

- LogDocument3 pagesLogVk Gonzales JayloNo ratings yet

- PHD Entrance Exam BIT MesraDocument5 pagesPHD Entrance Exam BIT MesraMohammad Mottahir AlamNo ratings yet

- Amanda Bokshan Resume 2016Document1 pageAmanda Bokshan Resume 2016api-325092229No ratings yet

- Characteristics of ComputersDocument2 pagesCharacteristics of ComputersBilas Joseph33% (3)

- Accessories For Camera Housings: SunshieldDocument10 pagesAccessories For Camera Housings: SunshieldSakerhetsNo ratings yet

- 3CX VoIP Telephone, Phone SystemDocument18 pages3CX VoIP Telephone, Phone SystemRob Bliss Telephone, Phone System SpecialistNo ratings yet

- Risk and OpportunityDocument5 pagesRisk and OpportunityQualityproNo ratings yet

- Service Manual BTS-350Document46 pagesService Manual BTS-350João GamaNo ratings yet

- Three Phase Capacitor Unit Brochure (2003-06)Document2 pagesThree Phase Capacitor Unit Brochure (2003-06)protectionworkNo ratings yet

- Part 2 Ethernet+NetworkingDocument23 pagesPart 2 Ethernet+NetworkingSumit MidhaNo ratings yet

- B.E. EeeDocument92 pagesB.E. Eeessathishkumar88No ratings yet

- Tugas Citra 4Document23 pagesTugas Citra 4AnonymousNo ratings yet

- Series Tl1105 Switches: Tact Switches - 6Mm X 6MmDocument3 pagesSeries Tl1105 Switches: Tact Switches - 6Mm X 6Mmalex kastaNo ratings yet

- Building Backbone - JsDocument23 pagesBuilding Backbone - JsFarid HidayatNo ratings yet