0% found this document useful (0 votes)

227 views31 pages8085 Microprocessor Guide

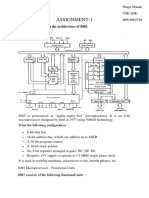

The document discusses the Intel 8085 microprocessor. It describes the 8085's features such as its 8-bit architecture, 16-bit address bus, and arithmetic logic unit. It outlines the 8085's registers including the accumulator, flags register, and temporary registers. The document provides details on the 8085's instruction set, addressing modes, and programming. It includes a block diagram of the 8085 architecture and pin configuration. An example program and its assembly are shown to demonstrate how machine code is generated from mnemonics and addresses.

Uploaded by

Munazza FatmaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

Topics covered

- Sign Flag,

- Memory Control,

- Data Exchange Programs,

- Data Flow,

- Program Structure,

- Memory Locations,

- Assembler,

- Addressing Modes,

- Interrupt Signals,

- Data Transfer

0% found this document useful (0 votes)

227 views31 pages8085 Microprocessor Guide

The document discusses the Intel 8085 microprocessor. It describes the 8085's features such as its 8-bit architecture, 16-bit address bus, and arithmetic logic unit. It outlines the 8085's registers including the accumulator, flags register, and temporary registers. The document provides details on the 8085's instruction set, addressing modes, and programming. It includes a block diagram of the 8085 architecture and pin configuration. An example program and its assembly are shown to demonstrate how machine code is generated from mnemonics and addresses.

Uploaded by

Munazza FatmaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

Topics covered

- Sign Flag,

- Memory Control,

- Data Exchange Programs,

- Data Flow,

- Program Structure,

- Memory Locations,

- Assembler,

- Addressing Modes,

- Interrupt Signals,

- Data Transfer