0% found this document useful (0 votes)

315 views4 pagesSlew-Rate Enhancement for Op-Amps

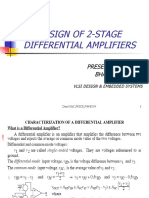

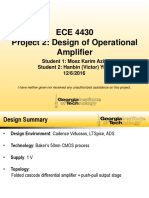

The document describes a technique to enhance the slew rate of one-stage operational amplifiers without increasing static power consumption. The technique adds two transistors that operate in triode region and generate a small drain-source voltage under normal conditions but a much larger voltage when maximum output current is needed. This allows the output current to increase almost an order of magnitude compared to a conventional design. Simulations show the slew rate enhanced amplifier achieves rise and fall times that are 4 times faster with peak transient currents almost 5 times larger, while maintaining the same supply requirements and with only a slight increase in static power.

Uploaded by

Shubham SharmaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

315 views4 pagesSlew-Rate Enhancement for Op-Amps

The document describes a technique to enhance the slew rate of one-stage operational amplifiers without increasing static power consumption. The technique adds two transistors that operate in triode region and generate a small drain-source voltage under normal conditions but a much larger voltage when maximum output current is needed. This allows the output current to increase almost an order of magnitude compared to a conventional design. Simulations show the slew rate enhanced amplifier achieves rise and fall times that are 4 times faster with peak transient currents almost 5 times larger, while maintaining the same supply requirements and with only a slight increase in static power.

Uploaded by

Shubham SharmaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd