Professional Documents

Culture Documents

Electronic Devices Quiz - 2 Notice

Electronic Devices Quiz - 2 Notice

Uploaded by

RishiOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electronic Devices Quiz - 2 Notice

Electronic Devices Quiz - 2 Notice

Uploaded by

RishiCopyright:

Available Formats

Electronic Devices Quiz – 2 Notice

Exam Date: 21/11/2019 (Thursday, 5 to 6 PM)

Exam weightage: 26 Marks; Exam questions: MCQ based questions; Exam type: Open Book

Open Book components: Handwritten class notes, mentioned text book, mentioned reference book,

photocopies of only these text & reference books (strictly no other books)

Please go through the detailed syllabus (topics wise)

From PN Junction (after midsem): Depletion capacitance, Diffusion capacitance, small signal equivalent model,

Tunnel diode, Forward bias Diode current, Reverse saturation current, 1/C^2 vs Voltage plot and from there doping

concentration or built-in potential calculation, Metal-Semiconductor contacts - Schottky diode and Ohmic contacts,

Forward bias Schottky Diode current, Reverse saturation current, Barrier height, and depletion width and internal

electric field of Schottky diode.

From MOSCAP: Accumulation-Depletion-Inversion in MOSCAP, surface potential, condition for inversion,

depletion width, max depletion width, Capacitance-voltage characteristics, accumulation-depletion-minimum-

inversion capacitances, metal-semiconductor work-function difference, flatband voltage, threshold voltage, effect of

fixed oxide charges on MOSCAP, and effects of N+ or P+ polysi Gate on MOSCAP.

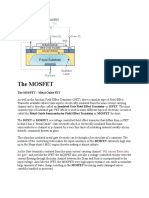

From MOSFETs: Basic difference between Enhancement mode and depletion mode MOSFET, Transfer

characteristics of MOSFET, Sub-threshold condition, Output characteristics, pinch off condition, Saturated drain

voltage and its relation with Gate and Threshold voltages, Drain current in active and saturation regions,

Transconductance (both in active & saturation regions), Output resistance, MOSFET small signal equivalent circuit

(both at low and high frequencies), Cut-off frequency in high frequency small signal equivalent circuit, effect of

source resistance on drain current, effect of short channel on MOSFET performances (surface scattering, drain

induced barrier lowering and its drain current relation), and how to further tune threshold voltage in MOSFET -

Effect of Body bias on threshold voltage; Effects of n+ polysilicon and p+ polysilicon gate on the threshold voltage

of n or p-channel MOSFETs (enhancement mode).

From JFETs: JFET Transfer characteristics - Drain current vs gate voltage (fixed drain voltage), transconductance,

Pinch off during transfer characteristics (turn off the device), channel conductance, depletion width in equilibrium

and with gate bias, corresponding internal pinch-off voltage, pinch-off voltage (applied gate voltage for which pinch-

off gets occurred), JFET output characteristics - Drain current vs drain voltage (fixed gate voltage) – active region,

saturation region, and cut-off region, depletion width with gate & drain bias, corresponding internal pinch-off

voltage, and drain saturation voltage (applied drain voltage for which pinch-off gets occurred).

Note: In class, for MOSFET, I have considered P-substrate (or n-channel) enhancement mode MOSFET, but go

through the N-substrate (or P-channel) MOSFET as well. On the other side, for JFET, I have considered n-channel

JFET, but go through the p-channel JFET. The operation will just be opposite; however the polarity in formulas will

be changed.

Seating arrangements:

Room F-102 & F-103: Only ECE (strictly NO EEE & INSTR) – 4 students/bench

Room F-105: Only EEE (Strictly NO ECE & INSTR) – 4 students/bench

Room F-104: Remaining EEE after F-105 + Remaining INSTR after F-107 (Strictly NO ECE) – 4

students/bench

Room F-107: Only INSTR (Strictly NO ECE & EEE) – 1 student/bench

Let’s maintain this seating arrangement so that I could track all the papers easily. Thanks!

Instructor In-charge

You might also like

- Sony KP Fx432m91Document220 pagesSony KP Fx432m91Iftikhar DaniNo ratings yet

- HPDesign Jet T120 T520 Upgrade ToolDocument26 pagesHPDesign Jet T120 T520 Upgrade ToolJorge Peralta OrozcoNo ratings yet

- Yamaha Gp1200 Owners ManualDocument3 pagesYamaha Gp1200 Owners ManualGregoryNo ratings yet

- Tweco Welding Catalogue 2001Document84 pagesTweco Welding Catalogue 2001Andrew Schroeder0% (1)

- MosfetDocument23 pagesMosfetgopikrishna yarlagaddaNo ratings yet

- Back To Basics Introduction To BJTs JFETs MESFETs and MOSFETsDocument28 pagesBack To Basics Introduction To BJTs JFETs MESFETs and MOSFETssonitha alvaNo ratings yet

- FETs 11Document55 pagesFETs 11بلسم محمود شاكرNo ratings yet

- 12-MOSFET - Structure and DC Characteristics-22!02!2024Document20 pages12-MOSFET - Structure and DC Characteristics-22!02!2024ashbinny1No ratings yet

- Lecture11!11!12284 MosfetDocument28 pagesLecture11!11!12284 Mosfetshivali.vannarathNo ratings yet

- AE - 1.7 MOSFET Circuits - DC Biasing, AC Coupling and Small-Signal Analysis of AmplifiersDocument65 pagesAE - 1.7 MOSFET Circuits - DC Biasing, AC Coupling and Small-Signal Analysis of AmplifiersjayanthiNo ratings yet

- Ed Unit 4Document32 pagesEd Unit 4Deepa.J DeeNo ratings yet

- Complete Vlsi NotesDocument160 pagesComplete Vlsi NotesTarun SinghalNo ratings yet

- Ecd LR - 1Document21 pagesEcd LR - 1Faaran Ahmed Zaheer AhmedNo ratings yet

- L2 Ivlsi 11012019Document31 pagesL2 Ivlsi 11012019naman mathurNo ratings yet

- Mini ProjectDocument25 pagesMini Projectcharan524No ratings yet

- 1 IntroductionDocument61 pages1 Introductionfiraol temesgenNo ratings yet

- 5 FET Part 1Document25 pages5 FET Part 1iamthebasselNo ratings yet

- Industrial Electronics Lecture-3 MosfetDocument13 pagesIndustrial Electronics Lecture-3 MosfetHamza TariqNo ratings yet

- Lesson 4 2 Semiconductors Diode Rectification PDFDocument39 pagesLesson 4 2 Semiconductors Diode Rectification PDFMuneNo ratings yet

- Debre Markos University Institute of Technology School of Electrical and Computer Engineering Computer Engineering (PG)Document10 pagesDebre Markos University Institute of Technology School of Electrical and Computer Engineering Computer Engineering (PG)enidegNo ratings yet

- Lab Manual: COURSE TITLE: - COURSE CODEDocument82 pagesLab Manual: COURSE TITLE: - COURSE CODEUmar AkhtarNo ratings yet

- Analog Circuits 2020 21Document1 pageAnalog Circuits 2020 21Padirikuppam PavithraNo ratings yet

- EC6201 Unit 3Document102 pagesEC6201 Unit 3Rajkumar PerumalNo ratings yet

- ECE221 MOSFETs-I SRMAP PDFDocument30 pagesECE221 MOSFETs-I SRMAP PDFRajeshNo ratings yet

- Lect 4,5,6,7 MOSFET Construction, Working Principle SND ChsrscteridticsDocument26 pagesLect 4,5,6,7 MOSFET Construction, Working Principle SND Chsrscteridticsshashikala kotiNo ratings yet

- Transistor: What Is A Transistor and How Does It WorkDocument7 pagesTransistor: What Is A Transistor and How Does It WorkmonalisaNo ratings yet

- Field Effect TransistorDocument13 pagesField Effect TransistorLORD TNo ratings yet

- Principles and Applications of MOSFET and JFET MosfetDocument5 pagesPrinciples and Applications of MOSFET and JFET MosfetKim KimNo ratings yet

- Mosfet Differential AmplifierDocument7 pagesMosfet Differential AmplifierSunil PandeyNo ratings yet

- Basic Electronics Engg Unit 2Document25 pagesBasic Electronics Engg Unit 2Harshal VaidyaNo ratings yet

- Mosfet and JfetDocument5 pagesMosfet and JfetJonarc Joseph VasquezNo ratings yet

- FALLSEM2022-23 BEEE102L TH VL2022230105984 Reference Material I 19-01-2023 003 MOSFETDocument22 pagesFALLSEM2022-23 BEEE102L TH VL2022230105984 Reference Material I 19-01-2023 003 MOSFETvishwadeepNo ratings yet

- Unit - 3Document8 pagesUnit - 3AgnathavasiNo ratings yet

- Complete Vlsi NotesDocument159 pagesComplete Vlsi NotesSUNIL MP75% (4)

- Chapter - 3 MOSFET AmplifiersDocument41 pagesChapter - 3 MOSFET AmplifiersNguyễn Phước Định TườngNo ratings yet

- Vlsi Group-B Q&aDocument13 pagesVlsi Group-B Q&aROHAN CHOWDHURYNo ratings yet

- EDID632C: Elementary Studies: Transistor FundamentalsDocument87 pagesEDID632C: Elementary Studies: Transistor Fundamentalsakash kumarNo ratings yet

- EDC JayalakshmiDocument90 pagesEDC Jayalakshmiandrew r fernandesNo ratings yet

- Mod 2Document55 pagesMod 2koushikraj900No ratings yet

- MOS Capacitors and Band Diagrams: Adding Citations To Reliable Sources RemovedDocument5 pagesMOS Capacitors and Band Diagrams: Adding Citations To Reliable Sources RemovedshohobiNo ratings yet

- Mosfet: A Seminar Report OnDocument11 pagesMosfet: A Seminar Report OnFrancisNo ratings yet

- Mosfet and BJT ReportDocument10 pagesMosfet and BJT ReportUmar AkhtarNo ratings yet

- MOSFET Interview Question AnswerDocument4 pagesMOSFET Interview Question AnswerAnkitMishraNo ratings yet

- Digital VLSI Design - Lecture 2Document24 pagesDigital VLSI Design - Lecture 2gobinathNo ratings yet

- Laboratory 5: Device Characteristics of nMOSFET: ObjectiveDocument8 pagesLaboratory 5: Device Characteristics of nMOSFET: ObjectiveRahul Kumar Meena0% (1)

- Dr. B. Bindu, Associate Professor, SenseDocument26 pagesDr. B. Bindu, Associate Professor, SenseAmal JohnNo ratings yet

- Course Name: Basic Electronics Engineering Course Code: EC101 Metal Oxide Semiconductor Field Effect Transistor (MOSFET)Document37 pagesCourse Name: Basic Electronics Engineering Course Code: EC101 Metal Oxide Semiconductor Field Effect Transistor (MOSFET)Dr Sunipa RoyNo ratings yet

- BUET Admission Test Study MaterialsDocument3 pagesBUET Admission Test Study MaterialsShahriar RumiNo ratings yet

- VLSI Design Important Questions On MOSFET For Exams: VoltageDocument5 pagesVLSI Design Important Questions On MOSFET For Exams: VoltageTarun SinghalNo ratings yet

- BEng FETDocument13 pagesBEng FETJai GaizinNo ratings yet

- The Mosfet: Home TransistorsDocument10 pagesThe Mosfet: Home TransistorsPrabashaNo ratings yet

- Chapter 5Document31 pagesChapter 5api-394738731No ratings yet

- Field-Effect Transistor: DR - Debashis de Associate Professor West Bengal University of TechnologyDocument23 pagesField-Effect Transistor: DR - Debashis de Associate Professor West Bengal University of TechnologySelva KumarNo ratings yet

- BUET SuggestionsDocument3 pagesBUET SuggestionsTanvir Alam ShishirNo ratings yet

- Metal Oxide Semiconductor Field Effect Transisitor AssignmentDocument20 pagesMetal Oxide Semiconductor Field Effect Transisitor AssignmentSokoine Hamad DenisNo ratings yet

- School of Electrical Engineering Department of Electrical EngineeringDocument8 pagesSchool of Electrical Engineering Department of Electrical EngineeringvbjioNo ratings yet

- Presented: Presentation On Jfet & MosfetDocument19 pagesPresented: Presentation On Jfet & MosfetManik MiaNo ratings yet

- Igfet'S Insulated Gate Field Effect TransistorsDocument4 pagesIgfet'S Insulated Gate Field Effect TransistorsAnonymous xzi9LiTNo ratings yet

- ETI 2203 Lesson 7Document10 pagesETI 2203 Lesson 7amash.emillyNo ratings yet

- A Field Effect Transistor WordDocument4 pagesA Field Effect Transistor Wordshalil hamidNo ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- STEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10From EverandSTEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10No ratings yet

- AN11130Document14 pagesAN11130RajasekarNo ratings yet

- Bus Diagnosis All Models From E60Document8 pagesBus Diagnosis All Models From E60Iongornistu0% (1)

- BLN-09947 Rev F Series 90 Axial Piston PumpsDocument88 pagesBLN-09947 Rev F Series 90 Axial Piston PumpsGabriel Amorim100% (1)

- Biaya Service Nissan MarchDocument2 pagesBiaya Service Nissan MarchSandy PrakosoNo ratings yet

- BTL Vac - User ManualDocument17 pagesBTL Vac - User Manualamerico.villarrealNo ratings yet

- D7R Track Type Tractor Electrical System (Differential Steer)Document2 pagesD7R Track Type Tractor Electrical System (Differential Steer)JorgeNo ratings yet

- Model Ventable, Pilot Operated, Balanced Piston Relief ValveDocument2 pagesModel Ventable, Pilot Operated, Balanced Piston Relief ValveErasmo LimaNo ratings yet

- Enstrom F28F 280F MM Rev 04 1994 PDFDocument655 pagesEnstrom F28F 280F MM Rev 04 1994 PDFstjepan100% (1)

- Power Cords Plugs TypesDocument1 pagePower Cords Plugs TypesAli SalemNo ratings yet

- Battery Maintenance and TroubleshootingDocument20 pagesBattery Maintenance and TroubleshootingProteksitrans1 p3bsNo ratings yet

- Dump TruckDocument4 pagesDump TruckHugo RodriguezNo ratings yet

- WorldRef - Boiler & Heating SolutionsDocument2 pagesWorldRef - Boiler & Heating SolutionsHarsh KumarNo ratings yet

- Daikin Casette 3 PK, SC-71K, FHYC71K (Indoor) + Outdoor)Document2 pagesDaikin Casette 3 PK, SC-71K, FHYC71K (Indoor) + Outdoor)Ware HandokoNo ratings yet

- Wireless Communication With Ir Based Projects:: Project Code Title of The Project Description Cost MIR01Document2 pagesWireless Communication With Ir Based Projects:: Project Code Title of The Project Description Cost MIR01nagasaikiran ponnapalliNo ratings yet

- Catalog - VIEWSKY® Roof Top TentDocument13 pagesCatalog - VIEWSKY® Roof Top TentSunMori IndustiralNo ratings yet

- Mazda cx5 2018Document15 pagesMazda cx5 2018bumbum1111No ratings yet

- Advanced Vehicle Technologies, Inc.: Controller Area Network (CAN)Document12 pagesAdvanced Vehicle Technologies, Inc.: Controller Area Network (CAN)WelleyNo ratings yet

- Transition-Mode PFC Controller: FeaturesDocument26 pagesTransition-Mode PFC Controller: FeaturesMariusNo ratings yet

- To Construct A Portable Mobile ChargerDocument5 pagesTo Construct A Portable Mobile ChargerADARSH TECHY PRADHANNo ratings yet

- Pneumatic Purification: FiltrationDocument6 pagesPneumatic Purification: Filtrationherysyam1980No ratings yet

- Hspice OptimizationDocument8 pagesHspice OptimizationAnand ThibbaiahNo ratings yet

- Sebp3781 86 01 AllDocument1,089 pagesSebp3781 86 01 AllRonald AparicioNo ratings yet

- Vibratory Soil Compactor: Stage II CompliantDocument12 pagesVibratory Soil Compactor: Stage II Compliantguillermo springNo ratings yet

- Resistron: Operating InstructionsDocument51 pagesResistron: Operating Instructions16_45_2013_gabri0% (1)

- Specifications: UT682 Series Wire TrackersDocument1 pageSpecifications: UT682 Series Wire TrackersR Esfandyari100% (1)