Professional Documents

Culture Documents

Hardwired Controler Brief PDF

Hardwired Controler Brief PDF

Uploaded by

AKSHAT GARGOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Hardwired Controler Brief PDF

Hardwired Controler Brief PDF

Uploaded by

AKSHAT GARGCopyright:

Available Formats

Hard-wired Controller

Hardware components-

Memory (2048*16bit)

MDR, AC -16bit

MAR, PC -12bit

(PC, MDR, MAR with increment and Clear signals)

Input output registers- INP, OUP - 8bit

ALU works with AC only and carry is indicated by flag E

Interrupt flag R (R sets When IE is set and any or both of FGI/FGO set)(when processor s interrupted , interrupt cycle resets R)

Interrupt Enable Flip flop is IE (set / reset by instruction ION / IOF)

Input and Output operation also set/reset flags FGI and FGO

(FGI set when external device write data in INP register. When INP read by processor it resets FGI)

(FGO is reset by processor when new data is written in OUP. Set by external device when it reads OUP)

A sequence generator(SG) generates 8 clocks (SG is reset by instruction after its completion. Disable signal to SG is controlled by instruction HLT.

SG is enabled from external switch)

Following instructions are incorporated-

memory reference instructions-

AND, ADD, LDA, STA, BUN(branch unconditional), BSA(branch and save return address), ISZ (increment memory and skip next instruction if memory

becomes zero)

(These are MRI. Memory can be referred directly (given address contains info. ) or indirectly (given address contains the address where the info. is stored ) )

Non MRI -Register based instructions-

CLA (AC=0), CLE(E=0), CMA(AC=1's complement of A), CME(E=1's complement of E), CIR(AC rotates right with E),CIL(AC rotates LEFT with

E),INC(Ac=AC+1), SPA(skip next instruction if A15=0),SNA(skip next instruction if A15=1),SZA(skip next instruction if AC=0),SZE(skip next instruction if

E=0),HLT(disable sequence generator)

Non MRI -I/O based instructions-

IN,OUT,SKI(skip next instruction if FGI=1),SKO(skip next instruction if FGO=1),ION(enable IE F/F),IOF(disable IE F/F)

Format of16-bit instruction-

15 14 12 11 0

I opcode Address/non mri inst. bits

3-bits of opcode selects one of the 7 mri instruction(000 to 110) or non mri instructions(111)

I in case of mri , identifies direct(I=0) or indirect (I=1) instructions

in case of non mri instructions register reference (I=0) or I/O reference (I=1) instructions

12-bit , in mri refers address, in case of non mri it identifies register or IO instruction

Flow chart of normal instruction execution-

Flow chart of interrupt execution-

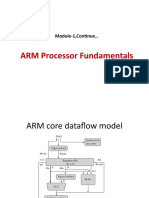

Micro operations of hardwired controller

(normal execution R=0)

R'T0 : MAR <- PC

R'T1 : MDR<- M[MAR] , PC <- PC+1

R'T2 : MAR <- MDR(11-0), I <- MDR(15), Decoder <-MDR(14-12)

(interrupt execution R=1, first two memory locations for interrupt handling data and instruction)

RT0 : MAR <- 0, MDR<-PC

RT1 : M[MAR] <- MDR

RT2 : PC <- 0

RT3 : PC <- 1 , IEN <- 0 ,R <- 0 ;Reset

(In non-mri instruction, when I=0, T3,T4 cycle is idle)

D'7IT3 : MDR <- M[MAR]

D'7IT4 : MAR <- MDR

memory reference Instructions

AND BUN

D0T5 : MDR <- M[MAR] D4T5 : PC <-MAR , Reset

D0T6 :AC <-AC . MDR , Reset

ADD BSA

D1T5 : MDR <- M[MAR] D5T5 : MDR <-PC

D1T6 : AC <-AC + MDR ,E <-carry , Reset D5T6 : M[MAR]<- MDR, MAR <-MAR+1

D5T7 : PC <-MAR , Reset

LDA ISZ

D2T5 : MDR <- M[MAR] D6T5 : MDR <- M[MAR]

D2T6 : AC <-MDR , Reset D6T6 : MDR <-MDR+1

D6T7 : M[MAR] <-MDR, if MDR=0, PC<-PC+1, Reset

STA

D3T5 : MDR <-AC , Reset

D3T6 : M[MAR] <-MDR , Reset

Register instructions- I/O instructions-

D7I' (conditional for register reference instruction) D7I (conditional for I/O reference instruction) Address

Address bits- b11 to b0 used to identify particular bits- b11 to b0 used to identify particular instruction

instruction D7IT3b11 – IN ; AC< INP, FGI=0; Reset

D7I'T3b11 - CLA ; AC<-0; Reset D7IT3b10 – OUT ; OUP<-AC, FGO=0; Reset

D7I'T3b10 - CLE ; E<-0; Reset D7IT3b9 – SKI ; if FGI =1 ,PC<-PC+1 ; Reset

D7I'T3b9 - CMA ; AC<- 1's complement of AC; Reset D7IT3b8 – SKO ; if FGO =1 ,PC<-PC+1 ; Reset

D7I'T3b8 - CME ; E<- 1's complement of E; Reset D7IT3b7 – ION ; IE=1 ; Reset

D7I'T3b7 – CIR ; A15<-E,...............E<-A0; Reset D7IT3b6 – IOF ; IE=0 ; Reset

D7I'T3b6 – CIL ; A0<-E,...............E<-A15; Reset

D7I'T3b5 – INC ; AC<- AC+1; Reset

D7I'T3b4 – SPA ; if A15=0 , PC<-PC+1 ; Reset

D7I'T3b3 – SNA ; if A15=1 , PC<-PC+1 ; Reset

D7I'T3b2 – SZA ; if AC=0 , PC<-PC+1 ; Reset

D7I'T3b1 – SZE ; if E=0 , PC<-PC+1 ; Reset

D7I'T3b0 – HLT ;disable SG

Control signals

example for PC- has four control signals – enable(read), load(write),increment, clear and clock

PC(E) – T0+D5T5+

PC(L) - D4T5+D5T6

PC(I)- R'T1+RT3+D6T7(MDR')+D7I'T3b4(A15')+D7I'T3b3(A15)+D7I'T3b2(AC')+D7I'T3b1(E')+D7IT3b9(FGI)+D7IT3b8(FGO)

PC( c) - RT2

Design combinational circuit using these control signals for PC

MAR- has four control signals – enable(read), load(write),increment, clear and clock

MDR- has three control signals – enable(read), load(write),increment, and clock

Memory- has two control signals – enable(read), load(write),

AC -

Circuit for interrupt ( R and IE flags)

(To'T1'T2')(IE)(FGI+FGO) sets R flag

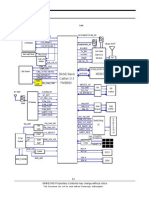

Complete schematic diagram showing all hardware components ,and logic circuit to generate control signals -

You might also like

- Korg SP-100 Service ManualDocument23 pagesKorg SP-100 Service ManualKolja80% (5)

- Requirements Engineering For Software and Systems by Phillip A. LaplanteDocument399 pagesRequirements Engineering For Software and Systems by Phillip A. LaplanteMateo Rossi80% (5)

- AnswerDocument10 pagesAnswerSurekhaben Shah56% (9)

- Oracle Flow Manufacturing - Process FlowDocument31 pagesOracle Flow Manufacturing - Process FlowPritesh MoganeNo ratings yet

- ROC and FloBoss Modbus Slave ConfigurationDocument12 pagesROC and FloBoss Modbus Slave ConfigurationJhon Jairo Sierra ContrerasNo ratings yet

- Ecdis: Instruction ManualDocument370 pagesEcdis: Instruction ManualМилен ДолапчиевNo ratings yet

- Rethink Social 10 FebDocument2 pagesRethink Social 10 FebJamesNo ratings yet

- Hardwired Controler BriefDocument2 pagesHardwired Controler BriefDeepak majhiNo ratings yet

- ch5 SolDocument9 pagesch5 Solblue_fire_englandNo ratings yet

- Mk7a25p v06Document53 pagesMk7a25p v06אור מהללאל בן השםNo ratings yet

- Basic Computer OrganizationMemory Reference InstructionsDocument9 pagesBasic Computer OrganizationMemory Reference InstructionsHARI HARAN REDDYNo ratings yet

- Lecture 29Document10 pagesLecture 29Roopali AgarwalNo ratings yet

- Samsung Plasma Training ManualDocument57 pagesSamsung Plasma Training Manualedsel72100% (2)

- Chapter SevenDocument29 pagesChapter Sevenremi1989No ratings yet

- Design Task 1 Final LabDocument15 pagesDesign Task 1 Final Labrazorblademk2No ratings yet

- Lecture 24Document8 pagesLecture 24Roopali AgarwalNo ratings yet

- Week 04Document68 pagesWeek 04aroosa naheedNo ratings yet

- Lecture 21Document10 pagesLecture 21VINAYNo ratings yet

- General Description: MK7A25PDocument53 pagesGeneral Description: MK7A25Pאור מהללאל בן השםNo ratings yet

- 08 GT E2530 Tshoo 7Document44 pages08 GT E2530 Tshoo 7Fabiomarferreira100% (1)

- Unit 2 Mcu PDFDocument12 pagesUnit 2 Mcu PDFatulNo ratings yet

- Question No. 2 How Snmpv3 Enhances Security Compared To Snmpv2? Question No. 3 A) Define Rmon B) What Are The Benefits of Rmon ?Document32 pagesQuestion No. 2 How Snmpv3 Enhances Security Compared To Snmpv2? Question No. 3 A) Define Rmon B) What Are The Benefits of Rmon ?shravaniNo ratings yet

- Basic Computer Organization and DesignDocument35 pagesBasic Computer Organization and DesignVinay KumarNo ratings yet

- F 818Document9 pagesF 818Eric YangNo ratings yet

- Ccs-Picc - HTML: // LCD Module ConnectionsDocument5 pagesCcs-Picc - HTML: // LCD Module ConnectionsagreykatoNo ratings yet

- About 2G Integration (CIG, Alarms, Dump)Document4 pagesAbout 2G Integration (CIG, Alarms, Dump)Aziz AbassiNo ratings yet

- Lab 14Document10 pagesLab 14ubaidNo ratings yet

- IC 8155 InformationDocument13 pagesIC 8155 InformationKajol PhadtareNo ratings yet

- Lecture 22Document8 pagesLecture 22VINAYNo ratings yet

- CA SolutionDocument14 pagesCA SolutionSaba InamNo ratings yet

- Lecture-25 7. SUB R: This Is A Single Byte Instruction. The Meaning of TheDocument9 pagesLecture-25 7. SUB R: This Is A Single Byte Instruction. The Meaning of TheWilliamNo ratings yet

- PS2 EE SIO InfoDocument5 pagesPS2 EE SIO InfozokiNo ratings yet

- G2B and G3B CANopen FDocument12 pagesG2B and G3B CANopen Fangel silvaNo ratings yet

- CombinepdfDocument14 pagesCombinepdfDuoDrenchNo ratings yet

- Sechtor300 Job AidDocument10 pagesSechtor300 Job AidGreg WilliamsNo ratings yet

- S7-200 Quick Reference Information: Special Memory BitsDocument6 pagesS7-200 Quick Reference Information: Special Memory BitspremchandarNo ratings yet

- Kenwood Kdc-4047ua 414um Kdc-Mp245u U3046 U346 U4046Document46 pagesKenwood Kdc-4047ua 414um Kdc-Mp245u U3046 U346 U4046Oscar DalisNo ratings yet

- ADCTest 2Document4 pagesADCTest 2JasonNo ratings yet

- 7-1 Overall Block DiagramDocument4 pages7-1 Overall Block DiagramCraig KalinowskiNo ratings yet

- MicroControllers HandbookDocument13 pagesMicroControllers Handbookjhon doeNo ratings yet

- Engr2105 Lab3Document8 pagesEngr2105 Lab3SUPER AMAZINGNo ratings yet

- Pic 16 F 628Document20 pagesPic 16 F 628Merényi Oszkár100% (1)

- AN957 - dsPIC33FJ12MC202 VersionDocument3 pagesAN957 - dsPIC33FJ12MC202 VersiontedozallennNo ratings yet

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocument8 pagesCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhNo ratings yet

- Compaq Presario CQ45 SchematicsDocument48 pagesCompaq Presario CQ45 Schematicsmeng798651No ratings yet

- Exercise - 4: EE443 - Embedded SystemsDocument4 pagesExercise - 4: EE443 - Embedded SystemscraticNo ratings yet

- Lab Set Ii - ReportDocument7 pagesLab Set Ii - ReportEZRA MOHAMMEDNo ratings yet

- Dan's Fanuc Spindle InfoDocument13 pagesDan's Fanuc Spindle InfoPham LongNo ratings yet

- Hcs12 Instruction Set SummaryDocument15 pagesHcs12 Instruction Set SummaryRedduan HarisNo ratings yet

- Atmega16 Enc28j60 WebserverDocument1 pageAtmega16 Enc28j60 WebserverTaher VohraNo ratings yet

- LI3 Retiene KR2Document3 pagesLI3 Retiene KR2Aga MenonNo ratings yet

- Samsung LN-S3292D LN-S4092D LN-S4692D Alignment & Adjustment (SM)Document12 pagesSamsung LN-S3292D LN-S4092D LN-S4692D Alignment & Adjustment (SM)Carlos OdilonNo ratings yet

- m62424 SPDocument17 pagesm62424 SPRizal AssegafNo ratings yet

- Ampotor: Resistors Capacitors Microamp Parts ListDocument1 pageAmpotor: Resistors Capacitors Microamp Parts Listgorgor2No ratings yet

- Ampotor: Resistors Capacitors Microamp Parts ListDocument1 pageAmpotor: Resistors Capacitors Microamp Parts ListcesarhracNo ratings yet

- Ampotor: Resistors Capacitors Microamp Parts ListDocument1 pageAmpotor: Resistors Capacitors Microamp Parts ListSDanielTorresPachasNo ratings yet

- Quiz 3 SolutionsDocument3 pagesQuiz 3 SolutionsP o o P o o H e a dNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysFrom EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo ratings yet

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- ECM Replacement FileDocument5 pagesECM Replacement FilePaul GalwezNo ratings yet

- Oracle: Oracle Cloud Infrastructure Foundation 2020Document22 pagesOracle: Oracle Cloud Infrastructure Foundation 2020Manish NayakNo ratings yet

- Webdispatcher ConfigurationDocument2 pagesWebdispatcher Configurationjaxil34452No ratings yet

- Review Pro User-ManualDocument40 pagesReview Pro User-ManualJuan PabloNo ratings yet

- Von Mises-Fisher Mixture Model-Based Deep Learning: Application To Face VerificationDocument16 pagesVon Mises-Fisher Mixture Model-Based Deep Learning: Application To Face Verificationassasaa asasaNo ratings yet

- The Pirat BayDocument2 pagesThe Pirat BayValera StrungariNo ratings yet

- MC 7Document36 pagesMC 7Muskan KhannNo ratings yet

- An Energy-Saving and Cost-Reduction Bandwidth Monitoring Model Using PRTG Monitoring SoftwareDocument7 pagesAn Energy-Saving and Cost-Reduction Bandwidth Monitoring Model Using PRTG Monitoring SoftwareInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Transformer&Reactor Protection PCS-978Document4 pagesTransformer&Reactor Protection PCS-978ganeshNo ratings yet

- Autosar SWS VFBDocument77 pagesAutosar SWS VFBAbbigeri VishwanathNo ratings yet

- In-Cell Capacitive Touch Panel Structures and Their Readout CircuitsDocument5 pagesIn-Cell Capacitive Touch Panel Structures and Their Readout CircuitsMaria Cristina López AreizaNo ratings yet

- An Automated Vehicle Parking Monitoring and Management System Using ANPR CamerasDocument6 pagesAn Automated Vehicle Parking Monitoring and Management System Using ANPR Camerasmas zak danielNo ratings yet

- Review On Topic Detection Methods For Twitter StreamsDocument5 pagesReview On Topic Detection Methods For Twitter StreamsInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Chapter 3 Operating System OverviewDocument50 pagesChapter 3 Operating System OverviewshalvenNo ratings yet

- Dash Cam, Full HD 1080p: User ManualDocument14 pagesDash Cam, Full HD 1080p: User ManualLeonardoNo ratings yet

- Executive Support System (ESS)Document6 pagesExecutive Support System (ESS)suraj_simkhadaNo ratings yet

- IPC6325Document1 pageIPC6325hasitha neelakaNo ratings yet

- Drdo Person ResumeDocument3 pagesDrdo Person ResumeYoutube UNo ratings yet

- 18CS44 MODULE1 Chapter2Document38 pages18CS44 MODULE1 Chapter2Jim MoriartyNo ratings yet

- g100 InstallationDocument8 pagesg100 InstallationAndi PrengaNo ratings yet

- 10.SQL Queriesaggregate FunctionsDocument14 pages10.SQL Queriesaggregate FunctionsAnkit RajputNo ratings yet

- Listening - Practice Test IDocument37 pagesListening - Practice Test IRamil BondadNo ratings yet

- Deedy CVDocument1 pageDeedy CVayushrastogi689No ratings yet

- #Include #Include #Include #Include #Include #Include #Include #Include #Include #Include #Include #Include #Include #IncludeDocument4 pages#Include #Include #Include #Include #Include #Include #Include #Include #Include #Include #Include #Include #Include #IncludeiDenisNo ratings yet