Professional Documents

Culture Documents

Electronics Ch13 PDF

Uploaded by

Abdullah MuzammilOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electronics Ch13 PDF

Uploaded by

Abdullah MuzammilCopyright:

Available Formats

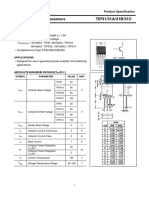

CHAPTER 13 OUTPUT STAGES AND POWER AMPLIFIERS

Chapter Outline

13.1 Classification of Output Stages

13.2 Class A Output Stage

13.3 Class B Output Stage

13.4 Class AB Output Stage

13.5 Biasing the Class AB Circuit

13.6 CMOS Class AB Output p Stages

g

NTUEE Electronics III 13-1

13.1 CLASSIFICATIONS OF OUTPUT STAGES

Output Stages

Class A output stage:

Bias current is greater than the magnitude of the signal current

Conduction angle is 360

Class B output stage:

Biased at zero dc current

Conduction angle is 180

Another transistor conducts during the alternate half-cycle

Class AB output stage:

AnA iintermediate

t di t class

l between

b t A andd B

Biased at a nonzero dc current much smaller than the peak current of the signal

Conduction angle is greater than 180 but much smaller than 360

Two transistors are used and currents are combined at the load

Class C output stage:

Conduction angle is smaller than 180

The current is passed through a parallel LC network to obtain the output signal

Class A, B and AB are used as output stage of op amps

Class AB amplifiers are preferred for audio power amplifier

Class C amplifiers are usually used at higher frequencies

NTUEE Electronics III 13-2

Collector current waveforms for the transistors operating in different classes

The classification also applies for output stages with MOSFETs

NTUEE Electronics III 13-3

13.2 CLASS A OUTPUT STAGE

Transfer Characteristics

Q1 biased with a constant current I supplied by Q2

vO vI vBE1

vO max VCC VCE1sat

vO min IRL or vO min VCC VCE 2 sat

| VCC VCE 2 sat |

I

RL

Si

Signal

l Waveforms

W f

The output swing from VCC to VCC for I = VCC/RL

The instantaneous power dissipation in Q1: PD1 = vCE1iC1

NTUEE Electronics III 13-4

Power Dissipation

Power dissipation for RL = VCC/I:

The maximum instantaneous power dissipation in Q1 is VCCI

This is equal to the power dissipation in Q1 with no input signal

applied (quiescent power dissipation)

The transistor Q1 much be able to withstand a continuous power

dissipation of VCCI

Power dissipation for unloaded case:

Maximum power dissipation occurs when vO = VCC

The maximum power dissipation in Q1 is 2VCCI

Power dissipation for an output short circuit:

A positive input may lead to an infinite load current

The output stages are usually equipped with short-circuit protection to guard against such a situation

Power dissipation in Q2:

Q2 conducts a constant current I

Maximum voltage across the collector and the emitter is 2VCC

Maximum instantaneous power dissipation in Q2 is 2VCCI

A more significant quantity for design purposes is the average power dissipation of VCCI

NTUEE Electronics III 13-5

Power Conversion Efficiency

The power conversion efficiency is defined as PL(load power) /PS(supply power)

The load power (PL) with an sinusoid output with a peak value of Vo is

(Vo / 2 ) 2 1 Vo2

PL

RL 2 RL

The total average supply power is PS = 2VCCI

The conversion efficiency is given by

1 Vo2 1 Vo Vo

4 IRLVCC 4 IRL VCC

Maximum efficiency (25%) is obtained when Vo VCC IRL

Class A output stage is rarely used in high-power applications

The efficiency achieved in practice is usually in the range of 10% to 20%

NTUEE Electronics III 13-6

13.3 CLASS B OUTPUT STAGE

Circuit Operation

Both transistors are cut off when vI is zero vO is zero

One of the transistor turns on as vI exceeds 0.5 V vO follows vI

The circuit operates in a push-pull fashion

The class B stage is biased at zero current and conducts only when

the input signal is present

Transfer Characteristic

There exists a range of input centered around zero

where both QN and QP are off

The transfer characteristic shows a dead band

which results in the crossover distortion at the output

NTUEE Electronics III 13-7

Power Conversion Efficiency

The average

load power by neglecting the cross-over distortion is

1 Vo2

PL

2 RL

The current drawn from each supply consists of half-sine waves of peak amplitude Vo / RL

The average power

drawn from each of the two power supply is

1 Vo

PS PS VCC

RL

The total

supply power is

2 Vo

PS VCC

RL

The

Th efficiency

ffi i is

i given

i by

b

Vo

4 VCC

Maximum efficiency is obtained when the output swing is maximized ( VCC):

78.5%

4

The maximum

average power available from a class B stage is

1 Vo2

PL

2 RL

NTUEE Electronics III 13-8

Power Dissipation

The quiescent power dissipation of the class B stage is zero (unlike class A)

The average power dissipation of the class B stage is given by PD = PS PL

2 Vo 1 Vo2

PD VCC

RL 2 RL

QN and QP must be capable of safely dissipating half of PD

PD depends on the output swing and the worst-case power dissipation is given by

2 2

2 VCC

Vo VCC PD max

RL

PD max

The maximum power dissipation of QN and QP occurs at = 50%:

2

1 VCC

PDN max PDP max

RL

NTUEE Electronics III 13-9

Reducing Crossover Distortion

The distortion can be reduced by employing a high-gain op amp and overall negative feedback

The 0.7V dead band is reduced by a factor of the dc gain of the op amp

The slew rate limitation of the op amp may cause the alternate turning on and off to be noticable

Single-Supply Operation

The class B stage can be operated from a single supply

The load is capacitivelu coupled

The derivations are directly applicable with supply of 2VCC

NTUEE Electronics III 13-10

13.4 CLASS AB OUTPUT STAGE

Circuit Operation

Cross-over distortion can be eliminated by biasing QN and QP at a small nonzero current

The bias current iN = iP = IQ = Isexp(VBB/2VT)

When vI goes positive by a certain amount:

vO vI VBB / 2 vBEN

vBEN vBEP VBB

iN i I

VT ln VT ln P 2VT ln Q iN iP I Q2 iN2 iN iL I Q2 0

IS IS IS

The load current is supplied by QN which acts as the output emitter follower

QP will be conducting a current that decreases as vO increases (negligible for large vO)

QP acts as the output emitter follower when vI goes negative

The power properties are almost identical to those derived for the class B stage

NTUEE Electronics III 13-11

Output Resistance

The output resistance is estimated by assuming the source supply vI ideal

VT VT V

Rout reN || reP || T

i N iP i N i P

The output resistance remains approximately constant in the region around vI = 0

The output resistance decreases at larger load currents

NTUEE Electronics III 13-12

13.5 BIASING THE CLASS AB CIRCUIT

Biasing Using Diodes

The bias voltage VBB is generated by passing a constant current IBIAS through a pair of diodes

The diodes need not to be large devices

Quiescent current IQ in QN and QP will be IQ = nIBIAS where n is the ratio of the areas of the emitter

junction of the BJT and the junction area of the diodes

IBN increases from IQ/N to IL/N for a positive vO

IBIAS has to be greater than the IBN for maximum IL case

The ratio n cannot be a large number as n = IQ/IBIAS

This biasing arrangement provides thermal stabilization of the quiescent current in the output stage

Collect current increases with temperature

p for a fixed VBE

Heat from power dissipation increases with current

Positive feedback may cause thermal runaway

VBB decreases at the same rate of VBEN + VEBP

Thermal runaway is alleviated with close thermal contact

NTUEE Electronics III 13-13

Biasing Using the Voltage Multiplier

The class AB stage can be biased by VBE multiplier

I R VBE1 / R1

VBB VBE1 (1 R2 / R1 )

The value of VBE1 is determined by the portion of IBIAS that flows through the collector of Q1

I C1 I BIAS I R

I I C1

VBE1 VT ln C1 VT ln

IS I BIAS I R

The quiescent current can be adjusted by the resistance value

NTUEE Electronics III 13-14

13.6 CMOS CLASS AB OUTPUT STAGES

The Classical Configuration

Circuit operation

VGG VGS1 VSG 2 Vtn | Vtp | 2 I BIAS

1 1

k n (W / L)1 k p (W / L) 2

VGG VGSN VSGP Vtn | Vtp | 2 I Q

1 1

k n (W / L) n k p (W / L) p

2

1 / k (W / L) 1 / k p (W / L) 2

I Q I BIAS n 1

1 / kn (W / L) n 1 / k p (W / L) p

For the case Q1 and Q2 are matched and QP and QN are matched:

(W / L) n

I Q I BIAS

(W / L)1

A drawback of the CMOS class AB circuit is the restricted range of output voltage swing

vO max VDD VOV |BIAS Vtn vOVN

vO min VSS VOV | I | Vtp | | vOVP |

where

vOVN is the overdrive voltage of QN when it is supplying iLmax

and

|vOVP| is the overdrive voltage of QP when sinking the maximum negative value of iL

NTUEE Electronics III 13-15

An Alternative Circuit Using Common-Source Transistors

The allowable output range can be increased by replacing the source followers with a pair of

complementary transistors in the common-source configuration

QP supplies the load current when vO is positive, allowing an output as high as VDD |vOVP|

QN sinks the load current when vO is negative, allowing an output as low as VSS + vOVN

The disadvantage is its high output resistance Rout = ron||rop

Negative feedback (error amplifiers) is employed to reduce the output resistance

NTUEE Electronics III 13-16

Output Resistance

The output resistance is derived by two half circuits: Rout Routn || Routp

The analysis techniques for feedback (shunt-series feedback) is utilized:

vo

1 and A g mp ( rop || RL )

vi

The open-loop output resistance: Ro RL || rop

The output resistance with feedback: Rof Ro /(1 A) ( RL || rop ) /[1 g m ( RL || rop )]

1 1

The output resistance excluding RL: Routp 1 /(1 / Rof 1 / RL ) rop ||

g mp g mp

Overall output resistance: Rout 1 / ( g mp g mn )

NTUEE Electronics III 13-17

The Voltage Transfer Characteristics

1

For the case where QN and QP are matched: I Q kVOV

2

2

2 2

v v v v

Drain currents: iDN I Q 1 O I and iDP I Q 1 O I

VOV VOV

Load current: iL iDP iDN

VOV VOV

Output voltage: vO vI /1 v I 1

4I Q RL 4I R

Q L

VOV VOV

Gain error: vO vI

4I Q RL 2g m RL

NTUEE Electronics III 13-18

You might also like

- Mod 3 PDFDocument22 pagesMod 3 PDFcynthiaNo ratings yet

- Chapter 8Document34 pagesChapter 8Abhinav GuptaNo ratings yet

- Power Amplifier (Part 2)Document29 pagesPower Amplifier (Part 2)Ahmad FadliNo ratings yet

- 2022 2023 Tri 3 EEE1046 Chapter 2B Practical Op Amp LimitationsDocument40 pages2022 2023 Tri 3 EEE1046 Chapter 2B Practical Op Amp Limitationsj2yshjzzsxNo ratings yet

- Ea 1Document20 pagesEa 1SutantoNo ratings yet

- Unit - 1 Operational Amplifier FundamentalsDocument23 pagesUnit - 1 Operational Amplifier FundamentalsWaleed HåšhįmNo ratings yet

- Inside 741opampDocument63 pagesInside 741opampRaja NaiduNo ratings yet

- Experiment # 1 (Finals)Document14 pagesExperiment # 1 (Finals)John Mickelson FaustinoNo ratings yet

- Ch8 Output Stages and Power AmplifiersDocument20 pagesCh8 Output Stages and Power Amplifiers陳冠邑No ratings yet

- Co-3 MaterialDocument35 pagesCo-3 MaterialMLM TELUGU GAMERSNo ratings yet

- Unit 4 InvertersDocument86 pagesUnit 4 InvertersHaritha RkNo ratings yet

- Amplifier A PrelabDocument7 pagesAmplifier A Prelabatomking73No ratings yet

- Diode ModifiedDocument77 pagesDiode Modifiedronaldbolorbaral8809No ratings yet

- Chapter 2Document7 pagesChapter 2JohnNo ratings yet

- Basic Electro - Module 3 - KtuQbankDocument21 pagesBasic Electro - Module 3 - KtuQbankveenau 1No ratings yet

- AEC Exp 6 ManualDocument9 pagesAEC Exp 6 ManualChandrahasa reddy ENo ratings yet

- 02 # 01 Output Stages and Power Amplifiers 2017Document112 pages02 # 01 Output Stages and Power Amplifiers 2017Febrian Winzton HutagalungNo ratings yet

- Diodes and Applications FinalDocument117 pagesDiodes and Applications FinalCris Diane G. DatingginooNo ratings yet

- Power Audio Amplifier Ic Lm380Document5 pagesPower Audio Amplifier Ic Lm380VelmuruganNo ratings yet

- Power Supply Lecture For CpEDocument82 pagesPower Supply Lecture For CpEvj hernandezNo ratings yet

- Poweramplifiers 120119221518 Phpapp02Document32 pagesPoweramplifiers 120119221518 Phpapp02shankar1577100% (1)

- Cascode BJT CircuitDocument6 pagesCascode BJT CircuitAsim Khan NiaziNo ratings yet

- Transito RampDocument30 pagesTransito RampMarium AliNo ratings yet

- Chapter 1c (RECTIFIER)Document15 pagesChapter 1c (RECTIFIER)Akmal Amyrul Aizat100% (1)

- Half Wave and Full Wave RectifierDocument6 pagesHalf Wave and Full Wave RectifierBilal KhanNo ratings yet

- Power AmplifiersDocument51 pagesPower AmplifiersRiyaz Khan PathanNo ratings yet

- Chapter 2 DIODE APPLICATIONSDocument81 pagesChapter 2 DIODE APPLICATIONSZain AliNo ratings yet

- Lab#7: Study of Common Emitter Transistor Amplifier CircuitDocument6 pagesLab#7: Study of Common Emitter Transistor Amplifier CircuitLeandro ZamaroNo ratings yet

- 1448249900UG - EE 2209 - Power Amplifier - 20140201 (Compatibility Mode)Document31 pages1448249900UG - EE 2209 - Power Amplifier - 20140201 (Compatibility Mode)Tanvir Ahmed MunnaNo ratings yet

- Op AmpBasicInfoDocument6 pagesOp AmpBasicInfosrinureddy2014No ratings yet

- 3 AC AmplificationDocument58 pages3 AC AmplificationAnthony BeltranNo ratings yet

- HITEC University Taxila: Power Electronics LabDocument9 pagesHITEC University Taxila: Power Electronics LabNisar Ahmed RanaNo ratings yet

- Basic DC Power Supply 2Document51 pagesBasic DC Power Supply 2Joshua RefeNo ratings yet

- 12-RC Phase Shift OscillatorDocument5 pages12-RC Phase Shift OscillatorA054 Shubham fundayNo ratings yet

- 12-RC Phase Shift OscillatorDocument5 pages12-RC Phase Shift OscillatorBanty BabliNo ratings yet

- Experiment No. 02: RC Coupled Single Stage BJT Common Collector AmplifierDocument5 pagesExperiment No. 02: RC Coupled Single Stage BJT Common Collector Amplifier5611 M.Mubeen M.yaseenNo ratings yet

- A. DC Operation I. ObjectiveDocument9 pagesA. DC Operation I. ObjectivedummyNo ratings yet

- Abert AinoDocument12 pagesAbert AinoAINOMUGISHA ABERTNo ratings yet

- SemiconductorsDocument4 pagesSemiconductorsGiezel RevisNo ratings yet

- A. DC Operation I. ObjectiveDocument9 pagesA. DC Operation I. ObjectivedummyNo ratings yet

- EE 306 ManualDocument55 pagesEE 306 Manualzain khuramNo ratings yet

- EC Lec09 Power AmplifierDocument69 pagesEC Lec09 Power Amplifierlê văn tiếnNo ratings yet

- Edc Lab Manuals Third SemesterDocument56 pagesEdc Lab Manuals Third SemesterSprout GigsNo ratings yet

- Half Wave and Full Wave RectifierDocument8 pagesHalf Wave and Full Wave RectifierArun Jyothi82% (11)

- Experiment # 1: Figure 1: Circuit DiagramDocument4 pagesExperiment # 1: Figure 1: Circuit DiagramMahnoor Siddiqi100% (1)

- Bab 2 EE201Document59 pagesBab 2 EE201Noor Hanisah AbdullahNo ratings yet

- Full-Wave Single-Phase and Three-Phase Diode Rectifiers (1) : R, RL, and RLE LoadsDocument28 pagesFull-Wave Single-Phase and Three-Phase Diode Rectifiers (1) : R, RL, and RLE LoadsFurqan Bilal BhuttaNo ratings yet

- AnalogEl-4-Power - Ampl-Part 1&2Document36 pagesAnalogEl-4-Power - Ampl-Part 1&2Albert GenceNo ratings yet

- TB2929HQ: 45W × 4-ch BTL Audio Power ICDocument17 pagesTB2929HQ: 45W × 4-ch BTL Audio Power ICmicaelfnNo ratings yet

- Chapter 2 FinalDocument83 pagesChapter 2 FinalSana SaleemNo ratings yet

- Power Electronics 1-2015bjrDocument80 pagesPower Electronics 1-2015bjrNurAdiFirawanNo ratings yet

- Week03 Diode CircuitDocument29 pagesWeek03 Diode CircuitEstika Vriscilla GintingNo ratings yet

- Quaid-E-Awam University of Engg., Sci. & Tech., Nawabshah Department of Telecommunication Engineering Amplifiers & OscillatorsDocument5 pagesQuaid-E-Awam University of Engg., Sci. & Tech., Nawabshah Department of Telecommunication Engineering Amplifiers & Oscillatorsakjan303No ratings yet

- Applied Electronics Lab 2Document9 pagesApplied Electronics Lab 2Rickel RoweNo ratings yet

- Experiment No. 4 Common Emitter Amplifier AIM: Fig 1. Circuit DiagramDocument4 pagesExperiment No. 4 Common Emitter Amplifier AIM: Fig 1. Circuit Diagrampandiyarajan142611No ratings yet

- Section F4: Power Amplifier Circuits - Class B & AB: Complementary Symmetry) ConfigurationDocument8 pagesSection F4: Power Amplifier Circuits - Class B & AB: Complementary Symmetry) ConfigurationKiệt NgôNo ratings yet

- RectifierDocument26 pagesRectifierShuvo Kumar Modak100% (2)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- ADC (Analog-To-Digital Converter) and Sensor InterfacingDocument17 pagesADC (Analog-To-Digital Converter) and Sensor InterfacingAbdullah MuzammilNo ratings yet

- ADC (Analog-To-Digital Converter)Document11 pagesADC (Analog-To-Digital Converter)Abdullah Muzammil0% (1)

- Mosfet CapacidadesDocument8 pagesMosfet Capacidadesluis coriaNo ratings yet

- AVR Serial Port ProgrammingDocument15 pagesAVR Serial Port ProgrammingAbdullah MuzammilNo ratings yet

- ADC (Analog-To-Digital Converter) and Sensor InterfacingDocument15 pagesADC (Analog-To-Digital Converter) and Sensor InterfacingAbdullah MuzammilNo ratings yet

- Assembly Language Programming: HandoutsDocument44 pagesAssembly Language Programming: HandoutsAbdullah MuzammilNo ratings yet

- Teoria Variadores de FrecuencuiaDocument12 pagesTeoria Variadores de FrecuencuiaasotozuazuaNo ratings yet

- A Comparative Study of Field-Oriented Control and Direct-Torque Control of Induction Motors Using An Adaptive Flux ObserverDocument15 pagesA Comparative Study of Field-Oriented Control and Direct-Torque Control of Induction Motors Using An Adaptive Flux ObserverFethi FarhaniNo ratings yet

- AC Line Reactors vs. DC Link Chokes: Application Note AP042003ENDocument7 pagesAC Line Reactors vs. DC Link Chokes: Application Note AP042003ENZinou ZizouNo ratings yet

- XC6219 Current Foldback CircuitDocument3 pagesXC6219 Current Foldback CircuitAbdullah MuzammilNo ratings yet

- TIP31Document3 pagesTIP31edwinfpsNo ratings yet

- IEEE Paper FormatDocument3 pagesIEEE Paper FormatSanhith RaoNo ratings yet

- XC6219 Current Foldback Circuit PDFDocument3 pagesXC6219 Current Foldback Circuit PDFAbdullah MuzammilNo ratings yet

- Yalla UpgradeDocument10 pagesYalla UpgradeBrett HendricksNo ratings yet

- Snubber CircuitsDocument8 pagesSnubber CircuitsHarri Makkonen100% (3)

- ProbabilityDocument12 pagesProbabilityAbdullah MuzammilNo ratings yet

- 1 Electrical SystemDocument28 pages1 Electrical SystemzeeshanNo ratings yet

- 1 Electrical SystemDocument28 pages1 Electrical SystemzeeshanNo ratings yet

- Lecture 0201Document18 pagesLecture 0201Abdullah MuzammilNo ratings yet

- 1 Electrical SystemDocument28 pages1 Electrical SystemzeeshanNo ratings yet

- ProbabilityDocument12 pagesProbabilityAbdullah MuzammilNo ratings yet

- File Stream Classes:-: Steps of File OperationsDocument28 pagesFile Stream Classes:-: Steps of File OperationscnpnrajaNo ratings yet

- HP Deskjet Ink Advantage 2645 Technische Details b1b2db PDFDocument2 pagesHP Deskjet Ink Advantage 2645 Technische Details b1b2db PDFblackdot28No ratings yet

- Super Decisions V.3.0: Tutorial 1 - Building Hierarchical Pairwise Comparison ModelsDocument59 pagesSuper Decisions V.3.0: Tutorial 1 - Building Hierarchical Pairwise Comparison ModelsYulizar WidiatamaNo ratings yet

- Ztest Assist CasesDocument6 pagesZtest Assist Casesjoga srikanthNo ratings yet

- IoGAS Tutorial Basic MonashDocument57 pagesIoGAS Tutorial Basic Monashjohazamo100% (1)

- Project: Security Domains and StrategiesDocument5 pagesProject: Security Domains and StrategiesInga OlafNo ratings yet

- Design of Analytical Model and Algorithm For Optimal Roadside Ap Placement in VanetsDocument11 pagesDesign of Analytical Model and Algorithm For Optimal Roadside Ap Placement in VanetsArash AziminejadNo ratings yet

- Account Usage and Recharge Statement From 29-Jan-2023 To 31-Jan-2023Document5 pagesAccount Usage and Recharge Statement From 29-Jan-2023 To 31-Jan-2023mazars advisoryNo ratings yet

- Kali Linux CommandsDocument6 pagesKali Linux Commandsranjan rajaNo ratings yet

- Daylight Factor: Prasented byDocument8 pagesDaylight Factor: Prasented byDebayan dasNo ratings yet

- Puzzle Test PDF (Box Based) Set 4Document42 pagesPuzzle Test PDF (Box Based) Set 4Ankur GautamNo ratings yet

- EAP Authentication With RADIUS ServerDocument13 pagesEAP Authentication With RADIUS ServerlancethNo ratings yet

- Gmail - ValueLabs - Interview Call Letter - 6th October 2018Document3 pagesGmail - ValueLabs - Interview Call Letter - 6th October 2018Katikireddi V NareshNo ratings yet

- SoC Encounter TutorialDocument18 pagesSoC Encounter Tutorialsyncc500No ratings yet

- Designer Guide To InstrumentationDocument72 pagesDesigner Guide To InstrumentationmarckosalexNo ratings yet

- Review: (V,, V) V V Nul (A) Ax 0Document7 pagesReview: (V,, V) V V Nul (A) Ax 0modiemaniaNo ratings yet

- Mathmatical Model of Control Systems PDFDocument36 pagesMathmatical Model of Control Systems PDFThomasVictor100% (1)

- COD4 CrackDocument1 pageCOD4 CrackRalph Kervie Stephen ChanNo ratings yet

- Study of Logic GatesDocument26 pagesStudy of Logic GatesArial96No ratings yet

- MSDR PDFDocument479 pagesMSDR PDFCarlos TrujilloNo ratings yet

- CMW LTE UE UserManual V3-5-30 en 22Document940 pagesCMW LTE UE UserManual V3-5-30 en 22monel_24671100% (3)

- ProStream 9100 ReleaseDocument79 pagesProStream 9100 Releasediegoh_silva100% (1)

- Adventures On Dungeon Planet PDFDocument143 pagesAdventures On Dungeon Planet PDFYog Sothoth88% (8)

- Oscar GNSS Receiver: Key FeaturesDocument4 pagesOscar GNSS Receiver: Key Featuresanishaa D4SNo ratings yet

- Compact Touch User Manual: Select A ChapterDocument128 pagesCompact Touch User Manual: Select A ChapterKroumson Ben AboubacarNo ratings yet

- Asdaf Kabupaten Mimika, Provinsi Papua Program Studi Kependudukan Dan Pencatatan SipilDocument15 pagesAsdaf Kabupaten Mimika, Provinsi Papua Program Studi Kependudukan Dan Pencatatan SipilretnoayuNo ratings yet

- 2005 Amc 10B Problems: Aops WikiDocument1 page2005 Amc 10B Problems: Aops WikiKevin LeeNo ratings yet

- Detailed Lesson Plan (DLP) Format: States Research QuestionsDocument1 pageDetailed Lesson Plan (DLP) Format: States Research QuestionsMJNo ratings yet

- VP Project Management Director PMO in Boston MA Resume Damnath de TisseraDocument3 pagesVP Project Management Director PMO in Boston MA Resume Damnath de TisseraDamnath De TisseraNo ratings yet

- 8230e DELL Vostro 3350 Wistron Nirvana 13 PDFDocument104 pages8230e DELL Vostro 3350 Wistron Nirvana 13 PDFanh_sao_dem_92No ratings yet