Professional Documents

Culture Documents

Using Icarus Verilog

Uploaded by

Mirta VerónCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Using Icarus Verilog

Uploaded by

Mirta VerónCopyright:

Available Formats

Using Icarus Verilog, VVP and Gtkwave

Icarus Verilog (iverilog) and VVP were DOS based programs. Assuming the readers are familiar in using

iverilog, here are the steps to compile and simulate a Verilog code.

1. Create a Verilog file of the circuit you want to design and simulate. Example given here is a full adder

circuit. The file name is fa.v and this file is saved in the folder C:\iverilog\bin\

`timescale 1ns/100ps //file fa.v

module fa (

input a,b,c,

output sum,carry );

wire d,e,f;

xor(sum,a,b,c);

and(d,a,b);

and(e,b,c);

and(f,a,c);

or(carry,d,e,f);

endmodule

2. Compile the file fa.v by typing at the DOS prompt C:\iverilog\bin\iverilog fa.v

3. If there is syntax error/s, correct it and compile again. No message displayed when there is no error/s.

4. Create a testbench file to simulate the full adder circuit. Example given (at the bottom) is the testbench

file fatb.v and this file is saved in the folder C:\iverilog\bin\

5. Compile the testbench file fatb.v by typing at the DOS prompt C:\iverilog\bin\iverilog fatb.v

6. If there is syntax error/s, correct it and compile again. No message displayed when there is no error/s.

At this point, an output file called a.out is created in the C:\iverilog\bin\

7. To display the table of the input and output signals, type at the DOS prompt C:\iverilog\bin\vvp a.out

Mohd Uzir Kamaluddin / October 2017

8. To display the output waveforms, navigate to C:\iverilog\gtkwave\bin.

9. Type C:\iverilog\gtkwave\bin\gtkwave. This will launch the gtkwave.

10. When the gtkwave window open, select File>Open New Tab

11. Open the file C:\iverilog\bin\test.vcd

12. Double click the SST window folder fulladdt_b and you will see the uut subfolder.

13. Click the uut subfolder, and all the signals is displayed in the Signals window below.

14. Select and drag one by one of the input and output signals of the full adder circuit, the wire a, wire b,

wire c, wire carry and wire sum signals, and place it in the Waves window.

15. Click the unzoom button until the signals is displayed properly.

Mohd Uzir Kamaluddin / October 2017

`timescale 1ns/100ps //file fatb.v

`include "fa.v"

module fulladdt_b;

reg a;

reg b;

reg c;

wire sum;

wire carry;

fa uut ( .a(a), .b(b),.c(c), .sum(sum), .carry(carry) );

initial

begin

$dumpfile("test.vcd");

$dumpvars(0, fulladdt_b); //for gtkwave display

a=0; b=0; c=0; //input signals for full adder

#50 a=0; b=0; c=1;

#50 a=0; b=1; c=0;

#50 a=0; b=1; c=1;

#50 a=1; b=0; c=0;

#50 a=1; b=0; c=1;

#50 a=1; b=1; c=0;

#50 a=1; b=1; c=1;

#50 a=0; b=0; c=0;

end

initial

begin //for display in DOS window

$monitor("a=%d, b=%d, c=%d, carry=%d, sum=%d \n", a, b, c, carry, sum);

end

endmodule

Mohd Uzir Kamaluddin / October 2017

The following is a JK flip flop verilog code. The JK flip flop has asynchronous inputs: set (S), reset (R)

and chip enable (CE).

//JK flip flop module

module FJKRSE(

input J,K,Clk,R,S,CE,

output Qout );

//Internal variable

reg Qout;

always@ (posedge(Clk)) //Everything is synchronous to positive edge of clock

begin

if(R == 1) //reset has highest priority.

Qout = 0;

else

if(S == 1) //set has next priority

Qout = 1;

else

if(CE == 1) //J,K values are considered only when CE is ON.

if(J == 0 && K == 0)

Qout = Qout; //no change J=K=0

else if(J == 0 && K == 1)

Qout = 0; //reset J=0,K=1

else if(J == 1 && K == 0)

Qout = 1; //set J=1, K=0

else

Qout = ~Qout; //toggle J=K=1

else

Qout = Qout; //no change

end

endmodule

//JK flip flop testbench module

`timescale 1ns/1ps

`include "jkff.v"

module tb_jkff;

// Inputs

reg J; reg K; reg Clk; reg R; reg S; reg CE;

// Outputs

wire Qout;

// Instantiate the Unit Under Test (UUT)

FJKRSE uut (.J(J), .K(K), .Clk(Clk), .R(R), .S(S), .CE(CE), .Qout(Qout));

Mohd Uzir Kamaluddin / October 2017

//Create 50 Mhz clock(20 ns clock period).

initial Clk = 0;

always #10 Clk = ~Clk;

initial begin

$dumpfile("test1.vcd");

$dumpvars(0, tb_jkff); //for the gtkwave waveform viewer

// Initialize Inputs

J = 0; K = 0; R = 0; S = 0; CE = 0;

//Apply inputs

#30; R = 1;

#50; R = 0; S = 1;

#50; S = 0; J = 1; K = 1;

#50; CE = 1;

#50; J = 0; K = 0;

#50; J = 0; K = 1;

#50; J = 1; K = 0;

#50; J = 1; K = 1;

#50; CE = 0;

#30; $finish;

end

initial begin //for the DOS tabular display

$monitor("t=%3d, J=%d,K=%d, R=%d,S=%d, CE=%d, Qout=%d",$time,J,K,R,S,CE,Qout);

end

endmodule

Mohd Uzir Kamaluddin / October 2017

You might also like

- UNIX Shell Programming Interview Questions You'll Most Likely Be AskedFrom EverandUNIX Shell Programming Interview Questions You'll Most Likely Be AskedNo ratings yet

- Using Icarus VerilogDocument6 pagesUsing Icarus VeriloggawengNo ratings yet

- VLSI Gold Chips Logic GatesDocument15 pagesVLSI Gold Chips Logic Gateskolihs090302No ratings yet

- EECE6017C - Lab 0 Introduction To Altera Tools and Basic Digital LogicDocument13 pagesEECE6017C - Lab 0 Introduction To Altera Tools and Basic Digital LogicCarlos Morales CarbajalNo ratings yet

- Lab 4Document26 pagesLab 4Saim AshrafNo ratings yet

- Vlsi Lab ManualDocument50 pagesVlsi Lab ManualAnith M ThomasNo ratings yet

- CPET7L Hands-OnExerciseNo2Document4 pagesCPET7L Hands-OnExerciseNo2Sebastian Austin SuelaNo ratings yet

- Lab 4Document26 pagesLab 4HaiderNo ratings yet

- 21-CP-6 (Report10) DLDDocument14 pages21-CP-6 (Report10) DLDAlmaas ChaudryNo ratings yet

- 22bce20019. Lab Report-DldDocument40 pages22bce20019. Lab Report-Dldrockstarguy2005No ratings yet

- V.Ls.I Lab Manual Part-A Prepared BY: Srinivasarao - UdaraDocument30 pagesV.Ls.I Lab Manual Part-A Prepared BY: Srinivasarao - UdaraGnaneshwara ParashuramNo ratings yet

- VerificationDocument11 pagesVerificationNaved Sadat YaminNo ratings yet

- VerilogcodeDocument27 pagesVerilogcodeskrsnaprasadNo ratings yet

- List of Experiments: Expt. No. Date Name of The Experiment Page No. RemarksDocument55 pagesList of Experiments: Expt. No. Date Name of The Experiment Page No. RemarksRakesh KumarNo ratings yet

- EE271 Lab1 Group06Document9 pagesEE271 Lab1 Group06Lê Vương TháiNo ratings yet

- 9 PolynomialDocument4 pages9 PolynomialShivaniNo ratings yet

- Lab1 Directed VerificationDocument17 pagesLab1 Directed Verificationfake godNo ratings yet

- Verilog Imp...Document105 pagesVerilog Imp...Arun JyothiNo ratings yet

- Expt No.:5 Verilog Program For 3 To 8 Decoder DateDocument11 pagesExpt No.:5 Verilog Program For 3 To 8 Decoder DateSandhya RaghunathNo ratings yet

- Verilog Modules For Common Digital FunctionsDocument30 pagesVerilog Modules For Common Digital Functionssudarshan poojaryNo ratings yet

- Systemverilog Q&A: Normal Inline Assertion ExampleDocument10 pagesSystemverilog Q&A: Normal Inline Assertion ExampleJitendraNo ratings yet

- ECEN 248 Lab8 - ReportDocument16 pagesECEN 248 Lab8 - ReportRebecca Sontheimer0% (1)

- Vlsi Part A ManualDocument47 pagesVlsi Part A ManualLohit PNo ratings yet

- COMSATS Institute of Information Technology: Lab#12: Convolutional EncodersDocument3 pagesCOMSATS Institute of Information Technology: Lab#12: Convolutional EncoderstalhaNo ratings yet

- Verilog Lab Manual (ECAD and VLSI Lab)Document57 pagesVerilog Lab Manual (ECAD and VLSI Lab)Swaminathan KathirvelNo ratings yet

- Dwnload Full Digital Systems Design Using Verilog 1st Edition Roth Solutions Manual PDFDocument35 pagesDwnload Full Digital Systems Design Using Verilog 1st Edition Roth Solutions Manual PDFhaodienb6qj100% (13)

- VHDL SynthesisDocument91 pagesVHDL SynthesisFennil KinsperNo ratings yet

- Vlsi Comple Lab TaskDocument37 pagesVlsi Comple Lab TaskTausique SheikhNo ratings yet

- Experiment - 3 Design and Simulation of Four-Bit Ripple Carry AdderDocument18 pagesExperiment - 3 Design and Simulation of Four-Bit Ripple Carry AdderUnlimited XfinityNo ratings yet

- Practical No - 1 Aim: Implementation of Gates.: 1) AND GateDocument18 pagesPractical No - 1 Aim: Implementation of Gates.: 1) AND GatePrince SharmaNo ratings yet

- LSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 3 - DelayDocument8 pagesLSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 3 - DelayMerupu DebbaNo ratings yet

- Wa0005.Document39 pagesWa0005.arfanss512No ratings yet

- Embedded Systems COE23Document37 pagesEmbedded Systems COE23Ishita SharmaNo ratings yet

- Verilog and Test Bench Code For FlipflopsDocument11 pagesVerilog and Test Bench Code For FlipflopsKeith Fernandes67% (3)

- Lab Results VlsiDocument18 pagesLab Results Vlsipankaj rangareeNo ratings yet

- Lapres 7Document23 pagesLapres 7Ika Yuliana WatiNo ratings yet

- Week10 Sequential CircuitsDocument27 pagesWeek10 Sequential Circuitsnavarrojules53No ratings yet

- CPE 316 - Laboratory 1-2 MACAPAGALDocument17 pagesCPE 316 - Laboratory 1-2 MACAPAGALGERLAND ANDREI CUEVASNo ratings yet

- Lab Manual: 1 Dept of E&C, PACE, MangaloreDocument78 pagesLab Manual: 1 Dept of E&C, PACE, MangaloreMr.Mohammed Zakir B ELECTRONICS & COMMUNICATIONNo ratings yet

- Assignment 3Document8 pagesAssignment 3Pranavkumar PatilNo ratings yet

- Dante Experiment#2Document8 pagesDante Experiment#2CHRISTIANJOIE DANTENo ratings yet

- Assignment 5 E23CSEU0525Document8 pagesAssignment 5 E23CSEU0525sanskarsinghsengarNo ratings yet

- Assignment 5 E23CSEU0698Document8 pagesAssignment 5 E23CSEU0698sanskarsinghsengarNo ratings yet

- Embedded ProjectDocument43 pagesEmbedded ProjectPurnima TayalNo ratings yet

- Soln To hw5Document4 pagesSoln To hw5Iven Rey B. TañaraNo ratings yet

- Digital Systems Design Using Verilog 1st Edition Roth Solutions ManualDocument25 pagesDigital Systems Design Using Verilog 1st Edition Roth Solutions ManualJesusEvansspaj100% (54)

- Ecad and Vlsi Lab ManualDocument125 pagesEcad and Vlsi Lab Manualsameer7mohammadNo ratings yet

- HET202 Final Examination Sem 2 2006Document21 pagesHET202 Final Examination Sem 2 2006Kai JieNo ratings yet

- DDCO Model Paper SolvedDocument33 pagesDDCO Model Paper SolvedPraneethNo ratings yet

- Questions&AnswersDocument8 pagesQuestions&AnswersECEII 065No ratings yet

- VLSI Record 2022-23Document77 pagesVLSI Record 2022-23MANOJNo ratings yet

- Drill 4 Soquiat Marc HendriDocument9 pagesDrill 4 Soquiat Marc HendriMarc Hendri SoquiatNo ratings yet

- Part 3: Verilog Tutorial: ECE232: Hardware Organization and DesignDocument18 pagesPart 3: Verilog Tutorial: ECE232: Hardware Organization and DesignAbhishek MishraNo ratings yet

- Full Download Digital Systems Design Using Verilog 1st Edition Roth Solutions ManualDocument35 pagesFull Download Digital Systems Design Using Verilog 1st Edition Roth Solutions Manualelenoretupper100% (34)

- Julius Lebita - Drill-4 - LebitaDocument16 pagesJulius Lebita - Drill-4 - LebitaJhong JhongNo ratings yet

- Solution of Quiz 3Document5 pagesSolution of Quiz 3Pranavkumar PatilNo ratings yet

- LSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 3 - DelayDocument10 pagesLSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 3 - DelayMerupu DebbaNo ratings yet

- Sample Eda Lab (Part-A) Manual: Simulation OutputDocument20 pagesSample Eda Lab (Part-A) Manual: Simulation Outputmdzakir_hussainNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- SWFP66D Series Fine-Grinding Hammer Mill: Operation ManualDocument65 pagesSWFP66D Series Fine-Grinding Hammer Mill: Operation ManualDanielDeFrancescoNo ratings yet

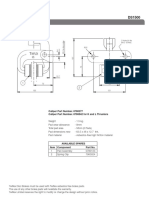

- F612/F627/F626B: Semi-Lugged Gearbox Operated Butterfly Valves PN16Document1 pageF612/F627/F626B: Semi-Lugged Gearbox Operated Butterfly Valves PN16RonaldNo ratings yet

- 3scribd Leech Generator - بحث GoogleDocument2 pages3scribd Leech Generator - بحث Googleplaylist youtubNo ratings yet

- MS Disc Brake CaliperDocument2 pagesMS Disc Brake Caliperghgh140No ratings yet

- Platform General Vxworks Migration Guide 3.6Document124 pagesPlatform General Vxworks Migration Guide 3.6Ding YueNo ratings yet

- Synapsis Radar NX Operator Manual E05.01Document346 pagesSynapsis Radar NX Operator Manual E05.01russepilNo ratings yet

- Reflection PaperDocument2 pagesReflection PaperKatrina DeveraNo ratings yet

- Rodavigo Acoplamientos 02 Acoplamientos de BielasDocument20 pagesRodavigo Acoplamientos 02 Acoplamientos de BielasArturo J. Londono MNo ratings yet

- Satellite TTC Module 4Document21 pagesSatellite TTC Module 4AmitNo ratings yet

- TM AHU 60R410A Onoff T SA NA 171205Document67 pagesTM AHU 60R410A Onoff T SA NA 171205Sam RVNo ratings yet

- Face Recognition - HLD - V1Document4 pagesFace Recognition - HLD - V1SuryaNo ratings yet

- M2 Pre-Task: Application Software - System Software Driver Software Programming SoftwareDocument2 pagesM2 Pre-Task: Application Software - System Software Driver Software Programming SoftwareBee Anne BiñasNo ratings yet

- Weld-On Brackets Type 35Document1 pageWeld-On Brackets Type 35Achraf BoudayaNo ratings yet

- ITC LAB 4 - FlowchartsDocument7 pagesITC LAB 4 - FlowchartspathwayNo ratings yet

- Hidden Beam DesignDocument8 pagesHidden Beam DesignAnil kumar R100% (1)

- Postgresql 11 A4 PDFDocument2,621 pagesPostgresql 11 A4 PDFGiuliano PertileNo ratings yet

- Developing A Social Media Strategy: © RB Consulting 2010Document12 pagesDeveloping A Social Media Strategy: © RB Consulting 2010edetpickin1No ratings yet

- Diagrams LH3Document101 pagesDiagrams LH3Angel Hernan Apaz HuancaNo ratings yet

- Getting Started With PIC Microcontroller - CCS C Compiler PDFDocument19 pagesGetting Started With PIC Microcontroller - CCS C Compiler PDFNithya100% (2)

- AN1009: Driving MOSFET and IGBT Switches Using The Si828x: Key FeaturesDocument22 pagesAN1009: Driving MOSFET and IGBT Switches Using The Si828x: Key FeaturesNikolas AugustoNo ratings yet

- Linkedin Emerging Jobs Report Indonesia FinalDocument24 pagesLinkedin Emerging Jobs Report Indonesia Finallontong4925No ratings yet

- Level Wound Copper TubeDocument1 pageLevel Wound Copper TubeAamer Abdul MajeedNo ratings yet

- Hvac and Refrigiration System: Group 1Document52 pagesHvac and Refrigiration System: Group 1Jessa Mae CatabayNo ratings yet

- No. 304 (171) 2021/PA Admn 111!: To, Centre ExcellenceDocument9 pagesNo. 304 (171) 2021/PA Admn 111!: To, Centre ExcellenceSanjeev kumarNo ratings yet

- Research Paper Latex ExampleDocument8 pagesResearch Paper Latex Exampleafnkjdhxlewftq100% (1)

- Compressor House Unit-3Document199 pagesCompressor House Unit-3Priyanka BasuNo ratings yet

- Tara Housing-Case StudyDocument25 pagesTara Housing-Case StudyTonmoy kumar sarker100% (1)

- HTML Project On Shopping WebsiteDocument2 pagesHTML Project On Shopping WebsiteSunitha ManamNo ratings yet

- Module 11A.5.2 L1 2016-08-16Document234 pagesModule 11A.5.2 L1 2016-08-16Abdul Aziz KhanNo ratings yet

- Tech M Service LetterDocument1 pageTech M Service LetterRahul upadhyayNo ratings yet