Professional Documents

Culture Documents

Assignment No: 3: Carry Save Adder

Uploaded by

Hasnain AwanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Assignment No: 3: Carry Save Adder

Uploaded by

Hasnain AwanCopyright:

Available Formats

Digital Electronics Lab (Pattern 2015)

R C O T Dated

Assignment No: 3 (2) (4) (2) (2) Sign

Title: BCD Adder

Objective: To learn different types of adder

Problem Statement: Design of n-bit Carry Save Adder (CSA) and Carry

Propagation Adder (CPA). Design and Realization of BCD Adder using 4-bit

Binary Adder (IC 7483).

Hardware and software requirement:

Digital Trainer Kit, IC 7483,7432 7408, Patch Cord ,+ 5V Power Supply

Theory:

Carry Save Adder:

A carry save adder is just a set of one bit full adder, without any carry

chaining. Therefore n-bit CSA receivers three n-bit operands,namely A(n-1),A(0)

and CIN(n-1)-----------CIN(0) and generate two n-bit result values, sum(n-1)-------

----sum(0) and count(n-1)--------count(0).

Carry Propagation Adder:

The parallel adder is ripple carry type in which the carry output of each full adder

stage is connected to the carry input of the next highest order stage.

Therefore, the sum and carry outputs of any stage cannot be produced until the

carry occurs. This leads to a time delay in addition process.

This is known as Carry Propagation Delay.

BCD Adder: It is a circuit that adds two BCD digits & produces a sum of digits

also in BCD.

Rules for BCD addition:

1. Add two numbers using rules of Binary addition.

2. If the 4 bit sum is greater than 9 or if carry is generated then the sum is invalid. To

correct the sum add 0110 i.e. (6)10 to sum. If carry is generated from this addition

add it to next higher order BCD digit.

3. If the 4 bit sum is less than 9 or equal to 9 then sum is in proper form.

S.N.J.B.’s College of Engineering, Chandwad 1

Digital Electronics Lab (Pattern 2015)

The BCD addition can be explained with the help of following 3 cases -

CASE I: Sum <= 9 & carry = 0.

Add BCD digits 3 & 4

1. 0011

+0 1 0 0

---------

0111

Answer is valid BCD number = (7) BCD & so 0110 is not added.

CASE II: Sum > 9 & carry = 0.

Add BCD digits 6 & 5

1. 0110

+0 1 0 1

-----------

1011

Invalid BCD (since sum > 9) so 0110 is to be added

2. 1011

+0 1 1 0

-----------

1 0001

(1 1)BCD

Valid BCD result = (11) BCD

CASE III: Sum < = 9 & carry = 1.

Add BCD digits 9 & 9

1. 1001

+1001

-----------

10010

Invalid BCD (since Carry = 1) so 0110 is to be added

S.N.J.B.’s College of Engineering, Chandwad 2

Digital Electronics Lab (Pattern 2015)

2. 1 0010

+0110

------------

11000

(1 8)BCD

Valid BCD result = (18) BCD

Design of BCD adder :

1. 4 bit binary adder is used for initial addition. i.e. binary addition of two 4 bit

numbers.( with Cin = 0 ),

2. Logic circuit to sense if sum exceeds 9 or carry = 1, this digital circuit will

produce high output otherwise its output will be zero.

3. One more 4-bit adder to add (0110)2 in the sum is greater than 9 or carry is 1.

S.N.J.B.’s College of Engineering, Chandwad 3

Digital Electronics Lab (Pattern 2015)

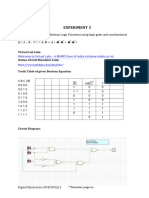

Truth Table:-

For design of combinational circuit for BCD adder to check invalid BCD

INPUT OUTPUT

S3 S2 S1 S0 Y

0 0 0 0 0

0 0 0 1 0

0 0 1 0 0

0 0 1 1 0

0 1 0 0 0

0 1 0 1 0

0 1 1 0 0

0 1 1 1 0

1 0 0 0 0

1 0 0 1 0

1 0 1 0 1

1 0 1 1 1

1 1 0 0 1

1 1 0 1 1

1 1 1 0 1

1 1 1 1 1

S.N.J.B.’s College of Engineering, Chandwad 4

Digital Electronics Lab (Pattern 2015)

K-map:-

For reduced Boolean expressions of output

Y= S3S2+S3S1

Circuit diagram:

For invalid BCD detection

S.N.J.B.’s College of Engineering, Chandwad 5

Digital Electronics Lab (Pattern 2015)

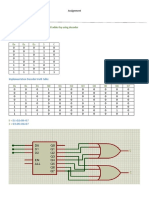

iv) Circuit diagram for BCD adder :

S.N.J.B.’s College of Engineering, Chandwad 6

Digital Electronics Lab (Pattern 2015)

Observation Table of BCD adder:

INPUT OUTPUT

1st Operand 2nd Operand MSD LSD

A3 A2 A1 A0 B3 B2 B1 B0 Cout S3 S2 S1 S0

(MSB) (LSB) (MSB) (LSB) (MSB) (LSB)

Outcome:

Thus, we studied single bit BCD adder using 4 bit parallel binary adder / 4 bit full adder

the observation table has been verified have been verified using IC 7483 & some logic

gates.

Assignments Questions:

S.N.J.B.’s College of Engineering, Chandwad 7

You might also like

- Pimpri Chinchwad Education Trust's Pimpri Chinchwad College of Engineering Name-Vedant Dhote Roll No. - SYITA131 Assignment-3Document9 pagesPimpri Chinchwad Education Trust's Pimpri Chinchwad College of Engineering Name-Vedant Dhote Roll No. - SYITA131 Assignment-3Vedant DhoteNo ratings yet

- Digital Lab ReportDocument9 pagesDigital Lab ReportNg Ming FengNo ratings yet

- Digital System Design Lab ExperimentsDocument45 pagesDigital System Design Lab ExperimentsshivaNo ratings yet

- Carry Look Ahead Adders: Lesson ObjectivesDocument10 pagesCarry Look Ahead Adders: Lesson ObjectivespadmavathiNo ratings yet

- Student Name Subject: ITNT202/LOGIC Design Information Technology Department Semester 2Document9 pagesStudent Name Subject: ITNT202/LOGIC Design Information Technology Department Semester 2Muhammad IrfanNo ratings yet

- Assignment No: 17 Group CDocument5 pagesAssignment No: 17 Group CAyimen LatheefNo ratings yet

- Tareq Sir 3 Number Lap ReportDocument4 pagesTareq Sir 3 Number Lap ReportMd.Rakibul IslamNo ratings yet

- Lecture 15 PDFDocument9 pagesLecture 15 PDFattiqueNo ratings yet

- Unit 4Document14 pagesUnit 4kaavya shruthiNo ratings yet

- Lab 3Document14 pagesLab 3trongnhansuper1No ratings yet

- LCD Mod3Ass TUMALIUANDocument6 pagesLCD Mod3Ass TUMALIUANmaxpein100% (1)

- Adc Lab 2-8-2017Document16 pagesAdc Lab 2-8-2017allanjwilsonNo ratings yet

- Co Lab ManualDocument81 pagesCo Lab ManualShiva KumarNo ratings yet

- De Unit2 SlidesDocument167 pagesDe Unit2 SlidesAravind RaoNo ratings yet

- Sample Midterm ExamDocument7 pagesSample Midterm ExamArnav ChaturvediNo ratings yet

- A - 29 - Pratham - Katariya DSD Exp-1Document5 pagesA - 29 - Pratham - Katariya DSD Exp-1pratham.22211592No ratings yet

- 2exautkuuoDS - Exp - 3 - BCD ADDER - Roll No - 57 - Batch - 3Document6 pages2exautkuuoDS - Exp - 3 - BCD ADDER - Roll No - 57 - Batch - 3Manoj DohaleNo ratings yet

- Lab 5 Binary ArithmeticDocument5 pagesLab 5 Binary ArithmeticIfthakharul Alam ShuvoNo ratings yet

- Binary To 9'S ComplementDocument3 pagesBinary To 9'S ComplementMarco FraquetNo ratings yet

- Practical Test 20 %: School of Computer Science Degree ProgrammeDocument14 pagesPractical Test 20 %: School of Computer Science Degree ProgrammeAnThonY Gaming NepalNo ratings yet

- Revision Q (Answer)Document6 pagesRevision Q (Answer)Johan ZafriNo ratings yet

- Experiment 7Document3 pagesExperiment 7AAAAALLENNNo ratings yet

- Unit 2 - Over View + DEDocument23 pagesUnit 2 - Over View + DEJaswanth SuggulaNo ratings yet

- DLD Lab Sessional 1Document8 pagesDLD Lab Sessional 1AitazazNo ratings yet

- 17BCB0091 DLD Da 6Document9 pages17BCB0091 DLD Da 6csolutionNo ratings yet

- Final SolDocument6 pagesFinal SolUmair MaqboolNo ratings yet

- DLD Final Lab ReportDocument10 pagesDLD Final Lab Reporthaiqa suhail100% (1)

- Combinational Circuits DesignDocument22 pagesCombinational Circuits DesignSHUBHAM KUMAR SINGHNo ratings yet

- Lab 10: BCD To Excess-3 Code: Objective(s)Document3 pagesLab 10: BCD To Excess-3 Code: Objective(s)HA AimNo ratings yet

- Recent PHD ResultDocument72 pagesRecent PHD ResultSavita Kiran BNo ratings yet

- Bahria University, Lahore Campus: Department of Computer SciencesDocument7 pagesBahria University, Lahore Campus: Department of Computer SciencesAbdul BasitNo ratings yet

- DSD Lab Record - 230114 - 203246Document33 pagesDSD Lab Record - 230114 - 203246Angelin ArulNo ratings yet

- CS101-Assignmnet 1Document5 pagesCS101-Assignmnet 1M Noaman AkbarNo ratings yet

- Tutorial3-With Answer KeyDocument12 pagesTutorial3-With Answer KeyRetheshNo ratings yet

- Experiment No. 6: Aim: Write VHDL Code For 2:4 Decoder Using If Statement. Software:Xilinx ISE 14.7 TheoryDocument3 pagesExperiment No. 6: Aim: Write VHDL Code For 2:4 Decoder Using If Statement. Software:Xilinx ISE 14.7 TheoryJaspreet KaurNo ratings yet

- 6.magnitude ComparatorDocument3 pages6.magnitude ComparatorSudhan HariNo ratings yet

- Exp-3 harviDocument5 pagesExp-3 harviharvi.kotadiya121816No ratings yet

- Exp9 1Document3 pagesExp9 1Ashley De LeonNo ratings yet

- Introduction To Computing (CS101) : Assignment # 01Document2 pagesIntroduction To Computing (CS101) : Assignment # 01bc200200813 JUNAID ARSHADNo ratings yet

- Lab Manual 06Document4 pagesLab Manual 06Rana jamshaid Rana jamshaidNo ratings yet

- COMP2611 Spring 2020 Homework #1 Solutions Deadline and Submission DetailsDocument9 pagesCOMP2611 Spring 2020 Homework #1 Solutions Deadline and Submission DetailsManan GoyalNo ratings yet

- DLD Project Report CompleteDocument10 pagesDLD Project Report CompleteAMMAD MAHMOODNo ratings yet

- Apsce DSD Lab 18ecl38Document54 pagesApsce DSD Lab 18ecl381AP20EC005 Kirthi BharadwajNo ratings yet

- Design and Study of Full Adder CircuitDocument3 pagesDesign and Study of Full Adder CircuitBinita SedhaiNo ratings yet

- 8 Bit Adder/Subtractor: B.S. Computer Science Project ReportDocument11 pages8 Bit Adder/Subtractor: B.S. Computer Science Project ReportHassan FaridNo ratings yet

- Combinational Logic CircuitsDocument39 pagesCombinational Logic CircuitsRhea Daluddung SanchezNo ratings yet

- Assignment2 SolutionDocument11 pagesAssignment2 SolutionSyed Abdullah Hasan ChishtiNo ratings yet

- Combinational Digital Design Laboratory Manual: Experiment #8 Decoders & EncodersDocument10 pagesCombinational Digital Design Laboratory Manual: Experiment #8 Decoders & EncodersJaideep Singh100% (1)

- Digital Logic Design Assignment 2Document7 pagesDigital Logic Design Assignment 2mesfinNo ratings yet

- DLD manual_EXP_3Document3 pagesDLD manual_EXP_3Ahmad RazaNo ratings yet

- DPCO ManualDocument64 pagesDPCO Manualg2272049No ratings yet

- Lab No. 6: Understanding The Simplification by Boolean Algebra, Truth Table and Karnaugh MapDocument4 pagesLab No. 6: Understanding The Simplification by Boolean Algebra, Truth Table and Karnaugh MapInam Ur RehmanNo ratings yet

- Lab Assignment Digital Design - نسخةDocument5 pagesLab Assignment Digital Design - نسخةMaged SarhanNo ratings yet

- Digital Systems: Exercises 1Document5 pagesDigital Systems: Exercises 1月野姮娥No ratings yet

- 19EC303 QP RepositoryDocument4 pages19EC303 QP RepositoryssfjvhsffsNo ratings yet

- Design The Following Combinatinal Logic CircuitDocument3 pagesDesign The Following Combinatinal Logic CircuitPEARL CAIRA MAE DIMALANTANo ratings yet

- Experiment:-7: AIM:-A.. Design A BCD To EXCESS-3 Code and Realize ItDocument6 pagesExperiment:-7: AIM:-A.. Design A BCD To EXCESS-3 Code and Realize ItAniket RatnakarNo ratings yet

- Modul Minggu Ke-2 (DB6 Dan DB7)Document15 pagesModul Minggu Ke-2 (DB6 Dan DB7)Eden HamamNo ratings yet

- Digital Electronics For Engineering and Diploma CoursesFrom EverandDigital Electronics For Engineering and Diploma CoursesNo ratings yet

- Experiment 5 BCD Adder and Comparator 1Document9 pagesExperiment 5 BCD Adder and Comparator 1Hasnain AwanNo ratings yet

- Vhannel DiscriptionDocument1 pageVhannel DiscriptionHasnain AwanNo ratings yet

- Et 09Document15 pagesEt 09Ajay Kumar MattupalliNo ratings yet

- A (A+B) Solution Aa+Ab A+Ab A (1+B) : Aa A ADocument3 pagesA (A+B) Solution Aa+Ab A+Ab A (1+B) : Aa A AHasnain AwanNo ratings yet

- Assignment No: 3: Carry Save AdderDocument7 pagesAssignment No: 3: Carry Save AdderHasnain AwanNo ratings yet

- Et 09Document15 pagesEt 09Ajay Kumar MattupalliNo ratings yet

- Convert Into SOP Form: (A+B) (C+B) Solution (A+B) (C+B)Document5 pagesConvert Into SOP Form: (A+B) (C+B) Solution (A+B) (C+B)Hasnain AwanNo ratings yet

- Sub Ncs 301 30sep14Document170 pagesSub Ncs 301 30sep14Nrgk Prasad100% (1)

- Lec 3Document18 pagesLec 3Hasnain AwanNo ratings yet

- Convert Into SOP Form: (A+B) (C+B) Solution (A+B) (C+B)Document5 pagesConvert Into SOP Form: (A+B) (C+B) Solution (A+B) (C+B)Hasnain AwanNo ratings yet

- Lec 3Document18 pagesLec 3Hasnain AwanNo ratings yet

- Lec 3Document18 pagesLec 3Hasnain AwanNo ratings yet

- Lec 3Document18 pagesLec 3Hasnain AwanNo ratings yet

- Cu20025ecpb W1JDocument6 pagesCu20025ecpb W1JBeenish MirzaNo ratings yet

- Service Manual Philips 150s6 170s6190s6Document31 pagesService Manual Philips 150s6 170s6190s6ashmitashrivasNo ratings yet

- TAC INET Seven System - Getting Started PDFDocument138 pagesTAC INET Seven System - Getting Started PDFRemon Adel AsaadNo ratings yet

- 4 Ie IcmpDocument17 pages4 Ie IcmpMarvin GarciaNo ratings yet

- FactoryTalk View Site Edition - 12.00.00 (Released 9 - 2020)Document11 pagesFactoryTalk View Site Edition - 12.00.00 (Released 9 - 2020)Manuel Alejandro Choque FernandezNo ratings yet

- SpeedTouch 585 UserGuideDocument110 pagesSpeedTouch 585 UserGuideLucian AvramNo ratings yet

- HargaDocument8 pagesHargarobialamsyahNo ratings yet

- How To: Install Matrikon Opc Simulation ServerDocument4 pagesHow To: Install Matrikon Opc Simulation ServerLeonardo TonimNo ratings yet

- Smart Card User Manual AU9520 v1Document1 pageSmart Card User Manual AU9520 v1Abdelmajid HosniNo ratings yet

- Iot ProtDocument91 pagesIot ProtYao-Ting ChiuNo ratings yet

- MANUAL DGS-3100 Series User Manual v3.6Document295 pagesMANUAL DGS-3100 Series User Manual v3.6Jose Manuel Diaz RoldanNo ratings yet

- A Beginner-Friendly Introduction To Kubernetes - by David Chong - Towards Data ScienceDocument20 pagesA Beginner-Friendly Introduction To Kubernetes - by David Chong - Towards Data ScienceMikiyas Tsegaye100% (1)

- Prince - Of.persia Collection Manual (PC, Mac) PDFDocument28 pagesPrince - Of.persia Collection Manual (PC, Mac) PDFdrazheNo ratings yet

- Adorage ProtocolDocument17 pagesAdorage ProtocolBreakr TopNo ratings yet

- Unit 2Document56 pagesUnit 2srrevishnu88No ratings yet

- SSS 1 3RD Term Lesson NoteDocument29 pagesSSS 1 3RD Term Lesson NoteOyinade AdeoluNo ratings yet

- Standard Access-List Example On Cisco RouterDocument1 pageStandard Access-List Example On Cisco RouterSamuel HOUNGBEMENo ratings yet

- Microchip Product Guide Q3-96Document48 pagesMicrochip Product Guide Q3-96jacerosiete2952No ratings yet

- RTPA ConfigDocument3 pagesRTPA Configsoufiane amraniNo ratings yet

- RACF5 Ichza6c1Document444 pagesRACF5 Ichza6c1Siranjeevi MohanarajaNo ratings yet

- Day 3-Video Training - MAXPRO VMS - 02-Feb-2014Document80 pagesDay 3-Video Training - MAXPRO VMS - 02-Feb-2014Arman Ul NasarNo ratings yet

- TG0029en Ed04Document74 pagesTG0029en Ed04brayam11No ratings yet

- DSS 7XX UxDocument90 pagesDSS 7XX UxJonathan Argel Maldonado JuarezNo ratings yet

- V Pos Installation GuideDocument49 pagesV Pos Installation GuideearlNo ratings yet

- Claroty and Check Point Integration BriefDocument4 pagesClaroty and Check Point Integration BriefAdrian ReyesNo ratings yet

- Exscript enDocument33 pagesExscript enjosalasNo ratings yet

- Troubleshoothing Guide Ccmigration 09186a008067a25cDocument499 pagesTroubleshoothing Guide Ccmigration 09186a008067a25charsh2488No ratings yet

- DX DiagDocument43 pagesDX DiagLevani BerianiNo ratings yet

- QF Il User GuideDocument20 pagesQF Il User GuideDrew AlbaneseNo ratings yet

- 1.1.1 (SL) Computer Architecture - Revision PackDocument29 pages1.1.1 (SL) Computer Architecture - Revision PackQWERTYNo ratings yet