Professional Documents

Culture Documents

Plasma TV: Service Manual

Uploaded by

Isaac Reyes DiegoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Plasma TV: Service Manual

Uploaded by

Isaac Reyes DiegoCopyright:

Available Formats

Internal Use Only

North/Latin America http://aic.lgservice.com

Europe/Africa http://eic.lgservice.com

Asia/Oceania http://biz.lgservice.com

PLASMA TV

SERVICE MANUAL

CHASSIS : PA01A

MODEL : 50PK550 50PK550-AA

CAUTION

BEFORE SERVICING THE CHASSIS,

READ THE SAFETY PRECAUTIONS IN THIS MANUAL.

P/NO : MFL62882003(1011-REV01) Printed in Korea

Downloaded from www.Manualslib.com manuals search engine

CONTENTS

CONTENTS ............................................................................................................................... 2

SAFETY PRECAUTIONS ...........................................................................................................3

SPECIFICATION.........................................................................................................................4

ADJUSTMENT INSTRUCTION ..................................................................................................6

TROUBLESHOOTING GUIDE..................................................................................................11

BLOCK DIAGRAM ...................................................................................................................22

EXPLODED VIEW ...................................................................................................................23

SVC. SHEET ................................................................................................................................

Copyright ©2010 LG Electronics Inc. All rights reserved. -2- LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

SAFETY PRECAUTIONS

IMPORTANT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These parts are identified by in the

Schematic Diagram and Exploded View.

It is essential that these special safety parts should be replaced with the same components as recommended in this manual to prevent

X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

General Guidance Leakage Current Hot Check (See below Figure)

Plug the AC cord directly into the AC outlet.

An isolation Transformer should always be used during the Do not use a line Isolation Transformer during this check.

servicing of a receiver whose chassis is not isolated from the AC Connect 1.5K/10watt resistor in parallel with a 0.15uF capacitor

power line. Use a transformer of adequate power rating as this between a known good earth ground (Water Pipe, Conduit, etc.)

protects the technician from accidents resulting in personal injury and the exposed metallic parts.

from electrical shocks. Measure the AC voltage across the resistor using AC voltmeter

with 1000 ohms/volt or more sensitivity.

It will also protect the receiver and it's components from being Reverse plug the AC cord into the AC outlet and repeat AC voltage

damaged by accidental shorts of the circuitry that may be measurements for each exposed metallic part. Any voltage

inadvertently introduced during the service operation. measured must not exceed 0.75 volt RMS which is corresponds to

0.5mA.

If any fuse (or Fusible Resistor) in this monitor is blown, replace it In case any measurement is out of the limits specified, there is

with the specified. possibility of shock hazard and the set must be checked and

repaired before it is returned to the customer.

When replacing a high wattage resistor (Oxide Metal Film Resistor,

over 1W), keep the resistor 10mm away from PCB.

Keep wires away from high voltage or high temperature parts. Leakage Current Hot Check circuit

Due to high vacuum and large surface area of picture tube, AC Volt-meter

extreme care should be used in handling the Picture Tube.

Do not lift the Picture tube by it's Neck.

Good Earth Ground

such as WATER PIPE,

Leakage Current Cold Check(Antenna Cold Check) CONDUIT etc.

To Instrument's 0.15uF

With the instrument AC plug removed from AC source, connect an

exposed

electrical jumper across the two AC plug prongs. Place the AC METALLIC PARTS

switch in the on position, connect one lead of ohm-meter to the AC

plug prongs tied together and touch other ohm-meter lead in turn to

each exposed metallic parts such as antenna terminals, phone 1.5 Kohm/10W

jacks, etc.

If the exposed metallic part has a return path to the chassis, the

measured resistance should be between 1MΩ and 5.2MΩ.

When the exposed metal has no return path to the chassis the

reading must be infinite.

An other abnormality exists that must be corrected before the

receiver is returned to the customer.

Copyright ©2010 LG Electronics Inc. All rights reserved. -3- LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

SPECIFICATIONS

NOTE : Specifications and others are subject to change without notice for improvement.

V Application Range

This spec is applied to the PDP TV used PA01A Chassis.

V Specification

Each part is tested as below without special appointment.

1) Temperature : 25±5°C (77±9°F), CST : 40±5

2) Relative Humidity: 65±10%

3) Power Voltage: Standard Input voltage (100-240V~, 50/60Hz)

* Standard Voltage of each product is marked by models.

4) Specification and performance of each parts are followed each drawing and specification by part number in accordance with

SBOM.

5) The receiver must be operated for about 20 minutes prior to the adjustment.

V Test Method

1) Performance : LGE TV test method followed.

2) Demanded other specification

Safety : CB specification

EMC : CISPR 13 specification

V Test Method

No Item Specification Remark

1. Broadcasting system PAL-B/B, DTV : DVB-T

2. Available Channel 1)DTV

-.VHF : 6 ~ 12

-.UHF : 27 ~ 69

2) ATV

-.VHF : 0 ~ 20

-.UHD : 21 ~ 75

3. Tuner IF 1) PAL : 38.90MHz(Picture),

34.40MHz(Sound)

2) DVB-T : 36.125MHz

4. Input Voltage AC 100 ~ 240 V, 50/60Hz Mark : 240V, 50Hz

5. Screen Size 42 inch XGA(1024 x 768)

50 inch Wide(1365 x 768)

50 inch Wide(1920 × 1080)

60 inch Wide(1920 × 1080)

6. Aspect Ratio 16:9

7. Module 42/50T1, 50/60R1

8. Operating Environment 1) Temp : 0 ~ 40 deg

2) Humidity : ~ 80 %

9. Storage Environment 1) Temp : -20 ~ 60 deg

2) Humidity : ~ 85 %

Copyright ©2010 LG Electronics Inc. All rights reserved. -4- LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

V Chroma & Brightness

(1) FHD Module (50R1 Module, 38% Glass Filter )

* Warning : When measuring following test items, Dynamic Colour & Dynamic Contrast should be turned off.

No Item Min Typ Max Unit Remark

1. White peak brightness 236 284 - cd/m2 (*) Peak Brightness Mode

-1/100 white Window pattern

(Typically 1% Window size)

-100IRE (255Gray)

-Picture: Vivid (Medium)

-Input: HDMI-PC(1920*1080 60Hz)

*Peak Brightness Condition may Slightly

different between sets.

140 150 -25/100 white Window pattern

2. White average brightness 44 50 cd/m2 - 100% Window White Pattern

- 100IRE(255Gray)

- Picture: Vivid(Medium )

3. Brightness uniformity -10 0 +10 % - 85IRE(216Gray) 100% Window White Pattern

- Picture: Vivid(Medium)

4. Color White X 0.270 0.285 0.300 - White : 85IRE(216Gray) 100% Window

Coordinate Y 0.278 0.293 0.303 White Pattern

Red X 0.635 0.640 - - R/G/B : 100IRE(255Gray) 100% Window

Y 0.318 0.333 0.345 White Pattern

Green X 0.242 0.300 0.305 - Picture: Vivid(Medium )

Y 0.595 0.600 - - 100% Window

Blue X - 0.150 0.158

Y - 0.065 0.075

5. Color coordinate uniformity -0.01 Average +0.01 - 85IRE 100% Window White Pattern

- Picture: Vivid(Medium)

6. Contrast ratio at dark room 100k: 1 1,000k: 1 -1/100 white window pattern(Peak mode)

-100IRE(255Gray)

-Picture: Vivid(Medium)

-Input: HDMI-PC (1920*1080 60Hz)

7. Color Cool X 0.261 0.276 0.291 - 85IRE 100% Window White Pattern

Temperature Y 0.268 0.283 0.298 Warm : ColorGamut => WIDE

Medium X 0.270 0.285 0.300 Cool : Color temperature C30

Y 0.278 0.293 0.308 Meduum : Color temperature 0

Warm X 0.298 0.313 0.328 Warm : Color temperature W30

Y 0.314 0.329 0.344

Copyright ©2010 LG Electronics Inc. All rights reserved. -5- LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

ADJUSTMENT INSTRUCTION

1. Application Range Caution

- Use 'power on' button of a service R/C to power on TV set.

This spec. sheet is applied to all of the PA01A chassis - Do not connect any external input cable if there is no any

manufactured at LG TV Plant all over the world. specifics.

2. Designation 3. Update S/W using auto download

Caution: The module keeping condition through the USB.

Caution: S/W version of USB file (xxx.epk) must be bigger than

1. The module keeping condition: The normal temperature one which is downloaded previously.

condition(more than 15°C) 1. Insert the USB stick to the USB socket

-> Immediately the line supply. 2. A downloaded file in USB stick will be detected

2. The module keeping condition: 0°C automatically.

-> The module must be kept for more than 2 hours at the 3. If S/W version of USB file (xxx.epk) is bigger than one which

normal temperature. is downloaded previously, the message, “Copying files from

3. The module keeping condition: -20°C memory”, will appear.

-> The module must be kept for more than 3 hours at the 4. If an update procedure was completed, TV set will be turned

normal temperature. off and on automatically.

4. The case of Gu-mi factory at the winter season. 5. If TV set is turned on, check an updated version.

-> The module must be kept for more than 5 minutes at the * If a downloaded version is more bigger than one of which

heating zone(40°C~45°C). TV set had, TV set can lost channel data. In this case,

you have to scan channels again.

(1) The adjustment is according to the order which is

designated and which must be followed, according to the

plan which can be changed only on agreeing. 4. After downloading S/W, adjust

(2) If there is no specific designation, the adjustment must be

performed in the circumstance of 25 ±5∞C of temperature TOOL OPTION.

and 65±10% of relative humidity.

(3) The input voltage of the set must keep 100~240V, (1) Push "IN-START" button on a service R/C.

50/60Hz. (2) Select "Tool Option 1" and Push “OK” button.

(4) Input signal Unit: Product Specification Standard. (3) Put the number of a below table in order of a suffix of the

(5) The set must be operated for about 5 minutes prior to the “Tool Option(X)”.

adjustment. . (Each model has a different number.)

* After turning on RGB Full Window pattern in HEAT-RUN

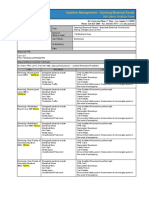

Mode, the receiver must be operated. Model Tool Option1 Tool Option2 Tool Option3 Tool Option4

* Enter into HEAT-RUN MODE 42PJ350-AB 25024 2632 51404 4384

1) Press the ‘POWER ON’ button on R/C for adjustment.

2) Press the ‘ADJ’ button on R/C and enter EZ ADJUST 42PJ650-AA 24896 2632 51408 4384

- Select "7. Test Pattern" by using F / G (CH +/-) and 50PJ350-AB 37312 2632 51404 4384

press ENTER(V)

50PJ650-AA 37184 2632 51408 4384

- Select "White" by using F / G (VOL +/-) and press

ENTER(V) 50PK550-AA 36992 2632 51404 4384

60PK550-AA 49280 2632 51404 4384

O Set heat run should be activated without a signal generator.

O Single color patterns (RED / BLUE / GREEN) of HEAT RUN

MODE are used to check a plasma panel.

O Caution: If you turn on a still screen more than 20 minutes

(Especially digital pattern, cross hatch pattern), an after

image may be made in the black level part of the screen.

Copyright ©2010 LG Electronics Inc. All rights reserved. -6- LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

5. ADC Calibration Procedure 6. EDID Download Procedure

(1) Input the component (480i/Horizontal Color Bar) signal to a (1) Push “ADJ” button on a service R/C.

TV set. (2) Enter EDID auto download mode by selecting ‘8. EDID

1) Input Signal Timing : Component 480i D/L’.

(Other external connection is unnecessary except the (3) If you select ‘Start’ on a dialog box of the screen, EDID

component before executing ADC calibration.) download will be begun automatically.

2) Input Signal Pattern

<Horizontal Color Bar pattern>

@ MODEL: 209 in Pattern Generator(480i Mode)

@ PATTERN : 65 in Pattern Generator(MSPG-925

SERISE) (4) Press ‘EXIT’ button on a service R/C.

(2) Push “ADJ” button on a service R/C. (5) EDID Data

(3) Enter internal ADC mode by selecting ‘5. ADC Calibration’. 1) HDMI (FHD Models, 256 bytes)

(4) If you select ‘Start’ on a dialog box of the screen, ADC

calibration will be begun.

Caution: Don’t connect any external input cable except the

component input(480i/Horizontal_Color_Bar) to adjust

ADC calibration

O Auto ADC Calibration Map(RS-232C) 2) RGB (HD Models, 128 bytes)

NO Item CMD1 CMD2 Data0

Enter Adjust When transfer the ‘Made

A A 0 0

Adjust MODE ‘Mode In’ In’, Carry the command.

ADC

ADC Adjust A D 1 0 Automatically adjustment

Adjust

# Adjust Sequence

- aa 00 00 [Enter Adjust Mode] O EDID Data detailing (ⓐ, ⓑ, ⓒ, ⓓ, ⓔ, ⓕ)

- xb 00 40 [Component1 Input (480i)]

- ad 00 10 [Adjust 480i Comp1]

- xb 00 60 [RGB Input (1024*768)]

- ad 00 10 [Adjust 1024*768 RGB]

- aa 00 90 End Adjust mode

Copyright ©2010 LG Electronics Inc. All rights reserved. -7- LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

ⓐ Product ID 7. POWER Supply Unit PCB Ass’y

MODEL EDID MODEL PRODUCT_ID FUNCTION Va/Vs Voltage Adjustment

ALL Model LG DTV 0001(0x01, 0x00) Analog

Caution: Both Vs and Va voltage adjustment are necessary.

ALL Model LG DTV 0001(0x01, 0x00) Digital

ⓑ Serial No 7-1. Va/Vs Adjustment Procedure

=> Controlled on production line (1) Connect positive(+) terminal of DMM to Vs/Va pin, connect

negative(-) terminal to GND.

ⓒ Month, Year (2) Turning ‘Vs/Va Adjust’ and adjust Vs/Va voltages to a

=> Controlled on production line: value which is written on a right/top label of a module.

(deviation ; ±0.5V)

ⓓ Model Name

ⓔ Checksum

=> Changeable by total EDID data

FHD HD

HDMI1 0xE2 0xB4 0xAF 0xE2

HDMI2 0xE2 0xA4 0xAF 0xE2

HDMI3 0xE2 0x94 0xAF 0xE2

HDMI4 - - - -

RGB 0x62 0x2F

Caution

- Each Power Supply Unit PCB assembly must be checked by

ⓕ HDMI Port No. check JIG set. (Because power PCB Ass’y damages to PDP

Module, especially be careful)

O Auto EDID Download Map(RS-232C) - Set up “RF mode(noise)” before a voltage adjustment.

- Test equipment: DMM 1EA

NO Item CMD1 CMD2 Data0

Enter

Download When transfer the ‘Made

download A A 0 0

‘Mode In’ In’, Carry the command.

MODE 8. White Balance Adjustment

EDID data and Automatically download

Model option Download A E 00 10 (The use of a internal Caution: Press the POWER ON KEY on R/C before W/B

download Data) adjustment.

O Test Equipment

Color Analyzer (CS-1000, CA-100+(CH.10), CA-210(CH.10))

O Please adjust CA-100+ / CA-210 by CS-1000 before

measuring

You should use Channel 10 which is Matrix compensated

(White, Red, Green, Blue revised) by CS-1000 and adjust

in accordance with White balance adjustment coordinate.

8-1. Color Temperature Standards According

to CSM and Module(TBD)

CSM PLASMA

Cool 11000K

Medium 9300K

Warm 6500K

Copyright ©2010 LG Electronics Inc. All rights reserved. -8- LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

8-2. Change Target Luminance and Range O Auto W/B Adjustment Map(RS-232C)

RS-232C COMMAND

of the Auto Adjustment W/B Equipment [ CMD ID DATA ]

Wb 00 00 White Balance Start

Target luminance 50

Wb 00 FF White Balance End

Range 20

RS-232C COMMAND CENTER

[CMD ID DATA] Min (DEFAULT) MA X

Cool Med Warm Cool Med Warm

8-3. White Balance Adjustment Coordinate R Gain jg Ja jd 00 192 192 192 255

and Color Temperature G Gain jh Jb je 00 192 192 192 255

B Gain ji Jc jf 00 192 192 192 255

Target luminance 50

R Cut 64 64 64 128

Range 20 50H3

G Cut 64 64 64 128

60H3

B C ut 64 64 64 128

8-4. White Balance Adjustment Coordinate

and Color Temperature

8-6. Manual W/B Adjustment

(1) Execute the zero calibration of CA-100+ / CA-210.

(2) Press the ‘ADJ’ button on a service R/C and enter EZ

ASJUST by selecting ‘6. White Balance’.

(3) Then, 216 gray pattern will appear on the screen.

(4) Change the R/G/B-Gain as passing in 3 color coordinates

and temperatures, COOL, MEDIUM and WARM.

< Temperature: COOL >

- R-Cut / G-Cut / B-Cut is set to 64

- Control R-Gain and G-Gain.

- Each gain is limited to 192

< Temperature: MEDIUM >

- R-Cut / G-Cut / B-Cut is set to 64

- Control R-Gain and G-Gain.

- Each gain is limited to 192

[ PC (for communication through RS-232C) ? UART Baud < Temperature: WARM >

rate : 115200 bps - R-Cut / G-Cut / B-Cut is set to 64

- Control G-Gain and B-Gain.

- Each gain is limited to 192

8-5. Automatic W/B Adjustment (5) Press ‘EXIT’ button on a service R/C

(1) Internal PATTERN should be used when W/B is adjusted.

Connect to auto controller like below.

(2) Start White-Balance adjustment, then the full white window

pattern will appear on the screen.

(3) Adjust in the place where the influx of light like floodlight

around is blocked.

(illumination is less than 10ux).

(4) Measure and adjust after sticking the Color Analyzer (CA-

100+, CA210 ) to the side of the module.

Copyright ©2010 LG Electronics Inc. All rights reserved. -9- LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

<Notice> Module Heat-Run Condition for W/B 9-3. Command Set

1. The adjustment must be performed in the circumstance of [Description]

25±5°C of temperature and 65±10% of relative humidity if FOS Default write : <7mode data> write

there is no any specifics. Vtotal, V_Frequency, Sync_Polarity, Htotal, Hstart, Vstart,

2. Before an W/B adjustment, the module which will be used 0, Phase

should be placed in the circumstance of 15°C~25°C for Data write : Model Name and Serial Number write in

above 2 hours. EEPROM,.

3. If a module was placed in the circumstance of below 15°C,

it should be placed in the circumstance of 15°C~25°C for

above 2 hours or be run for above 5 minutes in an aging

environment of 60°C. 10. Check Information (Serial No. & Model name)

4. Before an W/B adjustment, TV set should be run for 5

minutes at least. (1) Push the menu button in DTV mode.

(2) Select the SETUP -> Diagnostics -> To set

(3) Check the Serial Numbe

9. Serial Number Download

11. SET factoring condition

9-1. Download Procedure

(1) Press “Power on” button of a service R/C.(Baud rate : (1) This Adjustment result is set through factory shipment

115200 bps) mode.

(2) Connect RS232-C Signal Cable. (2) Push the ‘IN-STOP’ button on a service R/C before the

(3) Write Serial number through RS-232C. factory shipment and power button mush be pushed.

(4) Check the serial number at the Diagnostics of ‘SETUP’

menu. (Refer to below). Caution: If ‘IN-STOP’ button is pushed, preset CH map will be

lost.

Caution : Don’t download HDMI/RGB EEPROM to write a model

name. Model name dois unnecessary because this

model use ‘Tool Option’ to call a model name.

9-2. Signal TABLE

CMD : A0h

LENGTH : 85~94h (1~16 bytes)

ADH : EEPROM Sub Address high (00~1F)

ADL : EEPROM Sub Address low (00~FF)

Data : Write data

CS : CMD + LENGTH + ADH + ADL + Data_1 + ... +

Data_n

Delay : 20ms

Copyright ©2010 LG Electronics Inc. All rights reserved. - 10 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

TROUBLESHOOTING GUIDE

Copyright ©2010 LG Electronics Inc. All rights reserved. - 11 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

Copyright ©2010 LG Electronics Inc. All rights reserved. - 12 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

Copyright ©2010 LG Electronics Inc. All rights reserved. - 13 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

Copyright ©2010 LG Electronics Inc. All rights reserved. - 14 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

Copyright ©2010 LG Electronics Inc. All rights reserved. - 15 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

Copyright ©2010 LG Electronics Inc. All rights reserved. - 16 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

Copyright ©2010 LG Electronics Inc. All rights reserved. - 17 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

Copyright ©2010 LG Electronics Inc. All rights reserved. - 18 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

Copyright ©2010 LG Electronics Inc. All rights reserved. - 19 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

Copyright ©2010 LG Electronics Inc. All rights reserved. - 20 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

Copyright ©2010 LG Electronics Inc. All rights reserved. - 21 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

BLOCK DIAGRAM

Copyright ©2010 LG Electronics Inc. All rights reserved. - 22 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

EXPLODED VIEW

IMPORTANT SAFETY NOTICE

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essential that these special safety parts should be replaced with the same components as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

400

601

900

604

910

602

520

209

208

200

206

590

240

580

501

205

201

301

A12

302

207

204

A9

305

202

203

120

303

A10

302

LV1

570

300

A21

A2

310

Copyright ©2010 LG Electronics Inc. All rights reserved. - 23 - LGE Internal Use Only

Only for training and service purposes

Downloaded from www.Manualslib.com manuals search engine

IC100 X100

12MHz C111

+3.3V_ST LGE3369A (SATURN6 NON RM)

IC102 18pF

R193

+3.3V NAND512W3A2CN6E +3.3V 1M

NAND FLASH MEMORY S6_Reset

D4 HWRESET B3

C112

XIN

A3

XOUT

NC_1 NC_29 AC16 18pF

1 48 DEBUG PCMD0/CI_D0

TMUE312GAB

AA15

2

/PF_CE0 E6

NC_2 NC_28 PCMD1/CI_D1 TESTPIN/GND

SW100

H : Serial Flash 2 47 AA16

5

L : NAND Flash PCM_A[0-7] PCMD2/CI_D2

NC_3 NC_27 AC6

/PF_CE1 3 46 PCMD3/CI_D3

H : 16 bit R114 Y10 AE11 33 R1224 SPI_DI

1

NC_4 NC_26 100 PCMD4/CI_D4 SPI_DI

3.9K

1K

L : 8 bit 4 45 Y11 AF12

AR102 C102 PCMD5/CI_D5 SPI_DO

33 R1230 SPI_DO

NC_5 I/O7 PCM_A[7] 4.7uF Y12 AE12 33 R1225 SPI_CS

5 44 R116 PCM_A[0-7] PCMD6/CI_D6 /SPI_CS

10V 10 PCM_A[0-7] Y13 AD11 33 R1226

NC_6 I/O6 PCM_A[6] SPI_CK

PCMD7/CI_D7

R1240

S6_Reset SPI_CK

R111

6 43

RB I/O5 PCM_A[5] PCM_A[0] AB16

7 42 PCM_A0/CI_A0

KDS181

/F_RB PCM_A[1] AC15

R I/O4 PCM_A[4] C101

D100

R115 PCM_A[2] PCM_A1/CI_A1

/PF_OE 8 41 62K 0.1uF AC14

22 PCM_A[3] PCM_A2/CI_A2

E NC_25 AB14

/PF_CE0 9 40 PCM_A[4] PCM_A3/CI_A3

AC12 B5

NC_7 NC_24 PCM_A[5] PCM_A4/CI_A4 USB_DP_1

C105

1K

10 39 AB8 A5

10uF 6.3V

READY

PCM_A[6] PCM_A5/CI_A5 USB_DM_1

0.1uF

NC_8 NC_23 AC13 AC10

C103

11 38 PCM_A[7] PCM_A6/CI_A6 USB_DM_2 USB_DM

AA9 AB10

R112

USB

VDD_1 VDD_2 PCM_A7/CI_A7 USB_DP_2 USB_DP

12 37 AB5 R196 R197

PCM_A8/CI_A8 15K

VSS_1 VSS_2 C106 0.1uF AA4 15K

+3.3V READY 13 36 PCM_A9/CI_A9 READY

V4 READY

R105 NC_9 NC_22 PCM_A10/CI_A10

1K 14 35 Y4

PCM_A11/CI_A11

NC_10 NC_21 AB9

15 34 PCM_A12/CI_A12 R131 100

AA7 DBG_TX

CL NC_20 PCM_A13/CI_A13 +5V_ST

16 33 AD6 R130 100 AC_DET

/PF_CE1 AR103

R103

PCM_A14/CI_A14

10K

AL I/O3 PCM_A[3] PM GPIO Assignment Recommended by MStar

PF_ALE 17 32

AA14 E5 R1294 10K

W I/O2 PCM_A[2] PCM_RST/CI_RST GPIO_PM0/GPIO134 LED_R

/PF_WE 18 31 AB18 F5 R182 100 READY R195 AC_DET

PCM_CD/CI_CD GPIO_PM1/GPIO135

WP I/O1 PCM_A[1] Y5 G5 R185 100 10K

PF_WP 19 30 /PCM_OE GPIO_PM2/GPIO136 READY MODULE_ON

AB15 H5 100

R1239

R160 DISP_EN

NC_11 I/O0 PCM_A[0] PCM_REG/CI_CLK GPIO_PM3/GPIO137

20 29 AA10 F6 R186 100 RL_ON/PWR_ONOFF

1K

PCM_WAIT/CI_WACK GPIO_PM4/GPIO138 R134

NC_12 NC_19 22 AC8 G6

READY

21 28 /PCM_IRQA GPIO_PM5/INT1/GPIO139 27K DBG_RX

AC7 H6 100 R187

NC_13 NC_18 /PCM_WE GPIO_PM6/INT2/GPIO140 ISP_TXD

22 27 AA5 AC17 +3.3V

PCM_IOWR/CI_WR GPIO131/LDE/SPI_WPn1

R1203

R1202

NC_14 NC_17 W4 AB17

AR171

4.7K

4.7K

23 26 PCM_IOR/CI_RD GPIO130/LCK

T4 AF11 R159 100 Flash_WP_1

NC_15 NC_16 /PCM_CE GPIO132/LHSYNC/SPI_WPn

24 25 /PF_CE0 AE6 AA18 R1235 22 SDA1

/PF_CE0 GPIO60/PCM2_RESET/RX1

/PF_CE1 AF6 AA17 R1236 22 SCL1

/PF_CE1 GPIO62/PCM2_CD_N/TX1

/PF_OE AA12 +3.3V

22 /PF_OE

/PF_WE AR101 AA11

/PF_WE

R1205

R1204

PF_ALE AC9

4.7K

4.7K

PF_ALE

PF_WP Y14 +3.3V

PF_AD15

/F_RB +3.3V AB11 E7 R1237 22

F_RBZ LHSYNC2/I2S_OUT_MUTE/RX1 SUB_SCL

22

R1279

AC18 R1286 0

READY

4.7K

+3.3V LVSYNC/GPIO133 5V_HDMI_2

EEPROM_SCL R162 22 F8 C6 R1238 22

UART2_TX/SCKM GPIO79/LVSYNC2/TX1 SUB_SDA

R101

+3.3V

R102

IC103 +3.3V +3.3V_ST EEPROM_SDA R163 22 D11 F9

1K

UART2_RX/SDAM UART2_RX/GPIO84 H/W Version Opiton(F9)

1K

R1278

Serial FLASH MEMORY MX25L4005AM2C-12G IC105 PDP_SDA R164 22 AB21 F10

4.7K

USB_OCD

READY

R1233

DDCR_DA UART2_TX/GPIO85

L102

L101

M24M01-HRMN6TP 22 AC21 A6 100 R1277

4.7K

READY

for BOOT PDP_SCL R165

MOD_ROM_RX

R135 R133

4.7K

C116 C117 DDCR_CK UART1_RX/GPIO86 100

B6 R1276

CS# VCC 100pF 100pF UART1_TX/GPIO87 MOD_ROM_TX

SPI_CS 1 8 NC VCC 22 J1 AF5

1 8 ISP_RXD 50V 50V R140 C108 C107

C100 DDCA_CLK GPIO42/PCM2_CE_N

+3.3V 22 J2 AF10 10pF 10pF

0.1uF

0.1uF ISP_TXD R141 AV_DET

DDCA_DA GPIO43/PCM2_IRQA_N 50V 50V

C104

SO HOLD# E1 WP W5

0

DBG_RX R1297 100

R124

SPI_DO 2 7 READY READY

R125

2 7

R104

UART_RX2

10K

R1296 100 V5 AA8

2K

DBG_TX

2K

E2 SCL

UART_TX2 TS0_D0

3 6 Y8

WP# SCLK EEPROM_SCL TS0_D1

3 6 SPI_CK Y9

VSS SDA LGE3369A TS0_D2

4 5 AB7

Flash_WP_1 EEPROM_SDA TS0_D3

GND SI AA6

4 5 SPI_DI TS0_D4

AB6

TS0_D5

U4

TS0_D6

AC5

TS0_D7

AC4

TS0_SYNC

AD5

TS0_VLD

AB4

TS0_CLK

AB19 FE_TS_SERIAL

TS1_D0

AA20 FE_TS_SYN

TS1_SYNC

AB13 AC19

HDCP EEPROM +5V MCU BOOT STRAP PWM0

PWM0 TS1_VLD FE_TS_VAL

PWM1 AB12 AA19

PWM1 TS1_CLK FE_TS_CLK

KEY_BUZZER AD12

PWM2

R1287 100 READY AA13 C10

10 : BOOT 51 PWM3 ET_TXD0 SIDE_CVBS_DET

11 : BOOT RISC B11

IC107 +3.3V ET_TXD1

+3.3V A4 A9

CAT24WC08W-T SAR0

R1298

KEY1 ET_TX_CLK

R1256 B4 C11 +3.3V

10K

4.7K KEY2 SAR1 ET_RXD0 TU_SLEEP_MODE

A0 1 VCC 100 R1242 F4 C9 R1283 0

8 LED_B 5V_HDMI_3

R110 R198 1K 0 R106 SAR2 ET_RXD1

A1 2 WP 4.7K

E4 B10 R190 22 R1270

7 SB_MUTE SAR3 ET_TX_EN 4.7K

READY C4 A10 R191 0

PWM0 IR 5V_HDMI_1 5V Tolerance

IRIN ET_MDC

A2 3 SCL R1257 22 R199 1K B9

6 EEPROM_SCL /FE_RESET

ET_MDIO

R1201 1K A11

VSS

4 5

SDA READY PWM1 ET_COL COMP2_DET

EEPROM_SDA AC11 R1269

R1258 22 C114 R1200 1K GPIO44 4.7K

0.1uF +3.3V READY

D9

GPIO96

AMP_RST D10

R1271 GPIO88

+3.3V 4.7K D7

HD GPIO90/I2S_OUT_MUTE

R1241

E11

10K

XC5000_RESET GPIO91

E8

GPIO97

E10

ST_AMP_MUTE R1268 GPIO98

4.7K D6

GPIO99

FHD D5

COMP1_DET GPIO103/I2S_OUT_SD3

C5

DSUB_DET GPIO102

READY

READY

READY

READY

4.7K

4.7K

4.7K

4.7K

IC100-*1 IC100-*2

LGE4369A (SATURN6 NON RM_NON SRS) LGE4368A (SATURN6 NO-DIVX_NON SRS)

D4 B3 D4 B3

HWRESET XIN HWRESET XIN

A3 A3

XOUT XOUT

AC16 AC16

PCMD0/CI_D0 PCMD0/CI_D0

AA15 E6 AA15 E6

PCMD1/CI_D1 TESTPIN/GND PCMD1/CI_D1 TESTPIN/GND

AA16 AA16

PCMD2/CI_D2 PCMD2/CI_D2

AC6 AC6

PCMD3/CI_D3 PCMD3/CI_D3

Y10 AE11 Y10 AE11

PCMD4/CI_D4 SPI_DI PCMD4/CI_D4 SPI_DI

Y11 AF12 Y11 AF12

PCMD5/CI_D5 SPI_DO PCMD5/CI_D5 SPI_DO

Y12 AE12 Y12 AE12

PCMD6/CI_D6 /SPI_CS PCMD6/CI_D6 /SPI_CS

Y13 AD11 Y13 AD11

PCMD7/CI_D7 SPI_CK PCMD7/CI_D7 SPI_CK

R1300

R137

R1299

R1275

AB16 AB16

PCM_A0/CI_A0 PCM_A0/CI_A0

AC15 AC15

PCM_A1/CI_A1 PCM_A1/CI_A1

AC14 AC14

PCM_A2/CI_A2 PCM_A2/CI_A2

AB14 AB14

PCM_A3/CI_A3 PCM_A3/CI_A3

AC12 B5 AC12 B5

PCM_A4/CI_A4 USB_DP_1 PCM_A4/CI_A4 USB_DP_1

AB8 A5 AB8 A5

PCM_A5/CI_A5 USB_DM_1 PCM_A5/CI_A5 USB_DM_1

AC13 AC10 AC13 AC10

PCM_A6/CI_A6 USB_DM_2 PCM_A6/CI_A6 USB_DM_2

AA9 AB10 AA9 AB10

PCM_A7/CI_A7 USB_DP_2 PCM_A7/CI_A7 USB_DP_2

AB5 AB5

PCM_A8/CI_A8 PCM_A8/CI_A8

AA4 AA4

PCM_A9/CI_A9 PCM_A9/CI_A9

V4 V4

PCM_A10/CI_A10 PCM_A10/CI_A10

Y4 Y4

PCM_A11/CI_A11 PCM_A11/CI_A11

AB9 AB9

PCM_A12/CI_A12 PCM_A12/CI_A12

AA7 AA7

PCM_A13/CI_A13 PCM_A13/CI_A13

AD6 AD6

PCM_A14/CI_A14 PCM_A14/CI_A14

AA14 E5 AA14 E5

PCM_RST/CI_RST GPIO_PM0/GPIO134 PCM_RST/CI_RST GPIO_PM0/GPIO134

AB18 F5 AB18 F5

PCM_CD/CI_CD GPIO_PM1/GPIO135 PCM_CD/CI_CD GPIO_PM1/GPIO135

Y5 G5 Y5 G5

/PCM_OE GPIO_PM2/GPIO136 /PCM_OE GPIO_PM2/GPIO136

AB15 H5 AB15 H5

PCM_REG/CI_CLK GPIO_PM3/GPIO137 PCM_REG/CI_CLK GPIO_PM3/GPIO137

AA10 F6 AA10 F6

PCM_WAIT/CI_WACK GPIO_PM4/GPIO138 PCM_WAIT/CI_WACK GPIO_PM4/GPIO138

AC8 G6 AC8 G6

/PCM_IRQA GPIO_PM5/INT1/GPIO139 /PCM_IRQA GPIO_PM5/INT1/GPIO139

AC7 H6 AC7 H6

/PCM_WE GPIO_PM6/INT2/GPIO140 /PCM_WE GPIO_PM6/INT2/GPIO140

AA5 AC17 AA5 AC17

PCM_IOWR/CI_WR GPIO131/LDE/SPI_WPn1 PCM_IOWR/CI_WR GPIO131/LDE/SPI_WPn1

W4 AB17 W4 AB17

PCM_IOR/CI_RD GPIO130/LCK PCM_IOR/CI_RD GPIO130/LCK

T4 AF11 T4 AF11

/PCM_CE GPIO132/LHSYNC/SPI_WPn /PCM_CE GPIO132/LHSYNC/SPI_WPn

AE6 AA18 AE6 AA18

/PF_CE0 GPIO60/PCM2_RESET/RX1 /PF_CE0 GPIO60/PCM2_RESET/RX1

AF6 AA17 AF6 AA17

/PF_CE1 GPIO62/PCM2_CD_N/TX1 /PF_CE1 GPIO62/PCM2_CD_N/TX1

AA12 AA12

/PF_OE /PF_OE

AA11 AA11

/PF_WE /PF_WE

AC9 AC9

PF_ALE PF_ALE

Y14 Y14

PF_AD15 PF_AD15

AB11 E7 AB11 E7

F_RBZ LHSYNC2/I2S_OUT_MUTE/RX1 F_RBZ LHSYNC2/I2S_OUT_MUTE/RX1

AC18 AC18

LVSYNC/GPIO133 LVSYNC/GPIO133

F8 C6 F8 C6

UART2_TX/SCKM GPIO79/LVSYNC2/TX1 UART2_TX/SCKM GPIO79/LVSYNC2/TX1

D11 F9 D11 F9

UART2_RX/SDAM UART2_RX/GPIO84 UART2_RX/SDAM UART2_RX/GPIO84

AB21 F10 AB21 F10

DDCR_DA UART2_TX/GPIO85 DDCR_DA UART2_TX/GPIO85

AC21 A6 AC21 A6

DDCR_CK UART1_RX/GPIO86 DDCR_CK UART1_RX/GPIO86

B6 B6

UART1_TX/GPIO87 UART1_TX/GPIO87

+3.3V

J1 AF5 J1 AF5

DDCA_CLK GPIO42/PCM2_CE_N DDCA_CLK GPIO42/PCM2_CE_N

J2 AF10 J2 AF10

DDCA_DA GPIO43/PCM2_IRQA_N DDCA_DA GPIO43/PCM2_IRQA_N

W5 W5

UART_RX2 UART_RX2

V5 AA8 V5 AA8

UART_TX2 TS0_D0 UART_TX2 TS0_D0

Y8 Y8

TS0_D1 TS0_D1

Y9 Y9

LGE4369 TS0_D2 LGE4368 TS0_D2

AB7 AB7

TS0_D3 TS0_D3

AA6 AA6

TS0_D4 TS0_D4

AB6 AB6

TS0_D5 TS0_D5

U4 U4

TS0_D6 TS0_D6

AC5 AC5

TS0_D7 TS0_D7

AC4 AC4

TS0_SYNC TS0_SYNC

AD5 AD5

TS0_VLD TS0_VLD

AB4 AB4

TS0_CLK TS0_CLK

AB19 AB19

TS1_D0 TS1_D0

AA20 AA20

TS1_SYNC TS1_SYNC

AB13 AC19 AB13 AC19

PWM0 TS1_VLD PWM0 TS1_VLD

AB12 AA19 AB12 AA19

PWM1 TS1_CLK PWM1 TS1_CLK

AD12 AD12

PWM2 PWM2

AA13 C10 AA13 C10

PWM3 ET_TXD0 PWM3 ET_TXD0

B11 B11

ET_TXD1 ET_TXD1

A4 A9 A4 A9

SAR0 ET_TX_CLK SAR0 ET_TX_CLK

B4 C11 B4 C11

SAR1 ET_RXD0 SAR1 ET_RXD0

F4 C9 F4 C9

SAR2 ET_RXD1 SAR2 ET_RXD1

E4 B10 E4 B10

SAR3 ET_TX_EN SAR3 ET_TX_EN

C4 A10 C4 A10

IRIN ET_MDC IRIN ET_MDC

B9 B9

ET_MDIO ET_MDIO

A11 A11

ET_COL ET_COL

AC11 AC11

GPIO44 GPIO44

D9 D9

GPIO96 GPIO96

D10 D10

GPIO88 GPIO88

D7 D7

GPIO90/I2S_OUT_MUTE GPIO90/I2S_OUT_MUTE

E11 E11

GPIO91 GPIO91

E8 E8

GPIO97 GPIO97

E10 E10

GPIO98 GPIO98

D6 D6

GPIO99 GPIO99

D5 D5

GPIO103/I2S_OUT_SD3 GPIO103/I2S_OUT_SD3

C5 C5

GPIO102 GPIO102

A7 A7

GPIO67 GPIO67

B8 B8

GPIO68 GPIO68

A7 R192 100

GPIO67 USB_CTL

B8

GPIO68

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS MSD3368EV Platform 09/11/17

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC. FLASH/NVRAM/GPIO 1 10

Copyright © 2010 LG Electronics Inc. All rights reserved.

Downloaded from

Only for training and www.Manualslib.com

service purposes manuals search engine LGE Internal Use Only

+1.26V_VDDC

C240 C246 C257 C264 C275 C281 C2000 C2003 C2005

470uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

16V

Audio Mute

+1.26V_VDDC

C2032 C2033 C2034 C2035 C2036 C2037 C2038 C2039 C2040 C2041

D201 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

ENKMC2838-T112

A1

SB_MUTE

C

AMP_MUTE

A2

ST_AMP_MUTE

+3.3V_VDDP +3.3V

L210

MLB-201209-0120P-N2

C250 C253 C258 C2026 C2004

0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

+1.8V_DDR

C245 C248 C259 C266 C277 C283 C291 C296

C2048

0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

IC100 470uF

16V

LGE3369A (SATURN6 NON RM)

F1 RXACKP AE16

CK+_HDMI1 LVA0P RXE0+

F2 RXACKN AD16

CK-_HDMI1 LVA0M RXE0-

G2 RXA0P AD15

D0+_HDMI1 LVA1P RXE1+ IC100

D0-_HDMI1

G3 RXA0N AF16

RXE1-

+1.26V_VDDC

H3 RXA1P

LVA1M

AF15 LGE3369A (SATURN6 NON RM)

D1+_HDMI1 LVA2P RXE2+

G1 RXA1N AE15

D1-_HDMI1 LVA2M RXE2-

H1 RXA2P AD13

D2+_HDMI1 LVA3P RXE3+ E16 VDDC_1 D16

H2 RXA2N AF14 GND_2

D2-_HDMI1 LVA3M RXE3- E17 VDDC_2 D17

A1 DDCD_A_DA AF13 GND_3

DDC_SDA_1 LVA4P RXE4+ E18 D18

B2 DDCD_A_CK AE13 VDDC_3

DDC_SCL_1 GND_4

LVA4M RXE4- F7 VDDC_4 D19

R258 1K A2 HOTPLUG_A GND_5

HPD1 L9 D20

LVDS OUT

AE14 VDDC_5

GND_6

LVACKP RXECK+ L10 VDDC_6 H18

C3 RXBCKP AD14 GND_7

CK+_HDMI2 LVACKM RXECK- L11 VDDC_7 H19

B1 RXBCKN GND_8

CK-_HDMI2 VDDC_8 H20

C1 RXB0P AE20

D0+_HDMI2 LVB0P RXO0+ VDDC_9 J20

C2 RXB0N AD20

D0-_HDMI2 LVB0M RXO0- L12 VDDC_10 K20

D2 RXB1P AD19 GND_9

D1+_HDMI2 LVB1P RXO1+ L13 VDDC_11 L20

D3 RXB1N AF20 GND_10

D1-_HDMI2 LVB1M RXO1- L14 VDDC_12 M20

E3 RXB2P AF19 GND_11

D2+_HDMI2 LVB2P RXO2+ L15 VDDC_13 P7

D1 RXB2N AE19 GND_12

D2-_HDMI2 LVB2M RXO2- L16 VDDC_14 R7

E1 DDCD_B_DA AD17 GND_13

DDC_SDA_2 LVB3P RXO3+ L17 T7

F3 DDCD_B_CK AF18 GND_14 VDDC_15

DDC_SCL_2 LVB3M RXO3- L18 T22

HDMI

1K E2 HOTPLUG_B AF17 GND_15 VDDC_16

HPD2 R203

LVB4P RXO4+ M9 GND_16 U7

AE17 VDDC_17

LVB4M RXO4- U20

AE8 RXCCKP VDDC_18

CK+_HDMI3 M10 GND_17 U22

AD8 RXCCKN AE18 VDDC_19

CK-_HDMI3 LVBCKP RXOCK+ M11 GND_18 V7

AD9 RXC0P AD18 VDDC_20

D0+_HDMI3 LVBCKM RXOCK- M12 V22

AF8 RXC0N GND_19 VDDC_21

D0-_HDMI3 M13 W11

AF9 RXC1P GND_20 VDDC_22

D1+_HDMI3 M14 W12

AE9 RXC1N GND_21 VDDC_23

D1-_HDMI3 M15 W19

AE10 RXC2P AA3 C229 2.2uF GND_22 VDDC_24

D2+_HDMI3 AUR0 COMP1_RIN M16 W20

AD10 RXC2N Y1 C230 2.2uF GND_23 VDDC_25

D2-_HDMI3 AUL0 COMP1_LIN M17 W22

AE7 DDCD_C_DA AE1 C2006 2.2uF GND_24 VDDC_26

DDC_SDA_3 AUR1 Y22

AF7 DDCD_C_CK AF3 C2007 2.2uF VDDC_27

DDC_SCL_3 AUL1 M18

HPD3 R285 1K AD7 HOTPLUG_C AE3 C2008 2.2uF GND_25 +3.3V_VDDP

AUR2 SIDE_RIN N4

AUDIO IN

R204 100 J3 CEC AUL2 AE2 C2009 2.2uF GND_26

HDMI_CEC SIDE_LIN N9 H9

AA1 C2011 2.2uF GND_27 VDDP_1

AUR3 AV_RIN N10 H10

AB1 C2012 2.2uF GND_28 VDDP_2

AUL3 AV_LIN N11 H11

AB2 C2013 2.2uF GND_29 VDDP_3

AUR4 COMP2_RIN N12 H12

N2 HSYNC0/SC1_ID AC2 C2014 2.2uF GND_30 VDDP_4

AUL4 COMP2_LIN N13 N20

N1 VSYNC0/SC1_FB AB3 C2015 2.2uF GND_31 VDDP_5

AUR5 PC_RIN N14 P20

47 C200 0.047uF P2 RIN0P/SC1_R AC3 GND_32 VDDP_6

COMP1

R211 C2016 2.2uF

COMP1_Pr AUL5 PC_LIN W9

R212 47 C201 0.047uF R3 GIN0P/SC1_G VDDP_7

COMP1_Y N15 W10

R213 47 C202 0.047uF R1 BIN0P/SC1_B GND_33 VDDP_8

COMP1_Pb N16 +3.3V_AVDD

R214 470 C203 1000pF P3 SOGIN0/SC1_CVBS GND_34

N17 L209

R215 47 C204 0.047uF P1 RINM W3 C231 0.1uF R241 47 GND_35 MLB-201209-0120P-N2

SIF0P TUNER_SIF N18 W7

R216 47 C205 0.047uF T3 BINM W2 C232 0.1uF R242 47 GND_36 AVDD_AU

SIF0M P4 +1.8V_DDR

R217 47 C206 0.047uF R2 GINM GND_37

P9 C284 C293

GND_38

R243 R244 P10 G12

F11 R282 0 GND_39 AVDD_DDR_1 0.1uF 0.1uF

10K 10K SPDIF_IN PSU_ERR_DET G13

R246 22 K3 HSYNC1/DSUB_HSYNC E9 R230 100 AVDD_DDR_2

DSUB_HSYNC SPDIF_OUT SPDIF_OUT H13

R245 22 K2 VSYNC1/DSUB_VSYNC AVDD_DDR_3

DSUB_VSYNC P11 H14

R218 47 C212 0.047uF L1 RIN1P/DSUB_R GND_40 AVDD_DDR_4

DSUB

DSUB_R P12 H15

R219 47 C207 0.047uF L3 GIN1P/DSUB_G GND_41 AVDD_DDR_5

DSUB_G P13 H16

R220 47 C213 0.047uF K1 BIN1P/DSUB_B GND_42 AVDD_DDR_6

DSUB_B P14 W14

R221 470 C208 1000pF L2 SOGIN1 AF1 GND_43 AVDD_DDR_7

AUOUTR0/HP_ROUT P15 W15

AF2

AUDIO OUT

GND_44 AVDD_DDR_8

AUOUTL0/HP_LOUT P16 W16

AD3 GND_45 AVDD_DDR_9

AUOUTR1/SC1_ROUT P17 W17

R222 47 C214 0.047uF V1 RIN2P/COMP_PR+ AD1 GND_46 AVDD_DDR_10 +3.3V

COMP2

COMP2_Pr AUOUTL1/SC1_LOUT P18 W18

R223 47 C215 0.047uF V2 GIN2P/COMP_Y+ AC1 GND_47 AVDD_DDR_11

COMP2_Y AUOUTR2/SC2_ROUT L205

R224 47 C216 0.047uF U1 BIN2P/COMP_PB+ AD2 MLB-201209-0120P-N2

COMP2_Pb AUOUTL2/SC2_LOUT R4 H17

R225 470 C209 1000pF V3 SOGIN2 GND_48 AVDD_MEMPLL_1

R9 T20

J5 VSYNC2 GND_49 AVDD_MEMPLL_2 C262 C269 C273 C285

R10 V20

GND_50 AVDD_MEMPLL_3

R11

A8 R231 22 GND_51 0.1uF 0.1uF 0.1uF 0.1uF

I2S_OUT_MCK AUDIO_MASTER_CLK R12 +3.3V

B7 R232 22 GND_52

R205 47 C210 0.047uF U3 CVBS1/SC1_CVBS I2S_OUT_WS MS_LRCK R13

C7 R233 22 GND_53

0.047uF U2 CVBS2/SC2_CVBS R14

CVBS

R206 47 C211 I2S_OUT_BCK MS_SCK L207

SIDE_CVBS_IN D8 R234 22 GND_54 MLB-201209-0120P-N2

R226 47 C217 0.047uF T1 CVBS3/SIDE_CVBS I2S_OUT_SD MS_LRCH R15 R20

AV_CVBS_IN C8 R279 100 GND_55 AVDD_LPLL

R227 47 C218 0.047uF T2 VCOM1 I2S_IN_SD C236 C237 C238 C239 +3.3V_AVDD_MPLL

22pF 22pF 22pF 22pF R16 C2030 C279 C288

READY READY READY READY GND_56

R17 H7

R207 47 C219 0.047uF M1 CVBS4/S-VIDEO_Y +3.3V C235 GND_57 AVDD_MPLL 0.1uF 0.1uF 0.1uF

R18

R208 47 C220 0.047uF M2 CVBS6/S-VIDEO_C K4 C223 0.1uF GND_58 C255 C2025 C263

VCLAMP 0.1uF T5

H4 C233 GND_59 10uF 0.1uF

REFP T9 6.3V

R235 47 C2024 0.047uF N3 CVBS5 J4 GND_60 0.1uF

REFM 0.1uF T10

R236 47 C2019 0.047uF M3 CVBS7 G4 R229 390 GND_61

REXT C234 T11 +3.3V_AVDD

1% 0.1uF GND_62

T12 L206

R228 100 C221 0.047uF W1 CVBS0/RF_CVBS Check GND_63 MLB-201209-0120P-N2

TV/MNT

TUNER_CVBS J7

R209 100 C222 0.047uF Y3 VCOM0 AE5 C224 0.1uF AVDD_33_1

AUCOM T13 K7

AE4 GND_64 AVDD_33_2 C241 C242 C286

AUVRM T14 L7

Y2 CVBSOUT0/SC2_MNTOUT AF4 C225 10uF GND_65 AVDD_33_3

AUVRP T15 M7 0.1uF 0.1uF 0.1uF

AA2 CVBSOUT1 AD4 C226 0.1uF GND_66 AVDD_33_4

TP203 AUVAG T16 N7

C227 1uF GND_67 AVDD_33_5 +3.3V

T17

C228 4.7uF GND_68

T18

GND_69 L208

U5 W8

GND_70 AVDD_DM

W13 +3.3V MLB-201209-0120P-N2

GND_71 C287 C292

Y21 L202

GND_72 MLB-201209-0120P-N2

AA23 H8

GND_73 AVDD_USB 0.1uF 0.1uF

C2044 C2043 C256 C272

10uF 2.2uF

Close to IC 6.3V 10V 0.1uF 0.1uF

as close as possible

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS MSD3368EV Platform

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC. AV IN_OUT/LVDS/POWER 2 10

AV IN_OUT/LVDS/POWER

Copyright © 2010 LG Electronics Inc. All rights reserved.

Downloaded from www.Manualslib.com manuals search engine

Only for training and service purposes LGE Internal Use Only

DDR2 1.8V By CAP - Place these Caps near Memory

+1.8V_DDR +1.8V_S_DDR

L300

MLB-201209-0120P-N2

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

C325

C327

C329

10uF

C330

C331

C332

C334

C336

C337

C338

C339

C340

C341

0.1uF

0.1uF

C302

C324

C326

C328

C342

C323

C314

10uF

C303

10uF

10uF

C304

C305

C306

C307

C308

C310

C312

C313

C315

C316

C317

C318

C319

C320

0.1uF 0.1uF

+1.8V_S_DDR

+1.8V_S_DDR +1.8V_S_DDR

1K 1%

R345

R301

R321

1K 1%

1%

1K

C335 1000pF

0.1uF

0.1uF

C300 1000pF

C333 0.1uF

R302 1K 1%

1%

1%

1000pF

R322

R343

IC100

IC300 IC301

1K

C311

1K

C301

C309

HYB18TC1G160C2F-2.5 LGE3369A (Saturn6 Non RM) HYB18TC512160B2F-2.5

SDDR_D[0] DQ0 G8 J2 VREF AR300 D15 VREF J2 G8 DQ0 TDDR_D[0]

SDDR_A[5] ADDR2_A[5] A_MVREF

SDDR_D[1] DQ1 G2 AR303 G2 DQ1 TDDR_D[1]

SDDR_A[3] ADDR2_A[3] BDDR2_A[9] TDDR_A[9]

SDDR_D[2] DQ2 H7 H7 DQ2 TDDR_D[2]

M8 A0 SDDR_A[0] SDDR_A[1] ADDR2_A[1] ADDR2_A[0] C13 T26 BDDR2_A[0] BDDR2_A[3] TDDR_A[3] TDDR_A[0] A0 M8

SDDR_D[3] DQ3 H3 A_DDR2_A0 B_DDR2_A0 H3 DQ3 TDDR_D[3]

A1 SDDR_A[1] SDDR_A[10] 56 56 ADDR2_A[10] ADDR2_A[1] A22 AF26 BDDR2_A[1] BDDR2_A[1] TDDR_A[1] TDDR_A[1] A1

DQ4 M3 M3 DQ4

SDDR_D[4] H1 A_DDR2_A1 B_DDR2_A1 H1 TDDR_D[4]

M7 A2 SDDR_A[2] ADDR2_A[2] B13 T25 BDDR2_A[2] BDDR2_A[10] 56 TDDR_A[10] TDDR_A[2] A2 M7

SDDR_A[0-12]

TDDR_D[0-15]

SDDR_D[5] DQ5 AR301 A_DDR2_A2 B_DDR2_A2 DQ5 TDDR_D[5]

ADDR2_A[0-12]

H9 AR304 H9

SDDR_D[0-15]

N2 A3 SDDR_A[3] SDDR_A[9] ADDR2_A[9] ADDR2_A[3] C22 AF23 BDDR2_A[3] TDDR_A[3] A3 N2

SDDR_D[6] DQ6 F1 A_DDR2_A3 B_DDR2_A3 F1 DQ6 TDDR_D[6]

N8 A4 SDDR_A[4] SDDR_A[12] ADDR2_A[12] ADDR2_A[4] A13 T24 BDDR2_A[4] TDDR_A[4] A4 N8

BDDR2_A[5] TDDR_A[5]

TDDR_A[0-12]

SDDR_D[7] DQ7 A_DDR2_A4 B_DDR2_A4 DQ7 TDDR_D[7]

BDDR2_A[0-12]

F9 A5 A23 AE23 BDDR2_A[5] A5 F9

N3 SDDR_A[5] SDDR_A[7] ADDR2_A[7] ADDR2_A[5] BDDR2_A[12] TDDR_A[12] TDDR_A[5] N3

SDDR_D[8] DQ8 C8 A_DDR2_A5 B_DDR2_A5 C8 DQ8 TDDR_D[8]

N7 A6 SDDR_A[6] AR302 ADDR2_A[6] C12 R26 BDDR2_A[6] 56 TDDR_A[6] A6 N7

SDDR_D[9] DQ9 SDDR_A[0] ADDR2_A[0] A_DDR2_A6 B_DDR2_A6 BDDR2_A[7] TDDR_A[7] DQ9 TDDR_D[9]

C2 A7 B23 AD22 BDDR2_A[7] A7 C2

P2 SDDR_A[7] ADDR2_A[7] AR305 TDDR_A[7] P2

SDDR_D[10] DQ10 D7 SDDR_A[2] ADDR2_A[2] A_DDR2_A7 B_DDR2_A7 BDDR2_A[0] TDDR_A[0] D7 DQ10 TDDR_D[10]

P8 A8 SDDR_A[8] ADDR2_A[8] B12 R25 BDDR2_A[8] TDDR_A[8] A8 P8

SDDR_D[11] DQ11 D3 SDDR_A[4] ADDR2_A[4] A_DDR2_A8 B_DDR2_A8 BDDR2_A[2] TDDR_A[2] D3 DQ11 TDDR_D[11]

P3 A9 SDDR_A[9] ADDR2_A[9] C23 AC22 BDDR2_A[9] TDDR_A[9] A9 P3

SDDR_D[12] DQ12 D1 SDDR_A[6] 56 ADDR2_A[6] A_DDR2_A9 B_DDR2_A9 BDDR2_A[4] TDDR_A[4] D1 DQ12 TDDR_D[12]

M2 A10/AP SDDR_A[10] ADDR2_A[10] B22 AD23 BDDR2_A[10] TDDR_A[10] A10/AP M2

SDDR_D[13] DQ13 SDDR_A[11] R319 56 ADDR2_A[11] A_DDR2_A10 B_DDR2_A10 BDDR2_A[6] 56 TDDR_A[6] DQ13 TDDR_D[13]

D9 A11 R24 BDDR2_A[11] A11 D9

P7 SDDR_A[11] ADDR2_A[11] A12 TDDR_A[11] P7

SDDR_D[14] DQ14 B1 SDDR_A[8] R320 56 ADDR2_A[8] A_DDR2_A11 B_DDR2_A11 BDDR2_A[11] R325 56 TDDR_A[11] B1 DQ14 TDDR_D[14]

R2 A12 SDDR_A[12] ADDR2_A[12] A24 AE22 BDDR2_A[12] TDDR_A[12] A12 R2

SDDR_D[15] DQ15 B9 A_DDR2_A12 B_DDR2_A12 BDDR2_A[8] R326 56 TDDR_A[8] B9 DQ15 TDDR_D[15]

+1.8V_S_DDR +1.8V_S_DDR

L2 BA0 SDDR_BA[0] 56 R303 ADDR2_BA[0] C24 AC23 BDDR2_BA[0] R327 56 TDDR_BA[0] BA0 L2

A_DDR2_BA0 B_DDR2_BA0

L3 BA1 SDDR_BA[1] 56 R304 ADDR2_BA[1] B24 AC24 BDDR2_BA[1] R328 56 TDDR_BA[1] BA1 L3

VDD5 A1 A_DDR2_BA1 B_DDR2_BA1 A1 VDD5

L1 BA2 SDDR_BA[2] 56 R305 ADDR2_BA[2] D24 AB22

VDD4 E1 A_DDR2_BA2 B_DDR2_BA2 E1 VDD4

R351 22 R306 ADDR2_MCLK B14 V25 BDDR2_MCLK R330 22

VDD3 J9 0 A_DDR2_MCLK B_DDR2_MCLK CK J8 J9 VDD3

READY

READY

READY

R300

R344

150

150

VDD2 M9 J8 CK SDDR_CK CK K8 M9 VDD2

VDD1 R1 K8 CK /SDDR_CK 22 R307 /ADDR2_MCLK A14 V24 /BDDR2_MCLK R331 22 CKE K2 R1 VDD1

/A_DDR2_MCLK /B_DDR2_MCLK

K2 CKE SDDR_CKE 56 R308 ADDR2_CKE D23 AB23 BDDR2_CKE R332 56 TDDR_CKE

A_DDR2_CKE B_DDR2_CKE READY

READY +1.8V_S_DDR +1.8V_S_DDR TDDR_ODT

R346 4.7K R348 4.7K ODT K9

READY

VDDQ10 A9 K9 ODT READY SDDR_ODT 56 R309 ADDR2_ODT D14 U26 BDDR2_ODT R333 56 R349 4.7K CS L8 A9 VDDQ10

R347 4.7K A_DDR2_ODT B_DDR2_ODT

VDDQ9 C1 L8 CS RAS K7 C1 VDDQ9

VDDQ8 RAS D13 U25 /BDDR2_RAS /TDDR_RAS CAS VDDQ8

C3 QIMONDA 1G K7 /SDDR_RAS 56 R310 /ADDR2_RAS R334 56 L7 QIMONDA 512M C3

/A_DDR2_RAS /B_DDR2_RAS /TDDR_CAS

VDDQ7 C7 L7 CAS /SDDR_CAS 56 R311 /ADDR2_CAS D12 U24 /BDDR2_CAS R335 56 WE K3 C7 VDDQ7

/A_DDR2_CAS /B_DDR2_CAS /TDDR_WE

VDDQ6 C9 K3 WE /SDDR_WE 56 R312 /ADDR2_WE D22 AB24 /BDDR2_WE R336 56 C9 VDDQ6

/A_DDR2_WE /B_DDR2_WE

VDDQ5 E9 E9 VDDQ5

TDDR_DQS0_P LDQS F7

VDDQ4 G1 G1 VDDQ4

F7 LDQS SDDR_DQS0_P 56 R313 ADDR2_DQS0_P B18 AB26 BDDR2_DQS0_P R337 56 UDQS B7

VDDQ3 G3 A_DDR2_DQS0 B_DDR2_DQS0 G3 VDDQ3

B7 UDQS SDDR_DQS1_P 56 R314 ADDR2_DQS1_P C17 AA26 BDDR2_DQS1_P R338 56 TDDR_DQS1_P

VDDQ2 G7 A_DDR2_DQS1 B_DDR2_DQS1 G7 VDDQ2

VDDQ1 G9 TDDR_DQM0_P LDM F3 G9 VDDQ1

F3 LDM SDDR_DQM0_P 56 R315 ADDR2_DQM0_P C18 AC25 BDDR2_DQM0_P R339 56 UDM B3

A_DDR2_DQM0 B_DDR2_DQM0

B3 UDM SDDR_DQM1_P 56 R316 ADDR2_DQM1_P A19 AC26 BDDR2_DQM1_P R340 56 TDDR_DQM1_P

A_DDR2_DQM1 B_DDR2_DQM1

VSS5 A3 TDDR_DQS0_N LDQS E8 A3 VSS5

VSS4 E3 E8 LDQS SDDR_DQS0_N 56 R317 ADDR2_DQS0_N A18 AB25 BDDR2_DQS0_N R341 56 UDQS A8 E3 VSS4

A_DDR2_DQSB0 B_DDR2_DQSB0

VSS3 J3 A8 UDQS SDDR_DQS1_N 56 R318 ADDR2_DQS1_N B17 AA25 BDDR2_DQS1_N R342 56 TDDR_DQS1_N J3 VSS3

A_DDR2_DQSB1 B_DDR2_DQSB1

VSS2 N1 N1 VSS2

AR306 AR310 NC4 L1

VSS1 P9 SDDR_D[11] ADDR2_D[11] ADDR2_D[0] B15 W25 BDDR2_D[0] BDDR2_D[11] TDDR_D[11] P9 VSS1

R3 NC4 A_DDR2_DQ0 B_DDR2_DQ0 NC5 R3

SDDR_D[12] ADDR2_D[12] ADDR2_D[1] A21 AE26 BDDR2_D[1] BDDR2_D[12] TDDR_D[12]

R7 NC5 A_DDR2_DQ1 B_DDR2_DQ1 NC6 R7

SDDR_D[9] ADDR2_D[9] ADDR2_D[2] A15 W24 BDDR2_D[2] BDDR2_D[9] TDDR_D[9]

IC300-*1 A_DDR2_DQ2 B_DDR2_DQ2 IC301-*1

HY5PS1G1631CFP-S6

VREF J2 G8

G2

DQ0

DQ1

SDDR_D[14] 56 ADDR2_D[14] ADDR2_D[3] B21 AF24 BDDR2_D[3] BDDR2_D[14] TDDR_D[14] VREF

H5PS5162FFR-S6C

J2 G8

G2

DQ0

DQ1

VSSQ10 VSSQ10

H7 DQ2 H7 DQ2

A_DDR2_DQ3 B_DDR2_DQ3

A0 M8 A0 M8

H3 DQ3 H3 DQ3

A1 M3 A1 M3

DQ4 DQ4

B2 AR311 B2

A2 H1 A2 H1

M7 DQ5 M7 DQ5

H9 H9

AR307 56

A3 N2 A3 N2

F1 DQ6 F1 DQ6

A4 A4

NC1 C21 AF25 NC1

N8 DQ7 N8 DQ7

A5 F9 A5 F9

N3 N3

ADDR2_D[4] BDDR2_D[4]

C8 DQ8 C8 DQ8

A6 N7 A6 N7

DQ9 DQ9

A2 A2

A7 C2 A7 C2

P2 DQ10 P2 DQ10

D7 D7

SDDR_D[4] ADDR2_D[4] BDDR2_D[4] TDDR_D[4]

A8 P8 A8 P8

D3 DQ11 D3 DQ11

A9 A9

VSSQ9 VSSQ9

P3 DQ12 P3 DQ12

D1 D1

A_DDR2_DQ4 B_DDR2_DQ4

A10/AP M2 A10/AP M2

D9 DQ13 D9 DQ13

A11 P7 A11 P7

DQ14 DQ14

B8 B8

A12 B1 A12 B1

R2 DQ15 R2 DQ15

B9 B9

NC2 C14 V26 NC2

BA0 L2 BA0 L2

ADDR2_D[5] BDDR2_D[5]

BA1 L3 BA1 L3

A1 VDD5 A1 VDD5

BA2

E2 E2

BDDR2_D[0-15]

L1 VDD4 VDD4

E1 E1

SDDR_D[3] ADDR2_D[3] BDDR2_D[3] TDDR_D[3]

J9 VDD3 CK J8 J9 VDD3

CK VDD2 CK VDD2

VSSQ8 VSSQ8

J8 M9 K8 M9

A_DDR2_DQ5 B_DDR2_DQ5

CK K8 R1 VDD1 CKE K2 R1 VDD1

CKE K2

A7 A7 ODT K9

ADDR2_D[0-15]

ODT K9 A9 VDDQ10 CS L8 A9 VDDQ10

CS

RAS

CAS

WE

L8

K7

L7

K3

HYNIX 1G

C1

C3

C7

C9

VDDQ9

VDDQ8

VDDQ7

VDDQ6

R8 NC3 ADDR2_D[6] C20 AE25 BDDR2_D[6] NC3 R8

RAS

CAS

WE

K7

L7

K3

HYNIX 512M

C1

C3

C7

C9

VDDQ9

VDDQ8

VDDQ7

VDDQ6

LDQS

UDQS

F7

B7

E9

G1

G3

VDDQ5

VDDQ4

VDDQ3

VDDQ2

VSSQ7 SDDR_D[1] ADDR2_D[1] A_DDR2_DQ6 B_DDR2_DQ6 BDDR2_D[1] TDDR_D[1] VSSQ7

LDQS

UDQS

F7

B7

E9

G1

G3

VDDQ5

VDDQ4

VDDQ3

VDDQ2

D2 D2

G7 G7

G9 VDDQ1 LDM F3 G9 VDDQ1

LDM F3 UDM B3

C15 W26

UDM B3

LDQS

UDQS

E8

A8

A3

E3

J3

VSS5

VSS4

VSS3

VSS2

SDDR_D[6] 56 ADDR2_D[6] ADDR2_D[7] BDDR2_D[7] BDDR2_D[6] 56 TDDR_D[6]

LDQS

UDQS

E8

A8

A3

E3

J3

VSS5

VSS4

VSS3

VSS2

VSSQ6 VSSQ6

N1 NC4 N1

L1

A_DDR2_DQ7 B_DDR2_DQ7

P9 VSS1 P9 VSS1

NC5 R3 NC5 R3

NC6 NC6

D8 D8

R7 R7

B2 VSSQ10 B2 VSSQ10

NC1 NC1

C16 Y26

A2 VSSQ9 A2 VSSQ9

NC2 B8 NC2 B8

E2 E2

AR308 ADDR2_D[8] BDDR2_D[8] AR312

A7 VSSQ8 A7 VSSQ8

NC3 R8 NC3 R8

D2 VSSQ7 D2 VSSQ7

D8 VSSQ6 D8 VSSQ6

VSSDL E7 VSSQ5 VSSDL E7 VSSQ5

J7 J7

VDDL J1

F2

F8

H2

H8

VSSQ4

VSSQ3

VSSQ2

VSSQ1 VSSQ5 E7 VSSDL SDDR_D[15] ADDR2_D[15] A_DDR2_DQ8 B_DDR2_DQ8 BDDR2_D[15] TDDR_D[15] VSSDL E7 VSSQ5 VDDL J1

F2

F8

H2

H8

VSSQ4

VSSQ3

VSSQ2

VSSQ1

J7 ADDR2_D[9] C19 AD25 BDDR2_D[9] J7

VSSQ4 F2 SDDR_D[8] ADDR2_D[8] A_DDR2_DQ9 B_DDR2_DQ9 BDDR2_D[8] TDDR_D[8] +1.8V_S_DDR F2 VSSQ4

IC300-*2

+1.8V_S_DDR ADDR2_D[10] B16 Y25 BDDR2_D[10] IC301-*2

EDE1116AEBG-8E-F

VREF J2 G8

G2

DQ0

DQ1

VSSQ3 F8 SDDR_D[10] ADDR2_D[10] A_DDR2_DQ10 B_DDR2_DQ10 BDDR2_D[10] TDDR_D[10] F8 VSSQ3 EDE5116AJBG-8E-E

VREF J2 G8

G2

DQ0

DQ1

ADDR2_D[11] B20 AE24 BDDR2_D[11]

H7 DQ2 H7 DQ2

A0 M8 A0 M8

H3 DQ3 H3 DQ3

A1 M3 A1 M3

H1 DQ4 H1 DQ4

A2 M7 A2 M7

H9 DQ5 H9 DQ5

A3 N2 A3 N2

F1 DQ6 F1 DQ6

A4 A4

VSSQ2 56 VSSQ2

N8 DQ7 N8 DQ7

F9 F9

A_DDR2_DQ11 B_DDR2_DQ11

A5 N3 A5 N3

SDDR_D[13] ADDR2_D[13] BDDR2_D[13] TDDR_D[13]

C8 DQ8 C8 DQ8

A6 N7 A6 N7

DQ9 DQ9

H2 H2

A7 C2 A7 C2

P2 DQ10 P2 DQ10

A8 D7 A8 D7

P8 DQ11 P8 DQ11

A9 D3 A9 D3

ADDR2_D[12] A20 AD26 BDDR2_D[12]

P3 DQ12 P3 DQ12

A10 D1 A10 D1

M2 DQ13 M2 DQ13

A11 D9 A11 D9

P7 DQ14 P7 DQ14

AR309 AR313

A12 B1 A12 B1

R2 DQ15 R2 DQ15

B9 B9

BA0

BA1

BA2

L2

L3

A1 VDD_5

VSSQ1 VDDL A_DDR2_DQ12 B_DDR2_DQ12 56 VDDL VSSQ1 BA0

BA1

L2

L3

A1 VDD_5

H8 J1 J1 H8

L1 VDD_4 VDD_4

E1 E1

SDDR_D[7] ADDR2_D[7] BDDR2_D[7] TDDR_D[7]

J9 VDD_3 CK J8 J9 VDD_3

CK VDD_2 CK VDD_2

ADDR2_D[13] A16 Y24

J8 M9 K8 M9

CK K8 R1 VDD_1 CKE K2 R1 VDD_1

CKE

ODT

CS

K2

K9

L8

A9

C1

VDDQ_10

VDDQ_9

BDDR2_D[13] ODT

CS

RAS

K9

L8

K7

A9

C1

VDDQ_10

VDDQ_9

RAS

CAS

WE

K7

L7

K3

ELPIDA 1G C3

C7

C9

E9

VDDQ_8

VDDQ_7

VDDQ_6

VDDQ_5

SDDR_D[0] ADDR2_D[0] A_DDR2_DQ13 B_DDR2_DQ13 BDDR2_D[0] TDDR_D[0]

CAS

WE

LDQS

L7

K3

ELPIDA 512M C3

C7

C9

E9

VDDQ_8

VDDQ_7

VDDQ_6

VDDQ_5

ADDR2_D[14] B19 AD24 BDDR2_D[14]

VDDQ_4 F7 VDDQ_4

LDQS G1 UDQS G1

F7 VDDQ_3 B7 VDDQ_3

UDQS G3 G3

B7 VDDQ_2 VDDQ_2

G7 G7

G9 VDDQ_1 LDM F3 G9 VDDQ_1

LDM F3 UDM B3

UDM B3

LDQS

UDQS

E8

A8

A3

E3

J3

VSS_5

VSS_4

VSS_3

VSS_2

SDDR_D[2] ADDR2_D[2] A_DDR2_DQ14 B_DDR2_DQ14 BDDR2_D[2] TDDR_D[2]

LDQS

UDQS

E8

A8

A3

E3

J3

VSS_5

VSS_4

VSS_3

VSS_2

ADDR2_D[15] A17 AA24 BDDR2_D[15]

N1 NC_4 N1

VSS_1 L1 VSS_1

NC_5 P9 NC_5 P9

R3 R3

NC_6 R7 NC_6 R7

B2 VSSQ_10 B2 VSSQ_10

NC_1 A2 NC_1 A2

B8 VSSQ_9 B8 VSSQ_9

A_DDR2_DQ15 B_DDR2_DQ15

NC_2 E2 NC_2 E2

A7 VSSQ_8 A7 VSSQ_8

NC_3 R8 NC_3 R8

D2 VSSQ_7 D2 VSSQ_7

D8 VSSQ_6 D8 VSSQ_6

VSSDL

VDDL

J7

J1

E7

F2

F8

H2

H8

VSSQ_5

VSSQ_4

VSSQ_3

VSSQ_2

VSSQ_1

SDDR_D[5] ADDR2_D[5] BDDR2_D[5] 56 TDDR_D[5] VSSDL

VDDL

J7

J1

E7

F2

F8

H2

H8

VSSQ_5

VSSQ_4

VSSQ_3

VSSQ_2

VSSQ_1

56

IC300-*3 IC301-*3

K4T1G164QE-HCE7 K4T51163QG-HCE7

VREF J2 G8 DQ0 VREF J2 G8 DQ0

G2 DQ1 G2 DQ1

H7 DQ2 H7 DQ2

A0 M8 A0 M8

H3 DQ3 H3 DQ3

A1 M3 A1 M3

H1 DQ4 H1 DQ4

A2 M7 A2 M7

H9 DQ5 H9 DQ5

A3 N2 A3 N2

F1 DQ6 F1 DQ6

A4 N8 A4 N8

F9 DQ7 F9 DQ7

A5 N3 A5 N3

C8 DQ8 C8 DQ8

A6 N7 A6 N7

C2 DQ9 C2 DQ9

A7 P2 A7 P2

D7 DQ10 D7 DQ10

A8 P8 A8 P8

D3 DQ11 D3 DQ11

A9 P3 A9 P3

D1 DQ12 D1 DQ12

A10/AP M2 A10/AP M2

D9 DQ13 D9 DQ13

A11 P7 A11 P7

B1 DQ14 B1 DQ14

A12 R2 A12 R2

B9 DQ15 B9 DQ15

BA0 L2 BA0 L2

BA1 L3 BA1 L3

A1 VDD_5 A1 VDD_5

BA2 L1

E1 VDD_4 E1 VDD_4

J9 VDD_3 CK J8 J9 VDD_3

CK J8 M9 VDD_2 CK K8 M9 VDD_2

CK K8 R1 VDD_1 CKE K2 R1 VDD_1

CKE K2

ODT K9

ODT K9 A9 VDDQ_10 CS L8 A9 VDDQ_10

CS L8 C1 VDDQ_9 RAS K7 C1 VDDQ_9

RAS K7 SS 1G C3 VDDQ_8 CAS L7 SS 512M C3 VDDQ_8

CAS L7 C7 VDDQ_7 WE K3 C7 VDDQ_7

WE K3 C9 VDDQ_6 C9 VDDQ_6

E9 VDDQ_5 E9 VDDQ_5

LDQS F7

G1 VDDQ_4 G1 VDDQ_4

LDQS F7 UDQS B7

G3 VDDQ_3 G3 VDDQ_3

UDQS B7

G7 VDDQ_2 G7 VDDQ_2

G9 VDDQ_1 LDM F3 G9 VDDQ_1

LDM F3 UDM B3

UDM B3

A3 VSS_5 LDQS E8 A3 VSS_5

LDQS E8 E3 VSS_4 UDQS A8 E3 VSS_4

UDQS A8 J3 VSS_3 J3 VSS_3

N1 VSS_2 N1 VSS_2

NC_4 L1

P9 VSS_1 P9 VSS_1

NC_5 R3 NC_5 R3

NC_6 R7 NC_6 R7

B2 VSSQ_10 B2 VSSQ_10

NC_1 A2 NC_1 A2

B8 VSSQ_9 B8 VSSQ_9

NC_2 E2 NC_2 E2

A7 VSSQ_8 A7 VSSQ_8

NC_3 R8 NC_3 R8

D2 VSSQ_7 D2 VSSQ_7

D8 VSSQ_6 D8 VSSQ_6

VSSDL E7 VSSQ_5 VSSDL E7 VSSQ_5

J7 J7

F2 VSSQ_4 F2 VSSQ_4

F8 VSSQ_3 F8 VSSQ_3

H2 VSSQ_2 H2 VSSQ_2

VDDL J1 H8 VSSQ_1 VDDL J1 H8 VSSQ_1

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS MSD3368EV Platform

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC. DDR2 3 10

DDR2

Copyright © 2010 LG Electronics Inc. All rights reserved.

Downloaded from

Only for training and www.Manualslib.com

service purposes manuals search engine LGE Internal Use Only

5V_HDMI1

SHIELD R612

0

HPD1

20

1K R615

READY

19 C600 5V_HDMI1 +5V_ST

0.1uF

18 16V

R600

1K

17

A2

A1

16 DDC_SDA_1

IC600 ENKMC2838-T112

15 DDC_SCL_1 AT24C02BN-10SU-1.8 D600

C

14

5V_HDMI1 5V_HDMI2 5V_HDMI3

CEC_REMOTE A0 VCC

13 1 8

CK-_HDMI1 C603

R664

R660

R662

12 0.1uF

10K

10K

10K

EAG59023302

A1 WP R626 R629

2 7

11 18K 18K 5V_HDMI_1 5V_HDMI_2 5V_HDMI_3

CK+

10 CK+_HDMI1

A2 SCL

R665

R661

R663

D0- 3 6

33K

33K

33K

9 D0-_HDMI1 R623 22 DDC_SCL_1

D0_GND

8 GND SDA

4 5

D0+

7 R621 22

D0+_HDMI1 DDC_SDA_1

D1-

6 D1-_HDMI1

D1_GND

5

D1+

4 D1+_HDMI1

D2-

3 D2-_HDMI1

D2_GND

2

D2+

1 D2+_HDMI1

JK600

GND UI_HW_PORT1

5V_HDMI2

SHIELD R613

0

HPD2

20 5V_HDMI2 +5V_ST

1K R616

READY

19 C601

0.1uF

18 IC602

16V

A2

A1

AT24C02BN-10SU-1.8

R601

1K

17 ENKMC2838-T112

D602

16 DDC_SDA_2

C

A0 VCC

1 8

15 DDC_SCL_2

C607

14 A1 WP 0.1uF R649

2 7 R646

CEC_REMOTE 18K 18K

13

CK-_HDMI2 A2 SCL

12 3 6 DDC_SCL_2

R645 22

EAG59023301

11

CK+ GND SDA

10 CK+_HDMI2 4 5 DDC_SDA_2

D0- R642 22

9 D0-_HDMI2

D0_GND

8

GND

D0+

7 D0+_HDMI2

D1-

6 D1-_HDMI2 +3.3V_HDMI_ST

D1_GND

5

D1+

4 D1+_HDMI2

D2- R632 R637

3 D2-_HDMI2

READY

330K 27K

D2_GND

MMBD301LT1G

2

D2+

1 D2+_HDMI2 R624

0 D605

READY 30V

R659

0

CEC_REMOTE HDMI_CEC

S B D

D604

UI_HW_PORT2 READY

BSS83

JK601

GND

Q600

READY G

SIDE HDMI

5V_HDMI3

5V_HDMI3 +5V_ST

JACK_GND R636

0

HPD3

1K R638

A2

A1

20

READY

ENKMC2838-T112

19 C605 D603

C

0.1uF

18 16V IC603

R631

AT24C02BN-10SU-1.8

1K

17

16 DDC_SDA_3

A0 VCC

1 8

15 DDC_SCL_3

C608

A1 WP 0.1uF R648

14 18K R650

2 7

CEC_REMOTE 18K

13

CK-_HDMI3 A2 SCL

12 3 6 DDC_SCL_3

R643 22

EAG42463001

11

CK+ GND SDA

10 CK+_HDMI3 4 5 DDC_SDA_3

D0- R644 22

9

D0-_HDMI3

D0_GND

8

GND

D0+

7

D0+_HDMI3

D1-

6

D1-_HDMI3

D1_GND

5

D1+

4

D1+_HDMI3

D2-

3

D2-_HDMI3

D2_GND

2

D2+

1

D2+_HDMI3

UI_HW_PORT4

GND

JK603

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS MSD3368EV Platform

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC. HDMI 5 10

HDMI

Copyright © 2010 LG Electronics Inc. All rights reserved.

Downloaded from

Only for training and www.Manualslib.com

service purposes manuals search engine LGE Internal Use Only

AVSS

Audio Amp

This parts are Located

R717

on AVSS area. +3.3V

R715

0

470

2200pF

4700pF

C733

L702

1uF

16V

22K

AVSS 0.033uF +3.3V_AVDD_AMP

0.047uF

P_17V

120-ohm

C720

C702 4700pF 50V

AVSS

C713

C703

C730

R707

C736 R718

L701

0.047uF 470 +3.3V_DVDD

Separate DGND AND AVSS 120-ohm

C714 C735

C721 C775 C741 C742 C743 C744

GVDD_OUT_1

100uF 100uF 100uF 100uF 100uF 100uF

PLL_FLTP

PLL_FLTM

PVDD_A_2

PVDD_A_1

0.1uF 0.1uF 25V 25V 25V 25V 25V 25V

SSTIMER

READY READY

VR_ANA

OC_ADJ

BST_A

OUT_A

AVSS

9 NC

8

7

6

3

2

1

+3.3V_AVDD_AMP SPK_L+

12

11

10

AVDD 48 PGND_AB_2 P_17V C725

13 L705 0.01uF

C704

C723 C728 TESTOUT 47 PGND_AB_1 2S AD-9060 2F 0.1uF

10uF 16V 0.1uF 14 R704

C740 3.3

MCLK 15

46 OUT_B 1S 1F 0.68uF

AUDIO_MASTER_CLK AVSS

R705

R713 EAP61008401 3.3

R702 200 OSC_RES 45 PVDD_B_2 C726

22 16 50V 0.1uF C727

18K C732 0.033uF 0.01uF

1% R714 DVSS_1 44 PVDD_B_1 0.01uF

17 C701 @netLa

SPK_L-

VR_DIG 43 BST_B

+3.3V R712 PDN

18

TAS5709PHPR 42 BST_C

WAFER-ANGLE

AC_DET 19

1K C712 C718

C722

4.7uF

LRCLK 20

IC701 41 PVDD_C_2 SPK_L+

4

1000pF 0.1uF 10V

R725

10K R710 50V SCLK 40 PVDD_C_1

50V

0.033uF C734 SPK_R+

21 C729 0.01uF SPK_L-

C 0 L704 C717 3

R716 B

SDIN 22

39 OUT_C 2S AD-9060 2F 0.1uF

Q701 R711 R709

AMP_MUTE READY 33K R706 SPK_R+

10K 2SC3052

22 SDA 38 PGND_CD_2 C739 3.3 2

E MS_LRCK 23 1S 1F 0.68uF

R703 R719

22 SCL 37 PGND_CD_1 3.3 SPK_R-

24 EAP61008401 1

MS_SCK R708

C710

0.1uF

C715

22 0.01uF P700

MS_LRCH

25

26

27

28

29

30

31

32

33

34

35

36

@netLa

SPK_R-

SDA1

PVDD_D_1

PVDD_D_2

AGND

VREG

RESET

STEST

GVDD_OUT_2

BST_D

OUT_D

GND

DVSS_2

DVDD

SCL1

P_17V

C709

1000pF

C719 C706

C708

0.1uF 0.1uF

1uF

16V

+3.3V_DVDD C738 0.033uF

50V

AMP_RST C737

0.1uF

C711 C707

10uF 16V 0.1uF

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS MSD3368EV Platform

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC. AUDIO 6 10

AUDIO

Copyright © 2010 LG Electronics Inc. All rights reserved.

Downloaded from www.Manualslib.com manuals search engine

Only for training and service purposes LGE Internal Use Only

POWER B/D P800

SMAW200-H18S1

L801 P_17V

MLB-201209-0120P-N2 +5V

1 2

P_+5V +5V

C818 C817 +5V_ST +5V_ST P_+5V

3 4 0.1uF

50V

100uF

25V L817

C854

5 6

L800 C890 0.1uF

C820 C862 C865 C857

7 8 C813

MLB-201209-0120P-N2

10uF

C804

470uF 0.1uF

10uF

6.3V Q806 10uF 0.1uF 220uF

16V 16V READY SI4925BDY 16V 16V 16V

R856 R834

9 10 PSU_ERR_DET

10K

READY

10K L808

+5V_GENERAL

S1 1 8 D1_2

11 12 C809

16V +5V_ST C864 C866

+5V_ST R804 0.1uF G1 2 7 D1_1 10uF C858

READY 0.1uF 220uF

R837

13 14 0

C839

16V 16V 16V

2K R801 C837 C835 C834 R835 S2 3 6 D2_2

100uF 10uF

10uF 0.1uF

RL_ON/PWR_ONOFF

100

15 16 16V 16V 6.3V

Q803

560

C805 READY G2 4 5 D2_1

AC_DET 2SC3052 C

+5V_ST

0.1uF

16V

17 18 C812

RL_ON/PWR_ONOFF

B

16V R829

0.1uF

READY

10K

R828 E

R838 R803 120K

10K 100 READY

MODULE_ON 19

C807

0.1uF

16V

+3.3V_TU

L806

MLB-201209-0120P-N2

C826 C885 C828

Stand-by +3.3V +5V

0.1uF

16V

0.1uF

16V

68uF

10V

GND

IC804

AZ1085S-3.3TR/E1

+3.3V_CI

+3.3V_ST MAX 3A

L814 40 mA

+3.3V_AVDD_MPLL INPUT OUTPUT MLB-201209-0120P-N2

+5V_ST +3.3V_ST 3 2

$0.122

1

IC802 R858 ADJ/GND

0 C852

R866

AP2121N-3.3TRE1 0.1uF

16V

0

C815

VIN VOUT 0.1uF

3 2

16V C829 C831

1

10uF 0.1uF

C806 +3.3V_HDMI_ST

16V GND

+3.3V

C802 C803 GND C892 C808

10uF 0.1uF 10uF 10uF 0.1uF

16V 16V 16V 6.3V 16V 650 mA

R859

READY 0

0

C816 R862

0.1uF C850 C897 C844 C891

16V 10uF 220uF 0.1uF 10uF

6.3V 6.3V 6.3V

READY

GND GND

+3.3V_AVDD

320 mA

S6 core 1.26 volt

+5V +3.3V_AVDD

+3.3V_AVDD

50 mA +5V_GENERAL

IC803

AP1117E18G-13 +1.8V_TU 465 mA @85% efficiency

R865

L805

IN 3 1 ADJ/GND

0

IC801 2

AP1117E33G-13 C814 OUT C822 C889 C827 C824 C825

0.1uF 10uF 10uF 0.1uF 0.1uF 100uF P_+5V

16V 6.3V 6.3V 16V 16V 16V

IN ADJ/GND READY READY

3 1

10uF

2

L802 Replaced Part

R831 MAX 3A

READY

OUT C888 C811

C800 C801 0.1uF READY 10K +1.26V_VDDC

C842 10uF MLB-201209-0120P-N2

C810

10uF 0.1uF 6.3V 16V C841 R827

100uF 6.3V

16V 16V 100uF

16V 10K C899 READY

R2 = R1/(Vout/0.8-1) 0.1uF

16V

IC805

READY R824 MP2212DN

50V 360K R1 TP1451

100pF

450 mA C870

+3.3V

+1.8V_DDR +1.8V_DDR

1% FB

1 8

EN/SYNC 1600 mA

R825 L813

IC800 620K R2 R802

GND SW_2 3.6uH

AZ1085S-ADJTR/E1 0

2 7

R864

1%

NR8040T3R6N 1/4W

0

INPUT OUTPUT C OUT

3 2 IN SW_1

Placed on SMD-TOP 3 6 C843 C894 C856 C896

1 10uF 10uF 0.1uF 10uF

C893 C880 C877 6.3V 6.3V 6.3V

C878 ADJ/GND BS VCC

C883 10uF 10uF 0.1uF C830 READY

10uF 4 5

0.1uF 6.3V 6.3V 16V C838

6.3V R861 C898 0.01uF

16V READY 10uF

75 10uF 50V

16V 16V

1%

R860

33

1%

R830

10

C836

1% 1uF

10V

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS MSD3368EV Platform

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC. POWER 7 10

POWER

Copyright © 2010 LG Electronics Inc. All rights reserved.

Downloaded from www.Manualslib.com manuals search engine

Only for training and service purposes LGE Internal Use Only

JK900 REAR CVBS SIDE CVBS

PPJ237-01

6C [RD1]E-LUG 5A [YL]E-LUG R938

0

SIDE_CVBS_IN

4A [YL]O-SPRING +3.3V_AVDD

C916

5C [RD1]O-SPRING R908 10K D931 R937 47pF

AV_RIN 3A 30V 50V

[YL]CONTACT 75

C900

R915

R963

D901 R900 100pF

4C [RD1]CONTACT 5.6V 470K 50V 12K 4B [WH]O-SPRING

10K

R973

+3.3V_AVDD 3C 1K

[RD]CONTACT SIDE_CVBS_DET

[WH1]O-SPRING C911

D919

5B

30V

R909 10K

R940

AV_LIN 4C 0.1uF

[RD]O-SPRING

10K

C901 16V

D902 R901 100pF R916

4A [YL1]CONTACT 5.6V 470K 50V 12K AV_DET 5C [RD]E-LUG

C909 PPJ235-01

D915 0.1uF R933

30V 16V JK902 10K

[YL1]O-SPRING R917

5A 0 SIDE_LIN

C906 AV_CVBS_IN C913

D922

100pF

470K

D900 47pF

R923

R910

12K

30V R932

[YL1]E-LUG 75 50V

6A

R930

10K

[RD2]E-LUG SIDE_RIN

6H C912

D921

470K

R922

100pF

12K

R931

5H [RD2]O-SPRING_2 R913

COMP1_RIN

COMP1

C904 10K R925

R904 1000pF

[RD2]CONTACT D909 470K 12K

4H 50V

[WH2]O-SPRING R914

5G COMP1_LIN

C905 10K R926

D911 R905 1000pF

5F [RD2]O-SPRING_1 470K 50V 12K SWITCH ADDED

+3.3V_CI P_+5V

COMP1_Pr

IC900

AP2191SG-13

USB

READY

L901

[RD2]E-LUG-S IC902

R991

R927

7F NC GND NL17SZ08DFT2G

10K

1%

8 1

D912

75

OUT_2 IN_1

USB_CTL

0.1uF

7 2 5 1

C927

5E [BL2]O-SPRING C934

OUT_1

6 3

IN_2

READY 2 AC_DET

COMP1_Pb 470uF FLG EN

READY

R928

5 4 4 3

16V

D913

R999

R992

1%

75

10K

10K

7E [BL2]E-LUG-S R944 0

100

KJA-UB-4-0004

JK905

USB_OCD

1

USB DOWN STREAM

4D [GN2]CONTACT R970

R939

2

+3.3V_AVDD 0 USB_DM

COMP1_Y

READY

[GN2]O-SPRING

D914

R929

5D

1%

R907

75

USB_DP

10K

D932 D933

R936 CDS3C05HDMI1 CDS3C05HDMI1

6D [GN2]E-LUG 1K 5.6V 5.6V

4

COMP1_DET

READY

D910

30V

6N [RD3]E-LUG

5N [RD3]O-SPRING_2 R911

R902 C902

1000pF

10K R918

COMP2_RIN

COMP2

[RD3]CONTACT D903 470K 12K

4N 50V

5M [WH3]O-SPRING R912

COMP2_LIN

C903 10K R919

D905 R903

5L [RD3]O-SPRING_1 1000pF

470K 50V 12K

[RD3]E-LUG-S +5V_GENERAL +5V_GENERAL

7L

COMP2_Pr OPTIC

READY

R920

1%

D906 IC901

75

NL17SZ00DFT2G

5K [BL3]O-SPRING

A VCC

R964

SPDIF_OUT 1 5 1K

B

2

READY JK904

READY

COMP2_Pb R998

[BL3]E-LUG-S

READY

R921

7K 100 JST1223-001

D907

GND Y

3 4

1%

READY

75

R997 GND

1

Fiber Optic

0

4J [GN3]CONTACT R935

0

COMP2_Y

READY

VCC

+3.3V_AVDD

D908

D934

R924

READY

1%

75

5J [GN3]O-SPRING C926

0.1uF

R906

VINPUT

50V

3

10K

[GN3]E-LUG R934

6J 1K FIX_POLE

COMP2_DET

READY

D904

30V

GND

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS MSD3368EV Platform

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC. JACK 8 10

Copyright © 2010 LG Electronics Inc. All rights reserved.

Downloaded from

Only for training and www.Manualslib.com

service purposes manuals search engine LGE Internal Use Only

D1007

D1002

D1003

D1004

D1008

+5V_VGA

JK1001 +5V_VGA +5V_ST

SPG09-DB-010

C1001 R1018

0.1uF 22

A1

A2

DSUB_R ENKMC2838-T112

16V

IC1001 D1012

RED_GND C1015

6 AT24C02BN-10SU-1.8

C

GND_2 4.7pF

1 11 RED

GREEN_GND

7 DDC_SDA/UART_TX C1022

DDC_DATA R1017 1 8 R1024 R1029 0.1uF

2 12 GREEN 22 4.7K 4.7K

DSUB_G R1023

BLUE_GND 2 7

8 +3.3V_AVDD

H_SYNC 100 R1032

R1016

3 13 BLUE

C1014 0

3 6

4.7pF DDC_SCL/UART_RX

10K

NC R1033

9 0

V_SYNC 4 5 DDC_SDA/UART_TX

4 14 GND_1 R1019

1K C1018 C1021

SYNC_GND 18pF 18pF

10 DSUB_DET 50V 50V ISP_RXD

DDC_CLOCK

5 15

READY

D1009

DDC_GND C1013 ISP_TXD

30V

0.1uF

16V

16

SHILED

R1015

22

DSUB_B PC AUDIO

C1012 JK1000

4.7pF PEJ027-01

DSUB_HSYNC

C1017

R1014

12pF

3 E_SPRING

1K

6A T_TERMINAL1

DSUB_VSYNC 7A B_TERMINAL1

C1016

R1013 PC_RIN

12pF

1K D1010 R1028

4 R_SPRING C1020 10K

5.6V 100pF

50V R1022 R1027

T_SPRING 470K 12K

5

DDC_SCL/UART_RX

7B B_TERMINAL2

PC_LIN

R1005 R1007 R1010 R1011 R1012 C1019 R1026

GND 75 75 75 4.7K 4.7K

LVDS FFC WAFER LVDS 6B T_TERMINAL2 D1011

5.6V

100pF

50V

10K

R1021

470K

R1025

12K

P401

SMAW200-H26S1

ROM DOWNLOAD FOR PDP 52

51

PC_SER_CLK

50

PC_SER_DATA

49 1 2

PDP_SCL

48