Professional Documents

Culture Documents

Hef4071b PDF

Hef4071b PDF

Uploaded by

Leonardo NascimentoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Hef4071b PDF

Hef4071b PDF

Uploaded by

Leonardo NascimentoCopyright:

Available Formats

HEF4071B

Quad 2-input OR gate

Rev. 7 — 15 November 2011 Product data sheet

1. General description

The HEF4071B is a quad 2-input OR gate. The outputs are fully buffered for highest noise

immunity and pattern insensitivity to output impedance variations.

It operates over a recommended VDD power supply range of 3 V to 15 V referenced to VSS

(usually ground). Unused inputs must be connected to VDD, VSS, or another input.

2. Features and benefits

Fully static operation

5 V, 10 V, and 15 V parametric ratings

Standardized symmetrical output characteristics

Inputs and outputs are protected against electrostatic effects

Specified from 40 C to +85 C and 40 C to +125 C

Complies with JEDEC standard JESD 13-B

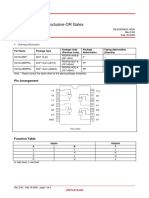

3. Ordering information

Table 1. Ordering information

All types operate from 40 C to +125 C.

Type number Package

Name Description Version

HEF4071BP DIP14 plastic dual in-line package; 14 leads (300 mil) SOT27-1

HEF4071BT SO14 plastic small outline package; 14 leads; body width 3.9 mm SOT108-1

4. Functional diagram

1 1A

1Y 3

2 1B

5 2A

2Y 4

6 2B

8 3A

3Y 10

9 3B

12 4A

4Y 11

13 4B nA

nY

nB

001aaj110 001aaj108

Fig 1. Functional diagram Fig 2. Logic diagram (one gate)

NXP Semiconductors HEF4071B

Quad 2-input OR gate

5. Pinning information

5.1 Pinning

HEF4071B

1A 1 14 VDD

1B 2 13 4B

1Y 3 12 4A

2Y 4 11 4Y

2A 5 10 3Y

2B 6 9 3B

VSS 7 8 3A

001aaj107

Fig 3. Pin configuration

5.2 Pin description

Table 2. Pin description

Symbol Pin Description

1A to 4A 1, 5, 8, 12 input

1B to 4B 2, 6, 9, 13 input

1Y to 4Y 3, 4, 10, 11 output

VSS 7 ground (0 V)

VDD 14 supply voltage

6. Functional description

Table 3. Function table[1]

Input Output

nA nB nY

L L L

L H H

H L H

H H H

[1] H = HIGH voltage level; L = LOW voltage level.

HEF4071B All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 7 — 15 November 2011 2 of 12

NXP Semiconductors HEF4071B

Quad 2-input OR gate

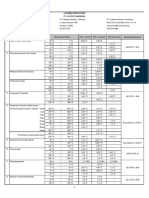

7. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to VSS = 0 V (ground).

Symbol Parameter Conditions Min Max Unit

VDD supply voltage 0.5 +18 V

IIK input clamping current VI < 0.5 V or VI > VDD + 0.5 V - 10 mA

VI input voltage 0.5 VDD + 0.5 V

IOK output clamping current VO < 0.5 V or VO > VDD + 0.5 V - 10 mA

II/O input/output current - 10 mA

IDD supply current - 50 mA

Tstg storage temperature 65 +150 C

Tamb ambient temperature 40 +125 C

Ptot total power dissipation Tamb = 40 C to + 125 C

DIP14 [1] - 750 mW

SO14 [2] - 500 mW

P power dissipation per output - 100 mW

[1] For DIP14 packages: above Tamb = 70 C, Ptot derates linearly with 12 mW/K.

[2] For SO14 packages: above Tamb = 70 C, Ptot derates linearly with 8 mW/K.

8. Recommended operating conditions

Table 5. Recommended operating conditions

Symbol Parameter Conditions Min Max Unit

VDD supply voltage 3 15 V

VI input voltage 0 VDD V

Tamb ambient temperature in free air 40 +125 C

t/V input transition rise and fall rate VDD = 5 V - 3.75 s/V

VDD = 10 V - 0.5 s/V

VDD = 15 V - 0.08 s/V

HEF4071B All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 7 — 15 November 2011 3 of 12

NXP Semiconductors HEF4071B

Quad 2-input OR gate

9. Static characteristics

Table 6. Static characteristics

VSS = 0 V; VI = VSS or VDD; unless otherwise specified.

Symbol Parameter Conditions VDD Tamb = 40 C Tamb = +25 C Tamb = +85 C Tamb = +125 C Unit

Min Max Min Max Min Max Min Max

VIH HIGH-level IO < 1 A 5V 3.5 - 3.5 - 3.5 - 3.5 - V

input voltage 10 V 7.0 - 7.0 - 7.0 - 7.0 - V

15 V 11.0 - 11.0 - 11.0 - 11.0 - V

VIL LOW-level IO < 1 A 5V - 1.5 - 1.5 - 1.5 - 1.5 V

input voltage 10 V - 3.0 - 3.0 - 3.0 - 3.0 V

15 V - 4.0 - 4.0 - 4.0 - 4.0 V

VOH HIGH-level IO < 1 A 5V 4.95 - 4.95 - 4.95 - 4.95 - V

output voltage 10 V 9.95 - 9.95 - 9.95 - 9.95 - V

15 V 14.95 - 14.95 - 14.95 - 14.95 - V

VOL LOW-level IO < 1 A 5V - 0.05 - 0.05 - 0.05 - 0.05 V

output voltage 10 V - 0.05 - 0.05 - 0.05 - 0.05 V

15 V - 0.05 - 0.05 - 0.05 - 0.05 V

IOH HIGH-level VO = 2.5 V 5V - 1.7 - 1.4 - 1.1 - 1.1 mA

output current VO = 4.6 V 5V - 0.64 - 0.5 - 0.36 - 0.36 mA

VO = 9.5 V 10 V - 1.6 - 1.3 - 0.9 - 0.9 mA

VO = 13.5 V 15 V - 4.2 - 3.4 - 2.4 - 2.4 mA

IOL LOW-level VO = 0.4 V 5V 0.64 - 0.5 - 0.36 - 0.36 - mA

output current VO = 0.5 V 10 V 1.6 - 1.3 - 0.9 - 0.9 - mA

VO = 1.5 R 15 V 4.2 - 3.4 - 2.4 - 2.4 - mA

II input leakage 15 V - 0.1 - 0.1 - 1.0 - 1.0 A

current

IDD supply current all valid input 5V - 0.25 - 0.25 - 7.5 - 7.5 A

combinations; 10 V - 0.5 - 0.5 - 15.0 - 15.0 A

IO = 0 A

15 V - 1.0 - 1.0 - 30.0 - 30.0 A

CI input - - - 7.5 - - - - pF

capacitance

HEF4071B All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 7 — 15 November 2011 4 of 12

NXP Semiconductors HEF4071B

Quad 2-input OR gate

10. Dynamic characteristics

Table 7. Dynamic characteristics

Tamb = 25 C; waveforms see Figure 4; test circuit see Figure 5; unless otherwise specified. [1]

Symbol Parameter Conditions VDD Extrapolation formula Min Typ Max Unit

tPHL HIGH to LOW nA or nB to nY 5V 28 ns + (0.55 ns/pF)CL - 55 115 ns

propagation delay 10 V 15 ns + (0.23 ns/pF)CL - 25 50 ns

15 V 12 ns + (0.16 ns/pF)CL - 20 35 ns

tPLH LOW to HIGH nA or nB to nY 5V 18 ns + (0.55 ns/pF)CL - 45 90 ns

propagation delay 10 V 9 ns + (0.23 ns/pF)CL - 20 45 ns

15 V 7 ns + (0.16 ns/pF)CL - 15 30 ns

tt transition time 5V [2] 10 ns + (1.00 ns/pF)CL - 60 120 ns

10 V 9 ns + (0.42 ns/pF)CL - 30 60 ns

15 V 6 ns + (0.28 ns/pF)CL - 20 40 ns

[1] The typical value of the propagation delay and output transition time can be calculated with the extrapolation formula (CL in pF).

[2] tt is the same as tTHL and tTLH.

Table 8. Dynamic power dissipation

VSS = 0 V; tr = tf 20 ns; Tamb = 25 C.

Symbol Parameter VDD Typical formula where:

PD dynamic power dissipation 5 V PD = 1150 fi + (fo CL) VDD (W) 2 fi = input frequency in MHz;

10 V PD = 4800 fi + (fo CL) VDD (W) fo = output frequency in MHz;

2

15 V PD = 19700 fi + (fo CL) VDD2 (W) CL = output load capacitance in pF;

(fo CL) = sum of the outputs;

VDD = supply voltage in V.

11. Waveforms

tr tf

VI

90 %

nA, nB input VM

10 %

0V

tPLH tPHL

VOH

90 %

nY output VM

10 %

VOL

tTLH tTHL

001aai140

Measurement points are given in Table 9.

Logic levels: VOL and VOH are typical output voltage levels that occur with the output load.

Fig 4. Input to output propagation delay and output transition times

HEF4071B All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 7 — 15 November 2011 5 of 12

NXP Semiconductors HEF4071B

Quad 2-input OR gate

Table 9. Measurement points

Supply voltage Input Output

VDD VM VM

5 V to 15 V 0.5VDD 0.5VDD

VDD

VI VO

G DUT

RT CL

001aag182

Test data is given in Table 10.

Definitions for test circuit:

DUT = Device Under Test.

CL = load capacitance including jig and probe capacitance.

RT = termination resistance should be equal to the output impedance Zo of the pulse generator.

Fig 5. Test circuit

Table 10. Test data

Supply voltage Input Load

VDD VI tr, tf CL

5 V to 15 V VSS or VDD 20 ns 50 pF

HEF4071B All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 7 — 15 November 2011 6 of 12

NXP Semiconductors HEF4071B

Quad 2-input OR gate

12. Package outline

DIP14: plastic dual in-line package; 14 leads (300 mil) SOT27-1

D ME

seating plane

A2 A

L A1

c

Z e w M

b1

(e 1)

b

14 8 MH

pin 1 index

E

1 7

0 5 10 mm

scale

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

UNIT

A A1 A2

b b1 c D (1) E (1) e e1 L ME MH w Z (1)

max. min. max. max.

1.73 0.53 0.36 19.50 6.48 3.60 8.25 10.0

mm 4.2 0.51 3.2 2.54 7.62 0.254 2.2

1.13 0.38 0.23 18.55 6.20 3.05 7.80 8.3

0.068 0.021 0.014 0.77 0.26 0.14 0.32 0.39

inches 0.17 0.02 0.13 0.1 0.3 0.01 0.087

0.044 0.015 0.009 0.73 0.24 0.12 0.31 0.33

Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC JEITA PROJECTION

99-12-27

SOT27-1 050G04 MO-001 SC-501-14

03-02-13

Fig 6. Package outline SOT27-1 (DIP14)

HEF4071B All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 7 — 15 November 2011 7 of 12

NXP Semiconductors HEF4071B

Quad 2-input OR gate

SO14: plastic small outline package; 14 leads; body width 3.9 mm SOT108-1

D E A

X

y HE v M A

14 8

Q

A2

(A 3) A

A1

pin 1 index

θ

Lp

1 7 L

e w M detail X

bp

0 2.5 5 mm

scale

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

A

UNIT A1 A2 A3 bp c D (1) E (1) e HE L Lp Q v w y Z (1) θ

max.

0.25 1.45 0.49 0.25 8.75 4.0 6.2 1.0 0.7 0.7

mm 1.75 0.25 1.27 1.05 0.25 0.25 0.1

0.10 1.25 0.36 0.19 8.55 3.8 5.8 0.4 0.6 0.3 8o

o

0.010 0.057 0.019 0.0100 0.35 0.16 0.244 0.039 0.028 0.028 0

inches 0.069 0.01 0.05 0.041 0.01 0.01 0.004

0.004 0.049 0.014 0.0075 0.34 0.15 0.228 0.016 0.024 0.012

Note

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC JEITA PROJECTION

99-12-27

SOT108-1 076E06 MS-012

03-02-19

Fig 7. Package outline SOT108-1 (SO14)

HEF4071B All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 7 — 15 November 2011 8 of 12

NXP Semiconductors HEF4071B

Quad 2-input OR gate

13. Revision history

Table 11. Revision history

Document ID Release date Data sheet status Change notice Supersedes

HEF4071B v.7 20111115 Product data sheet - HEF4071B v.6

Modifications: • Section Applications removed

• Table 6: IOH minimum values changed to maximum

HEF4071B v.6 20091201 Product data sheet - HEF4071B v.5

HEF4071B v.5 20090728 Product data sheet - HEF4071B v.4

HEF4071B v.4 20081128 Product data sheet - HEF4071B_CNV v.3

HEF4071B_CNV v.3 19950101 Product specification - HEF4071B_CNV v.2

HEF4071B_CNV v.2 19950101 Product specification - -

HEF4071B All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 7 — 15 November 2011 9 of 12

NXP Semiconductors HEF4071B

Quad 2-input OR gate

14. Legal information

14.1 Data sheet status

Document status[1][2] Product status[3] Definition

Objective [short] data sheet Development This document contains data from the objective specification for product development.

Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.

Product [short] data sheet Production This document contains the product specification.

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term ‘short data sheet’ is explained in section “Definitions”.

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status

information is available on the Internet at URL http://www.nxp.com.

14.2 Definitions malfunction of an NXP Semiconductors product can reasonably be expected

to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors accepts no liability for inclusion and/or use of

Draft — The document is a draft version only. The content is still under

NXP Semiconductors products in such equipment or applications and

internal review and subject to formal approval, which may result in

therefore such inclusion and/or use is at the customer’s own risk.

modifications or additions. NXP Semiconductors does not give any

representations or warranties as to the accuracy or completeness of Applications — Applications that are described herein for any of these

information included herein and shall have no liability for the consequences of products are for illustrative purposes only. NXP Semiconductors makes no

use of such information. representation or warranty that such applications will be suitable for the

specified use without further testing or modification.

Short data sheet — A short data sheet is an extract from a full data sheet

with the same product type number(s) and title. A short data sheet is intended Customers are responsible for the design and operation of their applications

for quick reference only and should not be relied upon to contain detailed and and products using NXP Semiconductors products, and NXP Semiconductors

full information. For detailed and full information see the relevant full data accepts no liability for any assistance with applications or customer product

sheet, which is available on request via the local NXP Semiconductors sales design. It is customer’s sole responsibility to determine whether the NXP

office. In case of any inconsistency or conflict with the short data sheet, the Semiconductors product is suitable and fit for the customer’s applications and

full data sheet shall prevail. products planned, as well as for the planned application and use of

customer’s third party customer(s). Customers should provide appropriate

Product specification — The information and data provided in a Product design and operating safeguards to minimize the risks associated with their

data sheet shall define the specification of the product as agreed between applications and products.

NXP Semiconductors and its customer, unless NXP Semiconductors and

customer have explicitly agreed otherwise in writing. In no event however, NXP Semiconductors does not accept any liability related to any default,

shall an agreement be valid in which the NXP Semiconductors product is damage, costs or problem which is based on any weakness or default in the

deemed to offer functions and qualities beyond those described in the customer’s applications or products, or the application or use by customer’s

Product data sheet. third party customer(s). Customer is responsible for doing all necessary

testing for the customer’s applications and products using NXP

Semiconductors products in order to avoid a default of the applications and

14.3 Disclaimers the products or of the application or use by customer’s third party

customer(s). NXP does not accept any liability in this respect.

Limited warranty and liability — Information in this document is believed to Limiting values — Stress above one or more limiting values (as defined in

be accurate and reliable. However, NXP Semiconductors does not give any the Absolute Maximum Ratings System of IEC 60134) will cause permanent

representations or warranties, expressed or implied, as to the accuracy or damage to the device. Limiting values are stress ratings only and (proper)

completeness of such information and shall have no liability for the operation of the device at these or any other conditions above those given in

consequences of use of such information. the Recommended operating conditions section (if present) or the

Characteristics sections of this document is not warranted. Constant or

In no event shall NXP Semiconductors be liable for any indirect, incidental,

repeated exposure to limiting values will permanently and irreversibly affect

punitive, special or consequential damages (including - without limitation - lost

the quality and reliability of the device.

profits, lost savings, business interruption, costs related to the removal or

replacement of any products or rework charges) whether or not such Terms and conditions of commercial sale — NXP Semiconductors

damages are based on tort (including negligence), warranty, breach of products are sold subject to the general terms and conditions of commercial

contract or any other legal theory. sale, as published at http://www.nxp.com/profile/terms, unless otherwise

Notwithstanding any damages that customer might incur for any reason agreed in a valid written individual agreement. In case an individual

whatsoever, NXP Semiconductors’ aggregate and cumulative liability towards agreement is concluded only the terms and conditions of the respective

customer for the products described herein shall be limited in accordance agreement shall apply. NXP Semiconductors hereby expressly objects to

with the Terms and conditions of commercial sale of NXP Semiconductors. applying the customer’s general terms and conditions with regard to the

purchase of NXP Semiconductors products by customer.

Right to make changes — NXP Semiconductors reserves the right to make

changes to information published in this document, including without No offer to sell or license — Nothing in this document may be interpreted or

limitation specifications and product descriptions, at any time and without construed as an offer to sell products that is open for acceptance or the grant,

notice. This document supersedes and replaces all information supplied prior conveyance or implication of any license under any copyrights, patents or

to the publication hereof. other industrial or intellectual property rights.

Suitability for use — NXP Semiconductors products are not designed, Export control — This document as well as the item(s) described herein

authorized or warranted to be suitable for use in life support, life-critical or may be subject to export control regulations. Export might require a prior

safety-critical systems or equipment, nor in applications where failure or authorization from competent authorities.

HEF4071B All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 7 — 15 November 2011 10 of 12

NXP Semiconductors HEF4071B

Quad 2-input OR gate

Non-automotive qualified products — Unless this data sheet expressly NXP Semiconductors’ specifications such use shall be solely at customer’s

states that this specific NXP Semiconductors product is automotive qualified, own risk, and (c) customer fully indemnifies NXP Semiconductors for any

the product is not suitable for automotive use. It is neither qualified nor tested liability, damages or failed product claims resulting from customer design and

in accordance with automotive testing or application requirements. NXP use of the product for automotive applications beyond NXP Semiconductors’

Semiconductors accepts no liability for inclusion and/or use of standard warranty and NXP Semiconductors’ product specifications.

non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in

automotive applications to automotive specifications and standards, customer 14.4 Trademarks

(a) shall use the product without NXP Semiconductors’ warranty of the

Notice: All referenced brands, product names, service names and trademarks

product for such automotive applications, use and specifications, and (b)

are the property of their respective owners.

whenever customer uses the product for automotive applications beyond

15. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

HEF4071B All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 7 — 15 November 2011 11 of 12

NXP Semiconductors HEF4071B

Quad 2-input OR gate

16. Contents

1 General description . . . . . . . . . . . . . . . . . . . . . . 1

2 Features and benefits . . . . . . . . . . . . . . . . . . . . 1

3 Ordering information . . . . . . . . . . . . . . . . . . . . . 1

4 Functional diagram . . . . . . . . . . . . . . . . . . . . . . 1

5 Pinning information . . . . . . . . . . . . . . . . . . . . . . 2

5.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

5.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 2

6 Functional description . . . . . . . . . . . . . . . . . . . 2

7 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 3

8 Recommended operating conditions. . . . . . . . 3

9 Static characteristics. . . . . . . . . . . . . . . . . . . . . 4

10 Dynamic characteristics . . . . . . . . . . . . . . . . . . 5

11 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

12 Package outline . . . . . . . . . . . . . . . . . . . . . . . . . 7

13 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . 9

14 Legal information. . . . . . . . . . . . . . . . . . . . . . . 10

14.1 Data sheet status . . . . . . . . . . . . . . . . . . . . . . 10

14.2 Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

14.3 Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

14.4 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 11

15 Contact information. . . . . . . . . . . . . . . . . . . . . 11

16 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Please be aware that important notices concerning this document and the product(s)

described herein, have been included in section ‘Legal information’.

© NXP B.V. 2011. All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 15 November 2011

Document identifier: HEF4071B

You might also like

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesFrom EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesRating: 4.5 out of 5 stars4.5/5 (7)

- Governor and Droop Basics - FinalDocument5 pagesGovernor and Droop Basics - FinalRasitha Peiris100% (1)

- Gentleyag Pro-U: Outstanding Results. Treating Multiple Indications. UpgradableDocument4 pagesGentleyag Pro-U: Outstanding Results. Treating Multiple Indications. UpgradableAndrea MejiaNo ratings yet

- FEM LectureDocument35 pagesFEM LecturebolamecNo ratings yet

- Chapter - 11: Prepared by Dr. K. SubramanyaDocument21 pagesChapter - 11: Prepared by Dr. K. SubramanyaMaha Sheikh83% (6)

- Rock BurstDocument74 pagesRock BurstSajid Iqbal100% (1)

- Lecture 9 - Quality AssuranceDocument41 pagesLecture 9 - Quality AssuranceLindaNo ratings yet

- Tale of 2 Deep Singapore Basements and How 3D Modeling Led To A Leaner Design and Keener Construction Programme - EiSandaDocument13 pagesTale of 2 Deep Singapore Basements and How 3D Modeling Led To A Leaner Design and Keener Construction Programme - EiSandablithevincentNo ratings yet

- HEF4071B: 1. General DescriptionDocument11 pagesHEF4071B: 1. General DescriptionElectronicos CaldasNo ratings yet

- HEF4071BDocument9 pagesHEF4071Bkopii0548No ratings yet

- HEF4081BDocument9 pagesHEF4081BGerman PascucciNo ratings yet

- HEF4093B: 1. General DescriptionDocument14 pagesHEF4093B: 1. General Descriptionpre freedaNo ratings yet

- Hef4001b 2938071Document10 pagesHef4001b 2938071Amit Kumar BasuNo ratings yet

- HEtghhuF40 DatasheetDocument11 pagesHEtghhuF40 DatasheetsongdashengNo ratings yet

- HEF4049BDocument12 pagesHEF4049BchrisNo ratings yet

- HEF4050B: 1. General DescriptionDocument12 pagesHEF4050B: 1. General DescriptionTamas VorosNo ratings yet

- HEF4093BDocument12 pagesHEF4093Bbd4ukyNo ratings yet

- Hef40106b 2938045Document14 pagesHef40106b 2938045Hisham MohamedNo ratings yet

- HEF4069UB: 1. General DescriptionDocument17 pagesHEF4069UB: 1. General DescriptionJoel PalzaNo ratings yet

- HEF4066BDocument13 pagesHEF4066Bparvalhao_No ratings yet

- HEF4555B: 1. General DescriptionDocument10 pagesHEF4555B: 1. General DescriptionLechero De Corazon MHNo ratings yet

- HEF4069URDocument18 pagesHEF4069URparvalhao_No ratings yet

- SN 74 CBTLV 3125Document22 pagesSN 74 CBTLV 3125TomášUličnýNo ratings yet

- 74AHC02 74AHCT02: 1. General DescriptionDocument13 pages74AHC02 74AHCT02: 1. General DescriptionalexNo ratings yet

- 74ALS04B Hex Inverter: Pin ConfigurationDocument2 pages74ALS04B Hex Inverter: Pin ConfigurationAravind RajanNo ratings yet

- 74HC132 74HCT132: 1 General DescriptionDocument18 pages74HC132 74HCT132: 1 General DescriptionSantiago RodríguezNo ratings yet

- HEF4051B: 1. General DescriptionDocument23 pagesHEF4051B: 1. General DescriptionNguyễn TrungNo ratings yet

- 74LV04Document12 pages74LV04mulia usmanNo ratings yet

- Po54G02A, Po74G02A: 54, 74 Series Noise Cancellation GHZ LogicDocument6 pagesPo54G02A, Po74G02A: 54, 74 Series Noise Cancellation GHZ LogicspotNo ratings yet

- HD74LS86: Quadruple 2-Input Exclusive-OR GatesDocument5 pagesHD74LS86: Quadruple 2-Input Exclusive-OR GatesRamírez López Erik SandroNo ratings yet

- 74HC HCT00Document12 pages74HC HCT00thecovenant2345No ratings yet

- 74LVC14A: 1. General DescriptionDocument18 pages74LVC14A: 1. General Descriptionrıdvan71No ratings yet

- 74HC02 74HCT02: 1. General DescriptionDocument16 pages74HC02 74HCT02: 1. General DescriptionmohamadziNo ratings yet

- 74 VHCT 08 AftDocument8 pages74 VHCT 08 AftNguyễn QuangNo ratings yet

- Data Sheet: 74AHC125 74AHCT125Document16 pagesData Sheet: 74AHC125 74AHCT125yanjunNo ratings yet

- 74ahc Ahct125Document16 pages74ahc Ahct125mikeguo76No ratings yet

- 74AHC08 74AHCT08: 1. General DescriptionDocument14 pages74AHC08 74AHCT08: 1. General DescriptionalexNo ratings yet

- 74AHC08 74AHCT08: 1. General DescriptionDocument14 pages74AHC08 74AHCT08: 1. General DescriptionalexNo ratings yet

- General Description: Quad 2-Input AND GateDocument10 pagesGeneral Description: Quad 2-Input AND Gateblackslash82No ratings yet

- Data Sheet: HEF4502B BuffersDocument4 pagesData Sheet: HEF4502B BuffersGoodLookingPirateNo ratings yet

- Imp Chip Diagrams 12Document7 pagesImp Chip Diagrams 12Chandani ShahNo ratings yet

- HD74LS00PDocument5 pagesHD74LS00PBIMO MODELADONo ratings yet

- 74AHC08 74AHCT08: 1. General DescriptionDocument14 pages74AHC08 74AHCT08: 1. General Descriptionteranet tbtNo ratings yet

- MC74LCX02DTR2G C233475Document9 pagesMC74LCX02DTR2G C233475somtchekusNo ratings yet

- HD74LS08: Quadruple 2-Input Positive AND GatesDocument6 pagesHD74LS08: Quadruple 2-Input Positive AND GatesMohammed Al gobariNo ratings yet

- 74HC02 74HCT02: 1. General DescriptionDocument13 pages74HC02 74HCT02: 1. General DescriptionLuccio MontanneriNo ratings yet

- HEF4001B PhilipsSemiconductorsDocument11 pagesHEF4001B PhilipsSemiconductorsmagsi20No ratings yet

- SN54F32, SN74F32 Quadruple 2-Input Positive-Or Gates: DescriptionDocument19 pagesSN54F32, SN74F32 Quadruple 2-Input Positive-Or Gates: DescriptionAlfonso BlancoNo ratings yet

- HEF40106BDocument14 pagesHEF40106BJames JansonNo ratings yet

- HD74LS02: Quadruple 2-Input Positive NOR GatesDocument6 pagesHD74LS02: Quadruple 2-Input Positive NOR GatesStevhen Dem SonNo ratings yet

- SN 74 CBTLV 3257Document6 pagesSN 74 CBTLV 3257Кирилл ОлейникNo ratings yet

- Ricoh RP111N361DDocument44 pagesRicoh RP111N361DClaudioNo ratings yet

- 74HC02 74HCT02: 1. General DescriptionDocument12 pages74HC02 74HCT02: 1. General Descriptionforeman pemudaNo ratings yet

- 2576 LDocument9 pages2576 LclanonNo ratings yet

- HD74LS279: Quadruple S-R LatchesDocument5 pagesHD74LS279: Quadruple S-R LatchesANITHA MNo ratings yet

- Po54G00A, Po74G00A: 54, 74 Series Noise Cancellation GHZ LogicDocument6 pagesPo54G00A, Po74G00A: 54, 74 Series Noise Cancellation GHZ LogicspotNo ratings yet

- Data Sheet: HEF4093B GatesDocument6 pagesData Sheet: HEF4093B GatesГригорий ШубинNo ratings yet

- Hef4093b PDFDocument6 pagesHef4093b PDFGoodLookingPirateNo ratings yet

- Data Sheet74ls00Document8 pagesData Sheet74ls00evhyajahNo ratings yet

- HEF4538BDocument14 pagesHEF4538BAlireza RahimiNo ratings yet

- 1 Tle5206 2 - 1Document23 pages1 Tle5206 2 - 1Fran CastanoNo ratings yet

- Dual 4-Channel Analog Multiplexer/Demultiplexer AZ4052Document18 pagesDual 4-Channel Analog Multiplexer/Demultiplexer AZ4052norgenNo ratings yet

- 74HC HCT366Document17 pages74HC HCT366Juciêr AlcântaraNo ratings yet

- Data Sheet AD620Document5 pagesData Sheet AD620aditya rinaldiNo ratings yet

- 74HC HCT4051Document28 pages74HC HCT4051Razak JeyNo ratings yet

- Quad 2-Input AND Gate: Integrated CircuitsDocument7 pagesQuad 2-Input AND Gate: Integrated CircuitsDaniel MuñozNo ratings yet

- 6.2 Total Internal Reflection SABDocument71 pages6.2 Total Internal Reflection SABEngerNo ratings yet

- Course Offer 20192020-1Document1 pageCourse Offer 20192020-1JunYangNo ratings yet

- Hydramem 4021 LpeDocument2 pagesHydramem 4021 Lpemaksudur4No ratings yet

- Caltesys Calibration ScopeDocument17 pagesCaltesys Calibration ScopeChandraNo ratings yet

- P3 MYE 2016 Answer Key - Version 4Document3 pagesP3 MYE 2016 Answer Key - Version 4Bernard ChanNo ratings yet

- Grippers and Lifting MechanismsDocument25 pagesGrippers and Lifting Mechanismsengr_faheemNo ratings yet

- Spectrophotochemical and Chroma Analysis .PPDocument55 pagesSpectrophotochemical and Chroma Analysis .PPKhyra JuliaNo ratings yet

- Graetz ProblemDocument13 pagesGraetz ProblemAbimbola100% (1)

- Chapter 8 Physics NotesDocument11 pagesChapter 8 Physics NotesAhnJelloNo ratings yet

- Column N Foundation DesignDocument26 pagesColumn N Foundation DesignSA023No ratings yet

- Difficulty Level Analysis NEETDocument4 pagesDifficulty Level Analysis NEETVinod Kumar JainNo ratings yet

- Phillips, J. D. Weathering Instability and Landscape EvolutionDocument18 pagesPhillips, J. D. Weathering Instability and Landscape EvolutionJorge MarquesNo ratings yet

- TEST 1 DAM14203 - Sem1 2021 - 19 NovDocument3 pagesTEST 1 DAM14203 - Sem1 2021 - 19 NovSsg AqifNo ratings yet

- Briquetting of Palm Fibre and Shell From The Processing of Palm Nuts To Palm OilDocument6 pagesBriquetting of Palm Fibre and Shell From The Processing of Palm Nuts To Palm OilIrfan FahrurozyNo ratings yet

- Emax Pressimpulse Booklet e 636824 PDFDocument12 pagesEmax Pressimpulse Booklet e 636824 PDFFabio WenoNo ratings yet

- Boiling Range of GasolineDocument4 pagesBoiling Range of GasolineSaad AhmedNo ratings yet

- JBL Spyro User GuideDocument68 pagesJBL Spyro User GuiderowanNo ratings yet

- TN4602 PDFDocument3 pagesTN4602 PDFMarcel BlinduNo ratings yet

- Me328 - Carabiner Project 1Document20 pagesMe328 - Carabiner Project 1api-534925017No ratings yet

- Taules SimetriaDocument12 pagesTaules SimetriahectorNo ratings yet

- ExtremophilesDocument7 pagesExtremophilesStephen MooreNo ratings yet

- Sample Exams - Mechanics DynamicsDocument22 pagesSample Exams - Mechanics DynamicsrahulNo ratings yet

- Slopes and The DerivativeDocument177 pagesSlopes and The DerivativeCamille Doon PerladaNo ratings yet