Professional Documents

Culture Documents

CP283

Uploaded by

zero cloud0 ratings0% found this document useful (0 votes)

19 views1 pageThis document provides process and geometry details for Central Semiconductor Corp's CP283 NPN silicon power transistor chip. Key details include a die size of 68 x 68 mils, die thickness of 9.5 mils, top side metalization of Al at 45,000Å, back side metalization of Ti/Ni/Ag at 3000Å/10,000Å/10,000Å, and the principal device type being the MJE13003 transistor. The gross die per 5 inch wafer is 3,675. Central Semiconductor Corp is located at 145 Adams Avenue, Hauppauge, NY.

Original Description:

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document provides process and geometry details for Central Semiconductor Corp's CP283 NPN silicon power transistor chip. Key details include a die size of 68 x 68 mils, die thickness of 9.5 mils, top side metalization of Al at 45,000Å, back side metalization of Ti/Ni/Ag at 3000Å/10,000Å/10,000Å, and the principal device type being the MJE13003 transistor. The gross die per 5 inch wafer is 3,675. Central Semiconductor Corp is located at 145 Adams Avenue, Hauppauge, NY.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

19 views1 pageCP283

Uploaded by

zero cloudThis document provides process and geometry details for Central Semiconductor Corp's CP283 NPN silicon power transistor chip. Key details include a die size of 68 x 68 mils, die thickness of 9.5 mils, top side metalization of Al at 45,000Å, back side metalization of Ti/Ni/Ag at 3000Å/10,000Å/10,000Å, and the principal device type being the MJE13003 transistor. The gross die per 5 inch wafer is 3,675. Central Semiconductor Corp is located at 145 Adams Avenue, Hauppauge, NY.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

TM

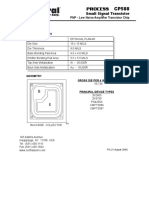

PROCESS CP283

Power Transistor Central

Semiconductor Corp.

NPN - Silicon Power Transistor Chip

PROCESS DETAILS

Die Size 68 x 68 MILS

Die Thickness 9.5 MILS

Base Bonding Pad Area 18 x 11 MILS

Emitter Bonding Pad Area 18 x 12 MILS

Top Side Metalization Al - 45,000Å

Back Side Metalization Ti/Ni/Ag - (3000Å, 10,000Å, 10,000Å)

GEOMETRY

GROSS DIE PER 5 INCH WAFER

3,675

PRINCIPAL DEVICE TYPES

MJE13003

145 Adams Avenue

Hauppauge, NY 11788 USA

Tel: (631) 435-1110

Fax: (631) 435-1824

www.centralsemi.com R0 (20-January 2006)

You might also like

- Komatsu pc40-6 Operation Maintenance Manual PDFDocument107 pagesKomatsu pc40-6 Operation Maintenance Manual PDFzero cloud100% (1)

- XR5 Data SheetDocument7 pagesXR5 Data SheetReeta DuttaNo ratings yet

- Ms 33kv Cable LayingDocument11 pagesMs 33kv Cable LayingAhmed Nagy100% (2)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Komatsu Epc 02 2011 Book ListDocument66 pagesKomatsu Epc 02 2011 Book Listzero cloudNo ratings yet

- Transistor 2021 Pag 3Document2 pagesTransistor 2021 Pag 3StuxnetNo ratings yet

- Central: ProcessDocument2 pagesCentral: ProcessNelson antonioNo ratings yet

- Central Central: ProcessDocument2 pagesCentral Central: ProcessNelson antonioNo ratings yet

- Datasheet TRDocument2 pagesDatasheet TRitssna consulting servicesNo ratings yet

- Central: ProcessDocument2 pagesCentral: ProcessNelson antonioNo ratings yet

- CP309Document2 pagesCP309Victor HemzNo ratings yet

- Datasheetsvf PDFDocument2 pagesDatasheetsvf PDFarjetaNo ratings yet

- Process: Small Signal TransistorDocument2 pagesProcess: Small Signal TransistorVictor HemzNo ratings yet

- Material/S Sample Card: Spug DppsDocument3 pagesMaterial/S Sample Card: Spug DppsWency JavateNo ratings yet

- Transistor 2021 Pag 1Document2 pagesTransistor 2021 Pag 1StuxnetNo ratings yet

- 9093KAMDocument1 page9093KAMleiyanNo ratings yet

- TM-533-T/R: TACT SwitchDocument4 pagesTM-533-T/R: TACT SwitchGyörök PeterNo ratings yet

- Present PCB+ NSC (2302) BDocument13 pagesPresent PCB+ NSC (2302) BGowthaman ArumugamNo ratings yet

- MCA and MOP For Your Humidifier ExplainedDocument2 pagesMCA and MOP For Your Humidifier ExplainedAntonio LantiguaNo ratings yet

- 3.5kW Spec Sheet (Data)Document2 pages3.5kW Spec Sheet (Data)Nishant SaxenaNo ratings yet

- Compro Aii 2021Document14 pagesCompro Aii 2021mbetNo ratings yet

- Análisis Del Cobre en Muestras de Concentrado de CobreDocument2 pagesAnálisis Del Cobre en Muestras de Concentrado de CobreJose Miguel Benavente MendezNo ratings yet

- Amstech LineCard 2010Document1 pageAmstech LineCard 2010tt234No ratings yet

- P6KE100 To P6KE440ADocument5 pagesP6KE100 To P6KE440AtycristinaNo ratings yet

- VLSID Fall10 LowPowerDocument42 pagesVLSID Fall10 LowPowerajayNo ratings yet

- Nde Request - Thickness SurveyDocument1 pageNde Request - Thickness SurveySam RajaNo ratings yet

- Selection and Ordering Data: Motion ControlDocument46 pagesSelection and Ordering Data: Motion ControlMiguel RomeroNo ratings yet

- SNP - Proposal StatmentDocument97 pagesSNP - Proposal Statmentvoeunsopha168No ratings yet

- 150-0023 Control Gp-Engine ElectronicDocument2 pages150-0023 Control Gp-Engine ElectronicHugo CiprianiNo ratings yet

- Vestax Handytrax UsbDocument22 pagesVestax Handytrax UsbMaximiliano TavernaNo ratings yet

- Item 13 SW Cooling Pump Misc Equip Sys - 721-113.10Document430 pagesItem 13 SW Cooling Pump Misc Equip Sys - 721-113.10Игорь КлимовNo ratings yet

- Process: Small Signal TransistorDocument2 pagesProcess: Small Signal TransistorVictor HemzNo ratings yet

- Transistor 2021 Pag 1Document2 pagesTransistor 2021 Pag 1StuxnetNo ratings yet

- Process: Small Signal TransistorDocument2 pagesProcess: Small Signal TransistorVictor HemzNo ratings yet

- PSC PoleDocument3 pagesPSC PoleKush SharmaNo ratings yet

- 1006 PDFDocument18 pages1006 PDFMohamed Jaffar Sadique100% (1)

- Customer: Project: Sheet No. Title: Sheet Contents: Drawn Dwg. No. Approved Revision Date ScaleDocument6 pagesCustomer: Project: Sheet No. Title: Sheet Contents: Drawn Dwg. No. Approved Revision Date ScaleLionel BacaniNo ratings yet

- Master Network Installation Tool Kit: 1PK-938A / 1PK-938BDocument1 pageMaster Network Installation Tool Kit: 1PK-938A / 1PK-938BrubenacvNo ratings yet

- Mustang PBDocument2 pagesMustang PBBob ScharfNo ratings yet

- Solar Pumping Project Solar Pumping Project: Grupo Bonnett S.ADocument8 pagesSolar Pumping Project Solar Pumping Project: Grupo Bonnett S.AJeka Cuevs SaenzNo ratings yet

- Repair of CAPAC Cathodic Protection System, Fabrication of AVR &Document2 pagesRepair of CAPAC Cathodic Protection System, Fabrication of AVR &Tin SoriaoNo ratings yet

- MK-S7097-P-001 Service Water Storage Tank Full (Revised by SSA)Document55 pagesMK-S7097-P-001 Service Water Storage Tank Full (Revised by SSA)Ranu JanuarNo ratings yet

- All Cummins CataloguesDocument205 pagesAll Cummins CataloguesahmedabougallabNo ratings yet

- MagneticMotors PDFDocument34 pagesMagneticMotors PDFJoao CarlosNo ratings yet

- YSK - Electromagnetic Flowmeter CW PhilemonDocument1 pageYSK - Electromagnetic Flowmeter CW PhilemonsswahyudiNo ratings yet

- Pt. Pancatama Tikta Mukti: Valves Acv, Instrumentations For WTP, Waterworks MunicipalsDocument2 pagesPt. Pancatama Tikta Mukti: Valves Acv, Instrumentations For WTP, Waterworks MunicipalsMaylinda ArsaNo ratings yet

- Solar Panel Specification: HT-SAAE 270 Watts PolycrystallineDocument3 pagesSolar Panel Specification: HT-SAAE 270 Watts Polycrystallinejinky mae lusterioNo ratings yet

- AL-SE3510 Servo Type CNC Turret Punching Machine ALLES Offersheet 20210722Document9 pagesAL-SE3510 Servo Type CNC Turret Punching Machine ALLES Offersheet 20210722mehrdadgeminiNo ratings yet

- Larson Electronics LLC 9419 E US HWY 175, Kemp, TX 75143 Phone: 800.369.6671 Fax: 903.498.3364Document3 pagesLarson Electronics LLC 9419 E US HWY 175, Kemp, TX 75143 Phone: 800.369.6671 Fax: 903.498.3364Coba BisnisNo ratings yet

- Quote 1500148911Document3 pagesQuote 1500148911Subhash C MohanNo ratings yet

- S. No. Description Unit Value 1.0 System Design Data 1.2 Ac SupplyDocument3 pagesS. No. Description Unit Value 1.0 System Design Data 1.2 Ac Supplyrohit kumarNo ratings yet

- Electromagnetic Braking SystemDocument7 pagesElectromagnetic Braking SystemAmnaNo ratings yet

- Alternates TO Surface Mount Tantalum Electrolytic CapacitorsDocument21 pagesAlternates TO Surface Mount Tantalum Electrolytic CapacitorsGuGazNo ratings yet

- PT2398Document0 pagesPT2398BengalProNo ratings yet

- Parker TB Series MotorsDocument28 pagesParker TB Series Motorsccorp0089No ratings yet

- Prepared by Date PRA 28-Jan-17 Checked by Revision Dr. Yeri R0 MegaDocument1 pagePrepared by Date PRA 28-Jan-17 Checked by Revision Dr. Yeri R0 MegapravinNo ratings yet

- Engr. Florencio D. BerenguelDocument79 pagesEngr. Florencio D. BerenguelJosamy MartinezNo ratings yet

- Electrical Working 6 Month To 3 Years Delhi and Near 15aug2017!1!852Document216 pagesElectrical Working 6 Month To 3 Years Delhi and Near 15aug2017!1!852prerna nandNo ratings yet

- NRJ6HM-1: Features & BenefitsDocument3 pagesNRJ6HM-1: Features & BenefitsHelson Jader RochaNo ratings yet

- Optimization of Machining Parameter For Surface Roughness On Wedm of En36 Alloy SteelDocument4 pagesOptimization of Machining Parameter For Surface Roughness On Wedm of En36 Alloy SteelIOSRjournalNo ratings yet

- Q - 14978 MRT-200 - Usa''Document4 pagesQ - 14978 MRT-200 - Usa''Gama LtdaNo ratings yet

- Computer-Communication NetworksFrom EverandComputer-Communication NetworksJames S. MeditchNo ratings yet

- (M16c單晶片) (M306N5FCTFP) m306n5fctfpukDocument90 pages(M16c單晶片) (M306N5FCTFP) m306n5fctfpukzero cloudNo ratings yet

- 2SC2855, 2SC2856: Silicon NPN EpitaxialDocument10 pages2SC2855, 2SC2856: Silicon NPN Epitaxialzero cloudNo ratings yet

- Dtc144Eu3 HZG: OutlineDocument9 pagesDtc144Eu3 HZG: Outlinezero cloudNo ratings yet

- Silicon PNP Power Transistors: Savantic Semiconductor Product SpecificationDocument5 pagesSilicon PNP Power Transistors: Savantic Semiconductor Product Specificationzero cloudNo ratings yet

- Silicon PNP Power Transistors: Savantic Semiconductor Product SpecificationDocument5 pagesSilicon PNP Power Transistors: Savantic Semiconductor Product Specificationzero cloudNo ratings yet

- 2SC2855, 2SC2856: Silicon NPN EpitaxialDocument10 pages2SC2855, 2SC2856: Silicon NPN Epitaxialzero cloudNo ratings yet

- A1015 ToshibaSemiconductor PDFDocument3 pagesA1015 ToshibaSemiconductor PDFzero cloudNo ratings yet

- HT1117 Series 1A General Purpose LDO: FeaturesDocument10 pagesHT1117 Series 1A General Purpose LDO: Featureszero cloudNo ratings yet

- Silicon PNP Triple Diffused: ApplicationDocument5 pagesSilicon PNP Triple Diffused: Applicationzero cloudNo ratings yet

- 1, TLP521 2, TLP521 4: Programmable Controllers Ac/Dc Input Module Solid State RelayDocument9 pages1, TLP521 2, TLP521 4: Programmable Controllers Ac/Dc Input Module Solid State Relayzero cloudNo ratings yet

- z1047 (TS)Document1 pagez1047 (TS)zero cloudNo ratings yet

- Unisonic Technologies Co., LTD: Telephone Tone RingerDocument5 pagesUnisonic Technologies Co., LTD: Telephone Tone Ringerzero cloudNo ratings yet

- Transient Voltage Suppression Diodes: Echnical RticleDocument3 pagesTransient Voltage Suppression Diodes: Echnical Rticlezero cloudNo ratings yet

- Excavator: - Flow Rate - Pressure Adjustment (+/-5 Bar)Document7 pagesExcavator: - Flow Rate - Pressure Adjustment (+/-5 Bar)zero cloud100% (1)