Professional Documents

Culture Documents

Datasheetsvf PDF

Uploaded by

arjeta0 ratings0% found this document useful (0 votes)

15 views2 pagesOriginal Title

datasheetsvf.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

15 views2 pagesDatasheetsvf PDF

Uploaded by

arjetaCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 2

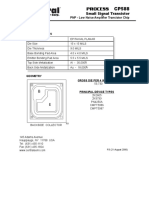

PROCESS CP588

Small Signal Transistor

PNP - Low Noise Amplifier Transistor Chip

PROCESS DETAILS

Process EPITAXIAL PLANAR

Die Size 15 x 15 MILS

Die Thickness 9.0 MILS

Base Bonding Pad Area 4.0 x 4.0 MILS

Emitter Bonding Pad Area 5.5 x 5.5 MILS

Top Side Metalization Al - 30,000Å

Back Side Metalization Au - 18,000Å

GEOMETRY

GROSS DIE PER 4 INCH WAFER

53,730

PRINCIPAL DEVICE TYPES

2N2605

2N3799

PN4250A

CMPT5086

CMPT5087

BACKSIDE COLLECTOR

145 Adams Avenue

Hauppauge, NY 11788 USA

Tel: (631) 435-1110

Fax: (631) 435-1824

www.centralsemi.com R3 (21-August 2006)

PROCESS CP588

Typical Electrical Characteristics

145 Adams Avenue

Hauppauge, NY 11788 USA

Tel: (631) 435-1110

Fax: (631) 435-1824

www.centralsemi.com R3 (21-August 2006)

You might also like

- Process: Small Signal TransistorDocument2 pagesProcess: Small Signal TransistorVictor HemzNo ratings yet

- Datasheet TRDocument2 pagesDatasheet TRitssna consulting servicesNo ratings yet

- Electronic Circuits, Systems and Standards: The Best of EDNFrom EverandElectronic Circuits, Systems and Standards: The Best of EDNRating: 3 out of 5 stars3/5 (2)

- Central: ProcessDocument2 pagesCentral: ProcessNelson antonioNo ratings yet

- Anglo–American Microelectronics Data 1968–69: Manufacturers A–PFrom EverandAnglo–American Microelectronics Data 1968–69: Manufacturers A–PNo ratings yet

- Central: ProcessDocument2 pagesCentral: ProcessNelson antonioNo ratings yet

- Central Semiconductor CP314 Transistor Process DetailsDocument2 pagesCentral Semiconductor CP314 Transistor Process DetailsNelson antonioNo ratings yet

- Transistor 2021 Pag 1Document2 pagesTransistor 2021 Pag 1StuxnetNo ratings yet

- Process: Small Signal TransistorDocument2 pagesProcess: Small Signal TransistorVictor HemzNo ratings yet

- Transistor 2021 Pag 1Document2 pagesTransistor 2021 Pag 1StuxnetNo ratings yet

- Process: Small Signal TransistorDocument2 pagesProcess: Small Signal TransistorVictor HemzNo ratings yet

- CP309Document2 pagesCP309Victor HemzNo ratings yet

- Transistor 2021 Pag 3Document2 pagesTransistor 2021 Pag 3StuxnetNo ratings yet

- BDP3100 Part ListDocument10 pagesBDP3100 Part ListcorrabNo ratings yet

- 1SNC110001C0202 CH EDocument14 pages1SNC110001C0202 CH EvonnetNo ratings yet

- Sample Bill of Materials (BOM) - Screaming Circuits Buys MaterialsDocument2 pagesSample Bill of Materials (BOM) - Screaming Circuits Buys MaterialsRahul DalviNo ratings yet

- SC Sample BomDocument1 pageSC Sample BomVenkat BhagavatiNo ratings yet

- Bill of Materials Excel TemplateDocument1 pageBill of Materials Excel TemplatePro ResourcesNo ratings yet

- Sample Bill of Materials (BOM) - Screaming Circuits Buys MaterialsDocument1 pageSample Bill of Materials (BOM) - Screaming Circuits Buys MaterialsDanny SiagianNo ratings yet

- Present PCB+ NSC (2302) BDocument13 pagesPresent PCB+ NSC (2302) BGowthaman ArumugamNo ratings yet

- Alternates TO Surface Mount Tantalum Electrolytic CapacitorsDocument21 pagesAlternates TO Surface Mount Tantalum Electrolytic CapacitorsGuGazNo ratings yet

- Process: Small Signal TransistorDocument2 pagesProcess: Small Signal TransistorVictor HemzNo ratings yet

- CP211Document2 pagesCP211Victor HemzNo ratings yet

- SLM360 Clamp BoltDocument1 pageSLM360 Clamp BoltTony CeNo ratings yet

- Armstrong - Manual Sprinkler SystemDocument78 pagesArmstrong - Manual Sprinkler SystemAvinash NathNo ratings yet

- 0121 Revo Mall Bekasi Lantai Ug - Serambi RasaDocument4 pages0121 Revo Mall Bekasi Lantai Ug - Serambi RasasuparmanNo ratings yet

- 218ID IPAL Subwoofer SystemDocument26 pages218ID IPAL Subwoofer Systemomarquisperojas100% (1)

- Dossier Teca A BDocument20 pagesDossier Teca A Bpeter2002No ratings yet

- Receptor HLSDocument2 pagesReceptor HLSWilder GomezNo ratings yet

- Simple Forward AC-DC Bom - ReportDocument11 pagesSimple Forward AC-DC Bom - ReportSwaminathan RajaramNo ratings yet

- Materal AbrilDocument3 pagesMateral Abriljuan castroNo ratings yet

- Inventario Stok de Sensores AlmacenDocument5 pagesInventario Stok de Sensores AlmacenLuis OjedaNo ratings yet

- CP283 NPN Power Transistor Process DetailsDocument1 pageCP283 NPN Power Transistor Process Detailszero cloudNo ratings yet

- Test Summary for Gas Scrubber Kit VSH2 Hard Plumbed (Mexico) ADocument3 pagesTest Summary for Gas Scrubber Kit VSH2 Hard Plumbed (Mexico) APaloma GarcíaNo ratings yet

- 30 07 2019Document7 pages30 07 2019Zubair MehmoodNo ratings yet

- Diy Sony Vfet Amplifier Os2-1Document9 pagesDiy Sony Vfet Amplifier Os2-1alex_81_No ratings yet

- Shutdown SIS Previous ScreenDocument2 pagesShutdown SIS Previous ScreenArmando Vara ChavezNo ratings yet

- SPARE Test - Station - IDocument35 pagesSPARE Test - Station - Ifatima cotryNo ratings yet

- Product DFGDDocument137 pagesProduct DFGDTanuj GhimireNo ratings yet

- 4 SQ MM Cu Armoured Cable 2.5 SQ MM Cu Armoured CableDocument4 pages4 SQ MM Cu Armoured Cable 2.5 SQ MM Cu Armoured Cablekoushik42000No ratings yet

- AGE Catalogue FebDocument56 pagesAGE Catalogue FebsitewebsaNo ratings yet

- Service Manual: Quality and Innovation Since 1963Document20 pagesService Manual: Quality and Innovation Since 1963Marcos MesquitaNo ratings yet

- GTC Materials ListDocument14 pagesGTC Materials ListRadulescu AndreiNo ratings yet

- Color TV Service Guide for DTQ-25G4FS and DTQ-29G4FS ModelsDocument7 pagesColor TV Service Guide for DTQ-25G4FS and DTQ-29G4FS Models77jacki77No ratings yet

- DS 8nhta-FDocument2 pagesDS 8nhta-FgrobedNo ratings yet

- Product Information Packet: 250HP, 3570RPM, 3PH, 60HZ, 449TS, 18104M, TEFCDocument9 pagesProduct Information Packet: 250HP, 3570RPM, 3PH, 60HZ, 449TS, 18104M, TEFCJosé Isaac Chávez HuamánNo ratings yet

- Technical Specifications: Enviropol Engineers Pvt. LTDDocument17 pagesTechnical Specifications: Enviropol Engineers Pvt. LTDArvind KumarNo ratings yet

- 3 Storey Stall SLDDocument3 pages3 Storey Stall SLDLAWRENCE KIM N. SACRISTANNo ratings yet

- Service Bulletin NO:07013-R2: Only TX-SR875/DTC-9.8/PR-SC885/TX-NR905/TX-NA905/DTR-8.8Document5 pagesService Bulletin NO:07013-R2: Only TX-SR875/DTC-9.8/PR-SC885/TX-NR905/TX-NA905/DTR-8.8dannysporeaNo ratings yet

- Customer Telma MG Site Id: DIA054 Telma Madagascar Site Name: Betsiaka Delivery Adress: Betsiaka Tel: Tel: Fax FaxDocument3 pagesCustomer Telma MG Site Id: DIA054 Telma Madagascar Site Name: Betsiaka Delivery Adress: Betsiaka Tel: Tel: Fax FaxPamela RatsimbazafyNo ratings yet

- Cabstrut Price List March 2014Document48 pagesCabstrut Price List March 2014maxmorekNo ratings yet

- lumitron_documentationDocument12 pageslumitron_documentationStani-Slav JanáčNo ratings yet

- LM2907 and LM2917 Frequency To Voltage Converter: FeaturesDocument42 pagesLM2907 and LM2917 Frequency To Voltage Converter: FeaturesHariman PurbaNo ratings yet

- Offerte CebeoDocument4 pagesOfferte CebeoBart De PauwNo ratings yet

- Prisma Illustrated Parts Manual 2002 Photo ViewDocument11 pagesPrisma Illustrated Parts Manual 2002 Photo ViewfernandomeiraNo ratings yet

- DS MP58 - 58T eDocument2 pagesDS MP58 - 58T eNirav PatelNo ratings yet

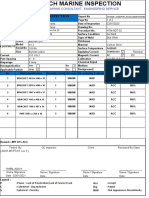

- Magnetic Particle Inspection: NDT Service - Marine Consultant - Engineering ServiceDocument4 pagesMagnetic Particle Inspection: NDT Service - Marine Consultant - Engineering ServiceSulthan HanifNo ratings yet

- 20-0 679 8254GCP Ashtart Revamping Project Rev Customer Specification No: Generator RatingDocument10 pages20-0 679 8254GCP Ashtart Revamping Project Rev Customer Specification No: Generator RatingKechaouNo ratings yet

- World Allergy Organization (WAO) :: Allergic Patients During COVID-19 PandemicDocument2 pagesWorld Allergy Organization (WAO) :: Allergic Patients During COVID-19 PandemicarjetaNo ratings yet

- mc7800 PDFDocument16 pagesmc7800 PDFsergeyNo ratings yet

- LDR DatasheetDocument4 pagesLDR DatasheetEmiliana Paez43% (7)

- Journal Pre-Proof: Microprocessors and MicrosystemsDocument29 pagesJournal Pre-Proof: Microprocessors and MicrosystemsarjetaNo ratings yet

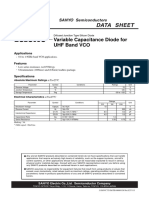

- EC2C03C: Variable Capacitance Diode For Uhf Band VcoDocument3 pagesEC2C03C: Variable Capacitance Diode For Uhf Band VcoarjetaNo ratings yet

- Rif Sensor PDFDocument2 pagesRif Sensor PDFarjetaNo ratings yet

- MKRGSM1400 SchematicDocument2 pagesMKRGSM1400 SchematicvijayforrockNo ratings yet

- Atmel Library Components ListDocument6 pagesAtmel Library Components ListAmey KulkarniNo ratings yet

- Analog Devices - by - Element14 - Batch - 1Document35 pagesAnalog Devices - by - Element14 - Batch - 1arjetaNo ratings yet

- Element14 Consolidated EAGLE CAD Library For Cirrus LogicDocument1 pageElement14 Consolidated EAGLE CAD Library For Cirrus LogicarjetaNo ratings yet

- ST Microelctronics by Element14 Batch 1Document9 pagesST Microelctronics by Element14 Batch 167409b5322No ratings yet

- VUSB board schematic diagramDocument2 pagesVUSB board schematic diagramluisNo ratings yet

- LDR DatasheetDocument4 pagesLDR DatasheetEmiliana Paez43% (7)

- EEG Signal Analysis and Classification: Siuly Siuly Yan Li Yanchun ZhangDocument257 pagesEEG Signal Analysis and Classification: Siuly Siuly Yan Li Yanchun ZhangarjetaNo ratings yet

- Handbook of Robotics Chapter 59: Robot Programming by DemonstrationDocument26 pagesHandbook of Robotics Chapter 59: Robot Programming by DemonstrationarjetaNo ratings yet