Professional Documents

Culture Documents

A B AND Nand OR NOR XOR Xnor NOT AND Nand OR NOR XOR Xnor NOT

Uploaded by

rabbystarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A B AND Nand OR NOR XOR Xnor NOT AND Nand OR NOR XOR Xnor NOT

Uploaded by

rabbystarCopyright:

Available Formats

Name: Student Number:

Bench Number: Group:

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 1

MARKS OBTAINED:

Circuit neatness (10)

Operation (1) (5)

Table (2) (10) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE

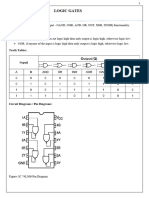

Verify all logic functions (AND, NAND, OR, NOR, XOR, XNOR and NOT) with pulsed operation using 2 I/P 74LS

series ICs.

The report will consist of this handout with the results filled in.

EQUIPMENT:

1 x Function generator 1 x Breadboard 1 x SN74LS04 2 x LEDs Green

1 x DC power supply 3 x Banana to crocodile cables 1 x SN74LS08 3 x LEDs Red

1 x Oscilloscope 3 x Banana to banana cables 1 x SN74LS32 2 x LEDs Yellow

1 x Multimeter 3 x BNC to crocodile cables 1 x SN74LS86 1 x 100 Resistor

PROCEDURE:

1. Build the circuit as shown below:

A B LED1

R1

IC1:A

IC4:A LED2

& Red 100R R2

1

Red 100R

74LS04 LED3

74LS08 R3

IC2:A

IC4:B LED4

1 Yellow 100R R4

1

Yellow 100R

74LS04 LED5

74LS32 R5

IC3:A

IC4:C LED6

=1 Green 100R R6

1

Green 100R

74LS04

74LS86

IC4:D LED7

R7

1

Red 100R

74LS04

REMEBER TO CONNECT ALL ICs TO VCC (+5 V) AND GROUND

L1-11

2. Complete the table below:

I/P EXPECTED O/P OBSERVED O/P

A B AND NAND OR NOR XOR XNOR NOT AND NAND OR NOR XOR XNOR NOT

0 0 0 1 0 1 0 1 1 0 1 0 1 0 1 1

0 1 0 1 1 0 1 0 1 0 1 1 0 1 0 1

1 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0

1 1 1 0 1 0 0 1 0 1 0 1 0 0 1 0

3. Compare the expected outputs with the observed outputs in the truth tables.

Determine and discuss the cause if there is a discrepancy between the expected outputs and the observed outputs.

No discrepancy

497597039.doc Page 1 of 19 03 November 2020

Name: Emanuel D N Student Number: 217151620

Bench Number: Group: 35 BELL

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 2

MARKS OBTAINED:

Circuit neatness (5)

Table (1) (5)

Karnaugh (2) (5)

Boolean equations (3) (4)

Diagram drawing (4) (6) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE

Design and build an encoder using logic gates. (Every student will be assigned one of the encoders to design.)

PROJECT SPECIFICATIONS

Binary to 2421 BCD

Binary to XS3 BCD

Binary to 5321 BCD

Binary to 842 1 BCD

The report will consist of this handout with the results filled in.

EQUIPMENT:

1 x Function generator 1 x Multimeter 3 x Banana to banana cables IC's determined by design

1 x DC power supply 1 x Breadboard 3 x BNC to crocodile cables 1 x 100 Resistor

1 x Oscilloscope 3 x Banana to crocodile cables 4 x LEDs

PROCEDURE:

Design the circuit using truth tables, Karnaugh mapping and Boolean algebra rules, laws and theorems:

1. Complete the tables below.

I/P EXPECTED O/P OBSERVED O/P

Dec

A B C D w x y z W X Y Z

0 0 0 0 0 0 0 0 0 0 0 0 0

1 0 0 0 1 0 0 0 1 0 0 0 1

2 0 0 1 0 0 0 1 0 0 0 1 0

3 0 0 1 1 0 0 1 1 0 0 1 1

4 0 1 0 0 0 1 0 0 0 1 0 0

5 0 1 0 1 1 0 1 1 1 0 1 1

6 0 1 1 0 1 1 0 0 1 1 0 0

7 0 1 1 1 1 1 0 1 1 1 0 1

8 1 0 0 0 1 1 1 0 1 1 1 0

9 1 0 0 1 1 1 1 1 1 1 1 1

10 1 0 1 0 x x x x x x x x

11 1 0 1 1 x x x x x x x x

12 1 1 0 0 x x x x x x x x

13 1 1 0 1 x x x x x x x x

14 1 1 1 0 x x x x x x x x

15 1 1 1 1 x x x x x x x x

497597039.doc Page 2 of 19 03 November 2020

2. Complete the Karnaugh maps below:

AB AB AB AB AB AB AB AB

CD 0 0 X 1 0 1 X 1

3. Boolean Equations

CD 0 1 X 1 0 X X 1

W = A + BD + BC

CD 0 1 X X 0 1 X X

X = A + BD + BC

CD 0 1 X X 0 1 X X Y = A BCD B C

Z=D

4. Draw the Logic Diagram:

CD 0 0 X 1 0 0 0 0

CD 0 1 X 1 1 1 X 1

CD 1 0 X X 1 1 X X

CD 1 0 X X 0 0 0 0

A B CD

IC2:A

W

1 2

IC1:A IC4:D D1

74LS04 1 IC4:A 12

R1

3 1 11

2 & 3 13 1

2 1 LED

100

IC2:B 74LS08 74LS32 GREEN

74LS32

3 4

IC1:B

X

74LS04

4

6

5 &

IC5:A D2

74LS08

IC4:B 1

R2

IC1:C 4 3

IC2:C 9 6 2 1

8 5 1 LED

100

5 6 10 & 74LS32 RED

74LS32

74LS08

74LS04

D3

12

IC1:D

IC4:C 4

IC5:B

Y R3

11 9 6

13 & 8 5 1

10 1 LED

100

74LS08 74LS32 YELLOW

74LS32

IC3:A

1

D4

Z

2 12

13 &

74LS11

R4

100

LED

ORANGE

5. Compare the expected outputs with the observed outputs in the truth tables.

Determine and discuss the cause if there is a discrepancy between the expected outputs and the observed outputs.

No discrepancy

497597039.doc Page 3 of 19 03 November 2020

Name: EMANUEL D N Student Number: 217151620

Bench Number: Group: 35 BELL

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 3

MARKS OBTAINED:

Circuit Nnatness (5)

Table (1) (5)

Karnaugh (2) (5)

Boolean equations (3) (4)

Diagram drawing (4) (6) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE:

Design, build and verify the operation of a Full-Subtractor.

The report will consist of this handout with the results filled in.

EQUIPMENT:

1 x Function generator 1 x Breadboard 1 x 74LS04 1 x LED Yellow

1 x DC power supply 3 x Banana to crocodile cables 1 x 74LS08 1 x LED Red

1 x Oscilloscope 3 x Banana to banana cables 1 x 74LS32 1 x 100 Resistor

1 x Multimeter 3 x BNC to crocodile cables 1 x 74LS86

PROCEDURE:

Design the circuit using truth tables, Karnaugh mapping and Boolean algebra rules, laws and theorems as follows:

1. Complete the table below.

I/P EXPECTED OBSERVED

Dec A B C O/P O/P

A B Bi D Bo D Bo

0

2. Complete the Karnaugh maps below and simplify:

D AB AB AB AB AB AB AB AB Bo

C

C

3. Complete the Boolean equations

D

Bo

497597039.doc Page 4 of 19 03 November 2020

4. Draw the logic diagram:

A B C

IC1:A

1

=1 3

IC1:B D1

2

4

74LS86 6

R1

5 =1 100

LED

74LS86 RED

IC3:A

1

2 & 3

IC2:A 74LS08

1 2 IC4:A D2

IC3:B 1 IC4:B

4 3 4 R2

1

74LS04

5 & 6 2

5 1 6

100

74LS32 LED

74LS08 74LS32 YELLOW

IC3:C

9

8

10 &

74LS08

497597039.doc Page 5 of 19 03 November 2020

5. Compare the expected outputs with the observed outputs in the truth tables.

Determine and discuss the cause if there is a discrepancy between the expected outputs and the observed outputs.

497597039.doc Page 6 of 19 03 November 2020

Name: Student Number:

Bench Number: Group:

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 4

MARKS OBTAINED:

Circuit neatness (6)

Truth table (1) (5)

Simplification Boolean (3) (2)

Simplification Karnaugh (3) (2)

Drawing circuit (4) (6)

Operation circuit 1 (5) (2)

Operation circuit 2 (5) (2) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE

To investigate how an 8-input multiplexer can be used to generate a 4 variable function.

The report will consist of this handout with the results filled in.

EQUIPMENT:

1 x Function generator 1 x Breadboard 2 x SN74LS04 1 x SN74LS151

1 x DC power supply 3 x Banana to crocodile cables 1 x SN74LS11 3 x LEDs Red

1 x Oscilloscope 3 x Banana to banana cables 1 x SN74LS21 2 x LEDs Green

1 x Multimeter 3 x BNC to crocodile cables 1 x SN74LS32 2 x 100 Resistor

PROCEDURE:

1. Build logic circuits to implement the function F(A, B, C, D) = Σ(1, 4, 7, 8, 9, 12, 14, 15) using:

74LS151 multiplexer IC

logic gates

A B C D F

0 0 0 0

F ? ABC ???

0 0 0 1 2

0 0 1 0

F ? ABC ???

2

0 0 1 1

0 1 0 0

F ? ABC ???

2

0 1 0 1

0 1 1 0

F ? ABC ???

2

0 1 1 1

1 0 0 0

F ? ABC ???

2

1 0 0 1

1 0 1 0

F ? ABC ???

2

1 0 1 1

1 1 0 0

F ? ABC ???

2

1 1 0 1

1 1 1 0

F ? ABC ???

2

1 1 1 1

2. Simplify the function using Boolean algebra.

497597039.doc Page 7 of 19 03 November 2020

3. Simplify the function using a Karnaugh map.

F AB AB AB AB

CD

CD

CD

CD

3. Draw the 2 logic diagrams using the same inputs.

4. Build the logic circuits and verify that their outputs are the same.

497597039.doc Page 8 of 19 03 November 2020

Name: Student Number:

Bench Number: Group:

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 5

MARKS OBTAINED:

Circuit neatness (5)

Table (2) (4)

Answer (2.2) (1)

Table (3) (14)

Answer (3.1) (1) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE:

Verify the operation of a JK flip-flop.

EQUIPMENT AND COMPONENTS NEEDED:

1 x Function generator 1 x Breadboard 1 x LED Yellow 1 x 470 Ω Resistor

1 x DC power supply 3 x Banana to crocodile cables 1x LED Green 4 x 1 kΩ Resistors

1 x Oscilloscope 3 x Banana to banana cables 1 x LED Red 1 x 4-SPST Dip-switch

1 x Multimeter 3 x BNC to crocodile cables 1 x 74LS76A

PROCEDURE

1. Construct the circuit as shown below.

+5 V

R2

R3

R1

R4

1k

1k

1k

1k

SW1A IC1:A LED1

PRE

J red

SW1B

C

LED2

K

CLR

SW1C yellow

74LS76A

470R

R5

SW1D

CLK I/P

L4-1-11

2. By changing the synchronous inputs (J & K), determine the outputs (Q & Q ) while the asynchronous

inputs ( PRESET & CLEAR ) are inactive (HIGH).

EXPECTED OBSERVED

INPUTS

O/P O/P

J K PRE CLR CLK Q Q Q Q

0 0 1 1 ↓

0 1 1 1 ↓

1 0 1 1 ↓

1 1 1 1 ↓

2.1 Compare the expected outputs with the observed outputs in the truth tables.

Determine and discuss the cause if there is a discrepancy between the expected outputs and the observed outputs.

2.2 When does data transfer occurs?

EXPECTED OBSERVED

497597039.doc Page 9 of 19 03 November 2020

3. By changing the asynchronous inputs ( PRESET & CLEAR ), determine the outputs (Q & Q ) while the synchronous

inputs (J & K) are don’t cares (HIGH or LOW). Do not apply a clock pulse.

EXPECTED OBSERVED

PRE CLR J K O/P O/P

Q Q Q Q

0 0 x x

0 1 x x

1 0 x x

1 1 x x

3.1 When does output change with a change at the asynchronous inputs?

EXPECTED OBSERVED

3.2 Compare the expected outputs with the observed outputs in the truth tables.

Determine and discuss the cause if there is a discrepancy between the expected outputs and the observed outputs.

497597039.doc Page 10 of 19 03 November 2020

Name: Student Number:

Bench Number: Group:

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 6

MARKS OBTAINED:

Circuit neatness (10)

Table (2) (-3 marks for mistake) (10)

Table (3) (-3 marks for mistake) (5) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE:

Verify the frequency division characteristics of the JK flip-flop in the toggle mode.

EQUIPMENT AND COMPONENTS NEEDED:

1 x Function generator 1 x Breadboard 1 x 74LS76A 2 x 470 Ω Resistors

1 x DC power supply 3 x Banana to crocodile cables 1 x LED Yellow 4 x 1 kΩ Resistors

1 x Oscilloscope 3 x Banana to banana cables 1 x LED Green 1 x 4-SPST Dip-switch

1 x Multimeter 3 x BNC to crocodile cables 1 x LED Red

PROCEDURE

1. Construct the circuit as shown below and set the J, K, PRESET and CL EAR inputs.

+5 V

R1

R2

R3

R4

1k

1k

1k

1k

S1 IC1:A LED1

PRE

J Red

S2

C

LED2

K

CLR

S3 Yellow

74LS76A

470R

R5

5 V, 0,5 Hz

S4

E1

470R

R6

Green

LED3

L5-1-11

2. Determine the outputs Q and Q with the PRESET and CLEAR inputs HIGH.

EXPECTED OBSERVED

fCLK/Hz

FQ/Hz

2.1 Compare the expected outputs with the observed outputs in the truth tables.

Determine and discuss the cause if there is a discrepancy between the expected outputs and the observed outputs.

3. Determine the duty cycle of the output compared to the clock input, in toggle mode.

EXPECTED OBSERVED

% Duty Cycle

4. Compare the expected outputs with the observed outputs in the truth tables.

Determine and discuss the cause if there is a discrepancy between the expected outputs and the observed outputs.

497597039.doc Page 11 of 19 03 November 2020

Name: Student Number:

Bench Number: Group:

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 7

MARKS OBTAINED:

Circuit neatness (5)

Table (3) (-3 marks for mistake) (5)

Graph (4) (-3 marks for mistake) (15) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE:

Measure propagation delay of a digital circuit (JK flip-flop).

EQUIPMENT AND COMPONENTS NEEDED:

1 x Function generator 1 x Multimeter 3 x Banana to banana cables 1 x 400 Ω Resistor

1 x DC power supply 1 x Breadboard 3 x BNC to crocodile cables 1 x 1 kΩ Resistor

1 x Oscilloscope 3 x Banana to crocodile cables 1 x 74LS76A

PROCEDURE

1. Construct the circuit as shown below.

+5 V

R1

1k

Channel 1

PRE

E1 J

C

5V 1 MHz K Channel 2

400R

RL

CLR

L6-1-11

2. Using method described below and measure tPLH. Compare it with the data sheet's specified maximum time.

To Measure tPLH and tPHL :

Trigger the scope form channel 2

Set trigger slope to negative triggering to measure tPLH, and to positive triggering to measure tPHL

Set the time base selector on 0,2 μs/div

Do not activate alternate triggering

Centre the two waveforms along the centre gradicule of the scope

Increase the time based setting to 0,1 μs/div

Activate the x 10 button

Measure the time (tPLH) form the 50% point of the trailing edge of the clock pulse to the 50% point

on the rising edge of the output pulse

3. Complete the table:

EXPECTED OBSERVED

(Range from Texas Instrument data sheet)

tPHL/ns

(Range from Texas Instrument data sheet)

tPLH/ns

497597039.doc Page 12 of 19 03 November 2020

4. Draw the observed input and output waveforms on the same axes.

5. Compare the expected outputs with the observed outputs in the truth tables. (Determine and discuss the cause if there is a

discrepancy between the expected outputs and the observed outputs.)

497597039.doc Page 13 of 19 03 November 2020

Name: Student Number:

Bench Number: Group:

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 8

MARKS OBTAINED:

Circuit neatness (9)

Table (3) (-3 marks for mistake) (16) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE:

Verify the operation of a 74LS195 shift register used as a serial in/serial out shift register.

EQUIPMENT AND COMPONENTS NEEDED:

1 x Function generator 1 x Breadboard 1 x 74LS195A 5 x 1 kΩ Resistors

1 x DC power supply 3 x Banana to crocodile cables 1 x 74LS279 1 x 4-SPST Dip-switches

1 x Oscilloscope 3 x Banana to banana cables 1 x LED 1 x SPDT switch

1 x Multimeter 3 x BNC to crocodile cables 1 x 470 Ω Resistor

PROCEDURE

1. Construct the circuits as shown below:

+5 VCC

1K

1K

1K

1K

1K

R1

R2

R3

R4

R5

SW1A

SW1B IC1

2

J SRG 4

3

K

SW1C 9

SH/LD

1

CLR

10 11 LED4

C Q3

IC2:B 7 12

D3 Q3

SW2 6 13 Q3

S D2 Q2

6 7 5 14

Q D1 Q1

470R

R6

4 15

R D0 Q0

5

74LS279

74LS195A L7-1a-06

2. Complete the table:

EXPECTED O/P OBSERVED O/P

CLK SH/LD CLR SERIAL I/P

Q3 Q3

- 1 0 -

1 1 1 1

2 1 1 0

3 1 1 1

4 1 1 1

5 1 1 X

6 1 1 X

7 1 1 X

497597039.doc Page 14 of 19 03 November 2020

Name: Student Number:

Bench Number: Group:

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 9

MARKS OBTAINED:

Circuit neatness (10)

Table (2) (-2 marks for mistake) (15) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE:

Verify the operation of a 74LS195 shift register used as a serial in/parallel out shift register.

EQUIPMENT AND COMPONENTS NEEDED:

1 x Function generator 1 x Breadboard 1 x 74LS08 1 x 470 Ω Resistor

1 x DC power supply 3 x Banana to crocodile cables 1 x 74LS195A 6 x 1 kΩ Resistors

1 x Oscilloscope 3 x Banana to banana cables 1 x 74LS279 1 x 4-SPST Dip-switches

1 x Multimeter 3 x BNC to crocodile cables 4 x LEDs 1 x SPDT Switch

PROCEDURE

1. Construct the circuits as shown below:

+5 VCC

1K

1K

1K

1K

1K

1K

R1

R2

R3

R4

R5

R6

SW1A IC2:A

& LED5

1 3

Parallel O/P Control

SW1B Q3

2

74LS08

IC2:B

IC1 LED3

SW1C &

4

2

J SRG 4 6

3 Q2

K

5

9

SW1D SH/LD 74LS08

1 IC2:C

CLR

IC3:B 10 11 & LED2

C Q3

SW2 7 12 9 8

S D3 Q3

6 7 6 13 Q1

Q D2 Q2

10

5 14

R D1 Q1 74LS08

5 4 15 IC2:D

74LS279 D0 Q0

& LED1

12

74LS195A 11

Q0

13

74LS08

470R

R7

L8-1a-06

2. Complete the table:

PARALLEL O/P SERIAL EXPECTED O/P OBSERVED O/P

CLK CLR SH/LD

CONTROL I/P Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0

- 0 1 0 -

1 1 1 0 1

2 1 1 0 1

3 1 1 0 0

4 1 1 0 1

- 1 1 1 -

497597039.doc Page 15 of 19 03 November 2020

Name: Student Number:

Bench Number: Group:

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 10

MARKS OBTAINED:

Circuit neatness (10)

Table (2) (-3 marks for mistake) (15) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE:

Verify the operation of a 74LS195 shift register used as a parallel in/serial out shift register.

EQUIPMENT AND COMPONENTS NEEDED:

1 x Function generator 1 x Breadboard 1 x 74LS08 1 x 470 Ω Resistor

1 x DC power supply 3 x Banana to crocodile cables 1 x 74LS195A 6 x 1 kΩ Resistors

1 x Oscilloscope 3 x Banana to banana cables 1 x 74LS279 1 x 4-SPST Dip-switches

1 x Multimeter 3 x BNC to crocodile cables 4 x LEDs 1 x SPDT Switch

PROCEDURE

1. Construct the circuits as shown below:

+5 VCC

R1

R2

R3

R5

R7

R9

1K

1K

1K

1K

1K

1K

SW1A

R10

R4

R6

R8

1K

1K

1K

1K

SW1B IC1

SW1C

2

J SRG 4

3

K

9

SW1D SH/LD

1

CLR

10 11 LED4

SW2A C Q3

7 12

D3 Q3

6 13 Q3

SW2B D2 Q2

5 14

D1 Q1

470R

R11

4 15

SW2C D0 Q0

SW2D

74LS195A

IC3:B

SW3

S

6 7

Q

R

5

L9-1a-06

74LS279

2. Complete the table.

PARALLEL I/P EXPECTED O/P OBSERVED O/P

CLK SH/LD CLR

D3 D2 D1 D0 Q3 Q3

- 1 0 - - - -

1 0 1 1 1 1 0

2 1 1 - - - -

3 1 1 - - - -

4 1 1 - - - -

497597039.doc Page 16 of 19 03 November 2020

Name: Student Number:

Bench Number: Group:

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 11

MARKS OBTAINED:

Circuit neatness (10)

Table (2) (-3 marks for mistake) (15) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE:

Verify the operation of a 74LS195 shift register used as a parallel in/parallel out shift register.

EQUIPMENT AND COMPONENTS NEEDED:

1 x Function generator 1 x Breadboard 1 x 74LS08 1 x 470 Ω Resistor

1 x DC power supply 3 x Banana to crocodile cables 1 x 74LS195A 6 x 1 kΩ Resistors

1 x Oscilloscope 3 x Banana to banana cables 1 x 74LS279 1 x 4-SPST Dip-switches

1 x Multimeter 3 x BNC to crocodile cables 4 x LEDs 1 x SPDT Switch

PROCEDURE

1. Construct the circuits as shown below:

+5 VCC

1K

1K

1K

1K

1K

R1

R3

R5

R7

R9

SW1A

IC2:A

Parallel O/P Control & LED4

1

3

R10

1K

1K

1K

1K

1K

R2

R4

R6

R8

Q3

2

SW1B IC1 74LS08

IC2:B

SW1C

2

J SRG 4 & LED3

3 4 6

K

9 Q2

SW1D SH/LD

1 5

CLR 74LS08

10 11 IC2:C

SW2A C Q3

7 12 & LED2

D3 Q3

9

6 13 8

SW2B D2 Q2

5 14 Q1

D1 Q1

4 15 10

SW2C D0 Q0 74LS08

IC2:D

SW2D

74LS195A & LED1

12 11

IC3:B Q0

13

SW3

S 74LS08

6

7

Q

470R

R11

R

5

74LS279 L10-1a-06

2. Complete the table.

PARALLEL PARALLEL I/P EXPECTED O/P OBSERVED O/P

CLK SH/LD O/P CLR D3 D2 D1 D0 Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0

CONTROL

1 0 0 - - - -

1 0 0 1 1 1 1 0

1 1 1 - - - -

497597039.doc Page 17 of 19 03 November 2020

Name: Student Number:

Bench Number: Group:

DIGITAL ELECTRONICS 1 LABORATORY ASSIGNMENT 12

MARKS OBTAINED:

Circuit neatness (5)

Logic diagram (1) (5)

Table (3) (5)

Timing diagram exp. (4) (5)

Timing diagram obs. (4) (5) MODERATOR SIGNATURE

Penalties (-x)

Total marks [25] Total %

OBJECTIVE:

Construct and verify the operation of decade counter using two 74LS76 (J-K flip-flop) integrated circuits.

EQUIPMENT AND COMPONENTS NEEDED:

1 x Function generator 1 x Breadboard 1 x 74LS00 1 x SPST Switch

1 x DC power supply 3 x Banana to crocodile cables 2 x 74LS76A

1 x Oscilloscope 3 x Banana to banana cables 4 x LEDs

1 x Multimeter 3 x BNC to crocodile cables 4 x 1 kΩ Resistor (Current limiting for LEDs)

PROCEDURE

1. Draw the circuit diagram of a decade counter using negative edge-triggered flip-flops. The circuit must make provision to clear

the counter.

2. Construct the circuit and set the clock input’s frequency to 0,5 Hz.

3. Complete the table:

EXPECTED OBSERVED

CLK

PULSE NO. CLR

Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0

0

1 1

2 1

3 1

4 1

5 1

6 1

7 1

8 1

9 1

10 1

497597039.doc Page 18 of 19 03 November 2020

4. Draw the expected timing diagram and then use the observed table to draw the observed timing diagram.

EXPECTED

1 2 3 4 5 6 7 8 9 10

1

CLK

0

1

CLR

0

1

Q0

0

1

Q1

0

1

Q2

0

1

Q3

0

L6-1-04c

Decoder 1

o/p 0

OBSERVED

1 2 3 4 5 6 7 8 9 10

1

CLK

0

1

CLR

0

1

Q0

0

1

Q1

0

1

Q2

0

1

Q3

0

L6-1-04c

Decoder 1

o/p 0

5. Compare the expected outputs with the observed outputs.

497597039.doc Page 19 of 19 03 November 2020

You might also like

- Multiplexers and Demultiplexers: Experiment - VDocument9 pagesMultiplexers and Demultiplexers: Experiment - VRuchira Kasun WeerasingheNo ratings yet

- Title: Decoder Instruction AimsDocument4 pagesTitle: Decoder Instruction Aimssuv_fameNo ratings yet

- Laboratory Manual Course Code:Ece 201Document41 pagesLaboratory Manual Course Code:Ece 201Atul SainiNo ratings yet

- How To Make A Police Style Strobe Light CircuitDocument3 pagesHow To Make A Police Style Strobe Light Circuittim schroderNo ratings yet

- Lab 2 - Flip Flops and CountersDocument27 pagesLab 2 - Flip Flops and CountersHoang Dung SonNo ratings yet

- DLD Lab ManualDocument109 pagesDLD Lab ManualAnwar JahanNo ratings yet

- Logic Design Lab ManualDocument22 pagesLogic Design Lab ManualAzarkhan Mokashi100% (1)

- DLD Equipment ListDocument6 pagesDLD Equipment Listmuhammad.shahrukhNo ratings yet

- Roll-Up, Roll-Up!: Win A Pico PC-Based OscilloscopeDocument3 pagesRoll-Up, Roll-Up!: Win A Pico PC-Based Oscilloscopesuperser123465No ratings yet

- Introduction To Electronic Circuits Activity SheetDocument4 pagesIntroduction To Electronic Circuits Activity SheetDarwin TacubanzaNo ratings yet

- Lab BookDocument216 pagesLab BookrkNo ratings yet

- Lab 10 2022 2Document4 pagesLab 10 2022 2CuongNo ratings yet

- Title:Implementation of 4-Line-To - 2-Line Encoder & 8-Line-To-3-Line Encoder Lab Worksheet #10Document5 pagesTitle:Implementation of 4-Line-To - 2-Line Encoder & 8-Line-To-3-Line Encoder Lab Worksheet #10MUNEEB SHAHNo ratings yet

- Exp3 Universal Gates 1Document23 pagesExp3 Universal Gates 1Joie Marie Yadao BulawanNo ratings yet

- Solutions Manual Digital Systems Principles Applications 11th Edition Tocci PDFDocument10 pagesSolutions Manual Digital Systems Principles Applications 11th Edition Tocci PDFTariqul Hasan0% (2)

- Design of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerDocument11 pagesDesign of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerPranav Satish0% (1)

- Design of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerDocument11 pagesDesign of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerPranav Satish100% (1)

- Introduction To Electronic Circuits Activity SheetDocument4 pagesIntroduction To Electronic Circuits Activity SheetDarwin TacubanzaNo ratings yet

- DCD Mini ProjectDocument17 pagesDCD Mini ProjectPooja KarandeNo ratings yet

- Sample Lab ReportDocument6 pagesSample Lab ReportJames WilsonNo ratings yet

- DS - Expt 9Document3 pagesDS - Expt 9Aditya SalunkheNo ratings yet

- De Lab PDFDocument36 pagesDe Lab PDFNaveen Yallapu100% (1)

- Warmly Welcome From My PresentationDocument59 pagesWarmly Welcome From My PresentationPrinces Ofattacker100% (4)

- 15ecl48 VTU Raghudathesh R 2r DacDocument5 pages15ecl48 VTU Raghudathesh R 2r Dacraghudatheshgp100% (1)

- 15ecl48-VTU-raghudathesh-r 2r Dac PDFDocument5 pages15ecl48-VTU-raghudathesh-r 2r Dac PDFraghudatheshgpNo ratings yet

- Safety Guard Circuit Diagram and InstructionsDocument1 pageSafety Guard Circuit Diagram and InstructionsSirJones KekapohNo ratings yet

- DSD Project Name Abstract Quiz DisplayDocument2 pagesDSD Project Name Abstract Quiz DisplayNaveen KumarNo ratings yet

- ETU 07322 - Digital Electronic Lab ManualDocument33 pagesETU 07322 - Digital Electronic Lab ManualFrancis LubangoNo ratings yet

- Ic TesterDocument3 pagesIc TesterSabarinath HaridasNo ratings yet

- Digital DiceDocument3 pagesDigital DicechakralabsNo ratings yet

- Digital Electronics Lab EE-224-FDocument48 pagesDigital Electronics Lab EE-224-FIshwar Singh ChandraNo ratings yet

- Ic Lab AllDocument45 pagesIc Lab AllRaghu KasulaNo ratings yet

- Analog and Digital Circuits Complete Mannual 2013Document123 pagesAnalog and Digital Circuits Complete Mannual 2013EASACOLLEGENo ratings yet

- Hardware Lab-I: (CS-217) Instruction ManualDocument36 pagesHardware Lab-I: (CS-217) Instruction Manualmaen2009No ratings yet

- Elec 2210 - Experiment 1 Basic Digital Logic Circuits: ObjectivesDocument5 pagesElec 2210 - Experiment 1 Basic Digital Logic Circuits: ObjectivesSameer IbrahimNo ratings yet

- EET 1131 Lab - Latches and Flip-Flops OperationDocument9 pagesEET 1131 Lab - Latches and Flip-Flops OperationAtija LihićNo ratings yet

- Data Hasil Percobaan: Tabel 6.1. Rangkaian Encoder 8 To 3Document2 pagesData Hasil Percobaan: Tabel 6.1. Rangkaian Encoder 8 To 3fardanNo ratings yet

- Expt 1Document9 pagesExpt 1PRINCESS JAMIE ARAH GALIASNo ratings yet

- Led Theo NhacDocument16 pagesLed Theo NhacNguyễn Thắng LợiNo ratings yet

- Deep Blue DelayDocument18 pagesDeep Blue DelayGasa RafliNo ratings yet

- Lab 9 Encoders And DecodersDocument7 pagesLab 9 Encoders And Decoderssafdarmunir070No ratings yet

- Proposed Laboratory Tool Kit For CPE107LDocument3 pagesProposed Laboratory Tool Kit For CPE107LArete JinseiNo ratings yet

- BCD AdderDocument9 pagesBCD Addersnehaa30.01.2005No ratings yet

- 1.logic GatesDocument2 pages1.logic Gatesregihih589No ratings yet

- Components ListDocument6 pagesComponents ListRiddhi ThakkerNo ratings yet

- Title: Encoder Instructional AimsDocument7 pagesTitle: Encoder Instructional Aimssuv_fame100% (4)

- DLD Lab 1 - Logic GatesDocument8 pagesDLD Lab 1 - Logic GatesTenkuu No AbarebouNo ratings yet

- NE-3102: Electronics-II Laboratory: Name of The ExperimentDocument8 pagesNE-3102: Electronics-II Laboratory: Name of The ExperimentK.M. Hasan [Maruf]No ratings yet

- Ic DigitalDocument16 pagesIc DigitalRajashekar ReddyNo ratings yet

- Lab Manual LIC&C 2017-18Document40 pagesLab Manual LIC&C 2017-18Arun UpadhyayaNo ratings yet

- Electrical Circuits and Systems II LaboratoryDocument4 pagesElectrical Circuits and Systems II Laboratoryluis diaz contreraNo ratings yet

- Realize Logic Gates and Flip-Flops Lab ManualDocument62 pagesRealize Logic Gates and Flip-Flops Lab Manualअंकित अनुरागNo ratings yet

- 4.multiplexer & DemultiplexerDocument3 pages4.multiplexer & DemultiplexerSudhan HariNo ratings yet

- DLD Lab ManualDocument101 pagesDLD Lab ManualHamza100% (1)

- LED ChaserDocument11 pagesLED ChaserRavindran MahadevanNo ratings yet

- LED ChaserDocument11 pagesLED ChaserRavindran Mahadevan100% (1)

- Realization of Boolean Functions Using Gates and ICsDocument16 pagesRealization of Boolean Functions Using Gates and ICsPraveen TPNo ratings yet

- ILERDDS V2.1 Manual EnglishDocument26 pagesILERDDS V2.1 Manual EnglishFrugiMeNo ratings yet

- Experiment 10: Understanding Shift RegistersDocument5 pagesExperiment 10: Understanding Shift RegistersCharan MandapakaNo ratings yet

- WiremensDocument1 pageWiremensrabbystarNo ratings yet

- Seminar Paper.Document8 pagesSeminar Paper.rabbystarNo ratings yet

- Fuse CalculationsDocument1 pageFuse CalculationsrabbystarNo ratings yet

- Fuse CalculationsDocument1 pageFuse CalculationsrabbystarNo ratings yet

- Electrical Machines LabDocument8 pagesElectrical Machines LabrabbystarNo ratings yet

- Name: IITA J.S Student Number: 214047547 Bench Number: A4 Group: 35BELL Electronics 2 Laboratory Assignment 1 Marks ObtainedDocument37 pagesName: IITA J.S Student Number: 214047547 Bench Number: A4 Group: 35BELL Electronics 2 Laboratory Assignment 1 Marks ObtainedrabbystarNo ratings yet

- Construction Cost Estimate Worksheet AppendixDocument2 pagesConstruction Cost Estimate Worksheet AppendixVenkatesh SankarNo ratings yet

- Lighting Standards - Owen ManleyDocument11 pagesLighting Standards - Owen ManleyShaip DautiNo ratings yet

- UNIT 2 K MappingDocument31 pagesUNIT 2 K MappingtoshgangwarNo ratings yet

- PG TRB Computer Teachers Care AcademyDocument97 pagesPG TRB Computer Teachers Care AcademyAgnes ElaarasuNo ratings yet

- Hazard and GlitchesDocument22 pagesHazard and GlitcheskumarbsnspNo ratings yet

- 4 - Boolean Logic DesignDocument22 pages4 - Boolean Logic DesignnghiemnguyenNo ratings yet

- ELEX MCQ-Digital Systems - Principles and ApplicationsDocument253 pagesELEX MCQ-Digital Systems - Principles and ApplicationsJohnPatrickRamirezCuevasNo ratings yet

- A.V.C.College of Engineering Mannampandal, Mayiladuthurai-609 305Document111 pagesA.V.C.College of Engineering Mannampandal, Mayiladuthurai-609 305Laks Sadeesh100% (1)

- Engr250lecture PDFDocument227 pagesEngr250lecture PDFRafaelMontalvoNo ratings yet

- Question Bank Binary Decimal ConversionDocument9 pagesQuestion Bank Binary Decimal ConversionEslam QazamelNo ratings yet

- Digital 16 Marks.Document4 pagesDigital 16 Marks.Saranya PrabhuNo ratings yet

- PW 2 WithanswershetDocument12 pagesPW 2 WithanswershetAiman 4444No ratings yet

- Lesson 1 - Signals: SignalDocument119 pagesLesson 1 - Signals: SignalReggie PalaganasNo ratings yet

- Dr.N.G.P. Institute's EC2203 Digital Electronics Two Mark QuestionsDocument30 pagesDr.N.G.P. Institute's EC2203 Digital Electronics Two Mark Questionskarthimegs100% (1)

- B.SC (CS) Real SyllabusDocument75 pagesB.SC (CS) Real SyllabusPeaky BlindersNo ratings yet

- DLD Unit Wise Imp Q'sDocument13 pagesDLD Unit Wise Imp Q'spaavanmokshaNo ratings yet

- Maths - A.J. Sheriffdeen DM (NC38988)Document90 pagesMaths - A.J. Sheriffdeen DM (NC38988)ahmedNo ratings yet

- Project Date of BirthDocument3 pagesProject Date of BirthShafin ZamanNo ratings yet

- New-R20 Syllabus-Upto-4th Semester-25-04-2020Document45 pagesNew-R20 Syllabus-Upto-4th Semester-25-04-2020viju001No ratings yet

- Digital Logic: William Stallings, Computer Organization and Architecture, 9 EditionDocument24 pagesDigital Logic: William Stallings, Computer Organization and Architecture, 9 EditionVũ Tâm MinhNo ratings yet

- Model Paper - B.Tech - DLD (II-I CAD)Document2 pagesModel Paper - B.Tech - DLD (II-I CAD)chikkam bala sameerNo ratings yet

- Digital Logic Design Syllabus EEEg3141Document4 pagesDigital Logic Design Syllabus EEEg3141chalaNo ratings yet

- Objective Questions. Topic: Number System and CodesDocument56 pagesObjective Questions. Topic: Number System and Codesthejareddy14No ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Gate-Level Minimization Using Boolean Algebra and Karnaugh MapsDocument48 pagesGate-Level Minimization Using Boolean Algebra and Karnaugh MapsAbaid UllahNo ratings yet

- DPSD (2 Marks)Document79 pagesDPSD (2 Marks)Kalai Selvan100% (2)

- Discrete Mathematics - OdtDocument20 pagesDiscrete Mathematics - OdtAhmedbacha Abdelkader100% (1)

- Logic GateDocument37 pagesLogic GateAkihiko Jiraiya NelvinNo ratings yet

- Naveen Chandra 191b167 Dsm-LabsDocument36 pagesNaveen Chandra 191b167 Dsm-LabsNoori KhokharNo ratings yet

- DDE 1313 Digital Electronics 1 LODocument6 pagesDDE 1313 Digital Electronics 1 LOAhmad FadzlyNo ratings yet

- Digital Fundamentals: FloydDocument21 pagesDigital Fundamentals: FloydadilNo ratings yet

- German Malaysian Institute Department of Industrial ElectronicDocument11 pagesGerman Malaysian Institute Department of Industrial ElectronicZam ZamNo ratings yet