Professional Documents

Culture Documents

Design and Implementation of A SHARC Digital Signal Processor Core in Verilog HDL

Uploaded by

Ahmed HamoudaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design and Implementation of A SHARC Digital Signal Processor Core in Verilog HDL

Uploaded by

Ahmed HamoudaCopyright:

Available Formats

Design and Implementation Of a SHARC Digital

Signal Processor Core In Verilog HDL

NMozaffar and N Z. Azeemi*

Department of Hardware, Streaming Networks Pvt. Ltd. Islamabad, Pakistan.

*Asst. Professor Department o f Computer Engineering, VLSl Lab, CIIT, Islamabad, Pakistan

Emails: naveed 33@vahoo.com,nazeemi@,comsats.edu.~k

Abstruct-This paper describes the design ami

implementation of on 8-bit rued point Digital Signal

Processor Core in verilog HDL. The architecture exploits

the principles of pipelining and parallelism in order to

obtain high speed ond throughput. The modules of the

design f i t on a XlLlNX,XC4OlOXLFPCA with 13OK gates

runningat a clockfreqrrencyof32.31 MHz.

The proposed architecture follows the Analog Devices, Figure I. Super Harvard Architecture

SHARC DSP standard. This DSP architecture balonces a The paper i s organized as follows. An outline o f the

high performance processor core with high performance Digital Signal Processor is discussed in Section 2 and i s

buses. Progrom Memory (PM) and Data Memory (DMj. followed by architecture details in Section 3. The synthesis

In the core, every instruction can execure in a single cy& results are provided in Section S with conclusion in

The burs and instmetion cache provide rapid, unimpeded Section 9.

dataflow to the core td maintain the execution rate.

2. ARCHITECTURE OUTLINE

Keywords: VLSI, Verilog HDL. FPCA, SHARC (Super

Harvard Architecture). FFTIFost Fourier transform).CLB The system architecture for the implementation i s shown

(Conjigurable logic blockr). in Figure 2. I n order to achieve high throughput, Super

Harvard architecture i s implemented. The architecture

1. INTRODUCTION consists o f a numeric execution unit. memory modules,

and the main control unit.

A Digital Signal Processor is a type of microprocessorone

that is incr&dibly fast and powerful. A DSP i s unique

because it processes.data in real time. These real time

I"WI I

processor makes up the fastest growing segment of the

semiconductor market and i s particularly well suited to

handle the demands o f processing information, whether as

the engine o f communication applications or by providing

the processingplatform for the convergence ofthe Internet

and wireless applications.

One of the best ways of implementing Digital Signal

Processor is the FPGA FPGA's have the capability of

being reconfigurable within a system, which can be a big

advantage in applications that need multiple trial version

within development, offering reasonably fast time to

market.

This motivates the design and implementation of Digital

Signal Processor in hardware presented in this article.

The design i s implemented using Verilog HDL. Each of

the nine modules i s coded individually. The functional and

timing simulations i s performed followed by the synthesis.

AI! these sub-modules are interconnected in a top-module,

which is also verified and synthesized.

Analog Devices' SHARCQ DSP i s based on a 32-bit super

Harvard architecture that includes a unique memory

architecture comprised o f two large on-chip, dual-poned

SRAM blocks coupled with a sophisticated I/O processor, I 1 -

which gives SHARC the bandwidth for sustained high-

speed computations. The Block diagram o f SHARC Figure 2. DSP System Architecture Block Diagram

architecture is illustrated in Figure 1

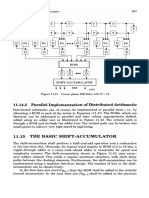

Proceedings IEEE INMIC 2003 247

The proposed design uses a register-register based data Performing a logical shift or arithmetic shifi of the

path prototype. where operands are fetched from the accumulator value.

register by the functional units and then the results are Normalizing the accumulator.

written back to the register file. Post scaling the accumulator before storing the

accumulator value in data register.

The DSP can be operated in either ofthe two modes In the Fig below the top register shows the pattern before

the shift, and the bottom register shows the pattern that

Reo1 Time Mode: results from the shift.

In this mode the DSP accepts real time data from the

-

field and process it.

Off line Mode:

In thi? mode the DSP can operate on the data stored in

the Data Memory. 7 6 5 4 3 2 1 0

I ~ l ' l ' l 0 1 ~ 1 0 1 ' 1 1

The design i s verified for Oftline mode only. Data Movement in an elght bit barrel shifter

Figure 4. Right ShiR operation

3. ARCHITECTURE DEATILS

3.3 Multiply and Accumulate Unit (MAC)

The design consist o f three main numeric execution units

for data processing as described below: A hardware Multiplier and Multiplier-Accumulator

(MAC) are standard components in all off-the-shelf DSPs.

3.1 Arithmetic Logic Unit (ALU) Multipliers are extensively used in signal processing and

communication systems.

An Arithmetic Logic Unit i s the center core o f a central

The Multiplierladder unit provides multiply and

processing unit. It consists o f a Purely combinational logic

accumulates (MAC) capability. The overall function o f the

and perfoms a set o f arithmetic and logic micro

Multiply Accumulator(MAC) i s given by equation (I).

operations on two input buses. I t has n encoded inputs for

selecting which operation to perform. The select lines are

decoded within the ALU to provide upto 2n different Count-1

operations. The A L U implements a wide range o f Q = Z ( t l ) Multiplicand(rr)*Multiplierfn) (1)

arithmetic and logical functions. The ALU transfer the n=O

result to a destination accumulator after an operation i s

performed. Instructions that perform memory -to- memory '9'i s the primary data output. 'A' and 'B' are multiplied

operation are exceptions. together and the'product added from the current result.

The proposed design o f the A L U i s capable o f performing The eounf value in the Equation is set to a fixed value by a

8 different micro operations. parameter.

The MAC uses Array Mulriplier for multiplication and a

i;~.

;;";o

~

L

;- . high-speed hardware Implemented adder for addition.

-. ~ ~ i

Figure 5 shows the proposed M A C architecture for

implementing in the DSP.

x- IO.ISI.nUlm.,lC

.\emur-

--7

.res",,

Figure 3. A L U System Architecture

3.2 Barrel Shifter

Barrel shifter circulates data bits in a synchronous manner. Figure 5 . The M A C System Architecture

The Barrel Shifter i s used for Scaling operations such as:

As evident form the Figure this architecture is base on an

Prescaling an input data memory operand or the Array Multiplier, a Adder, a M u , and Output hold

accumulator value before an ALU operation. register.

248 Proceedings IEEE INMlC 2003

There are two modes of M A C operation control by the

Multiplier Multiplication

input pin MAC / MUL:

Made I :

MAC / MUL= 0

Array Multiplier performs only Multiplication on the input

data.

Mode 2:

M A C / MUL = I Figure I . Steps required in multiplication

In this mode i t performs Multiplication and accumulation For partial product generation multiplicand x is multiplied

ofthe input data i.e. it is in M A C mode. by x"2"i for all i.Adding all bits o f the multiplicand with

ith bit of the multiplier generates pp, (partial product for

3.3.1 Array Multiplier ith bit) and then shill pp; left. Due to its concurrency, only

one level delay is introduced Independent of the

Due to today's VLSl technology, the array (or parallel) multiplication word length. Hence this area needs no fast

multiplier has become increasingly economical and speed algorithms for generation of partial products.

papular. Some multiplier basics, notations and Ml laplicam

4 Vlll VlZl 1111 flO1

conventions are described here.

Generation o f partial products i s the first step of

multiplication operation. These partial products need to be

added together for generating the final product of

multiplication. Figure 6 shows the process of partial

product generation in the multiplication of two unsigned

numbers a and b. Adding all partial products generates the

final product. So the process o f multiplication consists of

generating partial products and adding them together.

. . . . OD,

0, a. 0, 0, % Figure 8. Generation o f Partial Products.

b, b4 b, b: bt bm

The term reduction will be best explained by the following

*A 4.O,,

.. .. .

%bo +bo %b. .visual method o f reduction in Figure 9.

o.b, +b, 4 e,b, %b,

a,& o.b, u,b2 u,b, a,b, 0.b: LeAn

4 0, 4 0, +, 4

0.6. a.b. 4 4 %b. nab8

4 4 0, 4 4 a d ,

Figure 6. Multiplication oftwo 4-bit no

__ __ -

. m . m I

LeA(W

* w . w

An N x M array multiplier architecture consists of three

well-defined major sections performing different (FJlWSbapdlrg

operations: csrydhdlaiw lW*)

. The generation o f N partial products layers.

The reduction of these partial products into 2

Figure 9. Reduction o f Partial Products.

- layers.

And addition of the two layers into a final

product

In the above Figure three dots each symbolizes a partial

product. Using FA (Full Adder) reduces these to two bits,

where one has the weight o f 2'(sum) and the other

Z'(carry). This type o f reduction i s known as 3 to 2

Figure 7. Visually demonstraies'the three major sections reduction or carry saves addition. The two dots are

for performing array multiplication. reduced to 2 using a HA (Half Adder). It can be seen that

this stage (Level n+l) does not yield any reduction. The

rightmost diagram has I dot, which i s carried down

without any action.

Proceedings IEEE INMIC 2003 249

3.3.2 Adder 3. 4.3 Control Unit

The speed o f a signal processing or communication system The 5-bit opcode i s further decoded by the control unit

ASIC depends heavily on these lunctional units. Adders This module separate the 5-bits o f opcode and assign them

are in the critical path o f many other arithmetic operations to the control register of the appropriate functional unit.

like multiplication. scaling, add-compare select, and These Control register is connected to the Function select

division. pin ofthe three functional units.

--

Two basic adder architectures are studied for This opcode contains the following information:

implementation:

Defines the function to be performed.

Rippie Carry Adder.

Carry Lookahead Adder. . Select a specific functional unit for that operation

Specify the source of data to that functional unit.

A ripple adder i s not normally used in high-speed

3.5 MEMORY MODULES

arithmetic. However in situations in which a minimum

amount o f hardware is required and speed is not critical,

The proposed design uses three Memories for maximum

then a ripple adder can prove advantageous. The proposed

throughput of the DSP. The design has separate memories

design implements a C a q Look-ahead Adder schemefor

for storing data, filter coefficients and instructions as

f a r arifhmeric operorions.

specified below.

3 . 4 CONTROLLER

MODULES

- Data Memory (DM)

This unit o f the design serves as the torchbearer for the all

the signals flowing. This means to say that it routes all the

signals to their proper destinations. For some signals it

- Coefficient Memory (CM)

Program Memory (PM)

makes sure that the signals arrive at their destined place to 3.5.1 Data Memory

ensure the efficient operation o f architecture. The

Controller Unit includes three sub modules. Data Memory is used to store only Data coming from

either external source or Funcional units output registers.lt

Program Counter (PCj

can store 64 words each o f 8 bits.The address bus width is

Instruction Decoder (ID)

of 6-bit thus it easily address 64 memory ocations.The

Control Unit (CUj

memory is designed with separate read and write address

bus thus enabling read and write from different locations

3.4.1 Program Counter of the memory at the same time in the intelval o f one

clock cycle.At first the write instructions must be executed

The Program Counter i s a 6-bit counter its output i s

to write the data in the Data Memory

connected to Program Memory. It generates a 6-bit count

value, which is used to address the Program Memory,

3.5.2 Coellicient Memory

which stores the instructions. I t can select 64 memory

locations. The Program Counter usually holds the address

Coefficient Memory is used to store only Filter

o f the next instruction from the instruction, which i s

coefficients and twiddle factors in case o f FFTSt can store

currently executing.

16 words each o f 8 bits.The address bus width i s o f 4-bit

I t addresses a 64x1 I bit Program Memory

thus it easilyaddress 16 memory ocations.The memory is

designed with only a single address bus and a read control

3.4.1 Instruction Decoder signal.Before simulation the memory is initialized with

Memory initialirarion file which contains the required

The instruction decoder decodes the 1 I-bit instruction. It Coefficients needed for a particular operation.

also generates control signals for the memory. The

instructions contain the following information. 3.5.3 Program Memory

Opcode.

Program Memory i s used to store only intructions which

Address.

are first given as input by the user during simulation .It

Read control. can store 64 words each o f I 1 bits.The address bus width

Write control. i s of 6-bit thus it easily address 64 memory ocations.At

CMaddress. first the write instructions must be executed to write the

C M read control dlta in the Data Memory.

250 Proceedings IEEE INMIC 2003

4. IMPLEMENTING FFT ALGORlTHlUM

The proposed archilecture is tested for FFT Table A. Instructions for the Computation ofone butterfly.

implementation, a digital signal processing algorithm used

for calculating DFT. A 4-point radix-2 algorithm is

implemented for this architecture as shown in Figure IO.

r - -..-..-

addrcs o f x (2)

efsfc 2 from DM

rte 6 from x (01

Store ihercrvlr of IlO~OOoo~OOOl WRITE

step 7 on the

w4 -1 address of x 01

5. PIPELINING

Figure IO.Flow graph for a 4-poig radix-2 algorithm.

The proposed DSP design is a fully pipelined architecture

that has five stages. The pipelining in the design can be

The WO4and Wlrarethe twiddle factors and are stored in shown as follows:

the CM prior to the processing. For the convenience of

understanding, we have supposed the values of these as

the I and 2 respectively and are stored in the CM.The

algorithm uses four butterilies and each requires I 1

instructions and so 4 point DFT needs 44 instructions to be

computed. Four more have been added to output the four

outputs from the DM thus making a total 48 instructions.

Now these 48 instructions will need 53 clock cycles to

execute complying with the pipeline specifications.

The four.data inputs samples are coming from the external

environment (in our case given input by the simulation

waveform) and are stored in the memory. An efficient

program (set of EEDSPOOI-the proposed DSP

architecture-instruction sets) is written as shown in Table

A, so that data samples are fetched in the bit reversed CAR

order. Since each wite instruction takes 2 cycles to

execute 8 operations take 1 I cycles, as three write are

included. 19-"1

Cwff Addr. Rcgirleri

Feleh

Similar three more Sets of instNctionS are required with

different operands and addresses to compute 4 point DFT.

4 . 1 Simulation Waveform EllCEYlC

The simulation waveform is generated by XlLlNX ISE OHR

Ver. 4.2 showing the computation of 4 point DFT. The

input data samples are supposed as-x (n) = (2, 4. 6, I ) . Data out

The computation is completed in 53 cycles and at last we

have the output X (k) = (D,2, 3, F6). These values are

displayed in the ALU-OUT register. Figure IO. Five stages ofpipelining in DSP Architecture.

Proceedings IEEE INMlC 2003 251

I n this pipelined architecture first instruction takes five 8. SYNTHESIS RESULTS

cycles IO execute and thereafter the subsequent

instructions take only one cycle to execute. Therefore, the The architecture presented is highly modularized one that

throughput has been increased. This initial delay of five makes it very suitable for VLSl implementation. It has

cycles is called the lutency of the architecture. Hence N high input data rate of one sample per cycle and high

instructions take N + 5 cycles to execuie as compared to throughput rate. Due to smooth data flow, control circuits

serial processing where N instructions will require Nx5 are designed compactly as counter based logic with pause

cycles showing an increase of five times in the throughput. function to freeze all operations. The architecture is

One of the problems .that has been encountered in the verified by Verilog simulation based on register transfer

pipeline is that of the conflicting instructions. In our level descriptions. The entire architecture is fitted on a

design it occurs in the write instruction. Therefore, in the XlLlNX XC401OXL FPGA running at a clock frequency

pipelined architecture. control the flow of pipeline is a bit of 32.31 MHz. The implementationiSynthesis results are

changed by delaying conflicting instruction. This method shown in the Table B .

is called interlocking. Thus the write instruction takes two

cycles to execute. Table B. Synthesis results on XlLlNX XC401OXL FPGA

6. INTEGRATION O F COMPONENTS

Critical Path Timin 10.91 nr

3 2 3 i MHZ

To achieve the design o f the Digital Signal Process&, the

Number OfCLBr

modules were implemented according to the plan set. The 7765

Digital Signal Processor was divided into several Addirialai GareCounl For lOBr

Components (top-down approach). The Functionality of

each module that it must satisfy to Communicate with 9. CONCLUSION

other modules were defined at that stage with great caution.

This helped us in the bottom-up approach of integration o f DSPs is an answer to the intense need of high-speed and

the modules to get a final Digital Signal Processor intensive processing technologies, which is both cheap and

circuitry. The individual modules were combined to form easy to use. DSPs is finding favor not only for computer

the Digital Signal Processor core. systems, but also in consumer electronics products such as

cellular phones.

The CPU and the Data path are designed to comprehend

the details of DSPs architecture. The author develops the

logic, architecture and interface.

[ I ] Modeling, Synthesis, And Rapid Prototyping with the

Verilog HDL. Michcheal D. Cilerri.

(21 VLSl Digital Signal Processor, Kjay K Modisen i.

[3] The ADSP-21535 DSP Hardware Reference Manual.

141 Erskine, C.. and S. Magar. “Architecture and

Applications of a Second-Generation Digital Signal

Processor,” Proceedings of IEEE International

Conference on Acoustics, Speech, and Signal

Processing, USA, 1985.

Figure I 1.Integration of Components

7. DESIGN FLOW USING EDA TOOL

[SI Lin. K., G. Frantz. and R. Simar, Jr.. “The TMS320

Family orDigital Signal Processors,” Proceedings of

The EDA Tool used for the synthesis and simulation of the IEEE, USA, Volume 75, Number 9, pages 1143-

1159, September 1987.

the DSP processor is XlLlNX ISE Ver. 4.2. First the

architecture of the DSP is studied then the design is made

first using traditional Paper-pencil approach and then the

design is translated to the HDL language, Verilog HDL.

After the designing process is completed the verilog

description of the design is written and it is then imported

in the EDA tools.

252 P r o c e e d i n g s IEEE INMlC 2003

You might also like

- Design and Implementation of FPGA Based 32 Bit Floating Point Processor For DSP ApplicationDocument5 pagesDesign and Implementation of FPGA Based 32 Bit Floating Point Processor For DSP ApplicationAzhar Yaseen N JNo ratings yet

- Hardware Implementation BackpropagationDocument14 pagesHardware Implementation BackpropagationDavidThânNo ratings yet

- DSP Unit-6Document26 pagesDSP Unit-622pa5a0407No ratings yet

- A Reconfigurable Digital Signal Processing SystemDocument6 pagesA Reconfigurable Digital Signal Processing Systempym1506gmail.comNo ratings yet

- Risc Processor Using VHDLDocument5 pagesRisc Processor Using VHDLAruna RajanNo ratings yet

- Delayed Branch Logic: Texas Instruments TMS320 Is A Blanket Name For A Series ofDocument13 pagesDelayed Branch Logic: Texas Instruments TMS320 Is A Blanket Name For A Series ofnomadcindrellaNo ratings yet

- DSP Lab Manual C Matlab Programs Draft 2008 B.Tech ECE IV-I JNTU Hyd V 1.9Document47 pagesDSP Lab Manual C Matlab Programs Draft 2008 B.Tech ECE IV-I JNTU Hyd V 1.9Chanukya Krishna Chama100% (21)

- Rapid Prototyping of Image Analysis Algorithms On An Adaptive Fgpa ArchitectureDocument5 pagesRapid Prototyping of Image Analysis Algorithms On An Adaptive Fgpa ArchitectureUmar AnjumNo ratings yet

- FPGA Arquitectura BasicaDocument7 pagesFPGA Arquitectura BasicaJesus LeyvaNo ratings yet

- 21ec42 Module 5Document29 pages21ec42 Module 5ananyanagaral06No ratings yet

- Design of RISC Processor Using VHDL and CadenceDocument2 pagesDesign of RISC Processor Using VHDL and CadencepoojaNo ratings yet

- DSP-8 (DSP Processors)Document8 pagesDSP-8 (DSP Processors)Sathish BalaNo ratings yet

- Design and Performance Analysis of 8-Bit RISC Processor Using Xilinx ToolDocument7 pagesDesign and Performance Analysis of 8-Bit RISC Processor Using Xilinx Toolkirat palNo ratings yet

- CPU - Organisation - Sir NotesDocument8 pagesCPU - Organisation - Sir Notes69Sutanu MukherjeeNo ratings yet

- Chameleon ChipDocument21 pagesChameleon Chip429by3100% (1)

- Introduction to DSP Processors: Modified Bus Structures and Memory AccessDocument26 pagesIntroduction to DSP Processors: Modified Bus Structures and Memory AccessVaishnavi. KoyaNo ratings yet

- FPGA Implementation of A Trained Neural Network: Seema Singh, Shreyashree Sanjeevi, Suma V, Akhil TalashiDocument10 pagesFPGA Implementation of A Trained Neural Network: Seema Singh, Shreyashree Sanjeevi, Suma V, Akhil TalashiHaiNguyenNo ratings yet

- Module 5Document7 pagesModule 5cosmiclove7353No ratings yet

- Chameleon ChipDocument26 pagesChameleon Chipkrushang kananiNo ratings yet

- Digital Signal Processing Lab MannualDocument37 pagesDigital Signal Processing Lab Mannualsreenathreddy100% (4)

- FPGA Implementations of Feed Forward Neural Network by Using Floating Point Hardware AcceleratorsDocument10 pagesFPGA Implementations of Feed Forward Neural Network by Using Floating Point Hardware AcceleratorsCarlos Torres CasasNo ratings yet

- Ece-Vii-dsp Algorithms & Architecture U2Document21 pagesEce-Vii-dsp Algorithms & Architecture U2torchbearer oneNo ratings yet

- FPGA Implementation of Discrete Wavelet Transform For Jpeg2000Document3 pagesFPGA Implementation of Discrete Wavelet Transform For Jpeg2000attardecp4888No ratings yet

- DSP Hardware: EKT353 Lecture Notes by Professor Dr. Farid GhaniDocument44 pagesDSP Hardware: EKT353 Lecture Notes by Professor Dr. Farid GhanifisriiNo ratings yet

- NeuralScale: RISC-V Based Neural Processor Boosting AI InferenceDocument7 pagesNeuralScale: RISC-V Based Neural Processor Boosting AI InferenceRonald dNo ratings yet

- Implementation of MAC Unit Using Booth Multiplier & Ripple Carry AdderDocument3 pagesImplementation of MAC Unit Using Booth Multiplier & Ripple Carry AdderVijay KulkarniNo ratings yet

- Chameleon ChipDocument21 pagesChameleon ChipbiswalsantoshNo ratings yet

- DSP Hardware Architecture and Fixed-Point FormatsDocument21 pagesDSP Hardware Architecture and Fixed-Point FormatsJunaid Ahmed 404No ratings yet

- Arithmetic Logic UnitDocument11 pagesArithmetic Logic UnitPrasanna Kumar VotarikariNo ratings yet

- DSP Module 5 2018 SchemeDocument104 pagesDSP Module 5 2018 SchemeD SUDEEP REDDYNo ratings yet

- PSIM Simulation of DSP-Based Power Electronics ControlDocument6 pagesPSIM Simulation of DSP-Based Power Electronics ControlPasha ZubkovNo ratings yet

- International Refereed Journal of Engineering and Science (IRJES)Document4 pagesInternational Refereed Journal of Engineering and Science (IRJES)www.irjes.comNo ratings yet

- Single Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGADocument4 pagesSingle Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGAInternational Organization of Scientific Research (IOSR)No ratings yet

- Machine Learning Hardware AccelerationDocument26 pagesMachine Learning Hardware AccelerationSai SumanthNo ratings yet

- 8 Bit Microprocessor Using VHDL: Pallavi Deshmane, Maithili Lad & Pooja Mhetre Sharan KumarDocument6 pages8 Bit Microprocessor Using VHDL: Pallavi Deshmane, Maithili Lad & Pooja Mhetre Sharan KumarshubhamNo ratings yet

- 8085 Chapter9Document6 pages8085 Chapter9Amir Hossein Javan AmoliNo ratings yet

- Master-Slave DSP Board for Digital Control SystemsDocument5 pagesMaster-Slave DSP Board for Digital Control Systemsfurious143No ratings yet

- 32 Bit Risc ProcessorDocument60 pages32 Bit Risc ProcessorMuruganantham MuthusamyNo ratings yet

- FPGA Implementation of LSTM Based On Automatic Speech RecognitionDocument3 pagesFPGA Implementation of LSTM Based On Automatic Speech RecognitionsridharchandrasekarNo ratings yet

- Ece 18ec734 M2S5 SMDocument7 pagesEce 18ec734 M2S5 SM1GG20EC426 Yuvaraj MNo ratings yet

- Digital Design and Implementation of An Overcurrent Relay On FPGADocument5 pagesDigital Design and Implementation of An Overcurrent Relay On FPGANandi ?No ratings yet

- Mixed NeuromorphicDocument4 pagesMixed NeuromorphicPeter Wagih ZakiNo ratings yet

- Processor Realization For Application of Convolution: Prashant D Bhirange, V. G. Nasre, M. A. GaikwadDocument5 pagesProcessor Realization For Application of Convolution: Prashant D Bhirange, V. G. Nasre, M. A. GaikwadIJERDNo ratings yet

- MEL G642-Compre Solution - 2 2016-17Document9 pagesMEL G642-Compre Solution - 2 2016-17Gaurav PatilNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- 08 - Chapter 2 PDFDocument15 pages08 - Chapter 2 PDFBhavani BhavanNo ratings yet

- 08 - Chapter 2 PDFDocument15 pages08 - Chapter 2 PDFDimple AmudaNo ratings yet

- Irjet V5i3295 PDFDocument3 pagesIrjet V5i3295 PDFchaitanya sNo ratings yet

- 4th Process TomograpgyDocument6 pages4th Process TomograpgyEmmanuel Abdias Romano CastilloNo ratings yet

- XC Sysgen43Document3 pagesXC Sysgen43YogeeshHtNo ratings yet

- Digital Signal Processing AdvancedDocument14 pagesDigital Signal Processing AdvancedMathi YuvarajanNo ratings yet

- Secure Remote Protocol For Fpga ReconfigurationDocument5 pagesSecure Remote Protocol For Fpga ReconfigurationesatjournalsNo ratings yet

- Design and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolDocument10 pagesDesign and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolRakeshconclaveNo ratings yet

- Iat-4 McesDocument12 pagesIat-4 Mcesbhatt bhattNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Architecture-Aware Optimization Strategies in Real-time Image ProcessingFrom EverandArchitecture-Aware Optimization Strategies in Real-time Image ProcessingNo ratings yet

- Virtual Lab 7 - Martian RescueDocument4 pagesVirtual Lab 7 - Martian RescueAhmed HamoudaNo ratings yet

- Virtual Lab 8 - The Black BoxDocument4 pagesVirtual Lab 8 - The Black BoxAhmed HamoudaNo ratings yet

- Lecture 8: Verilog Code: EE533: Network Processor Design and ProgrammingDocument28 pagesLecture 8: Verilog Code: EE533: Network Processor Design and ProgrammingAhmed HamoudaNo ratings yet

- Transfer FunctionsDocument4 pagesTransfer FunctionsAhmed HamoudaNo ratings yet

- Virtual Lab 4 - Handling and Displaying DataDocument3 pagesVirtual Lab 4 - Handling and Displaying DataAhmed HamoudaNo ratings yet

- Virtual Lab 3 - Direct IO CommunicationDocument6 pagesVirtual Lab 3 - Direct IO CommunicationAhmed HamoudaNo ratings yet

- Virtual Lab 6 - Magnitudes, Phases Everywhere!Document5 pagesVirtual Lab 6 - Magnitudes, Phases Everywhere!Ahmed HamoudaNo ratings yet

- Digital Oscilloscopes Powerful Tools For Eet LaboratoriesDocument12 pagesDigital Oscilloscopes Powerful Tools For Eet LaboratoriesAhmed HamoudaNo ratings yet

- Trade Register 2022 2022Document1 pageTrade Register 2022 2022Ahmed HamoudaNo ratings yet

- A Network Project Course Based On Network ProcessoDocument5 pagesA Network Project Course Based On Network ProcessoAhmed HamoudaNo ratings yet

- Designing For Current Sharing in Power ArraysDocument4 pagesDesigning For Current Sharing in Power ArraysAhmed HamoudaNo ratings yet

- Lect7 Current Sources p20Document1 pageLect7 Current Sources p20firpealNo ratings yet

- Introduction To Network ProcessorsDocument7 pagesIntroduction To Network ProcessorsAhmed HamoudaNo ratings yet

- An Eet Program S Innovative First Semester Course in Electricity ElectronicsDocument11 pagesAn Eet Program S Innovative First Semester Course in Electricity ElectronicsAhmed HamoudaNo ratings yet

- 100A Redundant Isolation Module DatasheetDocument2 pages100A Redundant Isolation Module DatasheetAhmed HamoudaNo ratings yet

- Design of Auxiliary Power Supply For Fault-Tolerant Operation of Solar Array RegulatorDocument2 pagesDesign of Auxiliary Power Supply For Fault-Tolerant Operation of Solar Array RegulatorAhmed HamoudaNo ratings yet

- HCF Fie2002Document7 pagesHCF Fie2002Ahmed HamoudaNo ratings yet

- A FET Or-Ing Circuit For Fault-Tolerant Power SystemsDocument10 pagesA FET Or-Ing Circuit For Fault-Tolerant Power SystemsAhmed HamoudaNo ratings yet

- Long Term Aging of Electronics Systems & Maintainability Strategy For Critical ApplicationsDocument4 pagesLong Term Aging of Electronics Systems & Maintainability Strategy For Critical ApplicationsAhmed HamoudaNo ratings yet

- Backplane Health Rests On Fault FindingDocument20 pagesBackplane Health Rests On Fault FindingAhmed HamoudaNo ratings yet

- A "Beginner's Guide" To Fault Tolerant Power SuppliesDocument4 pagesA "Beginner's Guide" To Fault Tolerant Power SuppliesAhmed HamoudaNo ratings yet

- Space Product Assurance: Sneak Analysis - Part 2: Clue ListDocument98 pagesSpace Product Assurance: Sneak Analysis - Part 2: Clue Listaemis2010No ratings yet

- Space Product Assurance: Sneak Analysis - Part 1: Principles and RequirementsDocument50 pagesSpace Product Assurance: Sneak Analysis - Part 1: Principles and Requirementsaemis2010No ratings yet

- Benchmark Standards For ASIC Technology EvaluationDocument5 pagesBenchmark Standards For ASIC Technology EvaluationAhmed HamoudaNo ratings yet

- Sneak Analysis - Part 1 - Method and ProcedureDocument52 pagesSneak Analysis - Part 1 - Method and ProcedureAhmed HamoudaNo ratings yet

- Recipe For ReliabilityDocument4 pagesRecipe For ReliabilityAhmed HamoudaNo ratings yet

- Taming The All-Equipment Reliability TestDocument5 pagesTaming The All-Equipment Reliability TestAhmed HamoudaNo ratings yet

- RADC Initiatives in CAE For Reliability and MaintainabilityDocument3 pagesRADC Initiatives in CAE For Reliability and MaintainabilityAhmed HamoudaNo ratings yet

- Achieving Reliability in Semiconductor Memory SystemsDocument1 pageAchieving Reliability in Semiconductor Memory SystemsAhmed HamoudaNo ratings yet

- Navmat P-9492Document18 pagesNavmat P-9492Jess OrtonNo ratings yet

- Adder, Sub Tractor and Comparator Circuits: ObjectivesDocument12 pagesAdder, Sub Tractor and Comparator Circuits: ObjectivesAhmed JamalNo ratings yet

- Lecture 5 - Combinational LogicDocument164 pagesLecture 5 - Combinational LogicZülal DemirtaşNo ratings yet

- Ekgkjktk Xaxk Flag Fo'ofo - Ky Chdkusj: M.Sc. Computer ScienceDocument21 pagesEkgkjktk Xaxk Flag Fo'ofo - Ky Chdkusj: M.Sc. Computer SciencePankaj DadhichNo ratings yet

- Area Delay Power Efficient Carry Select AdderDocument5 pagesArea Delay Power Efficient Carry Select AdderAzeem TopNo ratings yet

- Project 3 ReportDocument40 pagesProject 3 Reportapi-355421942No ratings yet

- VLSI Design-QBANKDocument13 pagesVLSI Design-QBANKjascnjNo ratings yet

- MacDocument20 pagesMacdeepakk_alpineNo ratings yet

- De Lab ManualDocument42 pagesDe Lab ManualAnjali KumariNo ratings yet

- Cs302 Mid Term Solved by AliDocument10 pagesCs302 Mid Term Solved by AliMuheet Ali0% (1)

- CS302 Quiz-1 by Attiq Kundi-Updated-1Document41 pagesCS302 Quiz-1 by Attiq Kundi-Updated-1Atif MubasharNo ratings yet

- Mrs.v.uma Digital System Design LABDocument70 pagesMrs.v.uma Digital System Design LABRutuja KakadeNo ratings yet

- Basic Shift AccumulatorDocument4 pagesBasic Shift AccumulatorThahsin ThahirNo ratings yet

- DPCO Unit 1Document45 pagesDPCO Unit 1Laks SadeeshNo ratings yet

- DSD Model Paper 2Document8 pagesDSD Model Paper 2VigneshNo ratings yet

- Datasheet - 74LS283 - Somador Binário Completo de 4 BitsDocument7 pagesDatasheet - 74LS283 - Somador Binário Completo de 4 BitsLucas CarvalhoNo ratings yet

- Computer Organisation and Architecture Notes by Darshan InstituteDocument64 pagesComputer Organisation and Architecture Notes by Darshan Institute1golmatol1No ratings yet

- High-Speed, Area Efficient VLSI Architecture of Wallace-Tree Multiplier For DSP-applicationsDocument5 pagesHigh-Speed, Area Efficient VLSI Architecture of Wallace-Tree Multiplier For DSP-applicationsdivya_cestNo ratings yet

- Ecl 203 MCQDocument3 pagesEcl 203 MCQresham k vNo ratings yet

- Jalwin Cpe301 Ex5 PDFDocument14 pagesJalwin Cpe301 Ex5 PDFSiegrique Ceasar A. JalwinNo ratings yet

- Digital Design LaboratoryDocument10 pagesDigital Design Laboratorykarths22No ratings yet

- 4 Bit Adder M.P. Join AICTEDocument7 pages4 Bit Adder M.P. Join AICTEVivek SharmaNo ratings yet

- Lecture 1: Introduction: CS-216: Digital Logic DesignDocument23 pagesLecture 1: Introduction: CS-216: Digital Logic DesignDaniaNo ratings yet

- KL-300 10907Document4 pagesKL-300 10907Sergio LimaNo ratings yet

- Design Entry in VHDL, Entity, ArchitectureDocument32 pagesDesign Entry in VHDL, Entity, ArchitectureSHYAMNo ratings yet

- Arithmetic Building Blocks: Digital Integrated Circuits © Prentice Hall 1995 ArithmeticDocument45 pagesArithmetic Building Blocks: Digital Integrated Circuits © Prentice Hall 1995 ArithmeticFatima MirNo ratings yet

- Fast Vedic Multiplier Design Using ROM ApproachDocument4 pagesFast Vedic Multiplier Design Using ROM Approachvenkatraman1983No ratings yet

- Digital Questions ObjectiveDocument22 pagesDigital Questions ObjectiveSathiya GunasekaranNo ratings yet

- Certificate: DateDocument47 pagesCertificate: DaterohitNo ratings yet

- SAP-1 Simple ComputerDocument55 pagesSAP-1 Simple ComputerMd. MoniruzzamanNo ratings yet

- Approximate Multipliers Based On New Approximate CompressorsDocument14 pagesApproximate Multipliers Based On New Approximate Compressorsswetha sillveriNo ratings yet