Professional Documents

Culture Documents

09 Digital Signal Processing r17 PDF

Uploaded by

tajudeenOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

09 Digital Signal Processing r17 PDF

Uploaded by

tajudeenCopyright:

Available Formats

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Power System Protection

for Engineers

Digital Signal Processing

Overview

Copyright © SEL 2005

Digital Signal Processing_r17 1

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Digital Signal Processing

Objectives

z Review Digital Signal Processing

Techniques and Digital Filters

z Explain Why Digital Relays Require

Anti-Aliasing Filters

z Determine What Delays a

Microprocessor-Based Relay

z Explain Why a Cosine Filter is Better

than a Fourier Filter

Digital Signal Processing_r17 2

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Digital Signal Processing

z DSP is the Representation,

Transformation, and Manipulation of

Signals and the Information that They

Contain, Using Numerical Algorithms

Many Applications

Digital Relaying is One of These

Applications

We use signals to communicate between humans or between humans and machines. We

use signals to probe our environment and to control and use energy and information.

Signal processing is related to the representation, transformation, and manipulation of

signals and the information they contain. Digital signal processing uses numerical

algorithms to that end. There are many fields of application of digital signal processing in

the present-day world, mainly related to on-line applications of digital computers.

Digital Signal Processing_r17 3

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Input/Output Scheme of a Digital Relay

Auxiliary Input

(AC or DC)

Dry contacts

Analog Inputs Computer-Based Outputs

(trip, alarm,

Relay etc.)

Discrete Inputs (Digital Relay)

“Live” outputs

Computer

Communications

Digital Signal Processing_r17 4

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Line Fault Transients: Voltages

Phase A-to-Ground Fault

5

x 10

1.5

Voltages (V) 1

0.5

-0.5

-1

va

-1.5

0 0.01 0.02 0.03 0.04 0.05 0.06

Time (s)

This slide shows how the current and voltages behave in the substation during a single-

phase-to-ground fault. From this figure, it is possible to conclude that the fault was a

single-phase-to-ground fault. The detailed analysis of fault transients is out of the scope

of this section of the course, but the graph is presented to give an idea of the

instantaneous evolution of the phase quantities during the fault.

Digital Signal Processing_r17 5

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Line Fault Transients: Currents

Phase A-to-Ground Fault

4

x 10

2

1.5

1

Currents (A)

0.5

-0.5

-1

ia

-1.5

-2

0 0.01 0.02 0.03 0.04 0.05 0.06

Time (s)

This graph shows the fault current.

Digital Signal Processing_r17 6

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Review of Simple Frequency

Sinusoidal Signal

v(t) = VC1 cos(ω t) +VS1 sin(ω t) = V1 cos(ω t + φ1)

Where VC1 = Cosine

Component

VS1 =

v(t) Sine Component

V1 1

f=

T

t ω = 2πf = 2π

T

T

Period

A simple frequency sinusoidal signal can always be represented as the sum of a cosine

and a sine component.

Digital Signal Processing_r17 7

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Phasor Components

v(t) = VC1 cos(ω t) +VS1 sin(ω t) = V1 cos(ω t +φ1)

1 V1 jφ1

V = [VC1 + jVS1] = e

2 2

There is a phasor associated with the sinusoidal signal. The cosine and sine components

of the signal are directly related to the real and imaginary parts of the phasor.

Digital Signal Processing_r17 8

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

A Signal With Several Frequencies

v(t) = 1.0 ⋅ cos(ω t) + 0.7 ⋅ cos(2ω t) + 0.3⋅ cos(3ω t)

When there is more than one frequency present, the periodic signal does not appear as a

pure sinusoid.

Digital Signal Processing_r17 9

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

General Periodic Signal

z Fourier Representation:

∞ ∞

v(t) = ∑(VCn cos(nωt) +VSn sin(nωt)) = ∑Vn cos(nωt + φVn )

n=0 n=0

z Many Relay Applications Use

Fundamental Component Only:

v (1) (t ) = VC1 cos(ω t ) + VS 1 sin(ω t ) = V1 cos(ω t + φV 1 )

z Cosine and Sine Components for

Phasor Calculations:

VC1, VS1, IC1, I S1

Digital Signal Processing_r17 10

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Signal Component

Fundamental 0

-2

0 0.5 1 1.5 2 2.5 3 3.5 4

2

0

-2

0 0.5 1 1.5 2 2.5 3 3.5 4

2

DC 0

-2

0 0.5 1 1.5 2 2.5 3 3.5 4

2

0

-2

0 0.5 1 1.5 2 2.5 3 3.5 4

2

0

-2

0 0.5 1 1.5 2 2.5 3 3.5 4

cycle

Shown above are examples of various waveforms that might be found on any power

system.

Top waveform - example of a 60 hertz signal

Second waveform - example of non-60 hertz signal or harmonics

Third waveform - example of DC offset

Fourth waveform - example of high frequency white noise

Last waveform - combined waveforms of all of the above

The last waveform is one that a digital relay might have to deal with on any given power

system. This waveform is the perfect example of why filtering is required. Digital relays

do not operate directly from the sampled values of the original waveform but rather from

the filtered components of the sampled values of the original waveforms. It is the job of

the filter to extract the signals of interest. In most applications, the fundamental portion

(or 60 hertz) of the sampled waveform is the quantity of interest.

Digital Signal Processing_r17 11

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Filtering Requirements

z Depend on Relay Type

Traveling-wave relays

Harmonic-restraint relays

Distance relays

Overcurrent relays

Filtering requirements depend on the relay purpose. Traveling-wave relays do not need

the fundamental (60Hz) portion of the signal. These relays need to extract and operate

from the high frequency portion of the waveform. Transformer differential relays need

several waveform quantities. In this type of relay, the fundamental portion of the

waveform is used to calculate the operating or difference quantity. The transformer

differential relay must also extract the second and fourth harmonics to detect transformer

energizing in-rush.

Additionally, the presence of the fifth harmonic can be used to determine transformer

over-excitation. Distance and overcurrent relays need to extract and develop operating

quantities only from the fundamental portion of the waveform.

Digital Signal Processing_r17 12

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Filtering for Distance Relays

z Pass 50 or 60 Hz Only

z Attenuate High Frequencies

z Eliminate DC-Offset

z Null Out Harmonics

z Minimize Transient Response

z Must be Practical

Above are the design goals of a good filter. All fault study impedances are based on

system impedances calculated at the operating frequency of the power system.

Therefore, the fundamental component of the input signal waveform is the value that

relays need to extract in order to calculate accurate fault values.

Digital Signal Processing_r17 13

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Signal Path for Microprocessor Relays

Analog to

CT Analog Digital Magnitude

Digital

Lowpass Cosine Filter &

Conversion

Filter and Phasor Impedance

PT (A/D)

The signal path for voltage and current input signals are shown above. After the currents

and voltages are reduced to acceptable levels by the instrument transformers, the signals

are filtered with an analog filter, then digitized and re-filtered with a digital filter. Each

filter has a specific purpose that complements the other filter and will be discussed in the

following slides. Numerical operating quantities are then calculated from the processed

waveforms.

Digital Signal Processing_r17 14

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Digital Relay Architecture

Analog Discrete Tripping

M Input A/D Output M Outputs

Subsystem Subsystem

Operation

Discrete Microprocessor Signalling

M Input

} Communications

Subsystem

M Ports

RAM ROM / PROM EEPROM

Digital Signal Processing_r17 15

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Analog Input Subsystem

z Surge Suppression

z Signal Conditioning

z Galvanic Isolation

z Low-Pass (Anti-Aliasing)

Filtering

Digital Signal Processing_r17 16

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Analog Input System

Analog filter

Output

Input

Digital Signal Processing_r17 17

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Frequency Response of a

Simple Analog Low-Pass Filter

Magnitude

Frequency

Digital Signal Processing_r17 18

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Sampling of Analog Signals

S/H

Input Output

Continuous Signal Sampled Signal

Digital Signal Processing_r17 19

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Sampled Signal Sequence

Present

k Sample

k-1

Sampling

Frequency:

1

fs =

∆T = Sampling Rate

∆t

These are important definitions for a sampled (discrete) signal sequence.

Digital Signal Processing_r17 20

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Simple Representation of Aliasing

Improper Sampling Frequency

ω0 ωs − ω0

This figure shows the original signal with frequency ω0 and its aliased signal of

frequency ωs - ω0.

Digital Signal Processing_r17 21

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Analog to Digital (A/D) Conversion

Input Output

A/D

00000001

00000101

00001001

00100100

10010000

:

Analog Signal Digital Signal

Digital Signal Processing_r17 22

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Digital Relay Algorithm

READ PRESENT SAMPLE k

DIGITAL FILTERING

PHASOR CALCULATION

Modify if PROTECTION METHODS

required

RELAY LOGIC

NO-TRIP

TRIP ORDER

The relay algorithm is a set of mathematical operations implemented in a program.

These operations are performed over the last N samples of the sampled input signal.

The relay makes the decision of tripping (or not) the circuit breaker based on the result

of this algorithm. The algorithm presented in the slide is a particular example.

The routines are:

READING ROUTINES (Read last sample)

This part of the program is in charge of reading the last sample of the input signals.

ROUTINES FOR DIGITAL FILTERING

The digital filter smooth the signal, by eliminating DC and frequencies components

different than the fundamental (when required).

ROUTINES FOR PHASOR CALCULATION

These routines determine phasors V and I from the samples of the sampled signals.

ROUTINES FOR PROTECTION METHODS

These routines implement the protection function: overcurrent, directional, distance,

differential, etc.

ROUTINES FOR RELAY LOGIC

With the results of the protection methods routines, the relay logic make the final

decisions for tripping and other relay functions. In some modern relays, the logic can be

programmed by the user.

Sometimes the digital filtering routines and the phasor calculation routines are

considered the same module.

Digital Signal Processing_r17 23

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Digital Filtering

Non-Filtered Signal

(Samples)

DIGITAL FILTERING

Filtered Signal

(Samples)

The digital filter smoothes the signal by eliminating DC and frequencies components that

are different than the fundamental (when required).

Digital Signal Processing_r17 24

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Digital Filter Example

iok = ik − ik −1 − ik −2 + ik −3

ik DIGITAL io

FILTER

1 0.15

0.1

0.5

0.05

0

-0.5

-0.05

-1

-0.1

-1.5

-0.15

-2 -0.2

0 0.005 0.01 0.015 0.02 0.025 0.03 0.035 0.04 0.045 0.05 0 0.005 0.01 0.015 0.02 0.025 0.03 0.035 0.04 0.045 0.05

This is an example of a 4 sample-per-cycle filter that filters the DC offset of a fault

current.

Notice the following:

1. The signal is sampled at 24 samples per cycle, however the filter uses 4 equally-

spaced samples per cycle. This is a good example to make the difference of initial

sampling frequency and processing sampling frequency. The initial sampling

frequency is 60*20 = 1200 Hz; while the processing sampling frequency is 50*4 =

240 Hz.

2. The fact that the filter uses four equally spaced samples in a cycle, means that the

data window required by the filter is an entire cycle. We say that this filter has a data

window of one cycle, although it does not use all the available samples within the

cycle, just the four spaced π/4 electrical radians.

Digital Signal Processing_r17 25

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Unit Sample (Impulse)

⎧ 0, n ≠ 0

δ[n] = ⎨

0 n ⎩ 1, n = 0

This is a useful function defined in digital signal processing to mathematically model

digital systems.

Digital Signal Processing_r17 26

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Impulse Response

ik DIGITAL io

FILTER

0 n

iok = ik − ik −1 − ik −2 + ik −3

For this type of filter, the impulse response is directly given by the filter coefficients.

Digital Signal Processing_r17 27

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Frequency Response

The frequency response tells us at which frequencies the filter attenuates the input. Note

that for the simple example, the gain is zero for f = 0 Hz. This means the filter blocks the

dc component.

The slide shows the digital filter response up to 120 Hz only.

Digital Signal Processing_r17 28

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Complete Frequency Response

This is the frequency response shown up to the sampling frequency (240 Hz). The

folding frequency is one half of the sampling frequency.

Digital Signal Processing_r17 29

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

The Response is Similar for High

Frequencies

This is the frequency response shown up to 960 Hz. The frequency response repeats for

frequencies larger than the sampling frequency.

Digital Signal Processing_r17 30

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Another Example of a

Complete Response Frequency

Magnitude

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33

Frequency (Harmonics)

Folding Frequency

This is another example. Note that for high frequencies, the filter does not block the

input.

Digital Signal Processing_r17 31

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

General Equation for FIR Filters

N

i ok = b1i k + b 2i k −1 + b 3i k − 2 + b 4i k −3 + L + b N i k − N +1 = ∑ b ji k − j+1

j=1

b = [b1 b 2 b 3 L b N ] is the vector with the filter coefficients

DIGITAL

i io

FILTER

(input) (output)

Examples:

1) iok = ik − ik −1 − ik − 2 + ik −3 , b = [1 − 1 − 1 1]

2) iok = ik − 0.5ik −1 + 3ik − 2 − 4ik −3 + 0.2ik − 4 , b = [1 − 0.5 3 − 4 0.2]

There are several types of digital filters. The finite impulse response filters (FIR) are the

most adequate for relay applications. The general difference equation that represents a

filter is the best way to characterize it.

Two examples are shown.

Digital Signal Processing_r17 32

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Examples of Digital Filters

z CAL

z Cosine

z Fourier

z IIR

z Kalman

Each filter has characteristics and tradeoffs that will be discussed in the following slides.

Digital Signal Processing_r17 33

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

CAL Filter

Impulse Response

t

Frequency Response

The CAL filter is the simplest filter. It has filter coefficients of +/- 1, and the filtering

process uses only addition and subtraction. This eliminates time-consuming

multiplications. Therefore, it is the most computationally efficient filter. It rejects dc

and exponentially decaying dc offset. However, the filter does not reject odd harmonics.

Digital Signal Processing_r17 34

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

1 Cycle Fourier Filters

Impulse Response

t

Frequency Response

sine

cosine

g

A simplistic way of improving the cosine filter is to eliminate the ¼-cycle delay

necessary to calculate the quadrature component of the sampled waveform. The Fourier

Filter uses the orthogonal sine and cosine filter combination to eliminate the ¼-cycle

filter delay by allowing the phasor components of the waveform to be extracted

simultaneously. However, this does not directly correlate into a ¼- cycle operational

speed improvement in the relay. In fact, this method can even be slower than the pure

cosine filter method. Notice the frequency response of the sine and cosine filters as

plotted above. The sine filter has better high frequency rejection but does not reject

exponentially decaying signals. Therefore, the transient response is poor. This poor

transient response is illustrated in the following slides when the filtering techniques are

studied with a model power system.

Digital Signal Processing_r17 35

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Quadrature Components

1 cycle filters

Cos Filter Real

Input

Sine Filter Imaginary

Input x

Cos Filter Real

y

1/4 Cycle

Imaginary

Delay

The figure shows two ways to extract phasor components of the voltage and current

waveforms. One method requires two filters that determine signal quantities

simultaneously in quadrature (90 electrical degrees apart). On the surface, it seems that

this method might be faster. However, it will be shown that in many cases this method

can be slower because of the poor transient nature of the filter method. In addition, this

method places a greater computational burden on the relay.

SEL relays have never used the two-filter method. Instead, SEL relays filter the voltages

and current once and use samples calculated ¼ cycle later to extract the phasor

components of the voltage and current waveforms. The advantages of this method will

be illustrated in the following slides.

Digital Signal Processing_r17 36

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Cosine Filter (1)

Impulse Response

t

Frequency Response

The cosine filter has its coefficients evenly sampled from a cosine waveform. As with

the CAL filter, this filter rejects dc and exponentially decaying signals. Additionally, the

cosine filter rejects all harmonics and, thus, has an advantage over the CAL filter.

Digital Signal Processing_r17 37

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Cosine Filter (2)

Frequency Response of 1 cycle cosine filter

with sample rate of 4 samples per cycle

Harmonics

0 1 2 3 4

Fn Fs

(folding frequency)

FIR filters do a good job of filtering out low order harmonics. However, they do not

filter all harmonics, especially higher order harmonics. Higher order harmonics,

especially those that would normally be present in fault quantities, must be removed from

the signal before entering the digital FIR filter.

The performance (or frequency response) of the FIR filter for higher order harmonics

follows a predictable pattern that is determined through use of a simple concept called

the Nyquist Folding Frequency. The Nyquist Folding Frequency predicts which

frequencies or harmonics the FIR filter will pass (or not attenuate) based upon the

folding frequency. The folding harmonic frequency is always half the sample rate. This

folding frequency technique can be used to illustrate the theoretical requirements of the

low-pass FIR filter.

Digital Signal Processing_r17 38

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Cosine Filter (3)

Frequency Response of 1-cycle cosine filter

G with a sample rate of 4 samples per cycle

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33

Folding Frequency

Frequency (Harmonics)

Above is the frequency response of the 4-sample-per-cycle one cosine filter. When the

sample rate is 4 samples per cycle, the frequency response of the 1-cycle cosine filter

folds (or visually flips over) on the even harmonics.

Digital Signal Processing_r17 39

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Cosine Filter (4)

Frequency Response of 1-cycle cosine filter

with a sample rate of 8 samples per cycle

G

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33

Folding Frequency

Frequency (Harmonics)

Above is the frequency response of the 8-sample-per-cycle, one cosine filter. When the

sample rate is 8 samples per cycle, the frequency response of the 1-cycle cosine filter folds

(or visually flips over) at the 4th,8th, 12th, 16th, 20th, 24th, 28th, and 32nd harmonics. As

illustrated above, an 8-sample-per-cycle cosine filter attenuates all harmonics but the

fundamental, 7th,9th, 15th, 17th, 23rd, 25th, and 31st.

Digital Signal Processing_r17 40

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Cosine Filter (5)

Frequency Response of 1-cycle cosine

filter with a sample rate of 16 samples

G per cycle

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33

Folding Frequency

Frequency (Harmonics)

Above is the frequency response of the 16-sample-per-cycle, one-cosine filter. When

the sample rate is 16 samples per cycle, the frequency response folds (or visually flips

over) at the 8th,16th, 24th , and 32nd harmonics. As illustrated above, a 16-sample-per-

cycle cosine filter attenuates all harmonics but the fundamental, 15th, 17th, and 31st.

Digital Signal Processing_r17 41

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Total Filtering Concept

z Analog + Digital

Analog

Low-pass Anti-aliasing

Digital

Band-pass to Reject Harmonics

and DC-offset

SEL relays use a combination of analog and digital filtering techniques to optimize the

filter design. A low-pass filter (called the anti-aliasing filter) is used on the analog signal

to filter out the high frequency content of the voltage and current signals. This design

technique allows use of a simpler digital filter without compromising the performance of

the relay. The design of the low-pass filter (or the frequencies that it has to attenuate)

will be shown in the next few slides to be dependent on the sample rate and digital filter

window. Effectively, the low-pass or anti-aliasing filter must filter out all harmonics that

the digital filter does not attenuate.

Digital Signal Processing_r17 42

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Design Analog & Digital Filtering

Together

8-sample/cycle

1

LPF Cosine

0.8

g a in 0.6

0.4

folding frequency Total

0.2

0

0 2 4 6 8 10 12 14 16

16-sample/cycle

1

LPF Cosine

0.8

g a in

0.6

Total

0.4

folding frequency

0.2

0

0 2 4 6 8 10 12 14 16

frequency (harmonics)

The analog low pass (anti-aliasing) filter and the digital filter complement one another

and must be designed together. Above, it can be verified that the roll off of the low-pass

filter is a function of the digital filter sample rate. The slower sample rate digital FIR

filters do not do as good a job of filtering all harmonics that might be present on the

power system. Therefore, slower digital filter sampling requires more analog low- pass

filter attenuation. More analog low-pass filter attenuation results in a slower response

from the low-pass filter and a slower relay operate speed.

Digital Signal Processing_r17 43

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Power System Model

Zs Zl

m

Source Zload

Noise

Harmonics Rf

Voltage and Current

Filters should be evaluated from two aspects: their steady-state and transient

performance. The transient period is defined as the time when the filter window includes

pre-fault and post-fault samples. The filter is said to be in a “post-fault steady state” after

the filter window includes all post-fault data. To study the transient response of the

various filters, a single-phase model of the power system can be used to simulate system

conditions similar to one above. The model power system must include a means to inject

noise and harmonics to the filter signals to challenge the various filter techniques.

Digital Signal Processing_r17 44

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Voltage and Current

DC Offset

Zero Inception Angle Harmonics

One set of voltage and current waveforms generated from the model power system

illustrated in the previous slide is shown above. The waveforms above are the result of a

fault being placed on the model system at the end of the line with no fault resistance. An

inception angle of zero gives a full dc offset. The post-fault data are corrupted with noise

and 2nd, 3rd, and 5th harmonics.

Digital Signal Processing_r17 45

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Filtered Voltage and Current

The filtered quantities should look clean without any harmonics, dc offset, or noise.

Analysis of these quantities will yield proper current and voltage phasors.

Digital Signal Processing_r17 46

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

What Delays Relay Operation?

z Analog Filter

z Sampling Latency

z Digital Filter

z Processing Latency

z Output Devices

All the factors above must be considered when evaluating the speed of the relay system.

Digital Signal Processing_r17 47

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Effect of Filtering on Speed

z Analog Low-pass Filter Delay

Sample/Cycle Fc (Hz) Delay (cycle)

4 90 0.18

8 180 0.08

16 360 0.04

The analog low-pass filter is slower if it has to reject more harmonics. It was proven

earlier with the folding theorem that slower sample rates and FIR filters with less than a

1-cycle window require the low-pass filter to reject more harmonics (have a lower cutoff

frequency). Therefore, increasing the filter sample rate is a tradeoff that allows the speed

of the low-pass filter to be increased while decreasing the speed of the digital filter.

Digital Signal Processing_r17 48

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Effect of Filtering on Speed

z Digital Band-pass Filter

Fixed = Window length

The digital filter is the greatest determinant of relay operating speed. We have proven in

this presentation that the one cycle window for the cosine filter provides the optimum

performance.

Digital Signal Processing_r17 49

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Effect of Sampling Latency on

Speed

4-sample/cyc

8-sample/cyc

16-sample/cyc

time (cycle)

0 0.25

Fault Inception

Processing latency affects the overall speed of the relay because if the relay is only

processing every quarter of a cycle the relay has to wait longer to perform the impedance

calculation on the next sampled values.

Digital Signal Processing_r17 50

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

What Delays Relay Operation?

Output Delay

Processing Delay

Analog Delay

Sampling Latency

Digital Delay

0.00 0.25 0.50 0.75 1.00 1.25 1.50

t

The effect of all of the timing factors are illustrated above. Notice that the digital filter is

the largest determinate of the speed of the relay.

Digital Signal Processing_r17 51

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Operating Time vs. Sampling Rate

How much does increasing the sampling rate affect the operating speed? The slide above

indicates that increasing the sampling speed above 16 samples per cycle provides little

improvement in the operating speed of the relay when all of the factors are considered.

The speed increase is realized mainly from a reduced processing latency at the higher

sample rate and low-pass filter speed increase from the higher cutoff frequency.

Digital Signal Processing_r17 52

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Relay Operating Speed vs. Fault

1

0 .9

0 .8

F a u lt In itia tio n

0 .7

m a g n itu d e

0 .6

0 .5 C lo s e -in F a u lt T rip T ime

0 .4

0 .3

0 .2 R e mo te F a u lt T rip T ime

0 .1

T h re s h o ld

0

-1 0 1 2 3 4 5

time (c yc le )

One of the major factors that affects the operate speed of the relay is the fault location. In

the slide above, the trip torque threshold is indicated by a horizontal line at 0.1 per unit

magnitude. At fault inception, it can be seen that the close-in torque trajectory is much

steeper and the fault trip time much faster for the close-in fault.

This torque trajectory is related to the size of the digital filter window and steady state fault

torque. When the steady state fault torque value is close to the trip threshold, it takes more

fault sampled data points in the filter to reach the calculated trip threshold. However, when

the steady state fault torque value greatly exceeds the trip threshold, it may take only a few

samples of data in the filter to reach the calculated trip threshold. Below is a simple

example to illustrate this point.

Simple Filter Example - remote fault:

Pre-fault torque sample value =0.05, fault torque sample value = 0.11

If the torque threshold to trip is 0.1 this simple example shows that it would take seven

samples of fault of data in the filter for the torque to reach the trip value.

Sample 1 torque = (0.05+0.05+0.05+0.05+0.05+0.05+0.05+0.11)/8 = 0.057

Sample 2 torque = (0.05+0.05+0.05+0.05+0.05+0.05+0.11+0.11)/8 = 0.065

Sample 3 torque = (0.05+0.05+0.05+0.05+0.05+0.11+0.11+0.11)/8 = 0.073

Sample 4 torque = (0.05+0.05+0.05+0.05+0.11+0.11+0.11+0.11)/8 = 0.080

Sample 5 torque = (0.05+0.05+0.05+0.11+0.11+0.11+0.11+0.11)/8 = 0.086

Sample 6 torque = (0.05+0.05+0.11+0.11+0.11+0.11+0.11+0.11)/8 = 0.095

Sample 7 torque = (0.05+0.11+0.11+0.11+0.11+0.11+0.11+0.11)/8 = 0.103 TRIP POINT

In the example it becomes obvious that if the fault torque sample values are large with

respect to the trip threshold, it does not take as many fault samples in the filter to exceed the

trip threshold.

Digital Signal Processing_r17 53

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Short Window Implies More Speed

and Less Digital Filtering

0.5 1.5

1

0

0.5

-0.5 0

0 0.5 1 1.5 2 0 2 4 6 8

0.2 1.5

1

0

0.5

-0.2 0

0 0.5 1 1.5 2 0 2 4 6 8

0.1 1.5

1

0

0.5

-0.1 0

0 0.5 1 1.5 2 0 2 4 6 8

The previous example is proof that the cosine filter is preferred over the Fourier because

of superior transient response. The slide above illustrates that the 1-cycle cosine filter is

also preferred over the ½-cycle and 2-cycle cosine filters. The cosine FIR filter with less

than a 1-cycle window cannot reject all harmonics, and it is the even harmonics that are

not fully rejected. It can also be seen in the above illustration that the 2-cycle cosine

filter does not add much filter benefit.

The accuracy lost with the ½-cycle filter is critical for some faults that fall just over the

relay’s threshold. These error can be compensated by different means.

Digital Signal Processing_r17 54

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Quadrature Components

1 cycle

Input x

Cos Filter

Very fast, ultra secure, y

ultra accurate 1/4 Cycle

Delay

Ultra fast, very secure, ½ cycle

very accurate x’

Cos Filter

Input

DC Offset

Filter ½ cycle

y’

Sine Filter

The figure shows the block diagrams of two digital schemes.

The first scheme has 1-cycle cosine filter, for maximum security and accuracy; however,

for certain faults the relay can operate in about 1.25 cycles. This is not a slow algorithm;

however, it is not the fastest one.

The second scheme has ½-cycle cosine and sine filters with a previous DC offset filter. A

relay with a filtering scheme like this may have tripping times of less than 1 cycle. This

scheme allows the even harmonics pass (when they are present), producing an error that

may be intolerable in some cases.

What is suggested by some manufacturers is to use both schemes, as shown in the next

slide.

Digital Signal Processing_r17 55

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Combined Scheme

x, y

Accurate Phasor calculation

and protection

1-Cycle Cosine algorithms

Filter Scheme (21, 32, 67, etc.)

Input

OR

Ultra Fast Phasor Calculation

and protection

1/2-Cycle Cosine algorithms

Filter Scheme (21, 32, 67, etc.)

x’, y’

A possible solution to the conflict speed vs security between 1-cycle filter schemes and

½-cycle filter schemes is to use them as indicated by the simplified shown in the above

figure. The ultra fast elements can be set and employed in a conservative way or in

schemes where the relatively small error is not an issue (for example in a overreach

scheme). More over, the ultra-fast element’s operation can be blocked in case of

dangerous transient phenomenon, like line energization. In these cases the secure and not

so slow element can take the trip control without loosing the protection during the

switching operations. For most faults, this scheme will provide tripping times of less than

a cycle.

Digital Signal Processing_r17 56

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Conclusions

z Band-Pass Filtering Is Required

z Filtering (Not Sampling Rate)

Determines Speed

z Filters Must Reject DC and

Ramps

In conclusion, it has been shown that a combination of filters including a low-pass FIR

analog filter and a full cosine digital filter provide a very robust filter design.

Additionally, a sample rate of 16 samples per cycle provides an optimum balance

between relay speed, filter performance, and computational burden.

Digital Signal Processing_r17 57

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Best Filter: 1-Cycle Cosine

z Zeroes at Harmonics

z Excellent Exponential Rejection

z Combine fast filter schemes

with secure filter schemes

The 16-sample-per-cycle, 1-cosine filter is the best FIR filter because it allows the anti-

aliasing low-pass cutoff frequency to be higher and provide better speed performance of

the low-pass filter while still maintaining the rejection of exponentially decaying DC and

all harmonics.

Digital Signal Processing_r17 58

Power System Protection for Engineers – PROT 401

Section 9 - Digital Signal Processing

Questions

z How does a harmonic affect

microprocessor distance relays with a

Cosine filter?

z What is the function of the analog low-

pass filter?

z How does higher sampling rate affect

relay operating speed?

z Does a relay always take filter window

time to clear a fault?

Digital Signal Processing_r17 59

You might also like

- SEL 13 - PROT401 - LinePilotProtection - r4Document56 pagesSEL 13 - PROT401 - LinePilotProtection - r4bureyh98No ratings yet

- 03 PROT405 IndustrialPowerSystemProt r4Document79 pages03 PROT405 IndustrialPowerSystemProt r4Hector AguilarNo ratings yet

- Comunications FundamentalsDocument271 pagesComunications FundamentalsDiego100% (1)

- Manual Utilizador TD420 - Ed1 - 2.2.0 - Uk PDFDocument457 pagesManual Utilizador TD420 - Ed1 - 2.2.0 - Uk PDFPaulo MandingaNo ratings yet

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet

- Power System Protection Course AgendaDocument3 pagesPower System Protection Course AgendaABHINAV SAURAVNo ratings yet

- Substation Comms IntroDocument23 pagesSubstation Comms IntroNeelakandan MasilamaniNo ratings yet

- Session 22 - APPS - Substation Comms Intro PDFDocument46 pagesSession 22 - APPS - Substation Comms Intro PDFmubarakkirko100% (1)

- UNCC 2013 WorkshopDocument241 pagesUNCC 2013 WorkshopRicardo HungriaNo ratings yet

- RSTP PRP HSRDocument32 pagesRSTP PRP HSRShan DeepNo ratings yet

- 00b - PROT 401 Agenda and TOC 20050216 StudentDocument3 pages00b - PROT 401 Agenda and TOC 20050216 Studentراكان خالدNo ratings yet

- Discrete Wavelet Transforms - Algorithms and Applications PDFDocument308 pagesDiscrete Wavelet Transforms - Algorithms and Applications PDFabhishek sharmaNo ratings yet

- Poweredge Recloserscontrols PDFDocument159 pagesPoweredge Recloserscontrols PDFkhoaminh97No ratings yet

- 2 Teleprotection - 2Document21 pages2 Teleprotection - 2sabill arasyidNo ratings yet

- Modbus CommunicationDocument6 pagesModbus CommunicationRakeysh SharmaNo ratings yet

- Arc Model PDFDocument67 pagesArc Model PDFdankorankoNo ratings yet

- Security-Chapter1 - 1 - Intro - 1.0 - v1.0 PDFDocument18 pagesSecurity-Chapter1 - 1 - Intro - 1.0 - v1.0 PDFAlexandra Buendia100% (1)

- 6 Energy InfrastructureDocument32 pages6 Energy InfrastructuremeraatNo ratings yet

- 16mpe05 Completeissue PDFDocument124 pages16mpe05 Completeissue PDFDaniel AlvaradoNo ratings yet

- Hands-On Exercise: Arc-Flash Job Done Settings and Testing ExampleDocument5 pagesHands-On Exercise: Arc-Flash Job Done Settings and Testing Exampleabdelmouen larfiNo ratings yet

- 03 TLP Using Directional Overcurrent Elements Part I r5Document46 pages03 TLP Using Directional Overcurrent Elements Part I r5afmNo ratings yet

- François GallonDocument47 pagesFrançois Gallontiny_nithNo ratings yet

- Substation Communications: An Introduction to Protocols and StandardsDocument23 pagesSubstation Communications: An Introduction to Protocols and StandardsnooralhudNo ratings yet

- Application of Sectionalizers On Distribution SystemDocument8 pagesApplication of Sectionalizers On Distribution SystemRafat ThongNo ratings yet

- FOLD presentation-WAMSDocument41 pagesFOLD presentation-WAMShemanth727No ratings yet

- 03b App751 Optional Ocelementshandson r9 PDFDocument8 pages03b App751 Optional Ocelementshandson r9 PDFabdelmouen larfiNo ratings yet

- A2C4 39+Electrical+Transient+InteractionDocument66 pagesA2C4 39+Electrical+Transient+InteractionicovinyNo ratings yet

- 110KV BUS BAR SchemeDocument35 pages110KV BUS BAR Schememaxwell parassiNo ratings yet

- Diagnostic Measurements On Instrument TransformersDocument7 pagesDiagnostic Measurements On Instrument TransformersMauricio AgudeloNo ratings yet

- 11-Nonconv CT and VTDocument29 pages11-Nonconv CT and VTCarlos PlaceresNo ratings yet

- PID Control ExplainedDocument29 pagesPID Control Explainedsrikanthislavatu7615No ratings yet

- Model Development and Validation of Brushless ExcitersDocument8 pagesModel Development and Validation of Brushless ExcitersAmberMeerabNo ratings yet

- ABB Connectivity PackagesDocument102 pagesABB Connectivity Packagestin_gabby4876100% (1)

- 329 Guidelines For Specification and Evaluation of Substation Automation SystemsDocument90 pages329 Guidelines For Specification and Evaluation of Substation Automation Systemsgefregmail.comNo ratings yet

- 4 - SIPROTEC 5 - Applications OverviewDocument12 pages4 - SIPROTEC 5 - Applications OverviewHafid BaradjaNo ratings yet

- Power System Protection ECE 456Document50 pagesPower System Protection ECE 456Praveen Paul100% (1)

- Dynamic Structural Rigid and Flexible Bus Design in Air Insulated SubstationsDocument8 pagesDynamic Structural Rigid and Flexible Bus Design in Air Insulated SubstationsnashapkNo ratings yet

- Protección Diferencial de Barras DistribuidaDocument15 pagesProtección Diferencial de Barras DistribuidayesrojasNo ratings yet

- 998 1175581 Harmonic Mitigation SolutionDocument10 pages998 1175581 Harmonic Mitigation SolutionSing-Yew LAMNo ratings yet

- Power Plant Protection CoordinationDocument200 pagesPower Plant Protection Coordinationesee57No ratings yet

- Flashover Model of Arcing Horn in Transient SimulationDocument5 pagesFlashover Model of Arcing Horn in Transient SimulationNovia Khoirul AnnisaNo ratings yet

- Automatic Fault Analysis in Power System PDFDocument171 pagesAutomatic Fault Analysis in Power System PDFAshok KumarNo ratings yet

- Impact of HVDC Stations On Protection of AC Systems: Working Group JWG B5/B4.25Document84 pagesImpact of HVDC Stations On Protection of AC Systems: Working Group JWG B5/B4.25Billy ConnorNo ratings yet

- Investigation+of+Magnetizing+Inrush+Current+in+a+Single PhasetransformerDocument6 pagesInvestigation+of+Magnetizing+Inrush+Current+in+a+Single PhasetransformerpcelisNo ratings yet

- 04a Traditional Directional Relays Exercise r6Document6 pages04a Traditional Directional Relays Exercise r6afmNo ratings yet

- RET 630 Differential ProtectionDocument33 pagesRET 630 Differential ProtectionNarvin Raj ChandraNo ratings yet

- Synchronized phasor measurements in power systems reviewDocument7 pagesSynchronized phasor measurements in power systems reviewmgavrilasNo ratings yet

- Sync Check With Voltage Selection and VTs With Different Ratio enDocument8 pagesSync Check With Voltage Selection and VTs With Different Ratio enJose Antonio Huamani ChuquirimayNo ratings yet

- 07a - Instrument - Transformers - Tech - r8 401Document77 pages07a - Instrument - Transformers - Tech - r8 401tajudeen100% (1)

- Distribution Device CoordinationDocument60 pagesDistribution Device CoordinationCatrina FedericoNo ratings yet

- Smart Grid Future PDFDocument40 pagesSmart Grid Future PDFPoojaNo ratings yet

- Power System Protection Presentation Dated 03-10-2013 Integrated Protection ControlDocument89 pagesPower System Protection Presentation Dated 03-10-2013 Integrated Protection ControlNagarajan GanesanNo ratings yet

- ATPDraw - Graphical Preprocessor for ATP-EMTP Circuit SimulationsDocument27 pagesATPDraw - Graphical Preprocessor for ATP-EMTP Circuit SimulationsdbzoNo ratings yet

- COMPUTER METHODS IN POWER SYSTEMS NOTESDocument58 pagesCOMPUTER METHODS IN POWER SYSTEMS NOTESPower System Analysis-1No ratings yet

- Jlpea 05 00234Document23 pagesJlpea 05 00234alokNo ratings yet

- Introduction To Digital Signal Processing: Dr. Hugh Blanton ENTC 4347Document16 pagesIntroduction To Digital Signal Processing: Dr. Hugh Blanton ENTC 4347nikika1No ratings yet

- What Is Analog-To-Digital Conversion (ADC)Document7 pagesWhat Is Analog-To-Digital Conversion (ADC)SmiLy PeRsoNNo ratings yet

- Unit-1 Introduction To Digital Signal ProcessingDocument3 pagesUnit-1 Introduction To Digital Signal Processingpratik2882002No ratings yet

- Digital Signal Processing - An IntroductionDocument35 pagesDigital Signal Processing - An Introductionmeseret sisayNo ratings yet

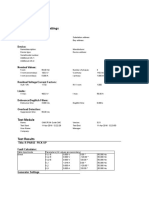

- Quickcmc1: Test Object - Device SettingsDocument18 pagesQuickcmc1: Test Object - Device SettingstajudeenNo ratings yet

- Quickcmc1: Test Object - Device SettingsDocument21 pagesQuickcmc1: Test Object - Device SettingstajudeenNo ratings yet

- Quickcmc1: Test Object - Device SettingsDocument18 pagesQuickcmc1: Test Object - Device SettingstajudeenNo ratings yet

- Quickcmc1: Test Object - Device SettingsDocument21 pagesQuickcmc1: Test Object - Device SettingstajudeenNo ratings yet

- Quickcmc1: Test Object - Device SettingsDocument21 pagesQuickcmc1: Test Object - Device SettingstajudeenNo ratings yet

- Device settings and test resultsDocument18 pagesDevice settings and test resultstajudeenNo ratings yet

- Available Fault Current Calculation: 0 I kVA X 1000 Trans. FLADocument6 pagesAvailable Fault Current Calculation: 0 I kVA X 1000 Trans. FLAtajudeenNo ratings yet

- Device settings and test resultsDocument18 pagesDevice settings and test resultstajudeenNo ratings yet

- Quickcmc1: Test Object - Device SettingsDocument18 pagesQuickcmc1: Test Object - Device SettingstajudeenNo ratings yet

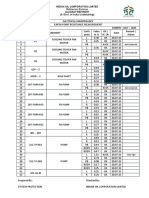

- Test Certificate of Energy Meter J K Cement Works, Nimbahera / Thermax LTDDocument7 pagesTest Certificate of Energy Meter J K Cement Works, Nimbahera / Thermax LTDtajudeenNo ratings yet

- Quickcmc1: Test Object - Device SettingsDocument21 pagesQuickcmc1: Test Object - Device SettingstajudeenNo ratings yet

- Electrical Equipment Earth Point Resistance MeasurementsDocument13 pagesElectrical Equipment Earth Point Resistance MeasurementstajudeenNo ratings yet

- Quickcmc1: Test Object - Device SettingsDocument21 pagesQuickcmc1: Test Object - Device SettingstajudeenNo ratings yet

- Quickcmc1: Test Object - Device SettingsDocument21 pagesQuickcmc1: Test Object - Device SettingstajudeenNo ratings yet

- NM, GuguDocument2 pagesNM, GugutajudeenNo ratings yet

- Xjba KJBXDocument23 pagesXjba KJBXtajudeenNo ratings yet

- Device settings and test resultsDocument16 pagesDevice settings and test resultstajudeenNo ratings yet

- Device settings and test resultsDocument18 pagesDevice settings and test resultstajudeenNo ratings yet

- Quickcmc1: Test ModuleDocument3 pagesQuickcmc1: Test ModuletajudeenNo ratings yet

- Device settings and test resultsDocument21 pagesDevice settings and test resultstajudeenNo ratings yet

- HvavbcjDocument5 pagesHvavbcjtajudeenNo ratings yet

- Device settings and test resultsDocument18 pagesDevice settings and test resultstajudeenNo ratings yet

- Quickcmc1: Test ModuleDocument3 pagesQuickcmc1: Test ModuletajudeenNo ratings yet

- Quickcmc1: Test Object - Device SettingsDocument18 pagesQuickcmc1: Test Object - Device SettingstajudeenNo ratings yet

- Quickcmc1: Test ModuleDocument3 pagesQuickcmc1: Test ModuletajudeenNo ratings yet

- Quickcmc1: Test ModuleDocument3 pagesQuickcmc1: Test ModuletajudeenNo ratings yet

- Quickcmc1: Test ModuleDocument12 pagesQuickcmc1: Test ModuletajudeenNo ratings yet

- QuickCMC1 UV PICK UP TestsDocument4 pagesQuickCMC1 UV PICK UP TeststajudeenNo ratings yet

- Quickcmc1: Test Object - Device SettingsDocument18 pagesQuickcmc1: Test Object - Device SettingstajudeenNo ratings yet

- Quickcmc1: Test ModuleDocument12 pagesQuickcmc1: Test ModuletajudeenNo ratings yet

- Infographic Registration of Pharmaceutical Product For General Sale 637828524496205508Document1 pageInfographic Registration of Pharmaceutical Product For General Sale 637828524496205508Kdp03No ratings yet

- Bangla FoodsDocument6 pagesBangla FoodsSubadrika DarmadewiNo ratings yet

- Development of Automatic Mini Fan with PIR SensorDocument8 pagesDevelopment of Automatic Mini Fan with PIR SensorToheebdareNo ratings yet

- ASPE Data Book Volume 1 & 2 - Attachment For Pump Head CalculationDocument2 pagesASPE Data Book Volume 1 & 2 - Attachment For Pump Head CalculationibnrafeeqNo ratings yet

- English 8-Quiz On Context CluesDocument2 pagesEnglish 8-Quiz On Context CluesMELINDA FERRERNo ratings yet

- Manifest Guide Ebook PDFDocument4 pagesManifest Guide Ebook PDFAnonymous dqCHWEADzNo ratings yet

- Comprehension Y9aDocument9 pagesComprehension Y9angwenping5No ratings yet

- Subway's Fresh Look: CEO Suzanne Greco Is Taking The Company To A Whole New Level With The Fresh Forward RebrandDocument9 pagesSubway's Fresh Look: CEO Suzanne Greco Is Taking The Company To A Whole New Level With The Fresh Forward RebrandTanvir KhanNo ratings yet

- JW1782BDocument13 pagesJW1782BGustavo AlonsoNo ratings yet

- Structural Dyanmics-Anna University Q PaperDocument7 pagesStructural Dyanmics-Anna University Q PaperVijay AravindNo ratings yet

- Paper1202169 2180 PDFDocument12 pagesPaper1202169 2180 PDFManish AnandNo ratings yet

- Stress 1Document28 pagesStress 1DrAma StabLeNo ratings yet

- F 25 Sensor Family Miniature Sensors for Precision DetectionDocument34 pagesF 25 Sensor Family Miniature Sensors for Precision DetectionAlex GarduñoNo ratings yet

- Cambridge English Pre A1 Starters Classroom Activities PDFDocument16 pagesCambridge English Pre A1 Starters Classroom Activities PDFFrank Guevara100% (2)

- Dynamic Simulation of Insulin-Glucose Interaction in Type 1 Diabetes With MATLAB Simulink®Document11 pagesDynamic Simulation of Insulin-Glucose Interaction in Type 1 Diabetes With MATLAB Simulink®Jonas KristantoNo ratings yet

- Sample Weekly Home Learning PlansDocument2 pagesSample Weekly Home Learning PlansJINGKY HUMAMOYNo ratings yet

- Honda Civic OBD0 EF ECU PINOUTS - My Pro Street PDFDocument11 pagesHonda Civic OBD0 EF ECU PINOUTS - My Pro Street PDFWill ?100% (2)

- CerebrumDocument26 pagesCerebrumsanthiyasandy100% (1)

- Nike Run Club 5K Training PlanDocument25 pagesNike Run Club 5K Training PlanSalvador0% (1)

- Toyota Forklift 42 6fgcu15!42!6fgcu18 Parts CatalogDocument22 pagesToyota Forklift 42 6fgcu15!42!6fgcu18 Parts Catalogjosephrichards120800wpq100% (110)

- Pump CommissioningDocument1 pagePump CommissioningMD SAMANNo ratings yet

- Realtime Physics: Active Learning Labs Transforming The Introductory LaboratoryDocument14 pagesRealtime Physics: Active Learning Labs Transforming The Introductory LaboratorysaleemNo ratings yet

- EA PSC Substation Earthing Course Leaflet PSC006CL MAR15Document2 pagesEA PSC Substation Earthing Course Leaflet PSC006CL MAR15David RothwellNo ratings yet

- FCL Shipment Specific Quotation For BRIDGESTONE AMERICAS INCDocument3 pagesFCL Shipment Specific Quotation For BRIDGESTONE AMERICAS INCmustova81No ratings yet

- Operations ManualDocument534 pagesOperations ManualAlthea Joy Castor SobretodoNo ratings yet

- Public List Programs by Specialty 460Document9 pagesPublic List Programs by Specialty 460Enta SyngNo ratings yet

- Mapsco Street GuidesDocument5 pagesMapsco Street Guidesapi-256961360No ratings yet

- Determination of Equilibrium Constant (KeqDocument0 pagesDetermination of Equilibrium Constant (KeqPablo BernalNo ratings yet

- Ch.2 Case and Duct SystemDocument11 pagesCh.2 Case and Duct Systemcpt.ghostNo ratings yet

- Meng 2nd Year Death Anniversary MassDocument6 pagesMeng 2nd Year Death Anniversary Massjoy in the spirit of the lordNo ratings yet