Professional Documents

Culture Documents

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A Synchronous 4-Bit Up/Down Binary Counters

Uploaded by

Gregorito Torrejano MunevarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A Synchronous 4-Bit Up/Down Binary Counters

Uploaded by

Gregorito Torrejano MunevarCopyright:

Available Formats

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

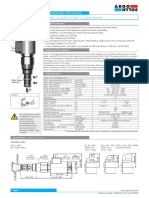

• Fully Synchronous Operation for Counting SN54ALS169B, SN54AS169A . . . J PACKAGE

and Programming SN74ALS169B, SN74AS169A . . . D OR N PACKAGE

(TOP VIEW)

• Internal Carry Look-Ahead Circuitry for

Fast Counting

U/D 1 16 VCC

• Carry Output for n-Bit Cascading CLK 2 15 RCO

• Fully Independent Clock Circuit A 3 14 QA

• Package Options Include Plastic B 4 13 QB

Small-Outline (D) Packages, Ceramic Chip C 5 12 QC

Carriers (FK), and Standard Plastic (N) and D 6 11 QD

Ceramic (J) 300-mil DIPs ENP 7 10 ENT

GND 8 9 LOAD

description

These synchronous 4-bit up/down binary SN54ALS169B, SN54AS169A . . . FK PACKAGE

presettable counters feature an internal carry (TOP VIEW)

look-ahead circuitry for cascading in high-speed

RCO

CLK

VCC

U/D

counting applications. Synchronous operation is

NC

provided by having all flip-flops clocked

simultaneously so that the outputs change 3 2 1 20 19

coincident with each other when so instructed by A 4 18 QA

the count-enable (ENP, ENT) inputs and internal B 5 17 QB

gating. This mode of operation eliminates the NC 6 16 NC

output counting spikes normally associated with C 7 15 QC

asynchronous (ripple-clock) counters. A buffered D 8 14 QD

9 10 11 12 13

clock (CLK) input triggers the four flip-flops on the

ENP

NC

LOAD

ENT

GND

rising (positive-going) edge of the clock waveform.

These counters are fully programmable; that is,

they may be preset to either level. The load-input NC – No internal connection

circuitry allows loading with the carry-enable

output of cascaded counters. Because loading is

synchronous, setting up a low level at the load

(LOAD) input disables the counter and causes the

outputs to agree with the data inputs after the next

clock pulse.

The internal carry look-ahead circuitry provides for cascading counters for n-bit synchronous application without

additional gating. ENP and ENT inputs and a ripple-carry output (RCO) are instrumental in accomplishing this

function. Both ENP and ENT must be low to count. The direction of the count is determined by the level of the

up/down (U/D) input. When U/D is high, the counter counts up; when low, it counts down. ENT is fed forward

to enable RCO. RCO, thus enabled, produces a low-level pulse while the count is zero (all inputs low) counting

down or maximum (15) counting up. This low-level overflow ripple-carry pulse can be used to enable successive

cascaded stages. Transitions at ENP or ENT are allowed regardless of the level of the clock input. All inputs

are diode clamped to minimize transmission-line effects, thereby simplifying system design.

These counters feature a fully independent clock circuit. Changes at control inputs (ENP, ENT, LOAD, or U/D)

that modify the operating mode have no effect on the contents of the counter until clocking occurs. The function

of the counter (whether enabled, disabled, loading, or counting) is dictated solely by the conditions meeting the

stable setup and hold times.

The SN54ALS169B and SN54AS169A are characterized for operation over the full military temperature range

of – 55°C to 125°C. The SN74ALS169B and SN74AS169A are characterized for operation from 0°C to 70°C.

PRODUCTION DATA information is current as of publication date. Copyright 1994, Texas Instruments Incorporated

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 2–1

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

logic symbol†

CTRDIV16

9

LOAD M1 [LOAD]

M2 [COUNT]

1

U/D M3 [UP]

M4 [DOWN] 15

10 3,5CT=15 RCO

ENT G5

7 4,5CT=0

ENP G6

2

CLK 2,3,5,6+/C7

2,4,5,6 –

3 14

A 1, 7D 1 QA

4 13

B 2 QB

5 12

C 4 QC

6 11

D 8 QD

† This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the D, J, and N packages.

2–2 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

logic diagram (positive logic)

9

LOAD

1 15

U/D RCO

10

ENT

7

ENP

C1

2 14

CLK 1D QA

3

A

C1

13

1D QB

4

B

C1

12

1D QC

5

C

C1

11

1D QD

6

D

Pin numbers shown are for the D, J, and N packages.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 2–3

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

typical load, count, and inhibit sequences

The following sequence is illustrated below:

1. Load (preset) to binary 13

2. Count up to 14, 15 (maximum), 0, 1, and 2

3. Inhibit

4. Count down to 1, 0 (minimum), 15, 14, and 13

LOAD

B

Data

Inputs

C

CLK

U/D

ENP and ENT

QA

QB

Data

Outputs

QC

QD

RCO

13 14 15 0 1 2 2 2 1 0 15 14 13

Count Up Inhibit Count Down

Load

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

Supply voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Input voltage, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Operating free-air temperature range, TA: SN54ALS169B . . . . . . . . . . . . . . . . . . . . . . . . . . . – 55°C to 125°C

SN74ALS169B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to 70°C

Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 65°C to 150°C

† Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2–4 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

recommended operating conditions

SN54ALS169B SN74ALS169B

UNIT

MIN NOM MAX MIN NOM MAX

VCC Supply voltage 4.5 5 5.5 4.5 5 5.5 V

VIH High-level input voltage 2 2 V

VIL Low-level input voltage 0.7 0.8 V

IOH High-level output current – 0.4 – 0.4 mA

IOL Low-level output current 4 8 mA

fclock Clock frequency 0 22 0 40 MHz

tw Pulse duration, CLK high or low 14 12.5 ns

A, B, C, or D 20 15

ENP or ENT 25 15

tsu ↑

Setup time before CLK↑ ns

LOAD 20 15

U/D 28 15

th Hold time, data after CLK↑ 0 0 ns

TA Operating free-air temperature – 55 125 0 70 °C

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

SN54ALS169B SN74ALS169B

PARAMETER TEST CONDITIONS UNIT

MIN TYP† MAX MIN TYP† MAX

VIK VCC = 4.5 V, II = – 18 mA – 1.5 – 1.5 V

VOH VCC = 4.5 V to 5.5 V, IOH = – 0.4 mA VCC – 2 VCC – 2 V

IOL = 4 mA 0.25 0.4 0.25 0.4

VOL VCC = 4

4.5

5V V

IOL = 8 mA 0.35 0.5

II VCC = 5.5 V, VI = 7 V 0.1 0.1 mA

IIH VCC = 5.5 V, VI = 2.7 V 20 20 µA

IIL VCC = 5.5 V, VI = 0.4 V – 0.2 – 0.2 mA

IO‡ VCC = 5.5 V, VO = 2.25 V – 20 – 112 – 30 – 112 mA

ICC VCC = 5.5 V 15 25 15 25 mA

† All typical values are at VCC = 5 V, TA = 25°C.

‡ The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 2–5

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

switching characteristics (see Figure 1)

VCC = 4.5 V to 5.5 V,

CL = 50 pF,

FROM TO RL = 500 Ω,

PARAMETER

(INPUT) (OUTPUT) TA = MIN to MAX† UNIT

SN54ALS169B SN74ALS169B

MIN MAX MIN MAX

fmax 22 40 MHz

tPLH 3 20 3 20

CLK RCO ns

tPHL 6 25 6 20

tPLH 2 20 2 15

CLK Any Q ns

tPHL 5 23 5 20

tPLH 2 16 2 13

ENT RCO ns

tPHL 3 24 3 16

tPLH 4 22 5 19

U/D RCO ns

tPHL 5 26 5 19

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)‡

Supply voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Input voltage, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Operating free-air temperature range, TA: SN54AS169A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 55°C to 125°C

SN74AS169A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to 70°C

Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 65°C to 150°C

‡ Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

recommended operating conditions

SN54AS169A SN74AS169A

UNIT

MIN NOM MAX MIN NOM MAX

VCC Supply voltage 4.5 5 5.5 4.5 5 5.5 V

VIH High-level input voltage 2 2 V

VIL Low-level input voltage 0.8 0.8 V

IOH High-level output current –2 –2 mA

IOL Low-level output current 20 20 mA

fclock* Clock frequency 0 60 0 75 MHz

tw* Pulse duration, CLK high or low 7.7 6.7 ns

A, B, C, or D 10 8

ENP or ENT 10 8

tsu* ↑

Setup time before CLK↑ ns

LOAD 10 8

U/D 14 11

th* Hold time, data after CLK↑ 2 0 ns

TA Operating free-air temperature – 55 125 0 70 °C

* On products compliant to MIL-STD-883, Class B, this parameter is based on characterization data but is not production tested.

2–6 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

SN54AS169A SN74AS169A

PARAMETER TEST CONDITIONS UNIT

MIN TYP† MAX MIN TYP† MAX

VIK VCC = 4.5 V, II = – 18 mA – 1.2 – 1.2 V

VOH VCC = 4.5 V to 5.5 V, IOH = – 2 mA VCC – 2 VCC – 2 V

VOL VCC = 4.5 V, IOL = 20 mA 0.25 0.5 0.25 0.5 V

LOAD, ENT, U/D 0.2 0.2

II VCC = 5 5V

5.5 V, VI = 7 V mA

All others 0.1 0.1

LOAD, ENT, U/D 40 40

IIH VCC = 5

5.5

5VV, VI = 2

2.7

7V µA

All others 20 20

LOAD, ENT, U/D –1 –1

IIL VCC = 5

5.5

5VV, VI = 0

0.4

4V mA

All others – 0.5 – 0.5

IO‡ VCC = 5.5 V, VO = 2.25 V – 30 – 112 – 30 – 112 mA

ICC VCC = 5.5 V 41 63 41 63 mA

† All typical values are at VCC = 5 V, TA = 25°C.

‡ The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

switching characteristics (see Figure 1)

VCC = 4.5 V to 5.5 V,

CL = 50 pF,

FROM TO RL = 500 Ω,

PARAMETER

(INPUT) (OUTPUT) TA = MIN to MAX§ UNIT

SN54AS169A SN74AS169A

MIN MAX MIN MAX

fmax* 60 75 MHz

tPLH RCO 3 17.5 3 16.5

CLK ns

tPHL (LOAD high or low) 2 14 2 13

tPLH 1 7.5 1 7

CLK Any Q ns

tPHL 2 14 2 13

tPLH 1.5 10 1.5 9

ENT RCO ns

tPHL 1.5 10 1.5 9

tPLH 2 14 2 12

U/D RCO ns

tPHL 2 14.5 2 13

* On products compliant to MIL-STD-883, Class B, this parameter is based on characterization data but is not production tested.

§ For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 2–7

SN54ALS169B, SN54AS169A, SN74ALS169B, SN74AS169A

SYNCHRONOUS 4-BIT UP/DOWN BINARY COUNTERS

SDAS125B – MARCH 1984 – REVISED DECEMBER 1994

PARAMETER MEASUREMENT INFORMATION

SERIES 54ALS/74ALS AND 54AS/74AS DEVICES

7V

VCC RL = R1 = R2

S1

RL

R1

From Output Test From Output Test From Output Test

Under Test Point Under Test Point Under Test Point

CL RL CL

CL R2

(see Note A) (see Note A)

(see Note A)

LOAD CIRCUIT FOR

BI-STATE LOAD CIRCUIT LOAD CIRCUIT

TOTEM-POLE OUTPUTS FOR OPEN-COLLECTOR OUTPUTS FOR 3-STATE OUTPUTS

Timing 3.5 V High-Level 3.5 V

Input 1.3 V Pulse 1.3 V 1.3 V

0.3 V 0.3 V

th tw

tsu

3.5 V 3.5 V

Data Low-Level

Input 1.3 V 1.3 V 1.3 V 1.3 V

Pulse

0.3 V 0.3 V

VOLTAGE WAVEFORMS VOLTAGE WAVEFORMS

SETUP AND HOLD TIMES PULSE DURATIONS

3.5 V

Output

Control 1.3 V 1.3 V

(low-level

enabling) 0.3 V 3.5 V

tPZL Input 1.3 V 1.3 V

tPLZ

[3.5 V 0.3 V

tPHL

Waveform 1 tPLH

S1 Closed 1.3 V

In-Phase VOH

(see Note B) 1.3 V 1.3 V

VOL Output

tPHZ 0.3 V VOL

tPZH tPLH

VOH tPHL

Waveform 2 VOH

Out-of-Phase

S1 Open 1.3 V 0.3 V 1.3 V 1.3 V

Output

(see Note B)

[0 V (see Note C) VOL

VOLTAGE WAVEFORMS VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS PROPAGATION DELAY TIMES

NOTES: A. CL includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. When measuring propagation delay items of 3-state outputs, switch S1 is open.

D. All input pulses have the following characteristics: PRR ≤ 1 MHz, tr = tf = 2 ns, duty cycle = 50%.

E. The outputs are measured one at a time with one transition per measurement.

Figure 1. Load Circuits and Voltage Waveforms

2–8 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

You might also like

- AS380 Integrated Drive Instruction Manual.Document271 pagesAS380 Integrated Drive Instruction Manual.Rebecca Dang100% (1)

- D D D D D: SN54ALS191A, SN74ALS191A Synchronous 4-Bit Up/Down Binary CountersDocument8 pagesD D D D D: SN54ALS191A, SN74ALS191A Synchronous 4-Bit Up/Down Binary CountersJaviNo ratings yet

- Synchronous 4-Bit Binary CounterDocument17 pagesSynchronous 4-Bit Binary Counteryogendra.shethNo ratings yet

- Synchronous 4-Bit Up/Down Counter SN54/74LS669: Low Power SchottkyDocument4 pagesSynchronous 4-Bit Up/Down Counter SN54/74LS669: Low Power Schottkyzequinhawins100% (1)

- 74LS190Document8 pages74LS190jaja558No ratings yet

- Datasheet 74192Document7 pagesDatasheet 74192phongbui135100% (3)

- Sn74ls165a PDFDocument16 pagesSn74ls165a PDFRachid RifaiNo ratings yet

- D D D D: SN54165, SN54LS165A, SN74165, SN74LS165A Parallel-Load 8-Bit Shift RegistersDocument23 pagesD D D D: SN54165, SN54LS165A, SN74165, SN74LS165A Parallel-Load 8-Bit Shift RegistersВиктор АгарковNo ratings yet

- Datasheet PDFDocument9 pagesDatasheet PDFChathura PriyankaNo ratings yet

- 74ls163 DatasheetDocument6 pages74ls163 DatasheetFernando LMNo ratings yet

- SN54/74LS160A SN54/74LS161A SN54/74LS162A SN54/74LS163A: Low Power SchottkyDocument5 pagesSN54/74LS160A SN54/74LS161A SN54/74LS162A SN54/74LS163A: Low Power Schottkygd8uj123No ratings yet

- D D D D D D D D D D D: Description/ordering InformationDocument16 pagesD D D D D D D D D D D: Description/ordering InformationJay rayNo ratings yet

- AC74Document17 pagesAC74Guido UribeNo ratings yet

- 74LS161 3Document6 pages74LS161 3Mohammd EssaNo ratings yet

- Onsms12244 1Document8 pagesOnsms12244 1HeartBraveNo ratings yet

- RegisterDocument12 pagesRegisterjairomarcanoNo ratings yet

- D D D D D D D D: TLV1549C, TLV1549I, TLV1549M 10-Bit Analog-To-Digital Converters With Serial ControlDocument15 pagesD D D D D D D D: TLV1549C, TLV1549I, TLV1549M 10-Bit Analog-To-Digital Converters With Serial ControlmoocomNo ratings yet

- 74 HC 595Document27 pages74 HC 595Lu HoaNo ratings yet

- SN 74 HC 595Document27 pagesSN 74 HC 595chrisNo ratings yet

- MC74HC161A MotorolaDocument12 pagesMC74HC161A MotorolaMed SamiNo ratings yet

- D D D D D: SN54HC165, SN74HC165 8-Bit Parallel-Load Shift RegistersDocument8 pagesD D D D D: SN54HC165, SN74HC165 8-Bit Parallel-Load Shift RegistersvetchboyNo ratings yet

- SN74LS193Document11 pagesSN74LS193HeartBraveNo ratings yet

- D D D D D D: LM111, LM211, LM311 Differential Comparators With StrobesDocument25 pagesD D D D D D: LM111, LM211, LM311 Differential Comparators With StrobesPé Lê Dzăn ĐạtNo ratings yet

- LM 311Document28 pagesLM 311Cubelinho ResuaNo ratings yet

- SN 74 HC 166Document35 pagesSN 74 HC 166Carlos OrtegaNo ratings yet

- Datasheet Ic 74hc165aDocument9 pagesDatasheet Ic 74hc165aNayla AzzahraNo ratings yet

- Datasheet Digital 74hcDocument10 pagesDatasheet Digital 74hcСтанислав ИвановNo ratings yet

- NE555Document15 pagesNE555api-3825669No ratings yet

- Ne 555Document24 pagesNe 555Otto Yhoda Alvarez DevarsNo ratings yet

- D D D D: Description/ordering InformationDocument24 pagesD D D D: Description/ordering InformationOmnhickNo ratings yet

- Description: Sn54F374 - . - J Package Sn74F374 - . - DB, DW, or N Package (Top View)Document23 pagesDescription: Sn54F374 - . - J Package Sn74F374 - . - DB, DW, or N Package (Top View)MikasaNo ratings yet

- SN54ALS74A, SN54AS74A, SN74ALS74A, SN74AS74A Dual Positive-Edge-Triggered D-Type Flip-Flops With Clear and PresetDocument7 pagesSN54ALS74A, SN54AS74A, SN74ALS74A, SN74AS74A Dual Positive-Edge-Triggered D-Type Flip-Flops With Clear and PresetIsabella FernandezNo ratings yet

- Archive: DatasheetDocument25 pagesArchive: DatasheetDidier DoradoNo ratings yet

- SN54173, SN54LS173A, SN74173, SN74LS173A 4-Bit D-Type Registers With 3-State OutputsDocument19 pagesSN54173, SN54LS173A, SN74173, SN74LS173A 4-Bit D-Type Registers With 3-State OutputsJanet WaldeNo ratings yet

- SN54173, SN54LS173A, SN74173, SN74LS173A 4-Bit D-Type Registers With 3-State OutputsDocument13 pagesSN54173, SN54LS173A, SN74173, SN74LS173A 4-Bit D-Type Registers With 3-State OutputsMauricio MontañoNo ratings yet

- SN54HCT74-SN74HCT74 - Flip FlopDocument15 pagesSN54HCT74-SN74HCT74 - Flip FlopTiago LeonhardtNo ratings yet

- SN54ACT574, SN74ACT574 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsDocument6 pagesSN54ACT574, SN74ACT574 Octal D-Type Edge-Triggered Flip-Flops With 3-State OutputsYenco Barliza DiazNo ratings yet

- Datasheet - 555Document15 pagesDatasheet - 555Javier RenanNo ratings yet

- D D D D D D: Description/ordering InformationDocument17 pagesD D D D D D: Description/ordering InformationBryan David Caceres DuarteNo ratings yet

- 74LS192Document9 pages74LS192jaja558No ratings yet

- D D D D D D: SN54HC74, SN74HC74 Dual D-Type Positive-Edge-Triggered Flip-Flops With Clear and PresetDocument24 pagesD D D D D D: SN54HC74, SN74HC74 Dual D-Type Positive-Edge-Triggered Flip-Flops With Clear and PresetViola Safa Nur AnnisaNo ratings yet

- SG3526Document11 pagesSG3526RocioLLactaMartinezNo ratings yet

- Synchronous Presettable BCD Decade Counter MC74F160A MC74F162ADocument4 pagesSynchronous Presettable BCD Decade Counter MC74F160A MC74F162AdavidNo ratings yet

- Up/down Binary Counter With Separate Up/down Clocks: Integrated CircuitsDocument12 pagesUp/down Binary Counter With Separate Up/down Clocks: Integrated CircuitsMarco Aurélio BagioNo ratings yet

- 74LS374Document24 pages74LS374aasadad100% (1)

- SN 74 Ls 374Document32 pagesSN 74 Ls 374Ajish joNo ratings yet

- SN54LS373, SN54LS374, SN54S373, SN54S374, SN74LS373, SN74LS374, SN74S373, SN74S374 Octal D-Type Transparent Latches and Edge-Triggered Flip-FlopsDocument32 pagesSN54LS373, SN54LS374, SN54S373, SN54S374, SN74LS373, SN74LS374, SN74S373, SN74S374 Octal D-Type Transparent Latches and Edge-Triggered Flip-FlopsMladen VujicicNo ratings yet

- 74LS190Document10 pages74LS190nukachNo ratings yet

- CD4510Document11 pagesCD4510John WoeNo ratings yet

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocument9 pagesHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataSo Was RedNo ratings yet

- Sn74hc76 J-K Flip FlopDocument11 pagesSn74hc76 J-K Flip Flopcarlos tito torresNo ratings yet

- Datasheetarchive 74hc163Document13 pagesDatasheetarchive 74hc163José AdelinoNo ratings yet

- D D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsDocument25 pagesD D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsДрагиша Небитни ТрифуновићNo ratings yet

- Bu4094bc eDocument22 pagesBu4094bc ekami samaNo ratings yet

- 74hc00 NandDocument5 pages74hc00 NandAs'ad ShidqyNo ratings yet

- NCP5212A, NCP5212T Single Synchronous Step-Down Controller: QFN16 Case 485apDocument19 pagesNCP5212A, NCP5212T Single Synchronous Step-Down Controller: QFN16 Case 485apokeinfoNo ratings yet

- Description: Sn54F573 - . - J Package Sn74F573 - . - DW or N Package (Top View)Document5 pagesDescription: Sn54F573 - . - J Package Sn74F573 - . - DW or N Package (Top View)moh hadiNo ratings yet

- E Book EcDocument28 pagesE Book EcYasin Ykz ZNo ratings yet

- B.Sc. (Aviation SC.) (I Sem.)Document3 pagesB.Sc. (Aviation SC.) (I Sem.)Vipan Sharma100% (1)

- Service Manual: SDM-X72Document47 pagesService Manual: SDM-X72kperenNo ratings yet

- NJM4558 NJM4559 E-218630Document5 pagesNJM4558 NJM4559 E-218630Diego EmanuelNo ratings yet

- SP4P2-B3: Proportional Pressure Reducing - Relieving Valve, Pilot OperatedDocument2 pagesSP4P2-B3: Proportional Pressure Reducing - Relieving Valve, Pilot OperatedДима ПолищукNo ratings yet

- Rajat Specifications PDFDocument24 pagesRajat Specifications PDFVirender RanaNo ratings yet

- EL221-Electromechanical System Lab 07: D.C. MachineDocument17 pagesEL221-Electromechanical System Lab 07: D.C. MachineMuhammad AreebNo ratings yet

- 09.01 ICU Rail Valve LeakagesDocument11 pages09.01 ICU Rail Valve LeakagesGennadi JermilovNo ratings yet

- Model: LTA216AT01Document24 pagesModel: LTA216AT01A.b. JethavaNo ratings yet

- Technician Manual: E-Type Electronic Table - Top Autoclaves Models 1730, 2340, 2540, 3140, 3850, 3870 E, Ek, Ea & EkaDocument107 pagesTechnician Manual: E-Type Electronic Table - Top Autoclaves Models 1730, 2340, 2540, 3140, 3850, 3870 E, Ek, Ea & EkaafzaluddinNo ratings yet

- Flip FlopsDocument11 pagesFlip FlopsZakaria JubarnNo ratings yet

- Lab Manual - 1: Ain Shams University Faculty of Engineering CESS ProgramDocument3 pagesLab Manual - 1: Ain Shams University Faculty of Engineering CESS Programninjas zoneNo ratings yet

- A Low-Noise, Non-Contact EEG - ECG Sensor PDFDocument4 pagesA Low-Noise, Non-Contact EEG - ECG Sensor PDFAdrian KippNo ratings yet

- Christmas Tree ProyectDocument16 pagesChristmas Tree Proyectchente_bNo ratings yet

- Chinese DVA PDFDocument8 pagesChinese DVA PDFSOMNATH KHAMARUNo ratings yet

- Protective Relaying and TestingDocument19 pagesProtective Relaying and Testingsherub wangdiNo ratings yet

- Power System Assignment 2Document12 pagesPower System Assignment 2ram010No ratings yet

- Typ. Beam Profile Typ. Beam & Column Profile: Edecorp Design & ConstructionDocument1 pageTyp. Beam Profile Typ. Beam & Column Profile: Edecorp Design & ConstructionEllen De Castro Corpuz0% (1)

- Engineering Circuit Analysis 8th Edition SolutionsDocument68 pagesEngineering Circuit Analysis 8th Edition SolutionsHanaNo ratings yet

- Class 7 Worksheet 25th June - ComputerDocument16 pagesClass 7 Worksheet 25th June - ComputervmhsphysicsNo ratings yet

- Mechanical Completion L.V. Power, Control and Telecomm / Instrument CablesDocument4 pagesMechanical Completion L.V. Power, Control and Telecomm / Instrument CablesJalal AlbadriNo ratings yet

- CYTEC SpindelDocument9 pagesCYTEC Spindel李恩杰No ratings yet

- Satellite Speed CertificateDocument2 pagesSatellite Speed CertificateZafar YabNo ratings yet

- Nmos Design Rules LayoutDocument53 pagesNmos Design Rules Layouttarun aggarwalNo ratings yet

- Smart Grids Section Course Outline-1Document3 pagesSmart Grids Section Course Outline-1Ab CNo ratings yet

- Power Electronics: Application-Induction HeatingDocument20 pagesPower Electronics: Application-Induction Heatingsree_cyberNo ratings yet

- Civil Site Engineer ResponsibilitiesDocument7 pagesCivil Site Engineer ResponsibilitiesApon khanNo ratings yet

- AA-036878-001 - SPREADER BEAMS - H BeamDocument1 pageAA-036878-001 - SPREADER BEAMS - H BeamGaurav BedseNo ratings yet

- PLL Control of DC DriveDocument12 pagesPLL Control of DC DriveRavi ANo ratings yet