Professional Documents

Culture Documents

8086 Opcodes

8086 Opcodes

Uploaded by

Spasmodium0 ratings0% found this document useful (0 votes)

3 views4 pagesOriginal Title

8086 Opcodes - Copy (4).txt

Copyright

© © All Rights Reserved

Available Formats

TXT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as TXT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

3 views4 pages8086 Opcodes

8086 Opcodes

Uploaded by

SpasmodiumCopyright:

© All Rights Reserved

Available Formats

Download as TXT, PDF, TXT or read online from Scribd

You are on page 1of 4

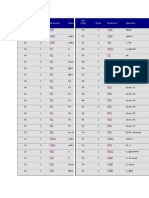

ADC r/m8, reg8 $10

ADC r/m16, reg16 $11

ADC reg8, r/m8 $12

ADC reg16, r/m16 $13

ADC AL, imm8 $14

ADC AX, imm16 $15

ADC r/m8, imm8 $80 010

ADC r/m16, imm16 $81 010

ADC r/m16, imm8 $83 010

ADD r/m8, reg8 $00

ADD r/m16, reg16 $01

ADD reg8, r/m8 $02

ADD reg16, r/m16 $03

ADD AL, imm8 $04

ADD AX, imm16 $05

ADD r/m8, imm8 $80 000

ADD r/m16, imm16 $81 000

ADD r/m16, imm8 $83 000

AND r/m8, reg8 $20

AND r/m16, reg16 $21

AND reg8, r/m8 $22

AND reg16, r/m16 $23

AND AL, imm8 $24

AND AX, imm16 $25

AND r/m8, imm8 $80 100

AND r/m16, imm16 $81 100

AND r/m16, imm8 $83 100

CALL 32-bit displacement $9A

CALL 16-bit displacement $E8

CLD $FC

CMP r/m8, reg8 $38

CMP r/m16, reg16 $39

CMP reg8, r/m8 $3A

CMP reg16, r/m16 $3B

CMP AL, imm8 $3C

CMP AX, imm16 $3D

CMP r/m8, imm8 $80 111

CMP r/m16, imm16 $81 111

CMP r/m16, imm8 $83 111

CMPSB ES:[DI]==DS:[SI] $A6

CMPW ES:[DI]==DS:[SI] $A7

DEC r/m8 $FE 001

DEC r/m16 $FF 001

DEC reg16 $48

DEC reg16 $49

DEC reg16 $4A

DEC reg16 $4B

DEC reg16 $4C

DEC reg16 $4D

DEC reg16 $4E

DEC reg16 $4F

DIV r/m8 $F6 110

DIV r/m16 $F7 110

HLT $F4

IDIV r/m8 $F6 111

IDIV r/m16 $F7 111

IMUL r/m8 $F6 101

IMUL r/m16 $F7 101

IN AL, addr8 $E4

IN AX, addr8 $E5

IN AL, port[DX] $EC

IN AX, port[DX] $ED

INC r/m8 $FE 000

INC r/m16 $FF 000

INC reg16 $40

INC reg16 $41

INC reg16 $42

INC reg16 $43

INC reg16 $44

INC reg16 $45

INC reg16 $46

INC reg16 $47

IRET 48-bit POP $CF

JA 8-bit relative $77

JAE 8-bit relative $73

JB 8-bitrelative $72

JBE 8-bit relative $76

JE 8-bit relative $74

JG 8-bit relative $7F

JGE 8-bit relative $7D

JL 8-bit relative $7C

JLE 8-bit relative $7E

JMP 32-bit displacement $EA

JNE 8-bit relative $75

JZ 8-bit relative $74

LDS reg16, mem32 $C4

LES reg16, mem32 $C5

LODSB AL = DS:[SI] $AC

LODSW AX = DS:[SI] $AD

LOOP 8-bit relative $E2

MOV r/m8, reg8 $88

MOV r/m16, reg16 $89

MOV AL, mem8 $A0

MOV AX, mem16 $A1

MOV mem8, AL $A2

MOV mem16, AX $A3

MOV reg8, imm8 $B0

MOV reg8, imm8 $B1

MOV reg8, imm8 $B2

MOV reg8, imm8 $B3

MOV reg8, imm8 $B4

MOV reg8, imm8 $B5

MOV reg8, imm8 $B6

MOV reg8, imm8 $B7

MOV reg16,imm16 $B8

MOV reg16,imm16 $B9

MOV reg16,imm16 $BA

MOV reg16,imm16 $BB

MOV reg16,imm16 $BC

MOV reg16,imm16 $BD

MOV reg16,imm16 $BE

MOV reg16,imm16 $BF

MOV r/m8, imm8 $C6 000

MOV r/m16, imm16 $C7 000

MOV r/m16,sreg $8C 000

MOV r/m16,sreg $8C 001

MOV r/m16,sreg $8C 010

MOV r/m16,sreg $8C 011

MOV sreg, r/m16 $8E 000

MOV sreg, r/m16 $8E 001

MOV sreg, r/m16 $8E 010

MOV sreg, r/m16 $8E 011

MOVSB ES:[DI] = DS:[SI] $A4

MOVSW ES:[DI] = DS:[SI] $A5

MUL r/m8 $F6 100

MUL r/m16 $F7 100

NEG r/m8 $F6 011

NEG r/m16 $F7 011

NOT r/m8 $F6 010

NOT r/m16 $F7 010

OR r/m8, reg8 $08

OR r/m16, reg16 $09

OR reg8, r/m8 $0A

OR reg16, r/m16 $0B

OR AL, imm8 $0C

OR AX, imm16 $0D

OR r/m8, imm8 $80 001

OR r/m16, imm16 $81 001

OR r/m16, imm8 $83 001

OUT addr8, AL $E6

OUT addr8, AX $E7

OUT port[DX], AL $EE

OUT port[DX], AX $EF

POP r/m16 $8F 000

POP reg16 $58

POP reg16 $59

POP reg16 $5A

POP reg16 $5B

POP reg16 $5C

POP reg16 $5D

POP reg16 $5E

POP reg16 $5F

POP sreg $07

POP sreg $0F

POP sreg $17

POP sreg $1F

PUSH r/m16 $FF 110

PUSH reg16 $50

PUSH reg16 $51

PUSH reg16 $52

PUSH reg16 $53

PUSH reg16 $54

PUSH reg16 $55

PUSH reg16 $56

PUSH reg16 $57

PUSH sreg $06

PUSH sreg $0E

PUSH sreg $16

PUSH sreg $1E

REP $F3

REPNE $F2

RET 32-bit POP $CA

RET 16-bit POP $C2

SBB r/m8, reg8 $18

SBB r/m16, reg16 $19

SBB reg8, r/m8 $1A

SBB reg16, r/m16 $1B

SBB AL, imm8 $1C

SBB AX, imm16 $1D

SBB r/m8, imm8 $80 011

SBB r/m16, imm16 $81 011

SBB r/m16, imm8 $83 011

SCASB ES:[DI] == AL $AE

SCASW ES:[DI] == AX $AF

STD $FD

STOSB ES:[DI] = AL $AA

STOSW ES:[DI] = AX $AB

SUB r/m8, reg8 $28

SUB r/m16, reg16 $29

SUB reg8, r/m8 $2A

SUB reg16, r/m16 $2B

SUB AL, imm8 $2C

SUB AX, imm16 $2D

SUB r/m8, imm8 $80 101

SUB r/m16, imm16 $81 101

SUB r/m16, imm8 $83 101

XOR r/m8, reg8 $30

XOR r/m16, reg16 $31

XOR reg8, r/m8 $32

XOR reg16, r/m16 $33

XOR AL, imm8 $34

XOR AX, imm16 $35

XOR r/m8, imm8 $80 110

XOR r/m16, imm16 $81 110

XOR r/m16, imm8 $83 110

You might also like

- PCB 1848ADocument32 pagesPCB 1848AMuhammad yousaf100% (4)

- ICTICT618 Student Assessment Tasks v1 2022Document16 pagesICTICT618 Student Assessment Tasks v1 2022Thanh Nguyen100% (1)

- FacebookH Cking 1 3 (SFILEDocument10 pagesFacebookH Cking 1 3 (SFILEFitra AkbarNo ratings yet

- 8086 OpcodesDocument2 pages8086 OpcodesKarthikeyan JhkNo ratings yet

- AL - Opcodes (06P)Document4 pagesAL - Opcodes (06P)Mc OrtegaNo ratings yet

- 8086 Instruction SetsDocument2 pages8086 Instruction SetsJohannah Kristel NatorNo ratings yet

- DOS AsmDocument24 pagesDOS AsmLukasBartosNo ratings yet

- 8086 Opcodes CompactDocument2 pages8086 Opcodes CompactIsmat DmourNo ratings yet

- ECS 50 8086 Instruction Set Opcodes Operation Operands OpcodeDocument2 pagesECS 50 8086 Instruction Set Opcodes Operation Operands OpcodehariNo ratings yet

- 8051 Instruction SetDocument6 pages8051 Instruction Setanamika_2k8No ratings yet

- 8085 - Instruction - Set - Operation Codes - HexaDocument2 pages8085 - Instruction - Set - Operation Codes - Hexaguddu guptaNo ratings yet

- Hex Code 8051Document6 pagesHex Code 8051blzz2netNo ratings yet

- Pba Septiembre 2020 CartagenaDocument17 pagesPba Septiembre 2020 CartagenaOmar Ospino CaicedoNo ratings yet

- K16A Training ManualDocument59 pagesK16A Training ManualAndrewWerdnaNo ratings yet

- Chuong Trinh Dung AT Mega 8535 Do Nhiet DoDocument6 pagesChuong Trinh Dung AT Mega 8535 Do Nhiet Doapi-26399985No ratings yet

- Colours Aw 18 19Document11 pagesColours Aw 18 19bawaneatulNo ratings yet

- 01.harga Septic Tank BIOFRESH 2018Document1 page01.harga Septic Tank BIOFRESH 2018BIOFRESH FIBERGLASSNo ratings yet

- Tabela de Preços Lamino FacasDocument4 pagesTabela de Preços Lamino FacasJoão Henrique Leite Andreotti (JHLA)No ratings yet

- BristlesDocument110 pagesBristlesLukasBartosNo ratings yet

- Tabela Inova BH 2021Document47 pagesTabela Inova BH 2021michelNo ratings yet

- As Built Drawing DetailsDocument24 pagesAs Built Drawing DetailsYasirNo ratings yet

- ADAM-6018 User NoteDocument5 pagesADAM-6018 User NoteSalvador FayssalNo ratings yet

- Part List - Rev 0005 - Por RevisarDocument29 pagesPart List - Rev 0005 - Por RevisarDavid BorjaNo ratings yet

- Distribution Board Schedule Db-L&P-Work Shop 1-4 TPN 10: 10A 10A 10A 10A 10A 10A 10A 10A 10A 10A 20A 20ADocument9 pagesDistribution Board Schedule Db-L&P-Work Shop 1-4 TPN 10: 10A 10A 10A 10A 10A 10A 10A 10A 10A 10A 20A 20ANiveeth ChattergyNo ratings yet

- Series POS LocalesDocument6 pagesSeries POS LocalesCesarunacNo ratings yet

- Usulan Cito Des 2018Document9 pagesUsulan Cito Des 2018anditriaikiNo ratings yet

- Catalogo MayoreoDocument10 pagesCatalogo MayoreoAlexx GonzalezaNo ratings yet

- Kymco People S - Parts List ManualDocument118 pagesKymco People S - Parts List ManualAmoema MasterBcnNo ratings yet

- SMB e 6502Document814 pagesSMB e 6502Jhon Brayan Angarita MedinaNo ratings yet

- PL 65 ROM DisassemblyDocument97 pagesPL 65 ROM DisassemblyMoe B. Us100% (1)

- Calculul PresiuniiDocument37 pagesCalculul PresiuniiSergiu LazărNo ratings yet

- Tabela Preços de Julho 2022Document1 pageTabela Preços de Julho 2022yuriwillian32No ratings yet

- TMS320c50 ProgramsDocument28 pagesTMS320c50 ProgramsGANAPATHY.S0% (1)

- Promoção: Pedido/atacado Mínimo 1000Document74 pagesPromoção: Pedido/atacado Mínimo 1000Marcio Costa FerreiraNo ratings yet

- ZHR003Document22 pagesZHR003Arie 402No ratings yet

- Lista CompletaDocument14 pagesLista CompletaEliana AriasNo ratings yet

- Todas As Transacoes SapDocument1,068 pagesTodas As Transacoes SapLucian HMRNo ratings yet

- Xotic BB PréAmpDocument7 pagesXotic BB PréAmpTarsilio GuitTarNo ratings yet

- C000: FUEL MAP1 (16x16 8-Bit)Document149 pagesC000: FUEL MAP1 (16x16 8-Bit)Said TouhamiNo ratings yet

- Lista Precio SQD COMPACTA ABRIL 2020Document2 pagesLista Precio SQD COMPACTA ABRIL 2020Rocio AsisNo ratings yet

- Fu TongDocument3 pagesFu TongDuong TruongNo ratings yet

- Practica6 BCD 7segmentosDocument2 pagesPractica6 BCD 7segmentosManuel sotoNo ratings yet

- D09 (Similar) : All Bracings L60x6 Forces Except Level of 116.400+/116.200+, 114.200+Document26 pagesD09 (Similar) : All Bracings L60x6 Forces Except Level of 116.400+/116.200+, 114.200+Abdul basithNo ratings yet

- The Following Table Lists The 8051 Instructions by HEX CodeDocument5 pagesThe Following Table Lists The 8051 Instructions by HEX CodeBruce_Jass_3739No ratings yet

- Sample Basic HoroscopeDocument15 pagesSample Basic HoroscopePrasannaNo ratings yet

- History AuditDocument1,263 pagesHistory AuditfadlylaNo ratings yet

- Medidas de Emblema RodrigoDocument9 pagesMedidas de Emblema RodrigoEve GómezNo ratings yet

- Dreamtime Delay - от астронавта PDFDocument4 pagesDreamtime Delay - от астронавта PDFВиталий ИвановNo ratings yet

- ' TL - T'R'L'Document1 page' TL - T'R'L'aunglwinNo ratings yet

- Celumania PDFDocument3 pagesCelumania PDFGabriela correaNo ratings yet

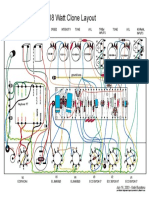

- Marshall 18watt LayoutDocument1 pageMarshall 18watt LayoutThomás HenriqueNo ratings yet

- 8051 RefDocument2 pages8051 RefNam NguyenNo ratings yet

- RS2 VWFDocument2 pagesRS2 VWFGuhhzinNo ratings yet

- Tabela Lançamento - 03-05-23Document9 pagesTabela Lançamento - 03-05-23Edinaldo AbelNo ratings yet

- Hex Code Bytesmnemonic OperandsDocument8 pagesHex Code Bytesmnemonic Operandsansari2erNo ratings yet

- List of Signals Om-OtDocument42 pagesList of Signals Om-OtPhong HuynhNo ratings yet

- FX Levels 02 SeptemberDocument7 pagesFX Levels 02 SeptemberNicola DukeNo ratings yet

- Apl Undercarriage - Ex 200Document206 pagesApl Undercarriage - Ex 200SamidiNo ratings yet

- Diseño Sencillo Riprap DissipatorDocument1 pageDiseño Sencillo Riprap DissipatorrajonjoliNo ratings yet

- Takamine Japan: Top Back & Sides Preamp CaseDocument1 pageTakamine Japan: Top Back & Sides Preamp CaseSava SavicNo ratings yet

- VLAN DOKU V10 enDocument38 pagesVLAN DOKU V10 enshimaa battahNo ratings yet

- 2015 Winter Model Answer Paper PDFDocument40 pages2015 Winter Model Answer Paper PDFMahesh Dahiwal100% (1)

- Honeypot and Honeynet PDFDocument3 pagesHoneypot and Honeynet PDFRamaadyuti BattabyalNo ratings yet

- Designer Complete 4 2 18 HelpFileDocument742 pagesDesigner Complete 4 2 18 HelpFilenoorNo ratings yet

- Blindleistungs BLR cm3p enDocument1 pageBlindleistungs BLR cm3p enRnDES1 CMLNo ratings yet

- India Post Payment Bank Project - Micro ATM User ManualDocument38 pagesIndia Post Payment Bank Project - Micro ATM User ManualMaheshkumarHMNo ratings yet

- WTQ Protocols enDocument86 pagesWTQ Protocols enrajapalayathulaNo ratings yet

- 4479-Sri960 InstructionDocument64 pages4479-Sri960 InstructionJAntonio De la CruzNo ratings yet

- NEC Semiconductror Selection Guide, April 1999 (Shortform) PDFDocument399 pagesNEC Semiconductror Selection Guide, April 1999 (Shortform) PDFNo more accountsNo ratings yet

- Sensitivity: Internal & RestrictedDocument7 pagesSensitivity: Internal & Restrictedkushagra0% (1)

- E522 80 81 82 83 - Elmos - Ds PDFDocument25 pagesE522 80 81 82 83 - Elmos - Ds PDFЕвгений ИвановNo ratings yet

- ANPR Lumo Datasheet en 1.6Document2 pagesANPR Lumo Datasheet en 1.6Jose CarrasquelNo ratings yet

- ML TechmaxDocument202 pagesML TechmaxRedihNo ratings yet

- Payslip November 2022Document1 pagePayslip November 2022Abhijit JhaNo ratings yet

- Introduction To C++ PDFDocument15 pagesIntroduction To C++ PDFAmrouch JridiNo ratings yet

- Pedagogy: Skilling - PK Whatsapp: 03144646739 Whatsapp: 03324646739Document49 pagesPedagogy: Skilling - PK Whatsapp: 03144646739 Whatsapp: 03324646739Minahil ManoNo ratings yet

- TAS Control Room Operations GGK 04052018Document45 pagesTAS Control Room Operations GGK 04052018Mohamed Abdul Qadir100% (1)

- Game CrashDocument41 pagesGame CrashBruno Carvalho RamalhoNo ratings yet

- Rohit Dwivedi: Brief Overview / Career Objective / SummaryDocument1 pageRohit Dwivedi: Brief Overview / Career Objective / Summaryrohit dwivediNo ratings yet

- Aakansha RBTUDocument14 pagesAakansha RBTUAakansha SaxenaNo ratings yet

- Ques. Evolution of Computer. Ans.: Important Questions With Solutions (Unit 1 To Unit 4)Document27 pagesQues. Evolution of Computer. Ans.: Important Questions With Solutions (Unit 1 To Unit 4)Tushar KhandelwalNo ratings yet

- Efficient Filtering Methodology For Image Processing and Its OperationsDocument7 pagesEfficient Filtering Methodology For Image Processing and Its OperationsShankar LingamNo ratings yet

- Heizka Catalogue Cat6 24awg Utp 2Document2 pagesHeizka Catalogue Cat6 24awg Utp 2votinh20687No ratings yet

- TOEIC Reading Practice Test 2Document25 pagesTOEIC Reading Practice Test 2CT MacaraegNo ratings yet

- EL FLOW Select - ENDocument5 pagesEL FLOW Select - ENsandip kcNo ratings yet

- WT and Fds Practical SlipsDocument32 pagesWT and Fds Practical SlipsRohidas SapkalNo ratings yet

- Air Conditioner Remote Controller Illustration: CR137-RG51FDocument8 pagesAir Conditioner Remote Controller Illustration: CR137-RG51FCarlos PONTET JOURDANNo ratings yet

- Configuring Automatic Packing in Outbound Delivery - SAP BlogsDocument18 pagesConfiguring Automatic Packing in Outbound Delivery - SAP Blogsprashantsdpiki100% (1)