Professional Documents

Culture Documents

Transmission Line Theory: Outline

Uploaded by

rakesh dasOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Transmission Line Theory: Outline

Uploaded by

rakesh dasCopyright:

Available Formats

Signal Integrity and High-Speed Interconnects

January-May 2006

Transmission Line Theory

(Part 1)

Dr. José Ernesto Rayas Sánchez

Outline

Common transmission media

Modeling uniform interconnects

Interconnect parasitics and their physical significance

From lumped circuits to distributed circuits

Fundamental transmission line equations

Dr. J.E. Rayas Sánchez 2

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Common Transmission Media

Uniform Interconnects

Waveguide

a

b

w

Coaxial

Twisted-pair

h

h

εr

w1

w

w2

Coplanar Microstrip

Dr. J.E. Rayas Sánchez (Hewlett-Packard's RF Design and Measurement Seminar, 2000) 3

Common Transmission Media (cont)

Practical interconnects can be decomposed in segments of

uniform interconnects (if necessary)

PCB

(add-in card)

Components

(Chip + Pkg)

PCB Connector

(Motherboard)

Dr. J.E. Rayas Sánchez (H. Heck, 2005) 4

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Modeling Uniform Interconnects

(A. Weisshaar, Tutorial on High-Speed Interconnects, IMS June 2004, Fort Worth, TX)

Dr. J.E. Rayas Sánchez 5

Modeling Uniform Interconnects (cont)

Parasitic effects associated to each transmission media

– Capacitance between conductors, C

– Resistance of conductors (conductor losses), R

– Inductance of conductor loops, L

– Dielectric conductivity (dielectric losses), G

R, C, L, and G must be determined per unit length

Dr. J.E. Rayas Sánchez 6

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Interconnect Shunt Capacitance

(A. Weisshaar, Tutorial on High-Speed Interconnects, IMS June 2004, Fort Worth, TX)

Dr. J.E. Rayas Sánchez 7

Fringing Capacitance Effect

(A. Weisshaar, Tutorial on High-Speed Interconnects, IMS June 2004, Fort Worth, TX)

Dr. J.E. Rayas Sánchez 8

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Interconnect Series Inductance

(A. Weisshaar, Tutorial on High-Speed Interconnects, IMS June 2004, Fort Worth, TX)

Dr. J.E. Rayas Sánchez 9

Interconnect Series DC Resistance

(A. Weisshaar, Tutorial on High-Speed Interconnects, IMS June 2004, Fort Worth, TX)

Dr. J.E. Rayas Sánchez 10

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Skin Effect

(A. Weisshaar, Tutorial on High-Speed Interconnects, IMS June 2004, Fort Worth, TX)

Dr. J.E. Rayas Sánchez 11

EM-Simulation of Conductor Current Distribution

(A. Weisshaar, Tutorial on High-Speed Interconnects, IMS June 2004, Fort Worth, TX)

Dr. J.E. Rayas Sánchez 12

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Proximity Effect

(A. Weisshaar, Tutorial on High-Speed Interconnects, IMS June 2004, Fort Worth, TX)

Dr. J.E. Rayas Sánchez 13

Edge and Indy Effects – Example

0.6 GHz

FR4

W 1 GHz

H

W = 5 mm L = 25 mm

H = 5 mm εr = 4.5

dielectric loss tan = 0.025

Dr. J.E. Rayas Sánchez 14

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Interconnect Shunt Conductance

(A. Weisshaar, Tutorial on High-Speed Interconnects, IMS June 2004, Fort Worth, TX)

Dr. J.E. Rayas Sánchez 15

Loss Tangent of Typical Materials

(A. Weisshaar, Tutorial on High-Speed Interconnects, IMS June 2004, Fort Worth, TX)

Dr. J.E. Rayas Sánchez 16

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Equivalent Circuit Models for Interconnects

On-chip Interconnects

– lumped C if very short

– lumped RC if very short and R significant

– cascaded lumped RC if short

– distributed RC if long

– RLC distributed line (high performance VLSI circuits

and microwave ICs)

Off-chip Interconnects (→ usually distributed models)

– LC line if losses can be ignored

– RLC line on low dielectric loss PCBs

– RLGC line (if dielectric loss is significant)

Dr. J.E. Rayas Sánchez 17

Lumped Equivalent Circuit Models

Dr. J.E. Rayas Sánchez 18

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

From Lumped Circuits to Distributed Circuits

(A. Weisshaar, Tutorial on High-Speed Interconnects, IMS June 2004, Fort Worth, TX)

Dr. J.E. Rayas Sánchez 19

Transmission Line Model

The interconnect is modeled using an infinite number

of RLCG sections

Dr. J.E. Rayas Sánchez (R. Ludwig and P. Bretchko, RF Circuit Design, Prentice Hall, 2000) 20

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Transmission Line Model

The interconnect is modeled using an infinite number

of RLCG sections

Dr. J.E. Rayas Sánchez (R. Ludwig and P. Bretchko, RF Circuit Design, Prentice Hall, 2000) 21

Transmission Line Model

Generic equivalent circuit for each section (R, L, C

and G are per unit length)

The interconnect is modeled using an infinite number

of these sections, making ∆z → 0

Dr. J.E. Rayas Sánchez (R. Ludwig and P. Bretchko, RF Circuit Design, Prentice Hall, 2000) 22

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Transmission Line Equations

Time-Domain (Telegrapher Equations)

∂v( z , t ) ∂i ( z , t )

= − Ri ( z , t ) − L

∂z ∂t

∂i ( z , t ) ∂v( z , t )

= −Gv( z , t ) − C

∂z ∂t

Telegrapher Equations in Frequency-Domain

dV ( z )

= − ( R + j ωL ) I ( z )

dz

dI ( z )

= −(G + jωC )V ( z )

dz

Dr. J.E. Rayas Sánchez 23

Transmission Line Equations (cont)

Wave Equation (frequency domain)

d 2V ( z ) d 2 I ( z)

2

− γ 2V ( z ) = 0 2

− γ 2 I ( z) = 0

dz dz

where γ = ( R + jωL)(G + jωC ) ≡ α + jβ

is the complex propagation constant

Solutions to the wave equation are

V ( z ) = Vo+ e −γz + Vo− e +γz I ( z ) = I o+ e −γz + I o− e +γz

incident waves

reflected waves

Dr. J.E. Rayas Sánchez 24

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Transmission Line Equations (cont)

Characteristic Impedance of the TL

Vo+ Vo−

Zo ≡ + =

I o − I o−

then

R + j ωL

Zo =

G + j ωC

Reflection Coefficient along the line, Γz

V ( z ) = Vo+ e −γz + Vo− e +γz

Vo− e +γz Vo− +2γz

Γz ( z) = = e

Vo+ e −γz Vo+

Dr. J.E. Rayas Sánchez 25

Transmission Line Equations (cont)

Solutions in the frequency domain

V ( z ) = Vo+ e −γz + Vo− e +γz I ( z ) = I o+ e −γz + I o− e +γz

γ = ( R + jωL)(G + jωC ) ≡ α + jβ

Solutions in the time domain

v( z , t ) = | Vo+ | cos(ωt − βz + φ + )e −αz + | Vo− | cos(ωt + β z + φ − )e +αz

Wavelength Phase velocity, wave velocity or

propagation speed

v p 2π

λ= = dz ω

f β vp = =

dt β

(speed at which a constant phase point

Dr. J.E. Rayas Sánchez travels down the line) 26

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Transmission Line Symbol

(Lossy) Transmission Line

l

Zo , γ

Length along the line

Zo , γ

z

l

Dr. J.E. Rayas Sánchez 0 27

Reflection Coefficient

Reflection coefficient along the line

Zo , γ ZL Vo− e −γl Vo− −2γl

Γl (l ) = + +γl = + e

Vo e Vo

l

0

Reflection coefficient at the load

Vo− Z L − Z o

Γ = Γl (l = 0) = =

Vo+ Z L + Z o

Dr. J.E. Rayas Sánchez 28

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

Signal Integrity and High-Speed Interconnects

January-May 2006

Input Impedance

Input Impedance along the line

Zo , γ ZL

l

0

V (l ) Z + Z o tanh(γl )

Z in (l ) = = Zo L

I (l ) Z o + Z L tanh(γl )

Dr. J.E. Rayas Sánchez 29

Dr. J. E. Rayas Sánchez

http://iteso.mx/~erayas erayas@iteso.mx

You might also like

- Closure On "Time-Varying Harmonics: Part II-Harmonic Summation and Propagation"Document1 pageClosure On "Time-Varying Harmonics: Part II-Harmonic Summation and Propagation"Isarar AhamadNo ratings yet

- The New Era of Foramenal LocationDocument7 pagesThe New Era of Foramenal LocationElizabeth CortésNo ratings yet

- 4.fault Diagnosis For Electrical Systems and Power Networks A Review.Document19 pages4.fault Diagnosis For Electrical Systems and Power Networks A Review.VEDER MIGUEL TORRES BENITESNo ratings yet

- Nonlinear Size-Dependent Modeling and Dynamics of Nanocrystalline Arc ResonatorsDocument19 pagesNonlinear Size-Dependent Modeling and Dynamics of Nanocrystalline Arc ResonatorsSi DoNo ratings yet

- Modeling and Detection of High Impedance FaultsDocument11 pagesModeling and Detection of High Impedance FaultsEduardo KilianNo ratings yet

- (McRae Et Al, 2008) Using Circuit Theory To Model Connectivity in Ecology, Evolution, and ConservationDocument14 pages(McRae Et Al, 2008) Using Circuit Theory To Model Connectivity in Ecology, Evolution, and ConservationOscar Leonardo Aaron Arizpe VicencioNo ratings yet

- De Luca - An Educational Overview of Ultrasound - 1 - 2021Document13 pagesDe Luca - An Educational Overview of Ultrasound - 1 - 2021Conrad WaluddeNo ratings yet

- Research Review: Modelling Disease Spread and Control in Networks: Implications For Plant SciencesDocument19 pagesResearch Review: Modelling Disease Spread and Control in Networks: Implications For Plant Sciencesntv2000No ratings yet

- Stationary Vs Non-Stationary ChannelsDocument3 pagesStationary Vs Non-Stationary Channelsolcay_yigit_1986No ratings yet

- Design of A Cpw-Fed Ultrawideband Fractal Antenna: Min Ding, Ronghong Jin, Junping Geng, and Qi WuDocument4 pagesDesign of A Cpw-Fed Ultrawideband Fractal Antenna: Min Ding, Ronghong Jin, Junping Geng, and Qi WuSudesh AgrawalNo ratings yet

- Filter-Antenna Consisting of Conical FSS Radome and Monopole AntennaDocument6 pagesFilter-Antenna Consisting of Conical FSS Radome and Monopole AntennaTOUGHNo ratings yet

- Parameters of Microstrip Transmission LinesDocument7 pagesParameters of Microstrip Transmission LinesSergio Castro RodriguezNo ratings yet

- Journal of Theoretical Biology: or Givan, Nehemia Schwartz, Assaf Cygelberg, Lewi StoneDocument8 pagesJournal of Theoretical Biology: or Givan, Nehemia Schwartz, Assaf Cygelberg, Lewi StonegraviphotonNo ratings yet

- A Research On Modeling of High Impedance Fault Detection For Protection of DC Distribution SystemDocument7 pagesA Research On Modeling of High Impedance Fault Detection For Protection of DC Distribution SystemIJRASETPublicationsNo ratings yet

- Broadband Sub-Wavelength Profile High-Gain Antennas Based On Multi-Layer MetasurfacesDocument5 pagesBroadband Sub-Wavelength Profile High-Gain Antennas Based On Multi-Layer MetasurfacesBindhuNo ratings yet

- Checar RedesDocument11 pagesChecar RedesChepis JrfNo ratings yet

- Vibro-Acoustic Response of An Infinite, Rib-Stiffened, Thick-Plate Assembly Using Finite-Element AnalysisDocument8 pagesVibro-Acoustic Response of An Infinite, Rib-Stiffened, Thick-Plate Assembly Using Finite-Element Analysisaurora borealissNo ratings yet

- Original Contribution: Performance of Ultrasound Echo Decomposition Using Singular Spectrum AnalysisDocument8 pagesOriginal Contribution: Performance of Ultrasound Echo Decomposition Using Singular Spectrum Analysismoonrise1985No ratings yet

- International Journal of Solids and Structures: Anil K. Vashishth, Vishakha GuptaDocument13 pagesInternational Journal of Solids and Structures: Anil K. Vashishth, Vishakha GuptaAmir JoonNo ratings yet

- Modeling of Sodium Currents From Mesencephalic Trigeminal Neurons by System Identification and Sensitivity AnalysisDocument2 pagesModeling of Sodium Currents From Mesencephalic Trigeminal Neurons by System Identification and Sensitivity Analysisvehaxo6855No ratings yet

- Mutual Coupling in Antenna Arrays: Guest Editors: Hon Tat Hui, Marek E. Bialkowski, and Hoi Shun LuiDocument94 pagesMutual Coupling in Antenna Arrays: Guest Editors: Hon Tat Hui, Marek E. Bialkowski, and Hoi Shun LuiMd AhmedNo ratings yet

- Handbook of Hydrophone Element Design TechnologyDocument2 pagesHandbook of Hydrophone Element Design TechnologyBrendon SoongNo ratings yet

- Lonngren - 2000 - On The Goubau-Schwering Beam Waveguide Using A Modified Paraxial ApproximationDocument2 pagesLonngren - 2000 - On The Goubau-Schwering Beam Waveguide Using A Modified Paraxial ApproximationAhmed AbdelraheemNo ratings yet

- Probe Oscillation Shear Elastography (PROSE)Document9 pagesProbe Oscillation Shear Elastography (PROSE)oscar.atondoNo ratings yet

- Characterizing The Wireless Data Transmission of Biosignals Within A Health-Care EnvironmentDocument7 pagesCharacterizing The Wireless Data Transmission of Biosignals Within A Health-Care EnvironmentPedro Javier Garcia RamirezNo ratings yet

- 19 ElectronicApexLocators-AnoverviewDocument7 pages19 ElectronicApexLocators-AnoverviewzaheerbdsNo ratings yet

- May 2004 Doc.: IEEE 802.11-03/940r: Date: AuthorsDocument49 pagesMay 2004 Doc.: IEEE 802.11-03/940r: Date: AuthorsYousef BilbeisiNo ratings yet

- On The CharacterizationDocument22 pagesOn The CharacterizationToàn LêNo ratings yet

- In Vivo Fiber Tractography Using DT-MRI DataDocument8 pagesIn Vivo Fiber Tractography Using DT-MRI DataMarioVerdicchioNo ratings yet

- TMP 4 CD8Document18 pagesTMP 4 CD8FrontiersNo ratings yet

- Inp HBT Ic Technology For Terahertz Frequencies: Fundamental Oscillators Up To 0.57 THZDocument13 pagesInp HBT Ic Technology For Terahertz Frequencies: Fundamental Oscillators Up To 0.57 THZPrasiNo ratings yet

- Electronic Apex Locators-An Overview: April 2017Document7 pagesElectronic Apex Locators-An Overview: April 2017Cahyani CahyaniNo ratings yet

- References: Received 23 July 2013 Revised 21 March 2014Document1 pageReferences: Received 23 July 2013 Revised 21 March 2014ab__ismNo ratings yet

- References: Received 23 July 2013 Revised 21 March 2014Document1 pageReferences: Received 23 July 2013 Revised 21 March 2014ab__ismNo ratings yet

- Double Heterostructure Lasers: Early Days and Future PerspectivesDocument9 pagesDouble Heterostructure Lasers: Early Days and Future PerspectivesLewis WilliamsonNo ratings yet

- Augilera Et Al. (2010) - Hybrid Bayesian Network Classifiers - Application To Species Distribution ModelsDocument10 pagesAugilera Et Al. (2010) - Hybrid Bayesian Network Classifiers - Application To Species Distribution ModelsAftab CoinNo ratings yet

- Satellite Systems for Personal Applications: Concepts and TechnologyFrom EverandSatellite Systems for Personal Applications: Concepts and TechnologyNo ratings yet

- Aban Et Al 2006 JASADocument9 pagesAban Et Al 2006 JASAhoangpvrNo ratings yet

- (FEM) Modelación de Elementos Finitos para Transductores UltrasónicosDocument24 pages(FEM) Modelación de Elementos Finitos para Transductores Ultrasónicosrotero_pujolNo ratings yet

- Acoustic Wave Reflection Control Based On Broadband Differential Phase ShiftersDocument6 pagesAcoustic Wave Reflection Control Based On Broadband Differential Phase Shiftersapi-633277434No ratings yet

- A Review On Protective Relays' Developments and Trends: ReferencesDocument1 pageA Review On Protective Relays' Developments and Trends: Referencesab__ismNo ratings yet

- Es14-00387 1Document16 pagesEs14-00387 1Jorge BotiaNo ratings yet

- WeqwewdDocument1 pageWeqwewdkona15No ratings yet

- Electric 20 Fields 20 in 20 The 20 Human 20 Body 20 Due 20 To 20 Electrostatic 20 DischargesDocument10 pagesElectric 20 Fields 20 in 20 The 20 Human 20 Body 20 Due 20 To 20 Electrostatic 20 Dischargesdarshan joshiNo ratings yet

- Review Parametric AcousticsDocument9 pagesReview Parametric AcousticsGeoFurrielNo ratings yet

- MTG 0801Document1 pageMTG 0801Sajjad Ahmad MadaniNo ratings yet

- Binder1 39Document1 pageBinder1 39vainateyagoldarNo ratings yet

- Sanderson 2015Document12 pagesSanderson 2015IMVG DatabaseNo ratings yet

- Radio-Wave Propagation Into Large Building Structures-Part 2: Characterization of MultipathDocument12 pagesRadio-Wave Propagation Into Large Building Structures-Part 2: Characterization of MultipathClenaNo ratings yet

- Wavelets PDFDocument64 pagesWavelets PDFCarlos GamioNo ratings yet

- Five Wave Equation For Small Signal AnalDocument7 pagesFive Wave Equation For Small Signal AnalVladimir ShkolnikovNo ratings yet

- MEDICAMENTESCALARDocument5 pagesMEDICAMENTESCALARStere StereNo ratings yet

- Rout 2016Document14 pagesRout 2016TabassumWaheedNo ratings yet

- Behavior of Underground Piping Joints Due To Static and Dynamic LoadingDocument260 pagesBehavior of Underground Piping Joints Due To Static and Dynamic LoadingjbNo ratings yet

- (MODELS) Obeidat Et Al 2018Document34 pages(MODELS) Obeidat Et Al 2018Uzairtahir77No ratings yet

- 1 s2.0 S002076830200358X MainDocument17 pages1 s2.0 S002076830200358X MainManu HegdeNo ratings yet

- Computational Simulation of Dental Implant Osseointegration Through Resonance Frequency AnalysisDocument10 pagesComputational Simulation of Dental Implant Osseointegration Through Resonance Frequency AnalysisDaniella NúñezNo ratings yet

- Simulating The Seismic Performance of A Large-Scale Electric Network in The U.S. MidwestDocument13 pagesSimulating The Seismic Performance of A Large-Scale Electric Network in The U.S. MidwestNicolas AhumadaNo ratings yet

- Lecture 1-1Document19 pagesLecture 1-1Masood ChoudharyNo ratings yet

- Some Necessary and Sufficient Conditions For Second-Order Consensus inDocument7 pagesSome Necessary and Sufficient Conditions For Second-Order Consensus intuvantoan17No ratings yet

- Transmission LinesDocument8 pagesTransmission LinesClaudiu Anton VitanNo ratings yet

- Lossless Transmission Line FundamentalsDocument6 pagesLossless Transmission Line Fundamentalsrakesh dasNo ratings yet

- Chapter Eleven: Transmission LinesDocument11 pagesChapter Eleven: Transmission Linesrakesh dasNo ratings yet

- Transmission LinesDocument23 pagesTransmission Linesravi010582No ratings yet

- Note2 PDFDocument82 pagesNote2 PDFLavanya ChandranNo ratings yet

- Transmission LinesDocument23 pagesTransmission Linesravi010582No ratings yet

- TransmissionLinesPart I PDFDocument21 pagesTransmissionLinesPart I PDFashishmanyanNo ratings yet

- Chapter 12: Transmission Lines: EET-223: RF Communication Circuits Walter LaraDocument39 pagesChapter 12: Transmission Lines: EET-223: RF Communication Circuits Walter Lararakesh dasNo ratings yet

- Transmission Line XDocument21 pagesTransmission Line XKifaru Micro-electronicsNo ratings yet

- TESP12201R0Document20 pagesTESP12201R0Muhammad AliNo ratings yet

- GR 9 Eng CodebDocument6 pagesGR 9 Eng CodebSharmista WalterNo ratings yet

- CHAPTER I Lesson II Seven Environmental PrinciplesDocument17 pagesCHAPTER I Lesson II Seven Environmental PrinciplesTrixie jade DumotNo ratings yet

- Aman Singh Rathore Prelms Strategy For UPSCDocument26 pagesAman Singh Rathore Prelms Strategy For UPSCNanju NNo ratings yet

- IoT Security Checklist Web 10 17 r1Document39 pagesIoT Security Checklist Web 10 17 r1SubinNo ratings yet

- CrimDocument29 pagesCrimkeziahmae.bagacinaNo ratings yet

- What Is The Difference Between Newtonian and Non-Newtonian Fluid and Give Example For Each Case?Document11 pagesWhat Is The Difference Between Newtonian and Non-Newtonian Fluid and Give Example For Each Case?MOHAMED ABD ELGHANYNo ratings yet

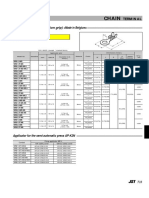

- Chain: SRB Series (With Insulation Grip)Document1 pageChain: SRB Series (With Insulation Grip)shankarNo ratings yet

- Bearing 1Document27 pagesBearing 1desalegn hailemichaelNo ratings yet

- Chapter 9Document28 pagesChapter 9Aniket BatraNo ratings yet

- Te-Chemical Sem5 CPNM-CBCGS Dec19Document2 pagesTe-Chemical Sem5 CPNM-CBCGS Dec19Mayank ShelarNo ratings yet

- Final LUS EvaluationDocument36 pagesFinal LUS EvaluationNextgenNo ratings yet

- Ortho TechnologyDocument196 pagesOrtho Technologyr3doc3No ratings yet

- Data Mining in IoTDocument29 pagesData Mining in IoTRohit Mukherjee100% (1)

- Half Yearly Examination, 2017-18: MathematicsDocument7 pagesHalf Yearly Examination, 2017-18: MathematicsSusanket DuttaNo ratings yet

- Brochure - OasisDocument24 pagesBrochure - OasisVivek RNo ratings yet

- Hesychasm - A Christian Path of TranscendenceDocument10 pagesHesychasm - A Christian Path of Transcendencebde_gnas100% (1)

- Grua Grove 530e 2 Manual de PartesDocument713 pagesGrua Grove 530e 2 Manual de PartesGustavo100% (7)

- HPSC HCS Exam 2021: Important DatesDocument6 pagesHPSC HCS Exam 2021: Important DatesTejaswi SaxenaNo ratings yet

- Bassoon (FAGOT) : See AlsoDocument36 pagesBassoon (FAGOT) : See Alsocarlos tarancón0% (1)

- Rare Watches (Christie's) 16. 05. 2016.Document236 pagesRare Watches (Christie's) 16. 05. 2016.Simon LászlóNo ratings yet

- Penelitian Tindakan Kelas - Alberta Asti Intan Sherliana 20220049Document25 pagesPenelitian Tindakan Kelas - Alberta Asti Intan Sherliana 20220049Asti SherlyanaNo ratings yet

- 全新全真题库一 PDFDocument36 pages全新全真题库一 PDFTzarlene100% (1)

- (Ebook - Antroposofia - EnG) - Rudolf Steiner - Fundamentals of TheraphyDocument58 pages(Ebook - Antroposofia - EnG) - Rudolf Steiner - Fundamentals of Theraphyblueyes247No ratings yet

- Lecture 7 - Friction - NptelDocument18 pagesLecture 7 - Friction - Nptels_murugan02No ratings yet

- 3-Phase Short-Circuit Current (Isc) at Any Point Within A LV Installation - Electrical Installation GuideDocument6 pages3-Phase Short-Circuit Current (Isc) at Any Point Within A LV Installation - Electrical Installation GuideYuukinoriNo ratings yet

- Lord of The Flies - Chapter Comprehension QuestionsDocument19 pagesLord of The Flies - Chapter Comprehension Questionsjosh johnsyNo ratings yet

- 2021 Individual 20546 (Lawrence, Stephen R. and Bette F.) ClientDocument18 pages2021 Individual 20546 (Lawrence, Stephen R. and Bette F.) ClientVANDA MOORENo ratings yet

- CH 1 Viscous Fluid Flow Part 1Document29 pagesCH 1 Viscous Fluid Flow Part 1Ammar WahabNo ratings yet

- Linux and The Unix PhilosophyDocument182 pagesLinux and The Unix PhilosophyTran Nam100% (1)