Professional Documents

Culture Documents

Advanced UVM: Architecting A UVM Testbench

Uploaded by

manchuricoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Advanced UVM: Architecting A UVM Testbench

Uploaded by

manchuricoCopyright:

Available Formats

Advanced UVM

Architecting a UVM Testbench

Tom Fitzpatrick

Strategic Verification Architect

UVM Testbench - Architectural Design

For Each Interface:

• How does the interface work?

• What information is transferred?

• Transaction variants? DUT

• Uni/bidirectional? Pipelined? APB

SPI

For the Design: IRQ I/F

• What does it do?

• What are the use cases?

• Which test cases are required?

• What type of stimulus scenarios are required?

• What represents correct behavior?

• What kind of functional coverage do I need?

2 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

UVM Structural Building Block: Agent

Analysis port: Send Detects transactions

transactions for checking on the interface

- Contains virtual Agent

interface handle One per

Configuration interface

- Pass information Monitor

on how agent Object

should behave

Sequencer

DUT

Sends stimulus Driver

seq_item

to Driver

Stimulus Converts seq_item to pin wiggles

3 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

UVM Architecture: Block-Level Env/Test

Test

Test

Test

Test

Test

Test

Test

Environment

Coverage

Test

seq Collector

Seqs

Agent

Bkgrnd

seq Configuration

Seqs Object

Monitor DUT

Env Config Config Sequencer

A Config A Config Driver

4 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

UVM Architecture: Block-Level Env/Test

Test

Test

Test

Environment

Agent2

Test Configuration

Monitor

Seqs Environment Object

Coverage Sequencer

Collector Driver

Score

Agent1

Bkgrnd Configuration

Seqs Monitor

Object

Env Config Config Sequencer DUT

A2 Config A2 Config Driver

A1 Config A1 Config

5 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

UVM Architecture: Integration-Level Env/Test

Test

Test

Test

Environment

Agent2

Test Configuration

Seqs Object

Monitor DUT

Score

Coverage Sequencer

Collector Driver

Score

Agent1

Bkgrnd Configuration

Seqs Monitor

Object

Env Config Config Sequencer DUT

E2 Config E2 Config

A2 Driver

E1 Config E1 Config

A1

6 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

Introducing Phasing

UVM execution is controlled by phases

<task/func> phasename_phase(uvm_phase phase);

build

Build is called top-down

connect

• Facilitates hierarchical instantiation and

end_of_elab

configuration

start_of_sim

All others called bottom-up

run_phase() is the only task run

• All run_phase methods execute in parallel (task)

Don’t use alternate run-time phases extract

check

report

final

7 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

Building the Agent

class if_agent extends uvm_component;

`uvm_component_utils(if_agent)

if_agent_cfg cfg;

if_driver driver;

if_sequencer seqr;

if_monitor monitor;

uvm_analysis_port #(if_txn) ap;

function void new(string name, uvm_component parent);

super.new(name, parent); Agent

endfunction Configuration

Object Monitor

Sequencer

endclass Driver DUT

8 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

Agent: The Build Phase

class if_agent extends uvm_component;

function void build_phase(uvm_phase phase);

if(!uvm_config_db #(if_agent_cfg)::get(this,“”,“cfg”, cfg))

`uvm_fatal(“Config fatal”,“Can’t get config”);

if(cfg.active == UVM_ACTIVE) begin

seqr = if_sequencer::type_id::create(“seqr”,this);

driver = if_driver::type_id::create(“driver”,this);

end

monitor = if_monitor::type_id::create(“monitor”,this);

… Agent

endfunction Configuration

Object Monitor

endclass

Sequencer

Driver DUT

9 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

Agent: The Connect Phase

class if_agent extends uvm_component;

function void connect_phase(uvm_phase phase);

monitor.vif = cfg.vif;

ap = m_monitor.ap;

if(cfg.active == UVM_ACTIVE) begin

driver.seq_item_port.connect(seqr.seq_item_export);

driver.vif = cfg.vif;

end

…

endfunction Agent

Configuration

Object Monitor

endclass

Sequencer

Driver DUT

10 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

The Environment: Declaration

class my_env extends uvm_env;

`uvm_component_utils(my_env)

if1_agent agent1;

if2_agent agent2;

my_score score;

my_cov cov;

my_env_config cfg;

function new(string name, uvm_component); Environment

super.new(name, parent); Agent2

endfunction

Environment

Coverage

Collector

Score

Agent1

endclass Config

A2 Config

DUT

A1 Config

11 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

The Environment: Build_phase

class my_env extends uvm_env;

function void build_phase(uvm_phase phase);

if(!uvm_config_db #( my_env_config )::get( this , "",

“my_env_config" , cfg ) begin

`uvm_fatal("build_phase", "unable to get my_env_config")

end

uvm_config_db #(if1_agent_config)::set(this , "m_agent1*",

"agent1_config", cfg.agent1_cfg );

agent1 = if1_agent::type_id::create( Environment

"agent1", this); Agent2

…

Environment

Coverage

Collector

endfunction:build_phase Score

endclass

Agent1

Config

A2 Config

DUT

A1 Config

12 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

The Environment: Build_phase

class my_env extends uvm_env;

function void build_phase(uvm_phase phase);

…

uvm_config_db #(if2_agent_config)::set(this , "agent2*",

“if2_agent_config", m_cfg. agent2_cfg );

agent2 = if2_agent2::type_id::create("agent2", this);

if(cfg.has_my_score)

score = my_score::type_id::create("score", this);

if(cfg.has_coverage) Environment

cov = my_cov::type_id::create(“cov”, Agent2

this);

Environment

Coverage

Collector

endfunction:build_phase Score

endclass

Agent1

Config

A2 Config

DUT

A1 Config

13 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

The Environment: Connect_phase

class my_env extends uvm_env;

function void connect_phase(uvm_phase phase);

if(cfg.has_my_score) begin

agent1.ap.connect(score.apb.analysis_export);

agent2.ap.connect(score.spi.analysis_export);

end

if(cfg.has_coverage)

agent1.ap.connect(cov.analysis_export);

endfunction: connect_phase Environment

Agent2

Environment

Coverage

Collector

Score

endclass

Agent1

Config

A2 Config

DUT

A1 Config

14 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

The Base Test

class my_test_base extends uvm_test;

`uvm_component_utils(my_test_base)

my_env env;

my_agent1_config a1_cfg;

my_agent2_config a2_cfg;

my_env_cfg cfg; Config

A2 Config

A1 Config

function new(string name, uvm_component); Environment

super.new(name, parent); Agent2

endfunction

Environment

Coverage

Collector

Score

endclass

Agent1

Config

A2 Config

DUT

A1 Config

15 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

The Base Test: Build_phase

class my_test_base extends uvm_test;

`uvm_component_utils(my_test_base)

function void build_phase( uvm_phase phase );

cfg = my_env_cfg::type_id::create(“cfg”);

configure_env();// setup configuration for env and agents

uvm_config_db#(my_env_cfg)::set(this,"*",

“my_env_config", cfg);

Config

A2 Config

A1 Config

env = my_env::type_id::create("env", Environment

this); Agent2

endfunction

Environment

Coverage

Collector

Score

endclass

Agent1

Config

A2 Config

DUT

A1 Config

16 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

The Actual Test

class my_test extends uvm_test_base;

`uvm_component_utils(my_test)

my_virt_seq m_vseq;

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

Config

A2 Config vseq

A1 Config

function void build_phase(uvm_phase phase);

super.build_phase(phase); Agent2

endfunction Coverage

Collector

endclass Score

Agent1

Config

A2 Config

DUT

A1 Config

17 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

The Actual Test

class my_test extends uvm_test_base;

`uvm_component_utils(my_test)

task run_phase(uvm_phase phase);

vseq = my_virt_seq::type_id::create(“vseq”);

phase.raise_objection(this, “Starting virtual sequence”);

vseq.start();

phase.drop_objection(this,

Config

vseq

seq2

seq1 A2 Config

A1 Config

“Finished virtual sequence”); Environment

endtask Agent2

Environment

Coverage

Collector

Score

endclass

Agent1

Config

A2 Config

DUT

A1 Config

18 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

Architecture Summary

Agents are protocol-specific

Environments define the testbench topology

• Which agents and how many

• Other components

Base Test instantiates env and handles default configuration

Extend the base test to define your test

• Tweek configuration and/or factory settings

• Start (virtual) sequence(s)

• Test handles phase objections

Keep to basic phasing

19 Unrestricted | © Siemens | Verification Academy: Advanced UVM | March 2021

Advanced UVM

Architecting a UVM Testbench

Tom Fitzpatrick

Strategic Verification Architect

You might also like

- Star Trek The Next Generation RPG Last Unicorn Games PDFDocument320 pagesStar Trek The Next Generation RPG Last Unicorn Games PDFNicolas Morin50% (2)

- List of Homoeopathic Medicines, Combinations & Their UsesDocument29 pagesList of Homoeopathic Medicines, Combinations & Their Usesgirish261187% (55)

- UVM Framework Users Guide PDFDocument105 pagesUVM Framework Users Guide PDFmanchuricoNo ratings yet

- Verification Approach For ASIC Generic IP Functional VerificationDocument3 pagesVerification Approach For ASIC Generic IP Functional VerificationMohammad Seemab AslamNo ratings yet

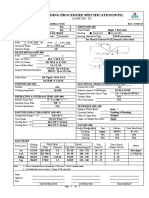

- Application For Registration: BIR Form NoDocument2 pagesApplication For Registration: BIR Form Noexonyeoshidae 05No ratings yet

- Welding Procedure Specification (WPS) : (Asme Sec. Ix)Document1 pageWelding Procedure Specification (WPS) : (Asme Sec. Ix)Ahmed Lepda100% (1)

- AXI Stream ProtocolDocument8 pagesAXI Stream ProtocolshwetabhagatNo ratings yet

- SystemVerilog Vs Verilog in RTL DesignDocument4 pagesSystemVerilog Vs Verilog in RTL DesignVijay KumarNo ratings yet

- SV-UVM of AXI - WBDocument4 pagesSV-UVM of AXI - WBRahul HanaNo ratings yet

- Verilog Inter QuestionsDocument21 pagesVerilog Inter Questionshari4041100% (1)

- Lec4 VerilogDocument58 pagesLec4 VerilogRohit BhelkarNo ratings yet

- FSM in SV-classDocument13 pagesFSM in SV-classkunaraj75% (4)

- Каталог гидромолот JCB HM385Document2 pagesКаталог гидромолот JCB HM385бекиров эрнестNo ratings yet

- Verification of Driver Logic Using Ambaaxi UvmDocument10 pagesVerification of Driver Logic Using Ambaaxi UvmAnonymous e4UpOQEPNo ratings yet

- Solving Complex Users' Assertions: by Ben CohenDocument8 pagesSolving Complex Users' Assertions: by Ben Cohenpinakin4uNo ratings yet

- Senior Design Verification Engineer in Phoenix AZ Resume Lloyd HeathDocument3 pagesSenior Design Verification Engineer in Phoenix AZ Resume Lloyd HeathLloyd HeathNo ratings yet

- A Step by Step Guide: UVM Framework Alu TutorialDocument95 pagesA Step by Step Guide: UVM Framework Alu TutorialmanchuricoNo ratings yet

- A Step by Step Guide: UVM Framework Alu TutorialDocument95 pagesA Step by Step Guide: UVM Framework Alu TutorialmanchuricoNo ratings yet

- 2016-DVClub-PDX Adopting Uvm SeminarDocument18 pages2016-DVClub-PDX Adopting Uvm SeminarspaulsNo ratings yet

- Interview Question UsefullinkDocument3 pagesInterview Question UsefullinkMOHAMMED JUNED RAHINo ratings yet

- Avinash Eswar Intrv QuesDocument13 pagesAvinash Eswar Intrv QuesVeeresh TangadgiNo ratings yet

- Apb SRAM Core Verification PlanDocument2 pagesApb SRAM Core Verification PlanRohit PandeyNo ratings yet

- Cache Coherence: CSE 661 - Parallel and Vector ArchitecturesDocument37 pagesCache Coherence: CSE 661 - Parallel and Vector ArchitecturesZia AtiqNo ratings yet

- SystemVerilog and Verification SlidesDocument39 pagesSystemVerilog and Verification SlidesSivasubramanian Manickam100% (1)

- Training On SV AssertionsDocument37 pagesTraining On SV AssertionsSam HoneyNo ratings yet

- Verilog Interview Questions Part 1Document7 pagesVerilog Interview Questions Part 1radhakodirekka8732No ratings yet

- Using Parameterised ClassesDocument14 pagesUsing Parameterised ClassespriyajeejoNo ratings yet

- UVM Interview Questions - VLSI EncyclopediaDocument7 pagesUVM Interview Questions - VLSI EncyclopediaVIKRAMNo ratings yet

- SystemVerilog VeriflcationDocument68 pagesSystemVerilog VeriflcationDrBhoopal RaoNo ratings yet

- Lesson Plan Ordinal NumbersDocument5 pagesLesson Plan Ordinal Numbersapi-329663096No ratings yet

- Assertions: Page 1 of 2Document56 pagesAssertions: Page 1 of 2Chakita ReddyNo ratings yet

- Verilog Interview Questions 1670709109Document21 pagesVerilog Interview Questions 1670709109Ali MuhammadNo ratings yet

- Ahb2ap BridgeDocument3 pagesAhb2ap BridgeFeroz Ahmed100% (1)

- Verification Test Question Paper - MavenDocument4 pagesVerification Test Question Paper - Mavenaman nigamNo ratings yet

- Class 12 TopicsDocument43 pagesClass 12 Topicsgideontargrave7No ratings yet

- The Missing Link: The Testbench To Dut Connection: David Rich - Mentor A Siemens BusinessDocument10 pagesThe Missing Link: The Testbench To Dut Connection: David Rich - Mentor A Siemens BusinessMarko NedicNo ratings yet

- 2012 DVCon SystemVerilog 2012 PaperDocument13 pages2012 DVCon SystemVerilog 2012 Papercoolkad81No ratings yet

- Design & Verification of AMBA APB ProtocolDocument4 pagesDesign & Verification of AMBA APB ProtocolKrishnajithKjNo ratings yet

- System Verilog - Verification Methodology ManualDocument36 pagesSystem Verilog - Verification Methodology ManualpearlkrishNo ratings yet

- SVTBDocument222 pagesSVTBsandeepNo ratings yet

- Chap 6 RandomizationDocument73 pagesChap 6 RandomizationravichettyraviNo ratings yet

- 2005-SNUG-Paper SystemVerilog Unique and PriorityDocument24 pages2005-SNUG-Paper SystemVerilog Unique and Priorityvaibhav27aprilNo ratings yet

- Gate SimulationDocument10 pagesGate SimulationMahmoud WafaNo ratings yet

- Semaphores in SystemVerilog With ExamplesDocument6 pagesSemaphores in SystemVerilog With ExamplesSatish BojjawarNo ratings yet

- Missing Link: Testbench To DUT Connection by David RichDocument9 pagesMissing Link: Testbench To DUT Connection by David RichapninexNo ratings yet

- UVM Presentation DAC2011 FinalDocument105 pagesUVM Presentation DAC2011 FinalSrivalli MurthyNo ratings yet

- Advanced Verilog CodingDocument76 pagesAdvanced Verilog Coding1234GAURAVNo ratings yet

- System Verilog: Program Block & InterfaceDocument38 pagesSystem Verilog: Program Block & InterfaceMeghana VeggalamNo ratings yet

- UVM Usage For Dynamic Reconfiguration of Complex Designs DVCon India 2014 PaperDocument12 pagesUVM Usage For Dynamic Reconfiguration of Complex Designs DVCon India 2014 PaperKunal PanchalNo ratings yet

- Uvm TB FlowDocument2 pagesUvm TB FlowMeghana VeggalamNo ratings yet

- SystemVerilog PDFDocument7 pagesSystemVerilog PDFFrank ObrienNo ratings yet

- Chap 9 Functional Coverage PDFDocument46 pagesChap 9 Functional Coverage PDFmahendraNo ratings yet

- 07 AceVerification SystemVerilog Nov2005Document17 pages07 AceVerification SystemVerilog Nov2005prabhuasbNo ratings yet

- 72 UVM Callbacks Vs Factory PDFDocument1 page72 UVM Callbacks Vs Factory PDFQuastnNo ratings yet

- Notes3 PDFDocument97 pagesNotes3 PDFrahulsportyNo ratings yet

- Functional Coverage Commands in QuestasimDocument1 pageFunctional Coverage Commands in QuestasimSivaprasad GodugunuriNo ratings yet

- Implementing Communication Bridge Between I2C and APBDocument4 pagesImplementing Communication Bridge Between I2C and APBDon RajuNo ratings yet

- Cummings Why Use Classes For UVM TransactionsDocument2 pagesCummings Why Use Classes For UVM Transactionsvishwalatha sNo ratings yet

- 2013 SNUG SV Synthesizable SystemVerilog PaperDocument45 pages2013 SNUG SV Synthesizable SystemVerilog PaperNvskinIdNo ratings yet

- CummingsSNUG2014AUS UVM MessagesDocument33 pagesCummingsSNUG2014AUS UVM MessagesKalpana ChaudharyNo ratings yet

- Code CoverageDocument69 pagesCode CoverageKowsick Prasad KNo ratings yet

- What Is Assertion-Based Verification?: Active PassiveDocument4 pagesWhat Is Assertion-Based Verification?: Active PassiveAli HmedatNo ratings yet

- Xge Mac SpecDocument24 pagesXge Mac Spechackdrag100% (1)

- Systemverilog Q&A: Normal Inline Assertion ExampleDocument10 pagesSystemverilog Q&A: Normal Inline Assertion ExampleJitendraNo ratings yet

- DVCon Europe 2015 T14 PresentationDocument39 pagesDVCon Europe 2015 T14 PresentationJon DCNo ratings yet

- UVM BasicsDocument36 pagesUVM BasicsRobert slashNo ratings yet

- 2014 - Curs VerifDocument7 pages2014 - Curs VerifMihaita SmintinaNo ratings yet

- DVCon Europe 2015 T08 PresentationDocument55 pagesDVCon Europe 2015 T08 PresentationJon DCNo ratings yet

- HiddenCharmsofKoreaSOOL enDocument59 pagesHiddenCharmsofKoreaSOOL enmanchuricoNo ratings yet

- Senior Hardware Design Verification Engineer - IrelandDocument2 pagesSenior Hardware Design Verification Engineer - IrelandmanchuricoNo ratings yet

- Advanced UVM: Modeling TransactionsDocument26 pagesAdvanced UVM: Modeling TransactionsmanchuricoNo ratings yet

- Advanced Uvm Session4 How TLM WorksDocument19 pagesAdvanced Uvm Session4 How TLM WorksmanchuricoNo ratings yet

- UVMF One Bite at A Time: UVM Framework OverviewDocument22 pagesUVMF One Bite at A Time: UVM Framework OverviewmanchuricoNo ratings yet

- Vdocuments - MX Fender Performer 650 Guitar AmplifierDocument10 pagesVdocuments - MX Fender Performer 650 Guitar AmplifiermanchuricoNo ratings yet

- Axi Verification Ip V1.1: Logicore Ip Product GuideDocument97 pagesAxi Verification Ip V1.1: Logicore Ip Product Guidemanchurico0% (1)

- P-Tile Avalon Streaming IP For PCI Express User GuideDocument222 pagesP-Tile Avalon Streaming IP For PCI Express User GuidemanchuricoNo ratings yet

- Intel FPGA P-Tile Avalon Streaming IP For PCI Express Design Example User GuideDocument22 pagesIntel FPGA P-Tile Avalon Streaming IP For PCI Express Design Example User GuidemanchuricoNo ratings yet

- Advanced UVM: Understanding The Factory and ConfigurationDocument18 pagesAdvanced UVM: Understanding The Factory and ConfigurationmanchuricoNo ratings yet

- UVMF One Bite at A Time: Series IntroductionDocument7 pagesUVMF One Bite at A Time: Series IntroductionmanchuricoNo ratings yet

- Uvm-Registers Tfitzpatrick PDFDocument47 pagesUvm-Registers Tfitzpatrick PDFmanchuricoNo ratings yet

- Ug900 Vivado Logic SimulationDocument267 pagesUg900 Vivado Logic SimulationmanchuricoNo ratings yet

- Uvm Cookbook Recipe of The Month More-Uvm-Registers Tfitzpatrick PDFDocument38 pagesUvm Cookbook Recipe of The Month More-Uvm-Registers Tfitzpatrick PDFmanchuricoNo ratings yet

- Cube-40xl Amp SettingsDocument2 pagesCube-40xl Amp SettingsmanchuricoNo ratings yet

- DisplayLink USB Graphics Software For Ubuntu 5.2-Release NotesDocument3 pagesDisplayLink USB Graphics Software For Ubuntu 5.2-Release NotesmanchuricoNo ratings yet

- LP Science2 q2w5Document7 pagesLP Science2 q2w5Gaila Mae Abejuela SanorjoNo ratings yet

- C6-Cable1-2 LSSS-LN0090-01 (UTP C6 - 250MHz)Document6 pagesC6-Cable1-2 LSSS-LN0090-01 (UTP C6 - 250MHz)crisandy31No ratings yet

- Appraisal of DSE & CSEDocument31 pagesAppraisal of DSE & CSEMohammad Shaniaz IslamNo ratings yet

- Dual 15A/Single 30A Step-Down Power Module: ISL8225MDocument34 pagesDual 15A/Single 30A Step-Down Power Module: ISL8225MAnonymous QakmLc3kTINo ratings yet

- Data Sheet Ko Drum 43-401Document14 pagesData Sheet Ko Drum 43-401sokrat sebtiNo ratings yet

- Chapter 1 and Chapter 2 PowerpointDocument14 pagesChapter 1 and Chapter 2 Powerpointapi-252892423No ratings yet

- FC52Document5 pagesFC52Bassel AlmouieNo ratings yet

- Module 4 - Design of Tension MembersDocument30 pagesModule 4 - Design of Tension MembersSreelakshmi GNo ratings yet

- Civil Engineering Paper 02Document35 pagesCivil Engineering Paper 02anubhavNo ratings yet

- Anushree - VivaDocument76 pagesAnushree - VivaCarolin R 16No ratings yet

- W. Chandraprakaikul Thesis 2008Document409 pagesW. Chandraprakaikul Thesis 2008Ana-Maria RaicuNo ratings yet

- Sibunag River Development Project: Industry Sector: Business Type: Location TypeDocument4 pagesSibunag River Development Project: Industry Sector: Business Type: Location Typeemma gallosNo ratings yet

- Connector GuideDocument20 pagesConnector GuideBastian VarelaNo ratings yet

- Business Partner Application Form: Bintang Arif Kurniawan 08119002384Document1 pageBusiness Partner Application Form: Bintang Arif Kurniawan 08119002384Bintang ArifNo ratings yet

- Thesis On Cybercrime in IndiaDocument8 pagesThesis On Cybercrime in Indiakarinathomasdenver100% (2)

- Maruti Suzuki TrainingDocument37 pagesMaruti Suzuki TrainingSanu Singh0% (1)

- 2010 First Yr First I Sem SyllabusDocument36 pages2010 First Yr First I Sem SyllabusNarayana SwamyNo ratings yet

- Beamray 50R100R Data SheetDocument2 pagesBeamray 50R100R Data Sheethassan elgamriNo ratings yet

- Food Stuff From List CompaniesDocument3 pagesFood Stuff From List CompaniesListonNo ratings yet

- WFH Log Sheet 23.03 To 28.03Document6 pagesWFH Log Sheet 23.03 To 28.03sampathkumarNo ratings yet

- USB-Link™ 2 Bluetooth Edition Installation and Setup ManualDocument54 pagesUSB-Link™ 2 Bluetooth Edition Installation and Setup ManualMichael Bennett100% (2)

- Steel Fence CatalogDocument4 pagesSteel Fence CatalogtempfencingNo ratings yet

- MOI Lesson PlanDocument4 pagesMOI Lesson PlanPreeti KumariNo ratings yet

- Central Ground Water Board: Khurda DistrictDocument24 pagesCentral Ground Water Board: Khurda Districtsunil kimar nathNo ratings yet