Professional Documents

Culture Documents

Addressing Modes: SFR Registers, General Purpose Registers

Uploaded by

Gopinathan MOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Addressing Modes: SFR Registers, General Purpose Registers

Uploaded by

Gopinathan MCopyright:

Available Formats

Module VI

8051 Addressing Modes, Different types of instructions and Instruction Set, Simple programs. Peripheral Chips

for timing control - 8254/8253.

Addressing Modes

The way of accessing data is called addressing mode. The CPU can access the data in different ways by using

addressing modes. The 8051 microcontroller consists of five addressing modes such as:

Immediate Addressing Mode:

In this addressing mode, the source must be a value that can be followed by the ‘#’ and destination must be SFR

registers, general purpose registers and address. It is used for immediately storing the value in the memory

registers.

Syntax:

MOV A, #20h //A is an accumulator register, 20 is stored in the A//

MOV R0,#15 // R0 is a general purpose register; 15 is stored in the R0 register//

MOV P0, #07h //P0 is a SFR register;07 is stored in the P0//

MOV 20h,#05h //20h is the address of the register; 05 stored in the 20h//

MOV DPTR,#4532H // DPTR=4532H.

Register Addressing Mode:

In this addressing mode, the source and destination must be a register, but not general purpose registers. So the

data is not moved within the general purpose bank registers.

Syntax:

MOV A, B; // A is a SFR register, B is a general purpose register//

MOV R0, R1 //Invalid instruction, GPR to GPR not possible//

Direct Addressing Mode

In this addressing mode, the source or destination (or both source and destination) must be an address, but not

value.

Direct addressing mode In direct addressing mode, the data is in a RAM memory location whose address is

known, and this address is given as a part of the instruction. Contrast this with the immediate addressing mode in

which the operand itself is provided with the instruction.

CSE ,ICET Page 1

Syntax:

MOV A,20h // 20h is an address; A is a register//

MOV 00h, 07h // both are addressed of the GPS registers//

Indirect Addressing Mode (Register Indirect mode):

In this addressing mode, the source or destination (or destination or source) must be a indirect address, but not a

value

In the register indirect addressing mode, a register is used as a pointer to the data. If the data is inside the CPU,

only register R0 and R1 are used for this purpose. In other words, R2-R7cannot be used to hold the address of an

operand located in RAM when using this addressing mode.

When R0 and R1 are used as pointers, that is, when they hold the address of RAM locations, they must be

preceded by the “@” sign.

Ex: - MOV A,@R0 // move contents of RAM location whose address is held by R0 into A.

MOV @R1, B // move contents of B RAM location whose address is held by R1

Base Index Addressing Mode:

This addressing mode is used to read the data from the external memory or ROM memory. All addressing modes

cannot read the data from the code memory. The code must read through the DPTR register. The DPTR is used to

point the data in the code or external memory.

Syntax:

MOVC A, @A+DPTR //C indicates code memory//

MOCX A, @A+DPTR // X indicate external memory//

Because the data elements are stored in the program space ROM of the 8051,it uses the instruction MOVC instead

of MOV.

The 16-bit register DPTR and register “A” are used to form the data element stored in on-chip ROM.

Instruction Set

The 8051 microcontroller can follow CISC instructions with Harvard architecture. In case of the 8051

programming different types of CISC instructions include:

Data Transfer Instruction set

Arithmetic Instruction set

Branching Instruction set

- Conditional Branching

- Unconditional Branching

Logical Instruction set

Bit Oriented Instruction set

CSE ,ICET Page 2

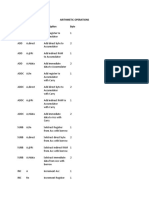

Data Transfer Instruction set

Addressing No. of bytes

Mnemonics Operational description

mode occupied

Copy the immediate data num in

Mov a,#num immediate 2

to acc

Mov Rx,A Copy the data from acc to Rx register 1

Mov A,Rx Copy the data from Rx to acc register 1

Copy the immediate data num in

Mov Rx,#num immediate 2

to Rx

Copy the data from direct

Mov A,addr direct 2

address to acc

Copy the data from acc to direct

Mov addr,A direct 2

address

Copy the immediate data num in

Mov addr,#num direct 3

to direct address

Copy the data from address2 to

Mov addr1,addr2 direct 3

address1

Copy the data from direct

Mov Rx,addr direct 2

address to Rx

Copy the data from Rx to direct

Mov addr,Rx direct 2

address

Copy the data in acc to address

Mov @Rp,A Indirect 1

in Rp

Copy the data that is at address

Mov A,@Rp Indirect 1

in Rp to acc

Copy the data that is at address

Mov addr,@Rp Indirect 2

in Rp to address

Copy the data in address to

Mov @Rp,addr Indirect 2

address in Rp

Copy the immediate byte num to

Mov @Rp,#num Indirect 2

the address in Rp

Copy the content of external add

Movx A,@Rp Indirect 1

in Rp to acc

CSE ,ICET Page 3

Copy the content of external add

Movx A,@DPTR Indirect 1

in DPTR to acc

Copy the content of acc to the

Movx @Rp,A Indirect 1

external add in Rp

Copy the content of acc to the

Movx @DPTR,A Indirect 1

external add in DPTR

The address is formed by adding

Movc A,@a+DPTR acc and DPTR and its content is indirect 1

copied to acc

The address is formed by adding

Movc A, @a+PC acc and PC and its content is indirect 1

copied to acc

Increment SP and copy the data

Push addr from source add to internal RAM Direct 2

address contained in SP

copy the data from internal RAM

address contained in SP to

Pop addr direct 2

destination add and decrement

SP

Exchange the data between acc

Xch A, Rx Register 1

and Rx

Exchange the data between acc

Xch A, addr Direct 2

and given add

Exchange the data between acc

Xch A,@Rp Indirect 1

and address in Rp

Exchange only lower nibble of

Xchd A, @Rp indirect 1

acc and address in Rp

Arithmetic Instruction Set:

The arithmetic instructions perform the basic operations such as:

Addition

Multiplication

CSE ,ICET Page 4

Subtraction

Division

DAA- Decimal adjust after addition

Addition:

ORG 0000h

MOV R0, #03H // move the value 3 to the register R0//

MOV A, #05H // move the value 5 to accumulator A//

ADD A, 00H // addA value with R0 value and stores the result inA//

END

Multiplication:

ORG 0000h

MOV R0, #03H // move the value 3 to the register R0//

MOV A, #05H // move the value 5 to accumulator A//

MUL A, 03H // Multiplied result is stored in the Accumulator A //

END

Subtraction:

ORG 0000h

MOV R0, #03H // move the value 3 to register R0//

MOV A, #05H // move the value 5 to accumulator A//

SUBB A, 03H // Result value is stored in the Accumulator A //

END

Division:

ORG 0000h

MOV R0, #03H // move the value 3 to register R0//

MOV A, #15H // move the value 5 to accumulator A//

DIV A, 03H // final value is stored in the Accumulator A //

END

CSE ,ICET Page 5

Logical Instruction Set:

Syntax:

MOV A, #20H /00100000/

MOV R0, #03H /00000101/

ORL A, R0 //00100000/00000101=00000000//

Syntax:

MOV A, #20H /00100000/

MOV R0, #03H /00000101/

ANL A, R0

3. Syntax:

MOV A, #20H /00100000/

MOV R0, #03H /00000101/

XRL A, R0

The 8051 microcontroller consist four shift operators:

RR —> Rotate Right

RRC —>Rotate Right through carry

RL —> Rotate Left

RLC —>Rotate Left through carry

Rotate Right (RR):

In this shifting operation, the MSB becomes LSB and all bits shift towards right side bit-by-bit, serially.

Syntax:

MOV A, #25h

RRA

Rotate Left (RL):

In this shifting operation, the MSB becomes LSB and all bits shift towards Left side bit-by-bit, serially.

CSE ,ICET Page 6

Syntax:

MOV A, #25h

RLA

RRC Rotate Right through Carry:

In this shifting operation, the LSB moves to carry and the carry becomes MSB, and all the bits are shift towards

right side bit by bit position.

Syntax:

MOV A, #27h

RRC A

RLC Rotate Left through Carry:

In this shifting operation, the MSB moves to carry and the carry becomes LSB and all the bits shift towards left

side in a bit-by-bit position.

Syntax:

MOV A, #27h

RLC A

Branch Instruction set

Conditional Instructions

The CPU executes the instructions based on the condition by checking the single bit status or byte status. The

8051microcontroller consists of various conditional instructions such as:

Call and Jump Instructions:

The call and jump instructions are used to avoid the code replication of the program. When some specific code

used more than once in different places in the program, if we mention specific name to code then we could use

that name anywhere in the program without entering a code for every time. This reduces the complexity of the

program.

CSE ,ICET Page 7

LJMP (long jump)

LJMP is an unconditional long jump. It is a 3-byte instruction in which the first byte is the opcode, and the second

and third bytes represent the 16-bit address of the target location.

SJMP (short jump)

In this 2-byte instruction, the first byte is the opcode and the second byte is the relative address of the target

location.

AJMP

Function: Absolute Jump Within 2K Block

Syntax: AJMP code address

Loop Instructions:

The loop instructions are used to repeat the block each time while performing the increment and decrement

operations. The 8051 microcontroller consist two types of loop instructions:

CJNE —> compare and jump if not equal

DJNZ —> decrement and jump if not zero

CSE ,ICET Page 8

Return instructions: RET and RETI(Return from subroutine and Return from interrupt service routine)

BIT-Oriented Instructions

Mnemonic Description Byte Cycle

CLR C Clears the carry flag 1 1

CLR bit Clears the direct bit 2 3

SETB C Sets the carry flag 1 1

SETB bit Sets the direct bit 2 3

CPL C Complements the carry flag 1 1

CPL bit Complements the direct bit 2 3

ANL C,bit AND direct bit to the carry flag 2 2

ANL C,/bit AND complements of direct bit to the carry flag 2 2

ORL C,bit OR direct bit to the carry flag 2 2

ORL C,/bit OR complements of direct bit to the carry flag 2 2

MOV C,bit Moves the direct bit to the carry flag 2 2

MOV bit,C Moves the carry flag to the direct bit 2 3

Simple Programs using 8051

Write A Program To Add Two 8 Bit Number And Store The Result At External Memory Location 2050H.

ORG 0000H

MOV A, #05H

MOV R, #09H

ADD A, R1

MOV DPTR, #2050H // Initialize DPTR with 2050 address

MOVX @ DPTR, A // Move content of A into 2050. We can see output in 2050 location

CSE ,ICET Page 9

AGAIN: SJMP AGAIN // this loop work infinitely, indicates end of the program

INPUT:

A=05H

R1=09H

OUTPUT:

2050 = 0EH..

Subtraction of two 8 bit numbers

ORG 4100

MOV A,#data1

SUBB A,#data2

MOV DPTR,#4500

MOVX @DPTR,A // X indicate external memory

HERE: SJMP HERE

Input: 66

23

Output: 43 (4500)

Assembly program for Simple 2 16bit number addition using registers

ORG 0000H

MOV R7, #34H // SAY R7 HAS LOWER BYTE 34

MOV R6, #24H // R6 HAS HIGHER BYTE 24

// MAKING NUMBER 2434

MOV R5,#45H // ANOTHER NUMBER SAY 3345

MOV R4, #33H //WITH R5 LOWER BYTE 45

// R4 HIGHER BYTE 33

MOV A, R5

ADD A , R7

MOV R3, A

MOV A, R6

ADDC A, R4

MOV R2,A

END

Multiplication of two 8 bit numbers

MOV DPTR,#8600H // initialize DPTR with 8600

CSE ,ICET Page 10

MOVX A,@DPTR // Move content of DPTR into A

MOV B,A

MOV DPTR,#8601H // Read the second operand from 8601 location

MOVX A,@DPTR

MUL AB

MOV DPTR,#8701H // Initialize DPTR with 8701 for storing output data

MOVX @DPTR,A

MOV DPTR,#8700H // The least significant byte of the result is placed in the Accumulator and the

// most significant-byte is placed in the "B" register. So we need to display from B

MOV A,B

MOVX @DPTR,A

E: SJMP E

Factorial of a number using subroutine

ORG 0000

MOV R1,#05

MOV A, R1

LCALL FACT

E: SJMP E

FACT:

CJNE R1,#00,UP // compare R1 and 00 if it is not equal go to UP

RET

UP: DEC R1 // Decrement R1 by one ie 4

MOV B, R1

MUL AB

LJMP FACT

Sorting of n numbers

ORG 0000H

MOV R7,#4

loop1:MOV R0,#40H

MOV R6,#04

loop:MOV A,@R0

INC R0

MOV 50H,@R0

CJNE A, 50H, next

SJMP down

next:JC down

CSE ,ICET Page 11

MOV @R0,A

DEC R0

MOV @R0,50H

down:DJNZ R6,loop

DJNZ R7,loop1

END

To add n bytes stored in external RAM(Sum of n numbers)

MOV R0, #0A

MOV R1, #00

MOV DPTR, #9000

Loop: MOVX A, @DPTR

ADD A, R1

MOV R1, A

INC DPTR

DJNZ R0, LOOP

Fibonacci series (Refer Page 87 in solved Text book)

MOV R1, 30 H

MOV R7,#40H

MOV @R7, #00H

INC R7

MOV @R7, #01H

MOV R5, #42H

DEC R1

DEC R1

DEC R7

LOOP: MOV A, @R7

INC R7

ADD A, @R7

MOV @R5,A

INC R5

DJNZ R1, LOOP

STOP: SJMP STOP

CSE ,ICET Page 12

8254/8253 Programmable Interval Timer

The Intel 8254 is a counter/timer device designed to solve the common timing control problems in microcomputer

system design.

It provides three independent 16-bit counters, each capable of handling clock inputs up to 10 MHz.

All modes are software programmable.

The 8254 is a superset of the 8253.

The 8254 uses HMOS technology and comes in a 24-pin plastic or CERDIP package.

These three counters can be programmed for either binary or BCD count.

It is compatible with almost all microprocessors.

8254 has a powerful command called READ BACK command, which allows the user to check the count

value, the programmed mode, the current mode, and the current status of the counter.

Data Bus Buffer

It is a tri-state, bi-directional, 8-bit buffer, which is used to interface the 8253/54 to the system data bus. It has

three basic functions −

Programming the modes of 8253/54.

Loading the count registers.

Reading the count values.

Read/Write Logic

It includes 5 signals, i.e. RD, WR, CS, and the address lines A0 & A1. Address lines A0 & A1 of the CPU are

connected to lines A0 and A1 of the 8253/54, and CS is tied to a decoded address. The control word register and

counters are selected according to the signals on lines A0 & A1.

CSE ,ICET Page 13

Control Word Register

This register is accessed when lines A0 & A1 are at logic 1. It is used to write a command word, which specifies

the counter to be used, its mode, and either a read or write operation.

Counters

Each counter consists of a single, 16 bit-down counter, which can be operated in either binary or BCD. Its input

and output is configured by the selection of modes stored in the control word register. The programmer can read

the contents of any of the three counters without disturbing the actual count in process.

Each counter has 2 input signals CLK and GATE and one output signal OUT.

GATE is used to enable or disable counters

Pin Diagram

D7-D0: Data lines

A1,A0: Selects one of the 4 internal registers in the 8254

CS: Enables the 8254

CLK: Timing source for each of the 3 timers. e.g. pulses applied to CLK0 are used to decrement counter 0.

G: Gate = 1, enables the counter.

e.g. when G0=1, counter 0 decrements on CLK

CSE ,ICET Page 14

OUT: Timer waveform output (a clock or a pulse)

RD: Causes data to be read from the 8254 (IORC)

WR: Causes data to be written to 8254 (IOWC)

Difference between 8253 and 8254

8253 8254

Its operating frequency is 0 - 2.6 MHz Its operating frequency is 0 - 10 MHz

It uses N-MOS technology It uses H-MOS technology

Read-Back command is not available Read-Back command is available

Reads and writes of the same counter Reads and writes of the same counter

cannot be interleaved. can be interleaved.

Programming the 8254(Control word register)

Counter Latch Command

- Selected counter has its content transferred into temporary latch, which can be read by CPU.

CSE ,ICET Page 15

Read back command

Modes of operation of 8254

MODE 0: INTERRUPT ON TERMINAL COUNT

In this mode OUT is low. Once a count is loaded the counter is decremented after every cycle, and when count

reaches zero, the OUT goes high.

This can be used as an interrupt. The OUT remains high until a new count or command word is loaded.

MODE 1: HARDWARE RETRIGGERABLE ONE SHOT

In this mode OUT is initially high. When gate is triggered, the OUT goes low, and at the end of count it goes high

again, thus generating a one shot pulse.

A pulse input has to be sent to gate input in order to trigger the counter

MODE 2: RATE GENERATOR

The mode is used to generate a pulse equal to given clock period at a given interval.

When a count is loaded, the OUT stays high until count reaches 1 and then OUT goes low for 1 clock period then

gets reloaded automatically and this is how pulse gets generated continuously.

CSE ,ICET Page 16

MODE 3: SQUARE WAVE GENERATOR

In this a continuous square wave with period equal to count is generated.

The frequency of square wave = frequency of clock divide by count. if count (N) is odd pulse stay high for (N +

1)/2 and low for (N – 1)/2.if count is even output remains high for half the count and low for the rest half of the

count.

MODE 4: SOFTWARE TRIGGERED STROBE

In this mode OUT is initially high, it goes low for one clock period at the end of count.

The count must be reloaded for subsequent outputs.

These pulses can be used as strobe for interfacing MP with peripherals

MODE 5: HARDWARE TRIGGERED STROBE

Same as MODE4 except that it is triggered by rising pulse at gate.

CSE ,ICET Page 17

You might also like

- MCQ Questions For Class 8 Science Chapter 17 Stars and The Solar System With AnswersDocument12 pagesMCQ Questions For Class 8 Science Chapter 17 Stars and The Solar System With AnswersGopinathan MNo ratings yet

- Question & Answers For Microcontrollers and Its Applications Btech Iv-I Semester (Ece A & B)Document13 pagesQuestion & Answers For Microcontrollers and Its Applications Btech Iv-I Semester (Ece A & B)Krapa Sai PraveenNo ratings yet

- PowerFlex OS v3.6 CLI Reference GuideDocument247 pagesPowerFlex OS v3.6 CLI Reference GuideAvi KinetNo ratings yet

- Moshell For Msrbs Du&BbDocument394 pagesMoshell For Msrbs Du&BbAnonymous XZnkpMec100% (2)

- Conceptual Programming: Conceptual Programming: Learn Programming the old way!From EverandConceptual Programming: Conceptual Programming: Learn Programming the old way!No ratings yet

- A Complete Study Guide For AWS Certified Solutions Architect Associate Exam PDFDocument7 pagesA Complete Study Guide For AWS Certified Solutions Architect Associate Exam PDFAkshay SharmaNo ratings yet

- 8051 Instruction Set: Data Moving or Handling InstructionsDocument3 pages8051 Instruction Set: Data Moving or Handling InstructionsDHANANJAY POPAT MANENo ratings yet

- 8051 Instruction Set: FacebooktwitterlinkedinredditpinterestshareDocument13 pages8051 Instruction Set: FacebooktwitterlinkedinredditpinterestshareManjunath KV Assistant Professor (CSE)No ratings yet

- Instruction SetDocument18 pagesInstruction SetGirl OnFireNo ratings yet

- Instruction SetDocument22 pagesInstruction SetmeghaNo ratings yet

- 8051 Instruction - SetDocument48 pages8051 Instruction - SetJibu JoseNo ratings yet

- Microcontroller Codes For PracticeDocument10 pagesMicrocontroller Codes For PracticeAditya KulkarniNo ratings yet

- 8051 Notes 3rd Unit PDFDocument36 pages8051 Notes 3rd Unit PDFfwefNo ratings yet

- 8051 Programming Sec B Elect M&MDocument25 pages8051 Programming Sec B Elect M&MAbujar ShaikhNo ratings yet

- 8051 Instruction SetDocument47 pages8051 Instruction SetSanthosh CricketNo ratings yet

- Instruction Set of 8051Document33 pagesInstruction Set of 8051Swetha RamasamyNo ratings yet

- UNIT 2 - ppt200910Document73 pagesUNIT 2 - ppt200910Yogesh GowdaNo ratings yet

- Moving DataDocument30 pagesMoving DataJoJoMoNo ratings yet

- 8051microcontroller Ayala (2) 59 114Document56 pages8051microcontroller Ayala (2) 59 114Kareem QpNo ratings yet

- Instruction Set 8051 - v1Document10 pagesInstruction Set 8051 - v1avinashNo ratings yet

- Programming Model of 8051Document45 pagesProgramming Model of 8051Mayuri ChebleNo ratings yet

- Fundamentals of Microcontroller & Its Application: Unit-IiDocument10 pagesFundamentals of Microcontroller & Its Application: Unit-IiRajan PatelNo ratings yet

- 6 8051-AssemblyDocument18 pages6 8051-AssemblyKritika SinghNo ratings yet

- Addressing Mode of 8051Document11 pagesAddressing Mode of 8051Harsh RajNo ratings yet

- Instruction Format 8051Document26 pagesInstruction Format 8051alex24arulNo ratings yet

- Introduction To 8085 MPDocument16 pagesIntroduction To 8085 MPDeepikaNo ratings yet

- HTTPDocument5 pagesHTTPkamalakarbNo ratings yet

- Instruction Set Summary: (I. Scott Mackenzie)Document12 pagesInstruction Set Summary: (I. Scott Mackenzie)saravanan_KLUNo ratings yet

- Topic 4 Assembly Language Programming (ISMAIL - FKEUTM 20192020)Document107 pagesTopic 4 Assembly Language Programming (ISMAIL - FKEUTM 20192020)Aya AmirNo ratings yet

- Asembbly Operation & Sintax Program Arithmetic Operations Mnemonic Description Bytes CyclesDocument6 pagesAsembbly Operation & Sintax Program Arithmetic Operations Mnemonic Description Bytes CyclesArief HamidNo ratings yet

- 8051 Add Sub ProgramDocument4 pages8051 Add Sub ProgramGopinathan MNo ratings yet

- Microcontroller Instruction SetDocument73 pagesMicrocontroller Instruction Set4SI21EC037 MONOJ S BNo ratings yet

- 8051 Instruction SetDocument5 pages8051 Instruction Setarul0% (1)

- MCS-51 Instruction: Arithmetic OperationsDocument3 pagesMCS-51 Instruction: Arithmetic OperationsAgus GunawanNo ratings yet

- 6 - ES - 8051 MC - ProgrammingDocument83 pages6 - ES - 8051 MC - ProgrammingSaket GoluNo ratings yet

- Addressing Modes 8051Document37 pagesAddressing Modes 80514SI21EC037 MONOJ S BNo ratings yet

- Microcontroller Lab ManualDocument57 pagesMicrocontroller Lab ManualTrinetra mNo ratings yet

- Arithmetic OperationsDocument2 pagesArithmetic OperationsRoselee Ann MontevirgenNo ratings yet

- Assembly Language ProgrammingDocument11 pagesAssembly Language ProgrammingAnonymous 4mPIMAL7zNo ratings yet

- Mci 4Document9 pagesMci 4Het PatelNo ratings yet

- Introduction To Address ModesDocument9 pagesIntroduction To Address ModeskamalakarbNo ratings yet

- Ece3430 Lecture 04Document17 pagesEce3430 Lecture 04Msk MskNo ratings yet

- Himpunan Instruksi 8051Document2 pagesHimpunan Instruksi 8051Hermin Kartika SariNo ratings yet

- 8051 Codding MapDocument1 page8051 Codding MapSelam12No ratings yet

- It 8051Document3 pagesIt 8051appalaraju2010No ratings yet

- UG - EC303 DSP Part-3 Fixed Point DSP Addressing Modes - PrintDocument25 pagesUG - EC303 DSP Part-3 Fixed Point DSP Addressing Modes - PrintShreyas TaterNo ratings yet

- 02.addressing ModesDocument10 pages02.addressing Modessasi_kar_1No ratings yet

- Instructions SetDocument81 pagesInstructions Setchintu333No ratings yet

- Microcontroller - 10ES42Document13 pagesMicrocontroller - 10ES42Laxman nadigNo ratings yet

- 8051 Addressing ModesDocument73 pages8051 Addressing ModesKUSHAGRA GUPTA 13BEE0102No ratings yet

- Set de Instrucciones DLXDocument2 pagesSet de Instrucciones DLXe1s1v09092023No ratings yet

- Addressing Modes & Instructions Set of 8051 Micro ControllerDocument29 pagesAddressing Modes & Instructions Set of 8051 Micro ControllerManjunath KV Assistant Professor (CSE)No ratings yet

- Addressing Modes in 8051Document7 pagesAddressing Modes in 8051Sundar SathappanNo ratings yet

- Lecture 4Document18 pagesLecture 4Ritesh KumarNo ratings yet

- Lecture 4Document15 pagesLecture 4bndgdd cncncjNo ratings yet

- Control Transfer Instructions and Programming Using 8051 MicrocontrolleDocument72 pagesControl Transfer Instructions and Programming Using 8051 MicrocontrollePujaChaudhuryNo ratings yet

- Module - 2: 8051 Instruction SetDocument39 pagesModule - 2: 8051 Instruction SetPramod PatilNo ratings yet

- Register Structure and Addressing ModesDocument8 pagesRegister Structure and Addressing ModesMruthika KumaraswamyNo ratings yet

- Immediate Addressing Direct Addressing Indirect Addressing External Direct Code IndirectDocument4 pagesImmediate Addressing Direct Addressing Indirect Addressing External Direct Code IndirectJayshil ParekhNo ratings yet

- ROUTING INFORMATION PROTOCOL: RIP DYNAMIC ROUTING LAB CONFIGURATIONFrom EverandROUTING INFORMATION PROTOCOL: RIP DYNAMIC ROUTING LAB CONFIGURATIONNo ratings yet

- LEARN MPLS FROM SCRATCH PART-B: A Beginners guide to next level of networkingFrom EverandLEARN MPLS FROM SCRATCH PART-B: A Beginners guide to next level of networkingNo ratings yet

- 3 8th Standard Term 3 5 in 1 Sura Guides Notes Download Tamil Medium 2Document121 pages3 8th Standard Term 3 5 in 1 Sura Guides Notes Download Tamil Medium 2Gopinathan MNo ratings yet

- Data TransferDocument4 pagesData TransferGopinathan MNo ratings yet

- Unit - I Difference Between Microprocessor and MicrocontrollerDocument30 pagesUnit - I Difference Between Microprocessor and MicrocontrollerGopinathan MNo ratings yet

- Es IiiDocument12 pagesEs IiiGopinathan MNo ratings yet

- 2 Chapter 1. Introduction To The Mc9S08Qg4/8 HardwareDocument3 pages2 Chapter 1. Introduction To The Mc9S08Qg4/8 HardwareGopinathan MNo ratings yet

- Session Paper Number of Questions Marks Duration: First I 50 ×2 100 1 Hours 100 Questions 100×2 200 2 HoursDocument5 pagesSession Paper Number of Questions Marks Duration: First I 50 ×2 100 1 Hours 100 Questions 100×2 200 2 HoursGopinathan MNo ratings yet

- Provisional Application FormDocument1 pageProvisional Application FormGopinathan MNo ratings yet

- 17feb Physics PiiiDocument19 pages17feb Physics PiiiGopinathan MNo ratings yet

- Cach25C - Chemistry - Ii: Öpõkuqøn Dû Gßóõà Gßú?Document6 pagesCach25C - Chemistry - Ii: Öpõkuqøn Dû Gßóõà Gßú?Gopinathan MNo ratings yet

- Periyar University: Procedure To Apply For CertificatesDocument2 pagesPeriyar University: Procedure To Apply For CertificatesGopinathan MNo ratings yet

- PG TRB PHYSICS STUDY MATERIAL - PDF'Document150 pagesPG TRB PHYSICS STUDY MATERIAL - PDF'Gopinathan M83% (12)

- Paper-III Paper-III Paper-III Paper-III Chemical Science Chemical Science Chemical Science Chemical ScienceDocument32 pagesPaper-III Paper-III Paper-III Paper-III Chemical Science Chemical Science Chemical Science Chemical ScienceGopinathan MNo ratings yet

- Chemical Science Chemical Science Chemical Science Chemical ScienceDocument32 pagesChemical Science Chemical Science Chemical Science Chemical ScienceGopinathan MNo ratings yet

- Engineering Materials and Metallurgy Questions For Campus Interviews - SanfoundryDocument9 pagesEngineering Materials and Metallurgy Questions For Campus Interviews - SanfoundryGopinathan MNo ratings yet

- Physical Science: Signature and Name of InvigilatorDocument28 pagesPhysical Science: Signature and Name of InvigilatorGopinathan MNo ratings yet

- Mars Earth Mercury VenusDocument7 pagesMars Earth Mercury VenusGopinathan MNo ratings yet

- 2 Marks MPDocument15 pages2 Marks MPGopinathan MNo ratings yet

- 8 Class Stars and Solar System The Universe MCQ Formative Test Paper With SolutionDocument6 pages8 Class Stars and Solar System The Universe MCQ Formative Test Paper With SolutionGopinathan MNo ratings yet

- Electronics Lab 2019 G-UmadeviDocument61 pagesElectronics Lab 2019 G-UmadeviGopinathan MNo ratings yet

- Rockstar JunkiesDocument8 pagesRockstar Junkiesapi-3811622No ratings yet

- Java Notes-2.Document142 pagesJava Notes-2.killerboy5652No ratings yet

- SSL Certificate ImplementationDocument3 pagesSSL Certificate ImplementationJaved AlamNo ratings yet

- JN0-103 Junos, Associate (JNCIA-Junos) Juniper 50 v2021-02-26 119 649Document17 pagesJN0-103 Junos, Associate (JNCIA-Junos) Juniper 50 v2021-02-26 119 649Amine BoubakeurNo ratings yet

- Windows Server Interview Questions and Answers PDF - Google SearchDocument2 pagesWindows Server Interview Questions and Answers PDF - Google SearchAshish kumar mishraNo ratings yet

- 12 CS Practical File Term-2 2023-24Document18 pages12 CS Practical File Term-2 2023-24preeyanshmehtaNo ratings yet

- Lab Exercise - Lesson 2Document2 pagesLab Exercise - Lesson 2Cj Nicole JacintoNo ratings yet

- UNIT II Application Development: TCP Echo ServerDocument38 pagesUNIT II Application Development: TCP Echo ServerSundariNo ratings yet

- Camouflage Technique Based Multifunctional Army RobotDocument3 pagesCamouflage Technique Based Multifunctional Army RobotKarthik SNo ratings yet

- Lesson 4Document9 pagesLesson 4Ahmed MujtabaNo ratings yet

- Software Requirement Specification: Orchid Auction SystemDocument17 pagesSoftware Requirement Specification: Orchid Auction SystemSáng Đặng NgọcNo ratings yet

- Reanibex 300 - Presentacion 2013Document17 pagesReanibex 300 - Presentacion 2013Josiel MarlosNo ratings yet

- Compiler Construction CS-4207: Instructor Name: Atif IshaqDocument13 pagesCompiler Construction CS-4207: Instructor Name: Atif IshaqFaisal ShehzadNo ratings yet

- CF ProjectDocument11 pagesCF ProjectapakkiNo ratings yet

- Amcrest+Http+API+9 202Document651 pagesAmcrest+Http+API+9 202nmccomputerNo ratings yet

- Casio wk1800 Keyboard SMDocument44 pagesCasio wk1800 Keyboard SMღ•Mika Chan•ღNo ratings yet

- Object-Oriented and Classical Software Engineering: Stephen R. SchachDocument63 pagesObject-Oriented and Classical Software Engineering: Stephen R. Schachgoflux pwnsNo ratings yet

- Mobile Attendance SystemDocument17 pagesMobile Attendance Systemsamten wangchukNo ratings yet

- Application Manual RV-3028-C7: Extreme Low Power Real-Time Clock Module With I C-Bus InterfaceDocument116 pagesApplication Manual RV-3028-C7: Extreme Low Power Real-Time Clock Module With I C-Bus InterfaceNelson Pimiento SerranoNo ratings yet

- OCI-IAM LabDocument15 pagesOCI-IAM LabPatrickNo ratings yet

- 25AA256/25LC256: 256K SPI Bus Serial EEPROMDocument32 pages25AA256/25LC256: 256K SPI Bus Serial EEPROMmelquisedecNo ratings yet

- r05410310 Artificial IntelligenceDocument4 pagesr05410310 Artificial IntelligenceSRINIVASA RAO GANTANo ratings yet

- Progress Test 02Document21 pagesProgress Test 02andrewlaurenNo ratings yet

- App SRM Unit 4 NotesDocument48 pagesApp SRM Unit 4 NotesHarshit BatraNo ratings yet

- Functions of The OSDocument1 pageFunctions of The OSÑámè ŢħómäŝNo ratings yet

- Web Technology LabDocument29 pagesWeb Technology Labnishant99djNo ratings yet

- CH 03 - OS8e - EdtDocument57 pagesCH 03 - OS8e - EdtAfiq AimanNo ratings yet