Professional Documents

Culture Documents

Avr Cpu Core: Figure 6-1. Block Diagram of The AVR Architecture

Uploaded by

salarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Avr Cpu Core: Figure 6-1. Block Diagram of The AVR Architecture

Uploaded by

salarCopyright:

Available Formats

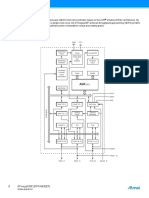

6.

AVR CPU Core

6.1 Overview

This section discusses the AVR® core architecture in general. The main function of the CPU core is to ensure correct

program execution. The CPU must therefore be able to access memories, perform calculations, control peripherals, and

handle interrupts.

Figure 6-1. Block Diagram of the AVR Architecture

Data Bus 8-bit

Flash Program Status and

Program Counter Control

Memory

Interrupt

32 x 8

Unit

General

Instruction

Purpose

Register

Registers SPI

Indirect Addressing Unit

Instruction

Direct Addressing

Decoder Watchdog

ALU Timer

Control Lines Analog

Comparator

I/O Module 1

Data

SRAM

I/O Module 2

I/O Module n

EEPROM

I/O Lines

In order to maximize performance and parallelism, the AVR uses a harvard architecture – with separate memories and

buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one

instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions

to be executed in every clock cycle. The program memory is in-system reprogrammable flash memory.

ATmega328P [DATASHEET] 9

7810D–AVR–01/15

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5796)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- 8.2 Clock Sources: 8.1.4 Asynchronous Timer Clock - CLKDocument1 page8.2 Clock Sources: 8.1.4 Asynchronous Timer Clock - CLKsalarNo ratings yet

- 8.3 Low Power Crystal Oscillator: Figure 8-2Document1 page8.3 Low Power Crystal Oscillator: Figure 8-2salarNo ratings yet

- System Clock and Clock OptionsDocument1 pageSystem Clock and Clock OptionssalarNo ratings yet

- Oscillator Source / Power Conditions Start-Up Time From Power-Down and Power-Save Additional Delay From Reset (V 5.0V) Cksel0 SUT1..0Document1 pageOscillator Source / Power Conditions Start-Up Time From Power-Down and Power-Save Additional Delay From Reset (V 5.0V) Cksel0 SUT1..0salarNo ratings yet

- 7.6 Register Description: 7.5.1 General Purpose I/O RegistersDocument1 page7.6 Register Description: 7.5.1 General Purpose I/O RegisterssalarNo ratings yet

- Sbic RJMP: Wait For Completion of Previous WriteDocument1 pageSbic RJMP: Wait For Completion of Previous WritesalarNo ratings yet

- Avr Memories: Figure 7-1. Program Memory Map Atmega328PDocument1 pageAvr Memories: Figure 7-1. Program Memory Map Atmega328PsalarNo ratings yet

- Figure 8-3. Crystal Oscillator ConnectionsDocument1 pageFigure 8-3. Crystal Oscillator ConnectionssalarNo ratings yet

- Eepm1 Eepm0 Programming Time Operation: Table 7-1. EEPROM Mode BitsDocument1 pageEepm1 Eepm0 Programming Time Operation: Table 7-1. EEPROM Mode BitssalarNo ratings yet

- 8.5 Low Frequency Crystal Oscillator: Table 8-7Document1 page8.5 Low Frequency Crystal Oscillator: Table 8-7salarNo ratings yet

- 7.4 EEPROM Data Memory: Section 27. "Memory Programming" On Page 241Document1 page7.4 EEPROM Data Memory: Section 27. "Memory Programming" On Page 241salarNo ratings yet

- Pin Configurations: Figure 1-1. PinoutDocument1 pagePin Configurations: Figure 1-1. PinoutsalarNo ratings yet

- 6.3.1 SREG - AVR Status Register: - Bit 7 - I: Global Interrupt EnableDocument1 page6.3.1 SREG - AVR Status Register: - Bit 7 - I: Global Interrupt EnablesalarNo ratings yet

- In Cli Sbi Sbi Out: Store SREG ValueDocument1 pageIn Cli Sbi Sbi Out: Store SREG ValuesalarNo ratings yet

- 7.3 SRAM Data Memory: Figure 7-2Document1 page7.3 SRAM Data Memory: Figure 7-2salarNo ratings yet

- Atmel 0013Document1 pageAtmel 0013salarNo ratings yet

- Figure 2-1. Block DiagramDocument1 pageFigure 2-1. Block DiagramsalarNo ratings yet

- 7 Atmega328P (Datasheet) : 7810D-Avr-01/15Document1 page7 Atmega328P (Datasheet) : 7810D-Avr-01/15salarNo ratings yet

- 6.6 Instruction Execution Timing: 6.5.1 SPH and SPL - Stack Pointer High and Stack Pointer Low RegisterDocument1 page6.6 Instruction Execution Timing: 6.5.1 SPH and SPL - Stack Pointer High and Stack Pointer Low RegistersalarNo ratings yet

- 1.1 Pin Descriptions: Atmega328P (Datasheet) 4Document1 page1.1 Pin Descriptions: Atmega328P (Datasheet) 4salarNo ratings yet

- 6.4 General Purpose Register File: Figure 6-2Document1 page6.4 General Purpose Register File: Figure 6-2salarNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (589)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Module1 UPDDocument72 pagesModule1 UPDZhanzhi LiuNo ratings yet

- MPMC Lesson PlanDocument3 pagesMPMC Lesson PlanASUTOSH PATNAIKNo ratings yet

- Background: The First x86 DesignDocument6 pagesBackground: The First x86 Designmayur_5252No ratings yet

- Logical Instructions in 8086 Micro ProcessorDocument21 pagesLogical Instructions in 8086 Micro ProcessorGANGADHARA SAIPRASANNANo ratings yet

- Spesifikasi Aplikasi Materi Kursus Fundamental LepkomDocument2 pagesSpesifikasi Aplikasi Materi Kursus Fundamental LepkomSultan AdityaNo ratings yet

- Lect5 DctranDocument36 pagesLect5 DctranMaaruf AliNo ratings yet

- CMOSDICDDocument19 pagesCMOSDICDsrihari_56657801No ratings yet

- ECE 545-Digital System Design With VHDL: Digital Logic Refresher Part B - Sequential Logic Building BlocksDocument20 pagesECE 545-Digital System Design With VHDL: Digital Logic Refresher Part B - Sequential Logic Building BlocksAli Mohamed EltemsahNo ratings yet

- MT7620 RalinkDocument523 pagesMT7620 RalinkSuhendri SihombingNo ratings yet

- PM265 ch2Document47 pagesPM265 ch2M. AhmedNo ratings yet

- Large-Scale 3D Chips: Challenges and Solutions For Design Automation, Testing, and Trustworthy IntegrationDocument18 pagesLarge-Scale 3D Chips: Challenges and Solutions For Design Automation, Testing, and Trustworthy Integrationyunfan yNo ratings yet

- Control and Computer Chapter1 2013Document45 pagesControl and Computer Chapter1 2013wondi BETNo ratings yet

- Advanced VLSI Design & Testability Issues 2021Document379 pagesAdvanced VLSI Design & Testability Issues 2021Hyperalex1987No ratings yet

- Fpga Timeline & Applications: Fpgas Past, Present & FutureDocument39 pagesFpga Timeline & Applications: Fpgas Past, Present & FuturesmsarmadNo ratings yet

- Fundamentals of Quantitative Design and Analysis: A Quantitative Approach, Fifth EditionDocument54 pagesFundamentals of Quantitative Design and Analysis: A Quantitative Approach, Fifth Editionmwangilaureen493No ratings yet

- Lesson Plan For Demo TeachingDocument2 pagesLesson Plan For Demo TeachingFa MarieNo ratings yet

- Introduction To Embedded System DesignDocument22 pagesIntroduction To Embedded System DesignAnanthNo ratings yet

- Computer Organization and Microprocessor-P1Document26 pagesComputer Organization and Microprocessor-P1REEJU YADAV0% (1)

- 8 Data Address GeneratorDocument14 pages8 Data Address GeneratorAzizur RahmanNo ratings yet

- Unit-5 (Coa) NotesDocument33 pagesUnit-5 (Coa) NotesyashNo ratings yet

- W6 製程整合newDocument37 pagesW6 製程整合newcharlietu86No ratings yet

- Syncmos Technologies Inc. Sm8951A/8952ADocument17 pagesSyncmos Technologies Inc. Sm8951A/8952AAlberto MontillaNo ratings yet

- Rohini 69771659590Document7 pagesRohini 69771659590simman8371029No ratings yet

- ProcessorsDocument26 pagesProcessorsNavi KaurNo ratings yet

- A Presentation On Microcontroller 8051Document22 pagesA Presentation On Microcontroller 8051Praveen ShrivastavaNo ratings yet

- Instruction Description Clock Cycles Number of BytesDocument5 pagesInstruction Description Clock Cycles Number of BytesKashyap ShahNo ratings yet

- Microprocessors and Microcontrollers - Lecture Notes, Study Materials and Important Questions AnswersDocument5 pagesMicroprocessors and Microcontrollers - Lecture Notes, Study Materials and Important Questions AnswersBrainKart ComNo ratings yet

- Dual Core ProcessorDocument12 pagesDual Core ProcessorKishore Kick50% (4)

- SRAMDocument7 pagesSRAMRuqaiya KhanamNo ratings yet

- List 5000Document331 pagesList 5000Arturo ArmuellesNo ratings yet