Professional Documents

Culture Documents

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) For Quasi-Resonant Operation

Uploaded by

Paulo Roberto s freireOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) For Quasi-Resonant Operation

Uploaded by

Paulo Roberto s freireCopyright:

Available Formats

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

November 2006

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311

Green Mode Fairchild Power Switch (FPS™) for

Quasi-Resonant Operation - Low EMI and High Efficiency

Features Description

Optimized for Quasi-Resonant Converter (QRC) A Quasi-Resonant Converter (QRC) generally shows

Low EMI through Variable Frequency Control and lower EMI and higher power conversion efficiency than a

Inherent Frequency Modulation conventional hard-switched converter with a fixed

High-Efficiency through Minimum Voltage Switching switching frequency. The FSQ-series is an integrated

Narrow Frequency Variation Range over Wide Load Pulse-Width Modulation (PWM) controller and

and Input Voltage Variation SenseFET specifically designed for quasi-resonant

Advanced Burst-Mode Operation for Low Standby operation with minimal external components. The PWM

Power Consumption controller includes an integrated fixed-frequency

Pulse-by-Pulse Current Limit oscillator, Under-Voltage Lockout, Leading Edge

Various Protection Functions: Overload Protection Blanking (LEB), optimized gate driver, internal soft-start,

(OLP), Over-Voltage Protection (OVP), Abnormal temperature-compensated precise current sources for

Over-Current Protection (AOCP), Internal Thermal loop compensation, and self-protection circuitry.

Shutdown (TSD) Compared with discrete MOSFET and PWM controller

Under-Voltage Lockout (UVLO) with Hysteresis solution, the FSQ-series can reduce total cost,

Internal Start-up Circuit component count, size and weight; while simultaneously

Internal High-Voltage Sense FET (650V) increasing efficiency, productivity, and system reliability.

Built-in Soft-Start (15ms) This device provides a basic platform that is well suited

for cost-effective designs of quasi-resonant switching fly-

back converters.

Applications

Power Supply for DVP Player and DVD Recorder

Power supply for Set-Top Box

Adapter

Auxiliary Power Supply for PC, LCD TV, and PDP TV

Ordering Information

Maximum Output Power(1)

Product Operating Current RDS(ON) 230VAC±15%(2) 85-265VAC Replaces

PKG.

Number(5) Temp. Limit Max. Open Open Devices

Adapter(3) Adapter(3)

Frame(4) Frame(4)

FSDL321

FSQ311 8-DIP -25 to +85°C 0.6A 19Ω 7W 10W 6W 8W

FSDM311

FSQ0165RN 8-DIP -25 to +85°C 0.9A 10Ω 10W 15W 9W 13W FSDL0165RN

FSDM0265RN

FSQ0265RN 8-DIP -25 to +85°C 1.2A 6Ω 14W 20W 11W 16W

FSDM0265RNB

FSDM0365RN

FSQ0365RN 8-DIP -25 to +85°C 1.5A 4.5Ω 17.5W 25W 13W 19W

RSDM0365RNB

Notes:

1. The junction temperature can limit the maximum output power.

2. 230VAC or 100/115VAC with doubler. The maximum power with CCM operation.

3. Typical continuous power in a non-ventilated enclosed adapter measured at 50°C ambient temperature.

4. Maximum practical continuous power in an open frame design at 50°C ambient.

5. PB-free package per JEDEC J-STD-020B.

FPSTM is a trademark of Fairchild Semiconductor Corporation.

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Application Diagram

VO

AC

IN

Vstr

Drain

PWM

Sync GND

FB VCC

FSQ0365RN Rev.00

Figure 1. Typical Flyback Application

Internal Block Diagram

Sync Vstr VCC Drain

4 5 2 6 7 8

+

OSC

0.7V/0.2V

-

+

+

Vref

0.35/0.55

VCC good -

VCC Vref VBurst -

8V/12V

Idelay IFB

FB 3R PWM

S Q

3

Gate

Soft- LEB

R

Start R Q driver

200ns

AOCP

1

6V TSD S Q VOCP

VSD GND

(1.1V)

2.5μs time R Q

Sync delay

6V

Vovp

VCC good

FSQ0365RN Rev.00

Figure 2. Internal Block Diagram

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 2

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Pin Configuration

GND D

VCC D

8-DIP

FB D

Sync Vstr

FSQ0365RN Rev.00

Figure 3. Pin Configuration (Top View)

Pin Definitions

Pin # Name Description

1 GND Ground. This pin is the control ground and the SenseFET source.

Power Supply. This pin is the positive supply input. This pin provides internal

2 VCC

operating current for both start-up and steady-state operation.

Feedback. This pin is internally connected to the inverting input of the PWM

comparator. The collector of an opto-coupler is typically tied to this pin. For

3 FB stable operation, a capacitor should be placed between this pin and GND. If

the voltage of this pin reaches 6V, the overload protection triggers, which shuts

down the FPS.

Sync. This pin is internally connected to the sync-detect comparator for quasi-

4 Sync resonant switching. In normal quasi-resonant operation, the threshold of the

sync comparator is 0.7V/0.2V.

Start-up. This pin is connected directly to the high-voltage DC link. At start-up,

the internal high-voltage current source supplies internal bias and charges the

5 Vstr

external capacitor connected to the VCC pin. Once VCC reaches 12V, the in-

ternal current source is disabled.

6 Drain SenseFET drain. High-voltage power SenseFET drain connection.

7 Drain SenseFET drain. High-voltage power SenseFET drain connection.

8 Drain SenseFET drain. High-voltage power SenseFET drain connection.

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 3

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Absolute Maximum Ratings

The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The

device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables

are not guaranteed at the absolute maximum ratings. TA = 25°C, unless otherwise specified.

Symbol Parameter Min. Max. Unit

Vstr Vstr Pin Voltage 500 V

VDS Drain Pin Voltage 650 V

VCC Supply Voltage 20 V

VFB Feedback Voltage Range -0.3 9.0 V

VSync Sync Pin Voltage -0.3 9.0 V

FSQ0365RN 12

FSQ0265RN 8

IDM Drain Current Pulsed(6) A

FSQ0165RN 4

FSQ311 1.5

FSQ0365RN 230

FSQ0265RN 140

EAS Single Pulsed Avalanche Energy(7) mJ

FSQ0165RN 50

FSQ311 10

PD Total Power Dissipation 1.5 W

TJ Operating Junction Temperature Internally limited °C

TA Operating Ambient Temperature -25 85 °C

TSTG Storage Temperature -55 150 °C

(8)

ESD Capability, HBM Model CLASS1 C

(8)

ESD Capability, Machine Model CLASS B

Notes:

6. Repetitive rating: Pulse width limited by maximum junction temperature.

7. L=14mH, starting TJ=25°C.

8. Meets JEDEC Standards JESD 22-A114 and 22-A115.

Thermal Impedance(9)

Symbol Parameter Value Unit

8-DIP

θJA(10) Junction-to-Ambient Thermal Resistance 80

θJC(11) Junction-to-Case Thermal Resistance 20 °C/W

θJT(12) Junction-to-Top Thermal Resistance 35

Notes:

9. All items are tested with the standards JESD 51-2 and 51-10 (DIP).

10. Free-standing, with no heat-sink, under natural convection.

11. Infinite cooling condition - refer to the SEMI G30-88.

12. Measured on the PKG top surface.

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 4

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Electrical Characteristics

TA = 25°C unless otherwise specified.

Symbol Parameter Condition Min. Typ. Max. Unit

SENSEFET SECTION

BVDSS Drain Source Breakdown Voltage VCC = 0V, ID = 100µA 650 V

IDSS Zero-Gate-Voltage Drain Current VDS = 560V 100 µA

FSQ0365RN 3.5 4.5

Drain-Source on- FSQ0265RN 5.0 6.0

RDS(ON) TJ = 25°C, ID = 0.5A Ω

State Resistance FSQ0165RN 8.0 10.0

FSQ311 14.0 19.0

FSQ0365RN 315

FSQ0265RN 550

CSS Input Capacitance VGS = 0V, VDS = 25V, f = 1MHz pF

FSQ0165RN 250

FSQ311 162

FSQ0365RN 47

FSQ0265RN 38

COSS Output Capacitance VGS = 0V, VDS = 25V, f = 1MHz pF

FSQ0165RN 25

FSQ311 18

FSQ0365RN 9.0

Reverse Transfer FSQ0265RN 17.0

CRSS VGS = 0V, VDS = 25V, f = 1MHz pF

Capacitance FSQ0165RN 10.0

FSQ311 3.8

FSQ0365RN 11.2

FSQ0265RN 20.0

td(on) Turn-On Delay Time VDD = 350V, ID = 25mA ns

FSQ0165RN 12.0

FSQ311 9.5

FSQ0365RN 34

FSQ0265RN 15

tr Rise Time VDD = 350V, ID = 25mA ns

FSQ0165RN 4

FSQ311 19

FSQ0365RN 28.3

FSQ0265RN 55.0

td(off) Turn-Off Delay Time VDD = 350V, ID = 25mA ns

FSQ0165RN 30.0

FSQ311 33.0

FSQ0365RN 32

FSQ0265RN 25

tf Fall Time VDD = 350V, ID = 25mA ns

FSQ0165RN 10

FSQ311 42

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 5

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Electrical Characteristics (Continued)

TA = 25°C unless otherwise specified.

Symbol Parameter Condition Min. Typ. Max. Unit

CONTROL SECTION

tON.MAX Maximum ON Time TJ = 25°C 10.5 12.0 13.5 µsec

tB Blanking Time 13.2 15.0 16.8 µsec

tW Detection Time Window TJ = 25°C, Vsync = 0V 3.0 µsec

fS Initial Switching Frequency 50.5 55.6 61.7 kHz

ΔfS Switching Frequency Variation(13) -25°C < TJ < 85°C ±5 ±10 %

IFB Feedback Source Current VFB = 0V 700 900 1100 µA

DMIN Minimum Duty Cycle VFB = 0V 0 %

VSTART 11 12 13 V

UVLO Threshold Voltage

VSTOP After turn-on 7 8 9 V

tS/S Internal Soft-Start Time With free-running frequency 15 ms

BURST-MODE SECTION

VBURH TJ = 25°C, tPD = 200ns(14) 0.45 0.55 0.65 V

VBURL Burst-Mode Voltages 0.25 0.35 0.45 V

Hysteresis 200 mV

PROTECTION SECTION

FSQ0365RN TJ = 25°C, di/dt = 240mA/µsec 1.32 1.50 1.68

FSQ0265RN TJ = 25°C, di/dt = 200mA/µsec 1.06 1.20 1.34

ILIMIT Peak Current Limit A

FSQ0165RN TJ = 25°C, di/dt = 150mA/µsec 0.8 0.9 1.0

FSQ311 TJ = 25°C, di/dt = 100mA/µsec 0.53 0.60 0.67

VSD Shutdown Feedback Voltage VCC = 15V 5.5 6.0 6.5 V

IDELAY Shutdown Delay Current VFB = 5V 4 5 6 µA

tLEB Leading-Edge Blanking Time(13) 200 ns

VOVP Over-Voltage Protection VCC = 15V, VFB = 2V 5.5 6.0 6.5 V

tOVP Over-Voltage Protection Blanking Time 2 3 4 µsec

TSD Thermal Shutdown Temperature(13) 125 140 155 °C

SYNC SECTION

VSH 0.55 0.70 0.85 V

Sync Threshold Voltage

VSL 0.14 0.20 0.26 V

tsync Sync Delay Time(13)(15) 300 ns

TOTAL DEVICE SECTION

Operating Supply Current

IOP VCC = 15V 1 3 5 mA

(Control Part Only)

VCC = VSTART - 0.1V

ISTART Start Current 270 360 450 µA

(before VCC reaches VSTART)

ICH Start-up Charging Current VCC = 0V, VSTR = min. 40V 0.65 0.85 1.00 mA

VSTR Minimum VSTR Supply Voltage 26 V

Notes:

13. Though guaranteed, it is not tested in the mass production.

14. Propagation delay in the control IC.

15. Include gate turn-on time.

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 6

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Comparison Between FSDM0x65RNB and FSQ-Series

Function FSDM0x65RNB FSQ-Series FSQ-Series Advantages

Constant frequency Quasi-resonant Improved efficiency by valley switching

Operation method

PWM operation Reduced EMI noise

Valley switching & Reduce EMI noise by two ways

Frequency

EMI reduction inherent frequency

modulation

modulation

Improved standby power by valley switch-

ing also in burst-mode

Burst-mode operation Fixed burst peak Advanced burst-mode Because the current peak during burst

operation is dependent on VFB, it is easier

to solve audible noise

Improved reliability through precise abnor-

Protection AOCP

mal over-current protection

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 7

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Typical Performance Characteristics

These characteristic graphs are normalized at TA= 25°C.

1.2 1.2

1.0 1.0

Normalized

Normalized

0.8 0.8

0.6 0.6

0.4 0.4

0.2 0.2

0.0 0.0

-25 0 25 50 75 100 125 -25 0 25 50 75 100 125

Temperature [°C] Temperature [°C]

Figure 4. Operating Supply Current (IOP) vs. TA Figure 5. UVLO Start Threshold Voltage (VSTART)

vs. TA

1.2 1.2

1.0 1.0

Normalized

Normalized

0.8 0.8

0.6 0.6

0.4 0.4

0.2 0.2

0.0 0.0

-25 0 25 50 75 100 125 -25 0 25 50 75 100 125

Temperature [°C] Temperature [°C]

Figure 6. UVLO Stop Threshold Voltage (VSTOP) Figure 7. Start-up Charging Current (ICH) vs. TA

vs. TA

1.2 1.2

1.0 1.0

Normalized

Normalized

0.8 0.8

0.6 0.6

0.4 0.4

0.2 0.2

0.0 0.0

-25 0 25 50 75 100 125 -25 0 25 50 75 100 125

Temperature [°C] Temperature [°C]

Figure 8. Initial Switching Frequency (fS) vs. TA Figure 9. Maximum On Time (tON.MAX) vs. TA

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 8

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Typical Performance Characteristics (Continued)

These characteristic graphs are normalized at TA= 25°C.

1.2 1.2

1.0 1.0

Normalized

Normalized

0.8 0.8

0.6 0.6

0.4 0.4

0.2 0.2

0.0 0.0

-25 0 25 50 75 100 125 -25 0 25 50 75 100 125

Temperature [°C] Temperature [°C]

Figure 10. Blanking Time (tB) vs. TA Figure 11. Feedback Source Current (IFB) vs. TA

1.2 1.2

1.0 1.0

Normalized

Normalized

0.8 0.8

0.6 0.6

0.4 0.4

0.2 0.2

0.0 0.0

-25 0 25 50 75 100 125 -25 0 25 50 75 100 125

Temperature [°C] Temperature [°C]

Figure 12. Shutdown Delay Current (IDELAY) vs. TA Figure 13. Burst-Mode High Threshold Voltage

(Vburh) vs. TA

1.2 1.2

1.0 1.0

Normalized

Normalized

0.8 0.8

0.6 0.6

0.4 0.4

0.2 0.2

0.0 0.0

-25 0 25 50 75 100 125 -25 0 25 50 75 100 125

Temperature [°C] Temperature [°C]

Figure 14. Burst-Mode Low Threshold Voltage Figure 15. Peak Current Limit (ILIM) vs. TA

(Vburl) vs. TA

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 9

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Typical Performance Characteristics (Continued)

These characteristic graphs are normalized at TA= 25°C.

1.2 1.2

1.0 1.0

Normalized

Normalized

0.8 0.8

0.6 0.6

0.4 0.4

0.2 0.2

0.0 0.0

-25 0 25 50 75 100 125 -25 0 25 50 75 100 125

Temperature [°C] Temperature [°C]

Figure 16. Sync High Threshold Voltage (VSH) vs. TA Figure 17. Sync Low Threshold Voltage (VSL) vs. TA

1.2 1.2

1.0 1.0

Normalized

Normalized

0.8 0.8

0.6 0.6

0.4 0.4

0.2 0.2

0.0 0.0

-25 0 25 50 75 100 125 -25 0 25 50 75 100 125

Temperature [°C] Temperature [°C]

Figure 18. Shutdown Feedback Voltage (VSD) vs. TA Figure 19. Over-Voltage Protection (VOV) vs. TA

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 10

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Functional Description 2.2 Leading Edge Blanking (LEB): At the instant the

internal SenseFET is turned on, a high-current spike

1. Startup: At startup, an internal high-voltage current

usually occurs through the SenseFET, caused by

source supplies the internal bias and charges the

primary-side capacitance and secondary-side rectifier

external capacitor (Ca) connected to the VCC pin, as

reverse recovery. Excessive voltage across the Rsense

illustrated in Figure 20. When VCC reaches 12V, the FPS

resistor would lead to incorrect feedback operation in the

begins switching and the internal high-voltage current current mode PWM control. To counter this effect, the

source is disabled. The FPS continues its normal FPS employs a leading edge blanking (LEB) circuit. This

switching operation and the power is supplied from the circuit inhibits the PWM comparator for a short time

auxiliary transformer winding unless VCC goes below the (tLEB) after the SenseFET is turned on.

stop voltage of 8V.

VCC Vref

Idelay IFB

VDC VO VFB SenseFET

3 OSC

FOD817A

D1 D2

CB 3R

Ca + Gate

VFB* R driver

KA431 -

VCC Vstr

2 5 OLP Rsense

VSD

ICH FSQ0365RN Rev. 00

Vref Figure 21. Pulse-Width-Modulation (PWM) Circuit

8V/12V VCC good

3. Synchronization: The FSQ-series employs a quasi-

Internal

resonant switching technique to minimize the switching

Bias

FSQ0365RN Rev.00 noise and loss. The basic waveforms of the quasi-

resonant converter are shown in Figure 22. To minimize

Figure 20. Start-up Circuit the MOSFET's switching loss, the MOSFET should be

turned on when the drain voltage reaches its minimum

2. Feedback Control: FPS employs current mode value, as shown in Figure 22. The minimum drain

voltage is indirectly detected by monitoring the VCC

control, as shown in Figure 21. An opto-coupler (such as

the FOD817A) and shunt regulator (such as the KA431) winding voltage, as shown in Figure 22.

are typically used to implement the feedback network. Vds

Comparing the feedback voltage with the voltage across

the Rsense resistor makes it possible to control the VRO

switching duty cycle. When the reference pin voltage of

the shunt regulator exceeds the internal reference VRO

VDC

voltage of 2.5V, the opto-coupler LED current increases,

thus pulling down the feedback voltage and reducing the

duty cycle. This event typically happens when the input Vsync tF

voltage is increased or the output load is decreased. Vovp (6V)

2.1 Pulse-by-Pulse Current Limit: Because current

mode control is employed, the peak current through the 0.7V

SenseFET is limited by the inverting input of PWM 0.2V

comparator (VFB*), as shown in Figure 21. Assuming 300ns Delay

that the 0.9mA current source flows only through the MOSFET Gate

internal resistor (3R + R = 2.8k), the cathode voltage of

diode D2 is about 2.5V. Since D1 is blocked when the

feedback voltage (VFB) exceeds 2.5V, the maximum

ON ON

voltage of the cathode of D2 is clamped at this voltage,

FSQ0365RN Rev.00

thus clamping VFB*. Therefore, the peak value of the

current through the SenseFET is limited. Figure 22. Quasi-Resonant Switching Waveforms

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 11

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

4. Protection Circuits: The FSQ-series has several voltage. If the output consumes more than this maximum

self-protective functions, such as Overload Protection power, the output voltage (VO) decreases below the set

(OLP), Abnormal Over-Current protection (AOCP), Over- voltage. This reduces the current through the opto-

Voltage Protection (OVP), and Thermal Shutdown coupler LED, which also reduces the opto-coupler

(TSD). All the protections are implemented as auto- transistor current, thus increasing the feedback voltage

restart mode. Once the fault condition is detected, (VFB). If VFB exceeds 2.8V, D1 is blocked and the 5µA

switching is terminated and the SenseFET remains off. current source starts to charge CB slowly up to VCC. In

This causes VCC to fall. When VCC falls down to the

this condition, VFB continues increasing until it reaches

Under-Voltage Lockout (UVLO) stop voltage of 8V, the

6V, when the switching operation is terminated, as

protection is reset and start-up circuit charges VCC

shown in Figure 24. The delay time for shutdown is the

capacitor. When the VCC reaches the start voltage of time required to charge CB from 2.8V to 6V with 5µA. A

12V, the FSQ-series resumes normal operation. If the 20 ~ 50ms delay time is typical for most applications.

fault condition is not removed, the SenseFET remains off

and VCC drops to stop voltage again. In this manner, the VFB FSQ0365RN Rev.00

auto-restart can alternately enable and disable the Overload protection

switching of the power SenseFET until the fault condition

is eliminated. Because these protection circuits are fully 6.0V

integrated into the IC without external components, the

reliability is improved without increasing cost.

2.8V

Fault

occurs Fault t12= CFB*(6.0-2.8)/Idelay

VDS Power

removed

on

t1 t2 t

Figure 24. Overload Protection

4.2 Abnormal Over-Current Protection (AOCP): When

VCC the secondary rectifier diodes or the transformer pins are

shorted, a steep current with extremely high-di/dt can

flow through the SenseFET during the LEB time. Even

12V though the FSQ-series has OLP (Overload Protection), it

8V is not enough to protect the FSQ-series in that abnormal

case, since severe current stress is imposed on the

SenseFET until OLP triggers. The FSQ-series has an

t internal AOCP (Abnormal Over-Current Protection)

Normal Fault Normal

circuit as shown in Figure 25. When the gate turn-on

FSQ0365RN Rev. 00 operation situation operation signal is applied to the power SenseFET, the AOCP

block is enabled and monitors the current through the

Figure 23. Auto Restart Protection Waveforms sensing resistor. The voltage across the resistor is

compared with a preset AOCP level. If the sensing

resistor voltage is greater than the AOCP level, the set

4.1 Overload Protection (OLP): Overload is defined as signal is applied to the latch, resulting in the shutdown of

the load current exceeding its normal level due to an the SMPS.

unexpected abnormal event. In this situation, the

protection circuit should trigger to protect the SMPS.

However, even when the SMPS is in the normal 3R

OSC

operation, the overload protection circuit can be PWM S Q

triggered during the load transition. To avoid this LEB

R Q

Gate

driver

undesired operation, the overload protection circuit is

200ns

designed to trigger only after a specified time to

R

determine whether it is a transient situation or a true

overload situation. Because of the pulse-by-pulse +

Rsense

1

current limit capability, the maximum peak current AOCP

-

GND

through the Sense FET is limited, and therefore the FSQ0365RN Rev.00

VOCP

maximum input power is restricted with a given input

Figure 25. Abnormal Over-Current Protection

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 12

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

4.3 Over-Voltage Protection (OVP): If the secondary

side feedback circuit malfunctions or a solder defect

VO

causes an opening in the feedback path, the current

through the opto-coupler transistor becomes almost VOset

zero. Then, VFB climbs up in a similar manner to the

overload situation, forcing the preset maximum current

to be supplied to the SMPS until the overload protection VFB

triggers. Because more energy than required is provided

to the output, the output voltage may exceed the rated

0.55V

voltage before the overload protection triggers, resulting 0.35V

in the breakdown of the devices in the secondary side.

To prevent this situation, an OVP circuit is employed. In IDS

general, the peak voltage of the sync signal is

proportional to the output voltage and the FSQ-series

uses a sync signal instead of directly monitoring the

output voltage. If the sync signal exceeds 6V, an OVP is

triggered, shutting down the SMPS. To avoid undesired VDS

triggering of OVP during normal operation, the peak

voltage of the sync signal should be designed below 6V.

4.4 Thermal Shutdown (TSD): The SenseFET and the time

control IC are built in one package. This makes it easy Switching

disabled

Switching

disabled

t2 t3 t4

for the control IC to detect the abnormal over FSQ0365RN Rev.00 t1

temperature of the SenseFET. If the temperature

exceeds ~150°C, the thermal shutdown triggers. Figure 26. Waveforms of Burst Operation

5. Soft-Start: The FPS has an internal soft-start circuit 7. Switching Frequency Limit: To minimize switching

that increases PWM comparator inverting input voltage loss and EMI (Electromagnetic Interference), the

with the SenseFET current slowly after it starts up. The MOSFET turns on when the drain voltage reaches its

typical soft-start time is 15ms, The pulse width to the minimum value in quasi-resonant operation. However,

power switching device is progressively increased to this causes switching frequency to increases at light load

establish the correct working conditions for transformers, conditions. As the load decreases, the peak drain current

inductors, and capacitors. The voltage on the output diminishes and the switching frequency increases. This

capacitors is progressively increased with the intention of results in severe switching losses at light-load condition,

smoothly establishing the required output voltage. This as well as intermittent switching and audible noise.

mode helps prevent transformer saturation and reduces Because of these problems, the quasi-resonant

stress on the secondary diode during startup. converter topology has limitations in a wide range of

applications.

To overcome this problem, FSQ-series employs a

6. Burst Operation: To minimize power dissipation in frequency-limit function, as shown in Figures 27 and 28.

standby mode, the FPS enters burst-mode operation. As Once the SenseFET is turned on, the next turn-on is

the load decreases, the feedback voltage decreases. As prohibited during the blanking time (tB). After the

shown in Figure 26, the device automatically enters

blanking time, the controller finds the valley within the

burst-mode when the feedback voltage drops below

detection time window (tW) and turns on the MOSFET, as

VBURL (350mV). At this point, switching stops and the

shown in Figures 27 and 28 (Cases A, B, and C). If no

output voltages start to drop at a rate dependent on

valley is found during tW, the internal SenseFET is forced

standby current load. This causes the feedback voltage

to rise. Once it passes VBURH (550mV), switching to turn on at the end of tW (Case D). Therefore, our

resumes. The feedback voltage then falls and the devices have a minimum switching frequency of 55kHz

process repeats. Burst-mode operation alternately and a maximum switching frequency of 67kHz, as shown

enables and disables switching of the power SenseFET, in Figure 28.

thereby reducing switching loss in standby mode.

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 13

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

tsmax=18μs When the resonant period is 2μs

67kHz

IDS IDS A B C Constant

frequency

59kHz

55kHz

A D

tB=15μs

Burst

mode

ts

IDS IDS

B PO

FSQ0365RN Rev. 00

tB=15μs

Figure 28. Switching Frequency Range

ts

IDS IDS

tB=15μs

ts

IDS IDS

tB=15μs

D

tW=3μs

tsmax=18μs FSQ0365RN Rev. 00

Figure 27. QRC Operation with Limited Frequency

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 14

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Application Information

Input Voltage Output Voltage

Application FPS Device Rated Output Power

Range (Max. Current)

5.1V (1.0A)

DVD Player 3.4V (1.0A)

FSQ0365RN 85-265VAC 19W

Power Supply 12V (0.4A)

16V (0.3A)

Features

High efficiency ( >77% at universal input)

Low standby mode power consumption (<1W at 230VAC input and 0.5W load)

Reduce EMI noise through Quasi-Resonant Operation

Enhanced system reliability through various protection functions

Internal soft-start (15ms)

Key Design Notes

The delay time for overload protection is designed to be about 30ms with C107 of 47nF. If faster/slower triggering of

OLP is required, C107 can be changed to a smaller/larger value (eg. 100nF for 60ms).

The input voltage of Vsync must be higher than -0.3V. By proper voltage sharing by R106 & R107 resistors, the input

voltage can be adjusted.

The SMD-type 100nF capacitor must be placed as close as possible to VCC pin to avoid malfunction by abrupt pul-

sating noises and to improved surge immunity.

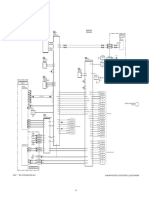

1. Schematic

C209

47pF

T101

L201

EER2828

16V, 0.3A

11

RT101 1 D201 C202

C201

5D-9 UF4003 470μF

470μF

R105 C104 C210 35V 35V

R102 2

100kΩ 56kΩ 10nF 47pF

630V L202

C103 D101

R108 1N 4007 12V, 0.4A

33μF

62Ω 3

400V 10 D202 C203 C204

2 UF4003 470μF 470μF

IC101 35V 35V

FSQ0365RN 12

BD101 5 8

1 3 Vstr Drain

Bridge 7

Drain L203

Diode 4 6

Drain C106 C107

Sync 6 5.1V, 1A

100nF 22μF R103

3 Vcc 2 SMD 50V 5Ω C205 C206

4 FB D203

GND 4 1000μF 1000μF

C102 C105 D102 SB360

1 10V 10V

100nF,275VAC 47nF 1N 4004 R104

50V 12kΩ 5 L204

9

ZD101 3.4V, 1A

1N4746A D204 C207 C208

C110

6.2kΩ 6.2kΩ

1000μF

R106 R107

33pF SB360 1000μF

1N4148

50V 10V 10V

D103

LF101

40mH

8

C302

3.3nF R201

C101 510Ω

100nF R203

275VAC 6.2kΩ

R202

R204 C209

1kΩ

20kΩ 100nF

IC202

TNR FOD817A

10D471K F101

FUSE IC201 R205

KA431 6kΩ

AC IN FSQ0365RN Rev:00

Figure 29. Demo Circuit

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 15

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

2. Transformer

EER2828

12

1 Np/2

Np/2 11

N16V N16V

Np/2 2 10

N12V N12V

3

9 N Na

3.4V

Na 4 8 N5.1V

6mm 3mm

5 N3.4V

7

Np/2

6 N

5.1V

FSQ0365RN Rev: 00

Figure 30. Transformer Schematic Diagram

3. Winding Specification

No Pin (s→f) Wire Turns Winding Method

Np/2 3→2 0.25φ ×1 50 Center Solenoid Winding

Insulation: Polyester Tape t = 0.050mm, 2 Layers

N3.4V 9→8 0.33φ × 2 4 Center Solenoid Winding

Insulation: Polyester Tape t = 0.050mm, 2 Layers

N5V 6→9 0.33φ × 1 2 Center Solenoid Winding

Insulation: Polyester Tape t = 0.050mm, 2 Layers

Na 4→5 0.25φ × 1 16 Center Solenoid Winding

Insulation: Polyester Tape t = 0.050mm, 2 Layers

N12V 10 → 12 0.33φ × 3 14 Center Solenoid Winding

Insulation: Polyester Tape t = 0.050mm, 3 Layers

N16V 11 → 12 0.33φ × 3 18 Center Solenoid Winding

Insulation: Polyester Tape t = 0.050mm, 2 Layers

Np/2 2→1 0.25φ × 1 50 Center Solenoid Winding

Insulation: Polyester Tape t = 0.050mm, 2 Layers

4. Electrical Characteristics

Pin Specification Remarks

Inductance 1-3 1.4mH ± 10% 100kHz, 1V

Leakage 1-3 25µH Max. Short all other pins

5. Core & Bobbin

Core: EER2828 (Ae=86.66mm2)

Bobbin: EER2828

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 16

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

6. Demo Board Part List

Part Value Note Part Value Note

Resistor Inductor

R102 56kΩ 1W L201 10µH

R103 5Ω 1/2W L202 10µH

R104 12kΩ 1/4W L203 4.9µH

R105 100kΩ 1/4W L204 4.9µH

R106 6.2kΩ 1/4W Diode

R107 6.2kΩ 1/4W D101 IN4007

R108 62Ω 1W D102 IN4004

R201 510Ω 1/4W ZD101 1N4746A

R202 1kΩ 1/4W D103 1N4148

R203 6.2kΩ 1/4W D201 UF4003

R204 20kΩ 1/4W D202 UF4003

R205 6kΩ 1/4W D203 SB360

Capacitor D204 SB360

C101 100nF/275VAC Box Capacitor

C102 100nF/275VAC Box Capacitor IC

C103 33µF/400V Electrolytic Capacitor IC101 FSQ0365RN FPS™

C104 10nF/630V Film Capacitor IC201 KA431 (TL431) Voltage reference

C105 47nF/50V Mono Capacitor IC202 FOD817A Opto-coupler

C106 100nF/50V SMD (1206) Fuse

C107 22µF/50V Electrolytic Capacitor Fuse 2A/250V

C110 33pF/50V Ceramic Capacitor NTC

C201 470µF/35V Electrolytic Capacitor RT101 5D-9

C202 470µF/35V Electrolytic Capacitor Bridge Diode

C203 470µF/35V Electrolytic Capacitor BD101 2KBP06M2N257 Bridge Diode

C204 470µF/35V Electrolytic Capacitor Line Filter

C205 1000µF/10V Electrolytic Capacitor LF101 40mH

C206 1000µF/10V Electrolytic Capacitor Transformer

C207 1000µF/10V Electrolytic Capacitor T101

C208 1000µF/10V Electrolytic Capacitor Varistor

C209 100nF /50V Ceramic Capacitor TNR 10D471K

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 17

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

Package Dimensions

8-DIP

Dimensions are in millimeters unless otherwise noted.

)

6.40 ±0.20

0.031

0.79

0.252 ±0.008

1.524 ±0.10

0.060 ±0.004

0.018 ±0.004

0.46 ±0.10

(

#1 #8

0.362 ±0.008

MAX

9.20 ±0.20

0.378

9.60

#4 #5

0.100

2.54

5.08 3.30 ±0.30

MAX 0.130 ±0.012

0.200

7.62

0.300 3.40 ±0.20 0.33

0.134 ±0.008 0.013 MIN

+0.10

0.25 –0.05

+0.004

0.010 –0.002

0~15° September 1999, Rev B

8dip_dim.pdf

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 18

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) for QRC

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an

exhaustive list of all such trademarks.

ACEx¥ GlobalOptoisolator¥ OCXPro¥ PSerDes¥ TinyBuck¥

® ® ®

ActiveArray¥ GTO¥ OPTOLOGIC SILENT SWITCHER TinyLogic

Bottomless¥ HiSeC¥ OPTOPLANAR¥ SMART START¥ TINYOPTO¥

2

Build it Now¥ I C¥ PACMAN¥ SPM¥ TinyPower¥

CoolFET¥ i-Lo¥ POP¥ Stealth¥ TinyPWM¥

CROSSVOLT¥ ImpliedDisconnect¥ Power247¥ SuperFET¥ TruTranslation¥

DOME¥ IntelliMAX¥ PowerEdge¥ SuperSOT¥-3 UHC¥

®

EcoSPARK¥ ISOPLANAR¥ PowerSaver¥ SuperSOT¥-6 UltraFET

2 ®

E CMOS¥ LittleFET¥ PowerTrench SuperSOT¥-8 UniFET¥

®

EnSigna¥ MICROCOUPLER¥ QFET SyncFET¥ VCX¥

FACT¥ MicroFET¥ QS¥ TCM¥ Wire¥

FACT Quiet Series¥ MicroPak¥ QT Optoelectronics¥ TinyBoost¥

®

FAST MICROWIRE¥ Quiet Series¥

FASTr¥ MSX¥ RapidConfigure¥ Across the board. Around the world.¥

FPS¥ MSXPro¥ RapidConnect¥ Programmable Active Droop¥

®

FRFET¥ OCX¥ ScalarPump¥ The Power Franchise

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS

HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE

APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER

ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S

WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR

SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support,

which, (a) are intended for surgical implant into the body or device, or system whose failure to perform can be

(b) support or sustain life, and (c) whose failure to perform reasonably expected to cause the failure of the life

when properly used in accordance with instructions for use support device or system, or to affect its safety or

provided in the labeling, can be reasonably expected to effectiveness.

result in a significant injury of the user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or In This datasheet contains the design specifications for product

Design development. Specifications may change in any manner without

notice.

Preliminary First Production This datasheet contains preliminary data; supplementary data will

be published at a later date. Fairchild Semiconductor reserves the

right to make changes at any time without notice to improve design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild

Semiconductor reserves the right to make changes at any time

without notice to improve design.

Obsolete Not In Production This datasheet contains specifications on a product that has been

discontinued by Fairchild Semiconductor. The datasheet is printed

for reference information only.

Rev. I20

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Rev. 1.0.0 19

You might also like

- FSQ0165R PDFDocument24 pagesFSQ0165R PDFLeonel AntonioNo ratings yet

- FSQ0565R, FSQ0765R Green-Mode Fairchild Power Switch (FPS™) For Quasi-Resonant OperationDocument22 pagesFSQ0565R, FSQ0765R Green-Mode Fairchild Power Switch (FPS™) For Quasi-Resonant OperationSilvio SchwanckNo ratings yet

- FSQ0365, FSQ0265, FSQ0165, FSQ321 Green Mode Fairchild Power Switch (FPS™)Document21 pagesFSQ0365, FSQ0265, FSQ0165, FSQ321 Green Mode Fairchild Power Switch (FPS™)Nicodemo DatiNo ratings yet

- FSQ510, FSQ510H - Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant ConverterDocument15 pagesFSQ510, FSQ510H - Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant ConverterEletronica TecnotronicaNo ratings yet

- FSQ100 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDocument13 pagesFSQ100 Green Mode Fairchild Power Switch (FPS™) : Features Descriptionايهاب فوزيNo ratings yet

- FS FSQ510Document15 pagesFS FSQ510Slobodan Boba JovanovićNo ratings yet

- 3-V To 6-V Input, 3-A Output Synchronous-Buck PWM Switcher With Integrated Fets (Swift™)Document21 pages3-V To 6-V Input, 3-A Output Synchronous-Buck PWM Switcher With Integrated Fets (Swift™)Adriana VNo ratings yet

- FSQ321 D 1810228Document23 pagesFSQ321 D 1810228Donchon chungNo ratings yet

- Datasheet PDFDocument45 pagesDatasheet PDFSonidos SotoNo ratings yet

- FSQ510 85947Document15 pagesFSQ510 85947علی امامیNo ratings yet

- Data SheetDocument20 pagesData Sheetcavalo doidoNo ratings yet

- FSQ0170RNA, FSQ0270RNA Green Mode Fairchild Power Switch (FPS™)Document17 pagesFSQ0170RNA, FSQ0270RNA Green Mode Fairchild Power Switch (FPS™)mircea mozoleaNo ratings yet

- Circuito Integrado Q0465RSDocument24 pagesCircuito Integrado Q0465RSmarcosNo ratings yet

- FSL206MRDocument16 pagesFSL206MRnightreader99No ratings yet

- FSCQ-Series FSCQ0565RT/FSCQ0765RT/FSCQ0965RT/FSCQ1265RT/ FSCQ1465RT/FSCQ1565RT/FSCQ1565RP Green Mode Fairchild Power Switch (FPS™)Document45 pagesFSCQ-Series FSCQ0565RT/FSCQ0765RT/FSCQ0965RT/FSCQ1265RT/ FSCQ1465RT/FSCQ1565RT/FSCQ1565RP Green Mode Fairchild Power Switch (FPS™)alamgir80100% (2)

- Fsdm0465re Fsdm0565re Fsdm07652reDocument20 pagesFsdm0465re Fsdm0565re Fsdm07652rejesus cautivoNo ratings yet

- Datasheet FSL117MRINDocument15 pagesDatasheet FSL117MRINeurofutabNo ratings yet

- FSQ311Document24 pagesFSQ311zektorNo ratings yet

- FSQ0370RNADocument18 pagesFSQ0370RNAvukica ivicNo ratings yet

- Green Mode Power Switch For Valley Switching Converter - Low EMI and High Efficiency FSQ0365, FSQ0265, FSQ0165, FSQ321Document22 pagesGreen Mode Power Switch For Valley Switching Converter - Low EMI and High Efficiency FSQ0365, FSQ0265, FSQ0165, FSQ321Mekkati MekkatiNo ratings yet

- Data SheetDocument44 pagesData SheetKendje MatsumotoNo ratings yet

- Str-A6251 Str-A6252 PDFDocument7 pagesStr-A6251 Str-A6252 PDFrafalero1No ratings yet

- FSDL0165RN: Green Mode Fairchild Power Switch (FPS)Document20 pagesFSDL0165RN: Green Mode Fairchild Power Switch (FPS)Kakajan KhormaliNo ratings yet

- FSGM300N Fairchild SemiconductorDocument16 pagesFSGM300N Fairchild SemiconductorValdelio JuniorNo ratings yet

- IC-ON-LINE - CN dm0365r 44840Document20 pagesIC-ON-LINE - CN dm0365r 44840MoscandoNo ratings yet

- FSDH321, FSDL321: Green Mode Fairchild Power Switch (FPS)Document20 pagesFSDH321, FSDL321: Green Mode Fairchild Power Switch (FPS)Ricardo WerlangNo ratings yet

- DM311Document16 pagesDM311Hernan Ortiz EnamoradoNo ratings yet

- FSL106HR Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDocument14 pagesFSL106HR Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDarknezzNo ratings yet

- FSL106HRDocument13 pagesFSL106HRGerson SoaresNo ratings yet

- Str-A6251M: Universal-Input/15 W 67 KHZ Flyback Switching RegulatorDocument7 pagesStr-A6251M: Universal-Input/15 W 67 KHZ Flyback Switching RegulatorAlexisNo ratings yet

- Tps 54140Document52 pagesTps 54140niceautomation8831No ratings yet

- DM0565Document21 pagesDM0565Tammy WashingtonNo ratings yet

- Al8860 1019719Document18 pagesAl8860 1019719hansNo ratings yet

- FSGM0465R Green-Mode Fairchild Power Switch (FPS™) : Features DescriptionDocument17 pagesFSGM0465R Green-Mode Fairchild Power Switch (FPS™) : Features DescriptionMartin Elias OrtizNo ratings yet

- HIP6302CBDocument18 pagesHIP6302CBrjbordaNo ratings yet

- Fsl136 - Flyback DC DCDocument13 pagesFsl136 - Flyback DC DCJasonLCNo ratings yet

- F DatasheetDocument16 pagesF DatasheetTerelia Kinan GallenNo ratings yet

- FSCQ-Series FSCQ0565RT/FSCQ0765RT/FSCQ0965RT/FSCQ1265RT/ FSCQ1465RT/FSCQ1565RT/FSCQ1565RP Green Mode Fairchild Power Switch (FPS™)Document45 pagesFSCQ-Series FSCQ0565RT/FSCQ0765RT/FSCQ0965RT/FSCQ1265RT/ FSCQ1465RT/FSCQ1565RT/FSCQ1565RP Green Mode Fairchild Power Switch (FPS™)AntonioNobregaNo ratings yet

- FS7M0680, FS7M0880: Fairchild Power Switch (FPS)Document18 pagesFS7M0680, FS7M0880: Fairchild Power Switch (FPS)Candelaria CortesNo ratings yet

- Arduino Nano 3 User ManualDocument20 pagesArduino Nano 3 User ManualDj PopNo ratings yet

- NB676 DatasheetDocument19 pagesNB676 DatasheetRudy BudimanNo ratings yet

- DM0265Document19 pagesDM0265liberthNo ratings yet

- FSFR-Series - : Fairchild Power Switch (FPS™) For Half-Bridge Resonant ConvertersDocument17 pagesFSFR-Series - : Fairchild Power Switch (FPS™) For Half-Bridge Resonant ConvertersAgustin PellegrinettiNo ratings yet

- CQ1565Document24 pagesCQ1565liberthNo ratings yet

- Silergy Corp SY8213FCC - C178246Document9 pagesSilergy Corp SY8213FCC - C178246Thai LamNo ratings yet

- DM0265R ONSemiconductorDocument16 pagesDM0265R ONSemiconductorAdriano HenriqueNo ratings yet

- High-Speed Step-Down Controller: Features General DescriptionDocument1 pageHigh-Speed Step-Down Controller: Features General Descriptionedi purwantoNo ratings yet

- GM0465RDocument18 pagesGM0465RautreraNo ratings yet

- Fsl117mrin 1010027Document18 pagesFsl117mrin 1010027ferreirabarbo93065gmail.com BarboNo ratings yet

- Datasheet FSDL0365RN y SG6858Document22 pagesDatasheet FSDL0365RN y SG6858Oscar Hugo ChateNo ratings yet

- FSQ0565R, FSQ0765R Green-Mode Fairchild Power Switch (FPS™) For Quasi-Resonant OperationDocument0 pagesFSQ0565R, FSQ0765R Green-Mode Fairchild Power Switch (FPS™) For Quasi-Resonant Operationsontuyet82No ratings yet

- Datasheet DMO565RDocument21 pagesDatasheet DMO565RSteve Bravo83% (6)

- 3PD5651EDocument14 pages3PD5651Easousa534No ratings yet

- 1565 RTDocument24 pages1565 RTJose Samuel Robelto RNo ratings yet

- FSFR1800Document17 pagesFSFR1800sontuyet82No ratings yet

- CQ0765RT DatasheetDocument24 pagesCQ0765RT DatasheetSergio Daniel BarretoNo ratings yet

- 3-A High Voltage Boost Converter With Soft-Start and Programmable Switching FrequencyDocument24 pages3-A High Voltage Boost Converter With Soft-Start and Programmable Switching FrequencyVinayak KulkarniNo ratings yet

- Max 5069Document19 pagesMax 5069h1169104No ratings yet

- DM311 FSDM311 Green Mode Power Switch (FPSTM) PDFDocument19 pagesDM311 FSDM311 Green Mode Power Switch (FPSTM) PDFKrista TranNo ratings yet

- Green-Mode PWM Controller With Integrated Protections: General Description FeaturesDocument18 pagesGreen-Mode PWM Controller With Integrated Protections: General Description FeaturesRUSLANNo ratings yet

- 3.3-V/5-V Input, 6-A, D-Cap+ Mode Synchronous Step-Down Integrated Fets Converter With 2-Bit VidDocument35 pages3.3-V/5-V Input, 6-A, D-Cap+ Mode Synchronous Step-Down Integrated Fets Converter With 2-Bit VidPaulo Roberto s freireNo ratings yet

- 12204-1 TopDocument1 page12204-1 TopPaulo Roberto s freireNo ratings yet

- Semiconductor Technical Data SheetDocument8 pagesSemiconductor Technical Data SheetPaulo Roberto s freireNo ratings yet

- 12204-1 BottomDocument1 page12204-1 BottomPaulo Roberto s freireNo ratings yet

- Cce TV 2918uspDocument1 pageCce TV 2918uspjailton1958No ratings yet

- Power Supply LED Driver 715G7734. TV Led Philips (TPN16.2E LA)Document4 pagesPower Supply LED Driver 715G7734. TV Led Philips (TPN16.2E LA)Ernesto Lambretch100% (7)

- Green-Mode PWM Controller Reduces Audio NoiseDocument18 pagesGreen-Mode PWM Controller Reduces Audio NoisePaulo Roberto s freireNo ratings yet

- Power Board With PF6003ASDocument1 pagePower Board With PF6003ASAleluiz LuizNo ratings yet

- Multi-Channel Power Supply IC For Car Audio Systems: DatasheetDocument44 pagesMulti-Channel Power Supply IC For Car Audio Systems: DatasheetPaulo Roberto s freireNo ratings yet

- 12 Block Diagram: 12.1. Servo & System ControlDocument18 pages12 Block Diagram: 12.1. Servo & System ControlPaulo Roberto s freireNo ratings yet

- 40 Ipl32l Pwg1xg+China+PsuDocument3 pages40 Ipl32l Pwg1xg+China+PsuPaulo Roberto s freireNo ratings yet

- High and Low Side Driver: IR25607SPBFDocument19 pagesHigh and Low Side Driver: IR25607SPBFPaulo Roberto s freireNo ratings yet

- FSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) For Quasi-Resonant OperationDocument19 pagesFSQ0365RN, FSQ0265RN, FSQ0165RN, FSQ311 Green Mode Fairchild Power Switch (FPS™) For Quasi-Resonant OperationPaulo Roberto s freireNo ratings yet

- Advanced 600V N-Channel MOSFET for Switching Regulator ApplicationsDocument8 pagesAdvanced 600V N-Channel MOSFET for Switching Regulator ApplicationsPaulo Roberto s freireNo ratings yet

- Digital Controller: E5AK/E5EKDocument37 pagesDigital Controller: E5AK/E5EKPaulo Roberto s freireNo ratings yet

- Esquema Elétrico C14CU51Document40 pagesEsquema Elétrico C14CU51Alessandra Rosario60% (5)

- For New Designs: AOZ1033AIDocument15 pagesFor New Designs: AOZ1033AIPaulo Roberto s freireNo ratings yet

- FWP2000/ Network Music PlayerDocument44 pagesFWP2000/ Network Music PlayerGilberto Grandini BitencourtNo ratings yet

- FSCQ1565RT: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterDocument25 pagesFSCQ1565RT: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterPaulo Roberto s freireNo ratings yet

- For New Designs: AOZ1033AIDocument15 pagesFor New Designs: AOZ1033AIPaulo Roberto s freireNo ratings yet

- Isc N-Channel MOSFET Transistor IRFR7540, IIRFR7540: INCHANGE SemiconductorDocument2 pagesIsc N-Channel MOSFET Transistor IRFR7540, IIRFR7540: INCHANGE SemiconductorkalanghoNo ratings yet

- SR302 - SR306: Not Recommended For New Designs, Use Sb3X0 SeriesDocument2 pagesSR302 - SR306: Not Recommended For New Designs, Use Sb3X0 SeriesPaulo Roberto s freireNo ratings yet

- High and Low Side Driver: IR25607SPBFDocument19 pagesHigh and Low Side Driver: IR25607SPBFPaulo Roberto s freireNo ratings yet

- FWP2000/ Network Music PlayerDocument44 pagesFWP2000/ Network Music PlayerGilberto Grandini BitencourtNo ratings yet

- Isc N-Channel MOSFET Transistor IRFR7540, IIRFR7540: INCHANGE SemiconductorDocument2 pagesIsc N-Channel MOSFET Transistor IRFR7540, IIRFR7540: INCHANGE SemiconductorkalanghoNo ratings yet

- 5W 2-Channel AF Power Amplifier With DC Volume ControlDocument9 pages5W 2-Channel AF Power Amplifier With DC Volume ControlMiloud ChouguiNo ratings yet

- 111Db 192Khz 24-Bit 2ChDocument26 pages111Db 192Khz 24-Bit 2ChPaulo Roberto s freireNo ratings yet

- 2 SC 2625Document3 pages2 SC 2625Paulo Roberto s freireNo ratings yet

- GPM32F011XBV10 Sensored FOC Control of PMSM Using GPM32F011xB User (English Version)Document39 pagesGPM32F011XBV10 Sensored FOC Control of PMSM Using GPM32F011xB User (English Version)ISHAK CHERGUINo ratings yet

- Ibm 2000w Power Supply OperationalDocument32 pagesIbm 2000w Power Supply OperationalsherlockmamenNo ratings yet

- 13 - L-7 (DK) (Pe) ( (Ee) Nptel)Document1 page13 - L-7 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- Indiabix IIDocument60 pagesIndiabix IISylvina Anne Conde AsiñoNo ratings yet

- Manual Pic 18F2550Document430 pagesManual Pic 18F2550Pancho NuncioNo ratings yet

- Features General Description: High Performance Current Mode PWM ControllerDocument8 pagesFeatures General Description: High Performance Current Mode PWM ControllerAouadi AbdellazizNo ratings yet

- Closed Loop Flyback ConverterDocument18 pagesClosed Loop Flyback ConverterIlavarasan SanNo ratings yet

- 555 Timer Guide: IC Pinout & Working PrincipleDocument1 page555 Timer Guide: IC Pinout & Working PrinciplePraveen KumarNo ratings yet

- Voltage Regulator DatasheetDocument6 pagesVoltage Regulator DatasheetSteveNo ratings yet

- B.E. Control Systems Syllabus (PSG Tech)Document48 pagesB.E. Control Systems Syllabus (PSG Tech)Nivas Kumar SureshNo ratings yet

- Mx341 Automatic Voltage Regulator (Avr) : Specification, Installation and AdjustmentsDocument4 pagesMx341 Automatic Voltage Regulator (Avr) : Specification, Installation and AdjustmentsNamiJen LobatoNo ratings yet

- Driver IC LG4573Document141 pagesDriver IC LG4573nio58No ratings yet

- Eup3482aeup3482a PDFDocument11 pagesEup3482aeup3482a PDFfabloNo ratings yet

- Philips Analog Cross ReferenceDocument2 pagesPhilips Analog Cross Referencetbscri0% (1)

- Max 17528Document41 pagesMax 17528William Medina GómezNo ratings yet

- Design of A New 3 Bit Flash Analog To DiDocument11 pagesDesign of A New 3 Bit Flash Analog To DisayemeeceNo ratings yet

- An Automatic Circuit Design Framework For Level Shifter CircuitsDocument13 pagesAn Automatic Circuit Design Framework For Level Shifter CircuitsVani YamaniNo ratings yet

- LTC 15389 FDocument32 pagesLTC 15389 FEdson HenriqueNo ratings yet

- Flasher IC With 18-m Shunt U6043B: FeaturesDocument9 pagesFlasher IC With 18-m Shunt U6043B: FeaturesSusana MendosaNo ratings yet

- Gate Ec: Q. 1-30 Carry One Mark EachDocument44 pagesGate Ec: Q. 1-30 Carry One Mark EachSuraj KumarNo ratings yet

- Federal Pa300 Siren SMDocument20 pagesFederal Pa300 Siren SMfernandoalejandroNo ratings yet

- DIGITAL LOGIC DESIGN PROJECT Password enDocument11 pagesDIGITAL LOGIC DESIGN PROJECT Password enZainAfridiNo ratings yet

- Quick Setup Guide for Weight Indicating InstrumentDocument32 pagesQuick Setup Guide for Weight Indicating InstrumentCeleynes RTNo ratings yet

- Project ReportDocument10 pagesProject ReportchaitanyaNo ratings yet

- Moog ServoelectronicsDocument27 pagesMoog ServoelectronicsMaxNo ratings yet

- Educational ElectronicsDocument94 pagesEducational Electronicsgilmeanualexmihai100% (3)

- Motorola SeminarsandApplicationBooksCMOSDataManualVolume2 SpecialFunctionsOCRDocument423 pagesMotorola SeminarsandApplicationBooksCMOSDataManualVolume2 SpecialFunctionsOCRFLAVIO100% (3)

- Applied Electronics 05 Ec 64xxDocument60 pagesApplied Electronics 05 Ec 64xxwhiteelephant93No ratings yet

- Square Wave Generator Using Op Amp IC 741 - ElectronicsDocument5 pagesSquare Wave Generator Using Op Amp IC 741 - ElectronicsurasousaNo ratings yet

- CO2037 - L03b - OpAmpDocument36 pagesCO2037 - L03b - OpAmpHào NguyễnNo ratings yet