Professional Documents

Culture Documents

8-Pin PFC and PWM Controller Combo: Features General Description

8-Pin PFC and PWM Controller Combo: Features General Description

Uploaded by

AndersonOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

8-Pin PFC and PWM Controller Combo: Features General Description

8-Pin PFC and PWM Controller Combo: Features General Description

Uploaded by

AndersonCopyright:

Available Formats

www.fairchildsemi.

com

FAN4803

8-Pin PFC and PWM Controller Combo

Features General Description

• Internally synchronized PFC and PWM in one 8-pin IC The FAN4803 is a space-saving controller for power factor

• Proprietary one-pin voltage error amplifier with advanc corrected, switched mode power supplies that offers very

input current shaping technique low start-up and operating currents.

• Peak or average current, continuous boost, leading edge

PFC (Input Current Shaping Technology) Power Factor Correction (PFC) offers the use of smaller, lower

• High efficiency trailing-edge current mode PWM cost bulk capacitors, reduces power line loading and stress on

• Low supply currents; start-up: 150µA typ., operating: the switching FETs, and results in a power supply fully compli-

2mA typ. ant to IEC1000-3-2 specifications. The FAN4803 includes

• Synchronized leading and trailing edge modulation circuits for the implementation of a leading edge, average

• Reduces ripple current in the storage capacitor between current “boost” type PFC and a trailing edge, PWM.

the PFC and PWM sections

• Overvoltage, UVLO, and brownout protection The FAN4803-1’s PFC and PWM operate at the same

• PFC VCCOVP with PFC Soft Start frequency, 67kHz. The PFC frequency of the FAN4803-2 is

automatically set at half that of the 134kHz PWM. This

higher frequency allows the user to design with smaller

PWM components while maintaining the optimum operating

frequency for the PFC. An overvoltage comparator shuts

down the PFC section in the event of a sudden decrease in

load. The PFC section also includes peak current limiting for

enhanced system reliability.

Block Diagram

7

PFC OFF VCC REF VREF

VEAO 7V +

4 COMP VCC OVP

+

– 17.5V COMP GND

16.2V – 2

35µA

–1 M3

M4

M1 M2 PFC PFC OUT

R1 C1 CONTROL 1

30pF LOGIC

M7

LEADING

EDGE PFC

ONE PIN ERROR AMPLIFIER

ISENSE + TRAILING

3 –4 COMP SOFT START EDGE PWM

PFC ILIMIT –

+

–1V –

VCC PFC/PWM UVLO

VREF OSCILLATOR

PFC – 67kHz DUTY CYCLE

26k PWM – 134kHz LIMIT

VDC

5 PWM COMPARATOR

–

COMP

40k +

PWM PWM OUT

1.2V – CONTROL 8

COMP LOGIC

ILIMIT +

6

M6

DC ILIMIT

1.5V –

+

REV. 1.2.3 11/2/04

FAN4803 PRODUCT SPECIFICATION

Pin Configuration

FAN4803

8-Pin PDIP (P08)

8-Pin SOIC (S08)

PFC OUT 1 8 PWM OUT

GND 2 7 VCC

ISENSE 3 6 ILIMIT

VEAO 4 5 VDC

TOP VIEW

Pin Description

Pin Name Function

1 PFC OUT PFC driver output

2 GND Ground

3 ISENSE Current sense input to the PFC current limit comparator

4 VEAO PFC one-pin error amplifier input

5 VDC PWM voltage feedback input

6 ILIMIT PWM current limit comparator input

7 VCC Positive supply (may require an external shunt regulator)

8 PWM OUT PWM driver output

Absolute Maximum Ratings

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum

ratings are stress ratings only and functional device operation is not implied.

Parameter Min Max Unit

ICC Current (average) 40 mA

VCC MAX 18.3 V

ISENSE Voltage -5 1 V

Voltage on Any Other Pin GND – 0.3 VCC + 0.3 V

Peak PFC OUT Current, Source or Sink 1 A

Peak PWM OUT Current, Source or Sink 1 A

PFC OUT, PWM OUT Energy Per Cycle 1.5 µJ

Junction Temperature 150 °C

Storage Temperature Range -65° 150 °C

Lead Temperature (Soldering, 10 sec) 260 °C

Thermal Resistance (θJA)

Plastic DIP 110 °C/W

Plastic SOIC 160 °C/W

Operating Conditions

Temperature Range

FAN4803CS-X 0°C to 70°C

FAN4803CP-X 0°C to 70°C

2 REV. 1.2.3 11/2/04

PRODUCT SPECIFICATION FAN4803

Electrical Characteristics

Unless otherwise specified, VCC = 15V, TA = Operating Temperature Range (Note 1)

Symbol Parameter Conditions Min TYP MAX UNITS

One-pin Error Amplifier

VEAO Output Current TA = 25°C, VEAO = 6V 34.0 36.5 39.0 µA

Line Regulation 10V < VCC < 15V, VEAO = 6V 0.1 0.3 µA

VCC OVP Comparator

Threshold Voltage 15.5 16.3 16.8 V

PFC ILIMIT Comparator

Threshold Voltage -0.9 -1 -1.15 V

Delay to Output 150 300 ns

DC ILIMIT Comparator

Threshold Voltage 1.4 1.5 1.6 V

Delay to Output 150 300 ns

Oscillator

Initial Accuracy TA = 25°C 60 67 74 kHz

Voltage Stability 10V < VCC < 15V 1 %

Temperature Stability 2 %

Total Variation Over Line and Temp 60 67 74.5 kHz

Dead Time PFC Only 0.3 0.45 0.65 µs

PFC

Minimum Duty Cycle VEAO > 7.0V,ISENSE = -0.2V 0 %

Maximum Duty Cycle VEAO < 4.0V,ISENSE = 0V 90 95 %

Output Low Impedance 8 15 Ω

Output Low Voltage IOUT = –100mA 0.8 1.5 V

IOUT = –10mA, VCC = 8V 0.7 1.5 V

Output High Impedance 8 15 Ω

Output High Voltage IOUT = 100mA, VCC = 15V 13.5 14.2 V

Rise/Fall Time CL = 1000pF 50 ns

PWM

Duty Cycle Range FAN4803-2 0-41 0-47 0-50 %

FAN4803-1 0-49.5 0-50 %

Output Low Impedance 8 15 Ω

Output Low Voltage IOUT = –100mA 0.8 1.5 V

IOUT = –10mA, VCC = 8V 0.7 1.5 V

Output High Impedance 8 15 Ω

Output High Voltage IOUT = 100mA, VCC = 15V 13.5 14.2 V

Rise/Fall Time CL = 1000pF 50 ns

Supply

VCC Clamp Voltage (VCCZ) ICC = 10mA 16.7 17.5 18.3 V

Start-up Current VCC = 11V, CL = 0 0.2 0.4 mA

Operating Current VCC = 15V, CL = 0 2.5 4 mA

Undervoltage Lockout Threshold 11.5 12 12.5 V

Undervoltage Lockout Hysteresis 2.4 2.9 3.4 V

Note:

1. Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

REV. 1.2.3 11/2/04 3

FAN4803 PRODUCT SPECIFICATION

Functional Description control of the PWM stage. The current ramp is offset inter-

nally by 1.2V and then compared against the opto feedback

The FAN4803 consists of an average current mode boost voltage to set the PWM duty cycle.

Power Factor Corrector (PFC) front end followed by a syn-

chronized Pulse Width Modulation (PWM) controller. It is PFC OUT and PWM OUT

distinguished from earlier combo controllers by its low pin

count, innovative input current shaping technique, and very PFC OUT and PWM OUT are the high-current power driv-

low start-up and operating currents. The PWM section is ers capable of directly driving the gate of a power MOSFET

dedicated to peak current mode operation. It uses conven- with peak currents up to ±1A. Both outputs are actively held

tional trailing-edge modulation, while the PFC uses leading- low when VCC is below the UVLO threshold level.

edge modulation. This proprietary Leading Edge/Trailing

Edge (LETE) modulation technique helps to minimize ripple VCC

current in the PFC DC buss capacitor. VCC is the power input connection to the IC. The VCC start-

up current is 150µA . The no-load I CC current is 2mA. VCC

The FAN4803 is offered in two versions. The FAN4803-1 quiescent current will include both the IC biasing currents

operates both PFC and PWM sections at 67kHz, while the and the PFC and PWM output currents. Given the operating

FAN4803-2 operates the PWM section at twice the fre- frequency and the MOSFET gate charge (Qg), average

quency (134kHz) of the PFC. This allows the use of smaller PFC and PWM output currents can be calculated as IOUT =

PWM magnetics and output filter components, while mini- Qg x F. The average magnetizing current required for any

mizing switching losses in the PFC stage. gate drive transformers must also be included. The VCC pin

is also assumed to be proportional to the PFC output voltage.

In addition to power factor correction, several protection fea- Internally it is tied to the VCCOVP comparator (16.2V)

tures have been built into the FAN4803. These include soft providing redundant high-speed over-voltage protection

start, redundant PFC over-voltage protection, peak current (OVP) of the PFC stage. VCC also ties internally to the

limiting, duty cycle limit, and under voltage lockout UVLO circuitry, enabling the IC at 12V and disabling it at

(UVLO). See Figure 12 for a typical application. 9.1V. VCC must be bypassed with a high quality ceramic

bypass capacitor placed as close as possible to the IC.

Detailed Pin Descriptions Good bypassing is critical to the proper operation of the

FAN4803.

VEAO

VCC is typically produced by an additional winding off the

This pin provides the feedback path which forces the PFC boost inductor or PFC Choke, providing a voltage that is pro-

output to regulate at the programmed value. It connects to portional to the PFC output voltage. Since the VCCOVP max

programming resistors tied to the PFC output voltage and is voltage is 16.2V, an internal shunt limits VCC overvoltage to

shunted by the feedback compensation network. an acceptable value. An external clamp, such as shown in

Figure 1, is desirable but not necessary.

ISENSE

This pin ties to a resistor or current sense transformer which VCC

senses the PFC input current. This signal should be negative

with respect to the IC ground. It internally feeds the pulse-

by-pulse current limit comparator and the current sense feed- 1N4148

back signal. The ILIMIT trip level is –1V. The ISENSE feed-

back is internally multiplied by a gain of four and compared

1N4148

against the internal programmed ramp to set the PFC duty

cycle. The intersection of the boost inductor current

downslope with the internal programming ramp determines 1N5246B

the boost off-time.

GND

VDC

This pin is typically tied to the feedback opto-collector. It is Figure 1. Optional VCC Clamp

tied to the internal 5V reference through a 26kΩ resistor and

to GND through a 40kΩ resistor. VCC is internally clamped to 16.7V minimum, 18.3V maxi-

mum. This limits the maximum VCC that can be applied to

ILIMIT the IC while allowing a VCC which is high enough to trip the

This pin is tied to the primary side PWM current sense resis- VCCOVP. The max current through this zener is 10mA.

tor or transformer. It provides the internal pulse-by-pulse External series resistance is required in order to limit the

current limit for the PWM stage (which occurs at 1.5V) and current through this Zener in the case where the VCC voltage

the peak current mode feedback path for the current mode exceeds the zener clamp level.

4 REV. 1.2.3 11/2/04

PRODUCT SPECIFICATION FAN4803

GND converter is the full wave rectified AC line voltage. No filter-

GND is the return point for all circuits associated with ing is applied following the bridge rectifier, so the input

this part. Note: a high-quality, low impedance ground is voltage to the boost converter ranges, at twice line frequency,

critical to the proper operation of the IC. High frequency from zero volts to the peak value of the AC input and back to

grounding techniques should be used. zero. By forcing the boost converter to meet two simulta-

neous conditions, it is possible to ensure that the current that

Power Factor Correction the converter draws from the power line matches the instan-

taneous line voltage. One of these conditions is that the

Power factor correction makes a nonlinear load look like a output voltage of the boost converter must be set higher than

resistive load to the AC line. For a resistor, the current drawn the peak value of the line voltage. A commonly used value is

from the line is in phase with, and proportional to, the line 385VDC, to allow for a high line of 270VACRMS. The other

voltage. This is defined as a unity power factor is (one). A condition is that the current that the converter is allowed to

common class of nonlinear load is the input of a most power draw from the line at any given instant must be proportional

supplies, which use a bridge rectifier and capacitive input fil- to the line voltage.

ter fed from the line. Peak-charging effect, which occurs on

the input filter capacitor in such a supply, causes brief high- Since the boost converter topology in the FAN4803 PFC is

amplitude pulses of current to flow from the power line, of the current-averaging type, no slope compensation is

rather than a sinusoidal current in phase with the line volt- required.

age. Such a supply presents a power factor to the line of less

than one (another way to state this is that it causes significant

current harmonics to appear at its input). If the input current Leading/Trailing Modulation

drawn by such a supply (or any other nonlinear load) can be Conventional Pulse Width Modulation (PWM) techniques

made to follow the input voltage in instantaneous amplitude, employ trailing edge modulation in which the switch will

it will appear resistive to the AC line and a unity power factor turn ON right after the trailing edge of the system clock.

will be achieved. The error amplifier output voltage is then compared with the

modulating ramp. When the modulating ramp reaches the

To hold the input current draw of a device drawing power level of the error amplifier output voltage, the switch will be

from the AC line in phase with, and proportional to, the input turned OFF. When the switch is ON, the inductor current will

voltage, a way must be found to prevent that device from ramp up. The effective duty cycle of the trailing edge modu-

loading the line except in proportion to the instantaneous line lation is determined during the ON time of the switch. Figure

voltage. The PFC section of the FAN4803 uses a boost- 2 shows a typical trailing edge control scheme.

mode DC-DC converter to accomplish this. The input to the

L1 SW2 I2 I3

I1

+ I4

VIN

DC SW1 RL

C1

RAMP

VEAO

REF U3

+

–EA

DFF TIME

+ VSW1

RAMP – R Q

OSC U1 D U2

CLK

Q

U4 CLK

TIME

Figure 2. Typical Trailing Edge Control Scheme.

REV. 1.2.3 11/2/04 5

FAN4803 PRODUCT SPECIFICATION

In the case of leading edge modulation, the switch is turned Programming Resistor Value

OFF right at the leading edge of the system clock. When the Equation 1 calculates the required programming resistor

modulating ramp reaches the level of the error amplifier value.

output voltage, the switch will be turned ON. The effective

duty-cycle of the leading edge modulation is determined VBOOST − VEAO 400V − 50V

.

during the OFF time of the switch. Figure 3 shows a leading Rp = = = 113

. MΩ (1)

IPGM 35µA

edge control scheme.

One of the advantages of this control technique is that it PFC Voltage Loop Compensation

requires only one system clock. Switch 1 (SW1) turns OFF

The voltage-loop bandwidth must be set to less than 120Hz

and Switch 2 (SW2) turns ON at the same instant to mini-

to limit the amount of line current harmonic distortion.

mize the momentary “no-load” period, thus lowering ripple

A typical crossover frequency is 30Hz. Equation 1, for

voltage generated by the switching action. With such

simplicity, assumes that the pole capacitor dominates

synchronized switching, the ripple voltage of the first stage

the error amplifier gain at the loop unity-gain frequency.

is reduced. Calculation and evaluation have shown that the

Equation 2 places a pole at the crossover frequency,

120Hz component of the PFC’s output ripple voltage can be

providing 45 degrees of phase margin. Equation 3 places a

reduced by as much as 30% using this method, substantially

zero one decade prior to the pole. Bode plots showing the

reducing dissipation in the high-voltage PFC capacitor.

overall gain and phase are shown in Figures 5 and 6. Figure 4

displays a simplified model of the voltage loop.

Typical Applications

Pin

One Pin Error Amp CCOMP = 2 (2)

R p × V BOOST × ∆VEAO × COUT × (2 × π × f)

The FAN4803 utilizes a one pin voltage error amplifier in the

300W

PFC section (VEAO). The error amplifier is in reality a cur- CCOMP =

rent sink which forces 35µA through the output program- 11.3MΩ × 400V × 0.5V × 220µF × (2 × π × 30Hz)2

ming resistor. The nominal voltage at the VEAO pin is 5V. CCOMP = 16nF

The VEAO voltage range is 4 to 6V. For a 11.3MΩ resistor

chain to the boost output voltage and 5V steady state at the

VEAO, the boost output voltage would be 400V.

L1 SW2 I2 I3

I1

+ I4

VIN

DC SW1 RL

C1

RAMP

VEAO

U3

+

REF –EA

VEAO TIME

DFF

CMP

+ VSW1

RAMP – R Q

OSC U1 D U2

CLK

Q

U4 CLK

TIME

Figure 3. Typical Leading Edge Control Scheme.

6 REV. 1.2.3 11/2/04

PRODUCT SPECIFICATION FAN4803

Internal Voltage Ramp

The internal ramp current source is programmed by way of

(3) the VEAO pin voltage. Figure 7 displays the internal ramp

1

RCOMP = current vs. the VEAO voltage. This current source is used to

2 × π × f × CCOMP develop the internal ramp by charging the internal 30pF +12/

1 –10% capacitor. See Figures 10 and 11. The frequency of the

RCOMP = = 330kΩ internal programming ramp is set internally to 67kHz.

. 8 × 30Hz × 16nF

62

1 PFC Current Sense Filtering

CZERO =

f

2×π× × RCOMP (4) In DCM, the input current wave shaping technique used by

10 the FAN4803 could cause the input current to run away.

1 In order for this technique to be able to operate properly

CZERO = . µF

= 016 under DCM, the programming ramp must meet the boost

6.28 × 3Hz × 330kΩ

inductor current down-slope at zero amps. Assuming the

programming ramp is zero under light load, the OFF-time

will be terminated once the inductor current reaches zero.

VO 60

Power Stage

Overall Gain

40 Compensation

11.3MΩ Network Gain

FAN4803 IOUT VEAO FAN4803

RLOAD 20

667Ω

GAIN (dB)

220µF 330kΩ IVEAO

∆VEAO +

34µA 0

15nF

–

0.15µF –20

POWER COMPENSATION

STAGE –40

Figure 4. Voltage Control Loop –60

0.1 1 10 100 1000

FREQUENCY (Hz)

Figure 5. Voltage Loop Gain

50

0

Power Stage FF @ –55ºC

Overall

Compensation TYP @ –55ºC

40

Network

50 TYP @ ROOM TEMP

30 TYP @ 155ºC

IRAMP (µA)

PHASE (º)

SS @ 155ºC

100

20

150 10

0

200 0 1 2 3 4 5 6 7

0.1 1 10 100 1000

VEAO (V)

FREQUENCY (Hz)

Figure 6. Voltage Loop Phase Figure 7. Internal Ramp Current vs. VEAO

REV. 1.2.3 11/2/04 7

FAN4803 PRODUCT SPECIFICATION

Subsequently the PFC gate drive is initiated, eliminating the sequence. Once disabled, the VEAO pin charges HIGH by

necessary dead time needed for the DCM mode. This forces way of the external components until the PFC duty cycle

the output to run away until the VCC OVP shuts down the goes to zero, disabling the PFC. The VCC OVP resets once

PFC. This situation is corrected by adding an offset voltage the VCC discharges below 16.2V, enabling the VEAO current

to the current sense signal, which forces the duty cycle to sink and discharging the VEAO compensation components

zero at light loads. This offset prevents the PFC from operat- until the steady state operating point is reached. It should be

ing in the DCM and forces pulse-skipping from CCM to no- noted that, as shown in Figure 8, once the VEAO pin exceeds

duty, avoiding DMC operation. External filtering to the cur- 6.5V, the internal ramp is defeated. Because of this, an exter-

rent sense signal helps to smooth out the sense signal, nal Zener can be installed to reduce the maximum voltage to

expanding the operating range slightly into the DCM range, which the VEAO pin may rise in a shutdown condition.

but this should be done carefully, as this filtering also Clamping the VEAO pin externally to 7.4V will reduce the

reduces the bandwidth of the signal feeding the pulse-by- time required for the VEAO pin to recover to its steady state

pulse current limit signal. Figure 9 displays a typical circuit value.

for adding offset to ISENSE at light loads.

UVLO

PFC Start-Up and Soft Start Once VCC reaches 12V both the PFC and PWM are enabled.

During steady state operation VEAO draws 35µA. At start-up The UVLO threshold is 9.1V providing 2.9V of hysteresis.

the internal current mirror which sinks this current is defeated

until VCC reaches 12V. This forces the PFC error voltage to Generating VCC

VCC at the time that the IC is enabled. With leading edge An internal clamp limits overvoltage to VCC. This clamp

modulation VCC on the VEAO pin forces zero duty on the circuit ensures that the VCC OVP circuitry of the FAN4803

PFC output. When selecting external compensation compo- will function properly over tolerance and temperature while

nents and VCC supply circuits VEAO must not be prevented protecting the part from voltage transients. This circuit

from reaching 6V prior to VCC reaching 12V in the turn-on allows the FAN4803 to deliver 15V nominal gate drive at

sequence. This will guarantee that the PFC stage will enter PWM OUT and PFC OUT, sufficient to drive low-cost

soft-start. Once VCC reaches 12V the 35µA VEAO current IGBTs.

sink is enabled. VEAO compensation components are then

discharged by way of the 35µA current sink until the steady It is important to limit the current through the Zener to avoid

state operating point is reached. See Figure 8. overheating or destroying it. This can be done with a single

resistor in series with the VCC pin, returned to a bias supply

PFC Soft Recovery Following VCC OVP of typically 14V to 18V. The resistor value must be chosen

The FAN4803 assumes that VCC is generated from a source to meet the operating current requirement of the FAN4803

that is proportional to the PFC output voltage. Once that itself (4.0mA max) plus the current required by the two gate

source reaches 16.2V the internal current sink tied to the driver outputs.

VEAO pin is disabled just as in the soft start turn-on

VCC 10V/div. to BR1 -Ve

C23 R29 R28 R4

0 0.01µF 20kΩ 20kΩ 1kΩ

VEAO 10V/div. PFC

GATE R19

0 CR16 C16

10kΩ R3

1N4148 1µF 0.15Ω

VOUT 10V/div. ISENSE 3W

C5

0 0.0082µF

VBOOST 200V/div. VCC

(see Figure 12)

RTN

0

200ms/Div.

Figure 8. PFC Soft Start Figure 9. ISENSE Offset for Light Load Conditions

8 REV. 1.2.3 11/2/04

PRODUCT SPECIFICATION FAN4803

VCC OVP Component Reduction

VCC is assumed to be a voltage proportional to the PFC Components associated with the VRMS and IRMS pins of a

output voltage, typically a bootstrap winding off the boost typical PFC controller such as the ML4824 have been elimi-

inductor. The VCC OVP comparator senses when this volt- nated. The PFC power limit and bandwidth does vary with

age exceeds 16V, and terminates the PFC output drive while line voltage. Double the power can be delivered from a 220

disabling the VEAO current sink. Once the VEAO current V AC line versus a 110 V AC line. Since this is a combina-

sink is disabled, the VEAO voltage will charge unabated, tion PFC/PWM, the power to the load is limited by the PWM

except for a diode clamp to VCC, reducing the PFC pulse stage.

width. Once the VCC rail has decreased to below 16.2V the

VEAO sink will be enabled, discharging external VEAO

compensation components until the steady state voltage is

reached. Given that 15V on VCC corresponds to 400V on

the PFC output, 16V on VCC corresponds to an OVP level of

426V.

VISENSE

VC1 RAMP

GATE

DRIVE

OUTPUT

Figure 10. Typical Peak Current Mode Waveforms

VOUT = 400V

RP

VC1

GATE

VEAO

OUTPUT

4 +

COMP

C1 –

30pF

RCOMP CCOMP 35µA 5V

CZERO R1

ISENSE

3 –4

VI SENSE

Figure 11. FAN4803 PFC Control

REV. 1.2.3 11/2/04 9

FAN4803 PRODUCT SPECIFICATION

102T RURP860

C19 L2 CR1 8A, 600V

TH1

4.7nF

250VAC 10Ω 1000µH

LINE F1 5A 250V FQP9N50

5A

C4 GBU4J Q5

J1-1 R1

R24 0.47µF

470kΩ 250VAC BR1

600V 36Ω

0.5W 4A

FQP9N50

NEUTRAL Q2

R2 C16

L3 C1

J1-2 0.01µF

C20 220µF

4.7nF 36Ω 450V

250VAC R22 1N5246B

10kΩ CR5

16V 0.5W

R3 0.15Ω 3W

FQP9N50

P6KE51CA

Q4

1N5818 CR7 R8 36Ω CR18 51V

R30 200Ω UF4005

T2 CR3 C18 4.7nF C25

R23 R36 220Ω

1 3 R38 22Ω Q1 0.01µF

10kΩ

2N3906 500V

C29 0.01µF 12V

10 4 T1

MBR3060PT J2-1

CR2

CR2 C3 R14

R27 30A, 60V

30A 1µF 150Ω

C7 20kΩ

60V C2 2W

R13 0.1µF 3W

2200µF

5.8MΩ 12VRET

R7

R26 L1 25µH J2-2

10Ω

20kΩ

3W 1N4148 C26

C23 0.01µF

CR8

0.01µF R29 20kΩ 500V

C11 L2

1000µF

C22 C9

CR16 R19 1µF 1µF 4T

IN4148 10kΩ

R31

10Ω C21 1N4148

R6 1.2kΩ

1µF CR15

R28 C14

R12 FQP9N50

20kΩ 1N5818 4.7µF

5.8MΩ FAN4803 CR10

Q3 R9

1 8 R5 36Ω 1.5kΩ

PFC PWM 5

2 7 U3 R37

GND 1

VCC 330Ω

R4 1kΩ R11 150Ω C17

3 6 0.1µF R15

ISENSE ILIMIT

1N5818 CR12 R32 100Ω 2 9.09kΩ

4 5 4

VEAO VDC

C13 1nF

R25 C5 C10 R10

390kΩ 8.2nF 2.2nF 0.75Ω

R21 3W R20 R17 3.3kΩ

7.0V C15 C28

10kΩ CR4 510Ω

0.015µF C6 1µF 3

C8 C27 UF4005 C12 0.1µF R18 1kΩ

1µF 0.01µF U2 1

0.15µF

2 RC431A

CR11 CR9 R16

1N5818 1N52468 2.37kΩ

Figure 12. Typical Application Circuit. Universal Input 240W 12V DC Output

10 REV. 1.2.3 11/2/04

PRODUCT SPECIFICATION FAN4803

Mechanical Dimensions

Package: S08

8 Pin SOIC

0.189 - 0.199

(4.80 - 5.06)

8

0.148 - 0.158 0.228 - 0.244

PIN 1 ID

(3.76 - 4.01) (5.79 - 6.20)

1

0.017 - 0.027 0.050 BSC

(0.43 - 0.69) (1.27 BSC)

(4 PLACES)

0.059 - 0.069

(1.49 - 1.75)

0°–8°

0.012 - 0.020 0.015 - 0.035

0.055 - 0.061 0.004 - 0.010 0.006 - 0.010

(0.30 - 0.51) (0.38 - 0.89)

(1.40 - 1.55) (0.10 - 0.26) (0.15 - 0.26)

SEATING PLANE

Package: P08

8-Pin PDIP

0.365 - 0.385

(9.27 - 9.77)

0.055 - 0.065

(1.39 - 1.65)

0.240 - 0.260 0.299 - 0.335

PIN 1 ID

(6.09 - 6.60) (7.59 - 8.50)

1

0.020 MIN

(0.51 MIN)

(4 PLACES) 0.100 BSC

(2.54 BSC)

0.015 MIN

(0.38 MIN)

0.170 MAX

(4.32 MAX)

0.016 - 0.020 0.008 - 0.012

0.125 MIN (0.40 - 0.51) 0° - 15° (0.20 - 0.31)

(3.18 MIN)

SEATING PLANE

REV. 1.2.3 11/2/04 11

FAN4803 PRODUCT SPECIFICATION

Ordering Information

Part Number PFC/PWM Frequency Temperature Range Package

FAN4803CS-1 67kHz / 67kHz 0°C to 70°C 8-Pin SOIC (S08)

FAN4803CS-2 67kHz / 134kHz 0°C to 70°C 8-Pin SOIC (S08)

FAN4803CP-1 67kHz / 67kHz 0°C to 70°C 8-Pin PDIP (P08)

FAN4803CP-2 67kHz / 134kHz 0°C to 70°C 8-Pin PDIP (P08)

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO

ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME

ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;

NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES

OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR

CORPORATION. As used herein:

1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support

which, (a) are intended for surgical implant into the body, device or system whose failure to perform can be

or (b) support or sustain life, and (c) whose failure to reasonably expected to cause the failure of the life support

perform when properly used in accordance with device or system, or to affect its safety or effectiveness.

instructions for use provided in the labeling, can be

reasonably expected to result in a significant injury of the

user.

www.fairchildsemi.com

11/2/04 0.0m 003

Stock#DS30004803

2004 Fairchild Semiconductor Corporation

You might also like

- The Physics of Nanoelectronics, First Edition, Tero T. Heikkilä, © Tero T. Heikkilä 2013Document288 pagesThe Physics of Nanoelectronics, First Edition, Tero T. Heikkilä, © Tero T. Heikkilä 2013Miloš DražićNo ratings yet

- Varicon eDocument6 pagesVaricon eHugo Samuel López VasquezNo ratings yet

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- A Step by Step Procedure On Designing Circuit Layout Using Express PCB SoftwareDocument7 pagesA Step by Step Procedure On Designing Circuit Layout Using Express PCB SoftwarePankaj SinghNo ratings yet

- Escrap Refiners Shopping Cheat Sheet - Rev 0.6Document10 pagesEscrap Refiners Shopping Cheat Sheet - Rev 0.6ulfheidner910367% (3)

- Power Factor Correction and PWM Controller Combo: Features General DescriptionDocument14 pagesPower Factor Correction and PWM Controller Combo: Features General DescriptionbiggertvNo ratings yet

- ML - ML4824-2 Samsung Service ManualDocument15 pagesML - ML4824-2 Samsung Service ManualpgcclNo ratings yet

- FL7930BDocument23 pagesFL7930BgkopchatovNo ratings yet

- R8CB05BO ChampionDocument15 pagesR8CB05BO ChampionwwwxxxNo ratings yet

- CM6500 PFC PWM AtxDocument17 pagesCM6500 PFC PWM Atxxerox4512No ratings yet

- CM6805BO: General Description FeaturesDocument15 pagesCM6805BO: General Description FeaturesQuaddroNo ratings yet

- FAN7930C Critical Conduction Mode PFC Controller: Features DescriptionDocument22 pagesFAN7930C Critical Conduction Mode PFC Controller: Features DescriptionRobinson FernandoNo ratings yet

- General Description Features: 10-PIN Green-Mode PFC/PWM Combo CONTROLLERDocument15 pagesGeneral Description Features: 10-PIN Green-Mode PFC/PWM Combo CONTROLLERgabriel SantosNo ratings yet

- FAN6921MR Integrated Critical Mode PFC and Quasi-Resonant Current Mode PWM ControllerDocument25 pagesFAN6921MR Integrated Critical Mode PFC and Quasi-Resonant Current Mode PWM ControllereduardskNo ratings yet

- CM6807Document16 pagesCM6807mhmd193No ratings yet

- CM6807 PDFDocument16 pagesCM6807 PDFAmjad ZaidNo ratings yet

- FAN7930C Critical Conduction Mode PFC Controller: Features DescriptionDocument22 pagesFAN7930C Critical Conduction Mode PFC Controller: Features DescriptionNorgen QuinteroNo ratings yet

- General Description Features: L S U C PFC/PWM C CDocument18 pagesGeneral Description Features: L S U C PFC/PWM C CArthit SomrangNo ratings yet

- ML4824 Power Factor Correction and PWM Controller Combo: General Description FeaturesDocument16 pagesML4824 Power Factor Correction and PWM Controller Combo: General Description FeaturesTaras100% (1)

- CM6805Document16 pagesCM6805mtomescu0% (1)

- CM6803Document15 pagesCM6803Indraz NilNo ratings yet

- Features Description: D D D D DDocument41 pagesFeatures Description: D D D D DNelson OrjuelaNo ratings yet

- Features Description: D D D D DDocument35 pagesFeatures Description: D D D D DPrashant MehtaNo ratings yet

- Datasheet CM6802Document18 pagesDatasheet CM6802Gilson3DNo ratings yet

- Nb679a MpsDocument19 pagesNb679a MpswarkeravipNo ratings yet

- Hiper Family Datasheet-14271Document27 pagesHiper Family Datasheet-14271nguyenthaibinh13No ratings yet

- FAN6961 FairchildSemiconductorDocument13 pagesFAN6961 FairchildSemiconductorAconatic tvhomeNo ratings yet

- KA5M0965Q: Fairchild Power Switch (SPS)Document14 pagesKA5M0965Q: Fairchild Power Switch (SPS)Jose Angel TorrealbaNo ratings yet

- Fast Pulse Width Modulation (FPWM) Technology For DC-DC Converter, Featuring High-Speed Response With A Clock-Synchronized Comparator Control MethodDocument2 pagesFast Pulse Width Modulation (FPWM) Technology For DC-DC Converter, Featuring High-Speed Response With A Clock-Synchronized Comparator Control MethodCan ERTANNo ratings yet

- TDA16888 SiemensSemiconductorGroupDocument39 pagesTDA16888 SiemensSemiconductorGroupGonzaloNo ratings yet

- MP28167GQ ADocument32 pagesMP28167GQ AHamouda MahmodNo ratings yet

- General Description Features: Design For High Efficient Power Supply at Both Full Load and Light LoadDocument20 pagesGeneral Description Features: Design For High Efficient Power Supply at Both Full Load and Light LoadRomanNo ratings yet

- Datasheet Ic Carga Moto E4Document48 pagesDatasheet Ic Carga Moto E4Xvier100No ratings yet

- Air Conditioner Reference Design User GuideDocument25 pagesAir Conditioner Reference Design User GuideDinh TucNo ratings yet

- Three-Phase Sensorless Fan Driver: Description Features and BenefitsDocument9 pagesThree-Phase Sensorless Fan Driver: Description Features and BenefitsLee HoonNo ratings yet

- FAN6961 Bounari Mode PFC Contr PDFDocument13 pagesFAN6961 Bounari Mode PFC Contr PDFendersonNo ratings yet

- Is Now Part ofDocument26 pagesIs Now Part ofeduardskNo ratings yet

- LTC1628/LTC1628-PG High Efficiency, 2-Phase Synchronous Step-Down Switching RegulatorsDocument32 pagesLTC1628/LTC1628-PG High Efficiency, 2-Phase Synchronous Step-Down Switching RegulatorsCarlos Henrique RibasNo ratings yet

- En - APEC2017 Exhibitor Seminar DigitalControl IC 1Document27 pagesEn - APEC2017 Exhibitor Seminar DigitalControl IC 1Toán Doãn QuốcNo ratings yet

- NB679Document18 pagesNB679Tri Nguyen Real EstateNo ratings yet

- Cm6502 Apfc Chip (Epa90+ Zvs Type)Document20 pagesCm6502 Apfc Chip (Epa90+ Zvs Type)1 2No ratings yet

- 22201B PDFDocument28 pages22201B PDFSanchez Resendiz BonifacioNo ratings yet

- A4942 DatasheetDocument13 pagesA4942 DatasheetLee HoonNo ratings yet

- High Performance Power Combi Controller TDA 16888: PFC SectionDocument39 pagesHigh Performance Power Combi Controller TDA 16888: PFC SectionaaaaaNo ratings yet

- Low Power PWM Controller For Off-Line Adapter Ap3710Document16 pagesLow Power PWM Controller For Off-Line Adapter Ap3710Abdulraouf DefnanyNo ratings yet

- 28V, 6.5A, Low Iq, Synchronous Buck Converter With 2-Bit VIDDocument24 pages28V, 6.5A, Low Iq, Synchronous Buck Converter With 2-Bit VIDElla Wijaya ChandraNo ratings yet

- MP3394 r1.07 PDFDocument17 pagesMP3394 r1.07 PDFAnonymous biMSzTyszNo ratings yet

- Circuito Integrado FAN4800Document22 pagesCircuito Integrado FAN4800daud_asiNo ratings yet

- MCP 14628Document24 pagesMCP 14628Hưng ĐứcNo ratings yet

- Ic 45532Document20 pagesIc 45532shaukatNo ratings yet

- CM6502THH: General Description FeaturesDocument21 pagesCM6502THH: General Description Features1 2No ratings yet

- IR1150 DatasheetDocument18 pagesIR1150 DatasheetPoliana RochaNo ratings yet

- LTC 15389 FDocument32 pagesLTC 15389 FEdson HenriqueNo ratings yet

- Ic - NCP1631Document24 pagesIc - NCP1631Alexandre SoaresNo ratings yet

- High Efficiency 3A, 16V, 500Khz Synchronous Step Down ConverterDocument15 pagesHigh Efficiency 3A, 16V, 500Khz Synchronous Step Down ConverterkadirovNo ratings yet

- BQ 24259Document50 pagesBQ 24259teehoweNo ratings yet

- LM 5023Document38 pagesLM 5023Kartik hegdeNo ratings yet

- UC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllerDocument15 pagesUC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM Controllernita_alecsandruNo ratings yet

- TEA1755T DatasheetDocument35 pagesTEA1755T DatasheetDext JafremNo ratings yet

- Integrated Sensorless FOC BLDC Driver: Features and Benefits DescriptionDocument15 pagesIntegrated Sensorless FOC BLDC Driver: Features and Benefits DescriptionBùi TuyếnNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Isc BU103A: Isc Silicon NPN Power TransistorDocument2 pagesIsc BU103A: Isc Silicon NPN Power TransistorAnca SterianNo ratings yet

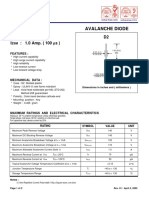

- Avalanche Diode: V: 140 Volts I: 1.0 Amp. (100 S) D2Document2 pagesAvalanche Diode: V: 140 Volts I: 1.0 Amp. (100 S) D2Anca SterianNo ratings yet

- Avalanche Diode: V: 120 Volts I: 2.0 Amp. (100 S) D2Document2 pagesAvalanche Diode: V: 120 Volts I: 2.0 Amp. (100 S) D2Anca SterianNo ratings yet

- Features: Vishay SemiconductorsDocument4 pagesFeatures: Vishay SemiconductorsAnca SterianNo ratings yet

- SMP60N06 PDFDocument5 pagesSMP60N06 PDFAnca SterianNo ratings yet

- Irfz40 - Irfz45 PDFDocument5 pagesIrfz40 - Irfz45 PDFAnca SterianNo ratings yet

- Metal Oxide Varistor 7mm Disc Metal Oxide Varistor 7mm DiscDocument1 pageMetal Oxide Varistor 7mm Disc Metal Oxide Varistor 7mm DiscAnca SterianNo ratings yet

- STP40NF10 STB40NF10 - STB40NF10-1Document12 pagesSTP40NF10 STB40NF10 - STB40NF10-1Anca SterianNo ratings yet

- RFG70N06, RFP70N06, RF1S70N06, RF1S70N06SM: 70A, 60V, 0.014 Ohm, N-Channel Power Mosfets FeaturesDocument9 pagesRFG70N06, RFP70N06, RF1S70N06, RF1S70N06SM: 70A, 60V, 0.014 Ohm, N-Channel Power Mosfets FeaturesAnca SterianNo ratings yet

- SUP/SUB70N06-14: Vishay SiliconixDocument5 pagesSUP/SUB70N06-14: Vishay SiliconixAnca SterianNo ratings yet

- FRCC - PC.004.B2.22-MT-MTZ-Feb2018 - DanfossDocument40 pagesFRCC - PC.004.B2.22-MT-MTZ-Feb2018 - DanfossAnca SterianNo ratings yet

- MTZ36-4VM - Danfoss CompressorDocument3 pagesMTZ36-4VM - Danfoss CompressorAnca SterianNo ratings yet

- BCT5511 Toaster ControllerDocument6 pagesBCT5511 Toaster ControllerTed SunNo ratings yet

- IRS2453 (1) D (S) : Features Product SummaryDocument18 pagesIRS2453 (1) D (S) : Features Product SummaryGabriel CalderonNo ratings yet

- AC Motor Control PDFDocument2 pagesAC Motor Control PDFgabrielsosa73No ratings yet

- C5X Design Rules 45000099 RevTDocument89 pagesC5X Design Rules 45000099 RevTMohammed TamheedNo ratings yet

- SNM of SramDocument6 pagesSNM of SramhaianhlhpNo ratings yet

- BHL Type: Discrepancy SwitchDocument10 pagesBHL Type: Discrepancy Switchinsan_soft6498No ratings yet

- 150 KV Tower Equipment and Accesories For Suspension Type With 2 Circuit LineDocument39 pages150 KV Tower Equipment and Accesories For Suspension Type With 2 Circuit LineCiel Panthomhive100% (2)

- How Digital Cameras WorkDocument17 pagesHow Digital Cameras WorkAnusha DandayNo ratings yet

- 970ff Acer Travelmate 5220 5520 7520 7520g Extensa 5120 5420 Wistron Pomona Texcoco Rev - 1 SCH PDFDocument49 pages970ff Acer Travelmate 5220 5520 7520 7520g Extensa 5120 5420 Wistron Pomona Texcoco Rev - 1 SCH PDFLouis DiasNo ratings yet

- PE Lecture 8 - Ac Ac Converters PDFDocument19 pagesPE Lecture 8 - Ac Ac Converters PDFKhairulNo ratings yet

- Linear CircuitDocument6 pagesLinear CircuitLilySolaimanNo ratings yet

- STM32F0 User ManualDocument41 pagesSTM32F0 User Manualandrestv93No ratings yet

- FCM and FRM Series: Control and Relay Modules With Flashscan®Document4 pagesFCM and FRM Series: Control and Relay Modules With Flashscan®terminatorNo ratings yet

- LogDocument1 pageLogkrows08No ratings yet

- 7.1 The MOSFET - Introduction: 7.1.1 Basic Structure and Principle of OperationDocument4 pages7.1 The MOSFET - Introduction: 7.1.1 Basic Structure and Principle of OperationManoj VatsNo ratings yet

- Emi Lab ManualDocument94 pagesEmi Lab ManualManu anand50% (2)

- 3 Terminal ICDocument33 pages3 Terminal ICDarshan BhansaliNo ratings yet

- Datasheet ls32Document2 pagesDatasheet ls32Alan MontalvoNo ratings yet

- Power SytemsDocument6 pagesPower SytemsAshwin RaghavanNo ratings yet

- MAnual Diodo Zener PDFDocument4 pagesMAnual Diodo Zener PDFferalNo ratings yet

- Noise MCQDocument13 pagesNoise MCQRogelyn barbosaNo ratings yet

- Cadmium Sulfide Enhances Solar Cell EfficiencyDocument5 pagesCadmium Sulfide Enhances Solar Cell EfficiencyAnonymous 0tqzNTWyyNo ratings yet

- Kumpulan Skematik Elektronika 3Document56 pagesKumpulan Skematik Elektronika 3rizal tri susiloNo ratings yet

- Hawkins 1986Document5 pagesHawkins 1986Ben-Hur Ribas MacielNo ratings yet

- Dasar OpampDocument54 pagesDasar OpampMaulana HidayatullahNo ratings yet

- Amada Laser CuttingDocument8 pagesAmada Laser CuttingMahmud MaherNo ratings yet

- Electronics and Instrumentation - 2020Document28 pagesElectronics and Instrumentation - 2020RahulNo ratings yet