Professional Documents

Culture Documents

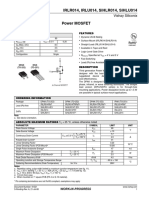

IRS2453 (1) D (S) : Features Product Summary

Uploaded by

Gabriel CalderonOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IRS2453 (1) D (S) : Features Product Summary

Uploaded by

Gabriel CalderonCopyright:

Available Formats

IRS2453(1)D(S)

Features Product Summary

Integrated 600 V full-bridge gate driver Topology Full-bridge

CT, RT programmable oscillator

15.6 V Zener clamp on VCC VOFFSET 600 V

Micropower startup Io+ & I o- (typical) 180 mA & 260 mA

Logic level latched shutdown pin

Non-latched shutdown on CT pin (1/6th VCC) 1.0 μs (IRS2453D)

Deadtime (typical)

Internal bootstrap FETs 0.5 μs (IRS24531D)

Excellent latch immunity on all inputs & outputs

ESD protection on all pins

14-lead SOIC or PDIP package Package Options

0.5 or 1.0μs (typ.) internal dead time

RoHS compliant

14 Lead PDIP 14 Lead SOIC

IRS2453DPbF (Narrow Body)

IRS2453(1)DSPbF

Ordering Information

Standard Pack

Base Part Number Package Type Complete Part Number

Form Quantity

PDIP14 Tube/Bulk 25 IRS2453DPBF

IRS2453D(S) Tube/Bulk 55 IRS2453DSPBF

SOIC14N

Tape and Reel 2500 IRS2453DSTRPBF

Tube/Bulk 55 IRS24531DSPBF

IRS24531DS SOIC14N

Tape and Reel 2500 IRS24531DSTRPBF

1 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Table of Contents Page

Ordering Information 1

Description 3

Typical Connection Diagram 3

Qualification Information 4

Absolute Maximum Ratings 5

Recommended Operating Conditions 6

Recommended Component Values 6

Electrical Characteristics 7

Functional Block Diagram 9

Input / Output Pin Equivalent Circuit Diagram 10

Lead Definitions 11

Lead Assignments 11

Application Information and Additional Details 12

Package Details 15

Tape and Reel Details 16

Part Marking Information 17

2 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Description

The IRS2453(1)D is based on the popular IR2153 self-oscillating half-bridge gate driver IC, and incorporates a

high voltage full-bridge gate driver with a front end oscillator similar to the industry standard CMOS 555 timer.

HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. The output driver

features a high pulse current buffer stage designed for minimum driver cross-conduction. Noise immunity is

achieved with low di/dt peak of the gate drivers, and with an under voltage lockout hysteresis greater than 1.5 V.

The IRS2453(1)D also includes latched and non-latched shutdown pins.

Typical Connection Diagram

+ AC rectified line

15 V

1 VCC VB1 14

IRS2453(1)D

2 COM HO1 13

3 CT VS1 12

4 RT NC 11

5 SD VB2 10

6 LO1 HO2 9

7 LO2 VS2 8

LOAD

- AC rectified line

3 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

†

Qualification Information

††

Industrial

Comments: This family of ICs has passed JEDEC’s

Qualification Level

Industrial qualification. IR’s Consumer qualification level is

granted by extension of the higher Industrial level.

†††

MSL2 260°C

SOIC14

(per IPC/JEDEC J-STD-020)

Moisture Sensitivity Level

Not applicable

PDIP14

(non-surface mount package style)

Class C

Machine Model

(per JEDEC standard JESD22-A115)

ESD

Class 2

Human Body Model

(per EIA/JEDEC standard EIA/JESD22-A114)

Class I, Level A

IC Latch-Up Test

(per JESD78)

RoHS Compliant Yes

† Qualification standards can be found at International Rectifier’s web site http://www.irf.com/

†† Higher qualification ratings may be available should the user have such requirements. Please contact

your International Rectifier sales representative for further information.

††† Higher MSL ratings may be available for the specific package types listed here. Please contact your

International Rectifier sales representative for further information.

4 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage

parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The thermal

resistance and power dissipation ratings are measured under board mounted and still air conditions.

Symbol Definition Min. Max. Units

VB1,

High side floating supply voltage -0.3 625

VB2

VS1,

High side floating supply offset voltage VB - 25 VB + 0.3

VS2

VHO1,

High side floating output voltage VS - 0.3 VB + 0.3

VHO2

VLO1, V

Low side output voltage -0.3 VCC + 0.3

VLO2

VRT RT pin voltage -0.3 VCC + 0.3

VCT CT pin voltage -0.3 VCC + 0.3

VSD SD pin voltage -0.3 VCC + 0.3

IRT RT pin current -5 5

mA

ICC Supply current (†) --- 25

dVS/dt Allowable offset voltage slew rate -50 50 V/ns

PD Maximum power dissipation @ TA≤ +25 ºC, PDIP14 --- 1.6

PD Maximum power dissipation @ TA ≤ +25 ºC, SOIC14N --- 1.0 W

RθJA Thermal resistance, junction to ambient, PDIP14 --- 75

RθJA Thermal resistance, junction to ambient, SOIC14N --- 120 ºC/W

TJ Junction temperature -55 150

TS Storage temperature -55 150 ºC

TL Lead temperature (soldering, 10 seconds) --- 300

† This IC contains a zener clamp structure between the chip VCC and COM which has a nominal

breakdown voltage of 15.6 V. Please note that this supply pin should not be driven by a DC, low

impedance power source greater than the VCLAMP specified in the Electrical Characteristics section.

5 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Recommended Operating Conditions

For proper operation the device should be used within the recommended conditions.

Symbol Definition Min. Max. Units

VBS1,

High side floating supply voltage VCC - 0.7 VCLAMP

VBS2

V

VS1, VS2 Steady state high side floating supply offset voltage -3.0 (†) 600

VCC Supply voltage VCCUV+ VCLAMP

ICC Supply current (††) 5 mA

TJ Junction temperature -25 125 ºC

† It is recommended to avoid output switching conditions where negative-going spikes at the VS node

would decrease VS below ground by more than -5V.

†† Enough current should be supplied to the VCC pin of the IC to keep the internal 15.6 V zener diode

clamping the voltage at this pin.

Recommended Component Values

Symbol Component Min. Max. Units

RT Timing resistor value 1 --- k

CT CT pin capacitor value 330 --- pF

VBIAS (VCC, VBS) = 14 V, VS=0 V and TA = 25 °C, CLO1=CLO2 = CHO1=CHO2 = 1nF.

IRS2453(1)D

IRS2453DFrequency

Frequencyvs.

vs.RT

RT

1000000

CT Values

100000 330pf

Frequency (Hz)

470pF

10000

1nF

2.2nF

1000

4.7nF

10nF

100

10

1000 10000 100000 1000000

RT (Ohm)

6 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Electrical Characteristics

VBIAS (VCC, VBS) = 14 V, CT = 1nF and TA = 25 °C unless otherwise specified. The VO and IO parameters are

referenced to COM and are applicable to the respective output leads:

HO or LO. CLO1=CLO2=CHO1=CHO2=1nF.

Symbol Definition Min Typ Max Units Test Conditions

Low Voltage Supply Characteristics

VCCUV+ Rising VCC under voltage lockout threshold 10.0 11.0 12.0

VCCUV- Falling VCC under voltage lockout threshold 8.0 9.0 10.0 V

VCCUVH VCC under voltage lockout hysteresis 1.5 2.0 2.4

YS

IQCCUV Micropower startup VCC supply current --- 140 200 µA VCC VCCUV-

IQCC Quiescent VCC supply current --- 1.3 2.0

mA

ICC_20K VCC supply current at fosc (RT = 36.5 kΩ) --- 3.0 3.5

ICCFLT VCC supply current when SD > VSD --- 360

360 500 µA

VCLAMP VCC Zener clamp voltage 14.6 15.6 16.6 V ICC = 5 mA

Floating Supply Characteristics

IQBS1UV, VCC VCCUV-

Micropower startup VBS supply current --- 3 10

IQBS2UV , VCC = VBS

µA

IQBS1,

Quiescent VBS supply current --- 30 100

IQBS2

VBS1UV+, VBS supply under voltage positive going

VBS2UV+

8.0 9.0 10.0

threshold

V

VBS1UV-, VBS supply under voltage negative going

VBS2UV-

7.0 8.0 9.0

threshold

ILK1, ILK2 Offset supply leakage current --- --- 50 A VB = VS = 600

V

Oscillator I/O Characteristics

19.6 20.2 20.8 RT = 36.5 k

fOSC Oscillator frequency kHz

88 94 100 RT = 7.15 k

d RT pin duty cycle 48 50 52 % fo < 100 kHz

ICT CT pin current --- 0.05 1.0 A

ICTUV UV-mode CT pin pull down current 1 5 --- mA VCC = 7 V

VCT+ Upper CT ramp voltage threshold --- 9.3 ---

V

VCT- Lower CT ramp voltage threshold --- 4.7 ---

IRT = 100 A

--- 10 50

RT = 140 k

VRT+ High level RT output voltage, VCC - VRT

IRT = 1 mA

--- 100 300

RT = 14 k

mV IRT = 100 A

--- 10 50

RT = 140 k

VRT- Low level RT output voltage

IRT = 1 mA

--- 100 300

RT = 14 k

VRTUV UV-mode RT output voltage --- 0 100 VCC VCCUV-

7 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Electrical Characteristics

VBIAS (VCC, VBS) = 14 V, CT = 1nF and TA = 25 °C, unless otherwise specified. The VO and IO parameters are

referenced to COM and are applicable to the respective output leads:

HO or LO. CLO1=CLO2=CHO1=CHO2=1nF.

Symbol Definition Min Typ Max Units Test Conditions

Gate Driver Output Characteristics

VOH High level output voltage, VBIAS - VO --- VCC ---

IO = 0 A

VOL Low level output voltage, VO --- COM ---

V

IO = 0 A,

VOL_UV UV-mode output voltage, VO --- COM --- VCC

VCCUV-

tr Output rise time --- 120 200

tf Output fall time --- 50 100 ns

tsd Shutdown propagation delay --- 250 ---

IRS2453D 0.8 1.0 1.40

td Output dead time (HO or LO) s

IRS24531D 0.4 0.5 0.7

IO+ Output source current --- 180 ---

mA

IO- Output sink current --- 260 ---

Shutdown

VSD Shutdown threshold at SD pin (latched) 1.8 2.0 2.3

V

VCTSD CT voltage shutdown threshold (non-latched) 2.2 2.3 2.5

IRT = 100 A,

--- 10 50 RT = 140 k

VCT = 0 V

VRTSD SD mode RT output voltage, VCC - VRT mV

IRT = 1 mA,

--- 100 300 RT = 14 k

VCT = 0 V

Bootstrap FET Characteristics

VB1_ON

VB when the bootstrap FET is on 13.7 14.0 --- V

VB2_ON

IB1_CAP

VB source current when FET is on 40 55 --- CBS=0.1 μF

IB2_CAP

mA

IB1_10 V

VB source current when FET is on 10 12 --- VB=10 V

IB2_10 V

8 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Functional Block Diagram

RT 4 14 VB1

R

HV Q

+ Level

PULSE R 13 HO1

- Shift

FILTER S

R

DEAD

R Q PULSE 12 VS1

TIME

GEN

+ BOOTSTRAP

S Q DRIVE

-

R/2

DEAD

TIME DELAY

S Q

+ 6 LO1

R1

CT 3 -

R2 Q

R/2

SD 5 10 VB2

S Q

2.0V

R HV Q

Level R 9 HO2

Shift PULSE

FILTER S

PULSE 8 VS2

GEN

BOOTSTRAP

UV DRIVE

DETECT 1 VCC

15.4V

DELAY

7 LO2

2 COM

9 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Input / Output Pin Equivalent Circuit Diagrams:

VB1

VB2

ESD ESD

Diode Diode

HO1 25V HO2 25V

ESD ESD

Diode Diode

VS1 VS2

600V 600V

VCC VCC

ESD ESD

Diode Diode

LO1 25V LO2 25V

ESD ESD

Diode Diode

COM

COM

VCC VCC

ESD ESD

Diode Diode

SD 25V

RESD

ESD ESD

Diode Diode

COM

VCC

ESD

Diode

CT

RESD

ESD

Diode

COM

10 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Lead Definitions

Pin Symbol Description

1 VCC Logic and internal gate drive supply voltage

2 COM IC power and signal ground

3 CT Oscillator timing capacitor input

4 RT Oscillator timing resistor input

5 SD Shutdown input

6 LO1 Low side gate driver output

7 LO2 Low side gate driver output

8 VS2 High voltage floating supply return

9 HO2 High side gate driver output

10 VB2 High side gate driver floating supply

11 NC No connect

12 VS1 High voltage floating supply return

13 HO1 High side gate driver output

14 VB1 High side gate driver floating supply

Lead Assignment

VCC 1 14 VB1

IRS2453(1)D(S)

COM 2 13 HO1

CT 3 12 VS1

RT 4 11 NC

SD 5 10 VB2

LO1 6 9 HO2

LO2 7 8 VS2

11 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Application Information and Additional Details

Timing Diagram

VCCUV+

VCC

Fault mode

VCT<1/6*VCC

2/3 VCC

1/3 VCC

1/6 VCC

VCC

LO1

VCC

DT

LO2

VCC

HO1 DT

VCC

DT

HO2

VCC

VRT

1mA

IRT

-1mA

12 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Functional Description

Under-Voltage Lock-Out Mode (UVLO)

The under-voltage lockout mode (UVLO) is defined as the state the IC is in when VCC is below the turn-on

threshold of the IC. The IRS2453(1)D under-voltage lock-out is designed to maintain an ultra low supply current of

e the high and low side output drivers are

activated. During under-voltage lock-out mode, the high and low side driver outputs LO1, LO2, HO1, HO2 are all

low. With VCC above the VCCUV+ threshold, the IC turns on and the output begin to oscillate.

Normal Operating Mode

Once VCC reaches the start-up threshold VCCUV+, the MOSFET M1 opens, RT increases to approximately VCC

(VCC-VRT+) and the external CT capacitor starts charging. Once the CT voltage reaches V CT- (about 1/3 of VCC),

established by an internal resistor ladder, LO1 and HO2 turn on with a delay equivalent to the dead time (td).

Once the CT voltage reaches VCT+ (approximately 2/3 of VCC), LO1 and HO2 go low, RT goes down to

approximately ground (VRT-), the CT capacitor starts discharging and the dead time circuit is activated. At the end

of the dead time, LO2 and HO1 go high. Once the CT voltage reaches V CT-, LO2 and HO1 go low, RT goes to

high again, the dead time is activated. At the end of the dead time, LO1 and HO2 go high and the cycle starts

over again.

The frequency is best determined by the graph, Frequency vs. RT, page 3, for different values of CT. A first order

approximate of the oscillator frequency can also be calculated by the following formula:

1

f

1.453 RT CT

This equation can vary slightly from actual measurements due to internal comparator over- and under-shoot

delays.

Bootstrap MOSFET

The internal bootstrap FET and supply capacitor (C BOOT) comprise the supply voltage for the high side driver

circuitry. The internal bootstrap FET only turns on when the corresponding LO is high. To guarantee that the high-

side supply is charged up before the first pulse on HO1 and HO2, LO1 and LO2 outputs are both high when CT

ramps between zero and 1/3*VCC. LO1 and LO2 are also high when CT is grounded below 1/6*VCC to ensure that

the bootstrap capacitor is charged when CT is brought back over 1/3*V CC.

Non-Latched Shutdown

If CT is pulled down below VCTSD (approximately 1/6 of VCC) by an external circuit, CT is not able to charge up

and oscillation stops. HO1 and HO2 outputs are held low. LO1 and LO2 outputs remain high while VCT remains

below VCT- enabling the bootstrap capacitors to charge. This state remains until the CT input is released and

oscillation can resume.

Latched Shutdown

When the SD pin is brought above 2 V, the IC goes into fault mode and all outputs are low. V CC has to be recycled

below VCCUV- to restart. The SD pin can be used for over-current or over-voltage protection using appropriate

external circuitry.

13 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

50%

50%

HO1

td_HO1 td_LO1

LO1

50% 50% ton_LO 50%

Deadtime Waveform

tr tf

90%

HO

LO 10%

Rise and Fall Time Waveform

14 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Package Details

15 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Tape and Reel Details

LOADED TAPE FEED DIRECTION

B A H

F C

NOTE : CONTROLLING

DIM ENSION IN M M E

CARRIER TAPE DIMENSION FOR 14SOICN

Metric Imperial

Code Min Max Min Max

A 7.90 8.10 0.311 0.318

B 3.90 4.10 0.153 0.161

C 15.70 16.30 0.618 0.641

D 7.40 7.60 0.291 0.299

E 6.40 6.60 0.252 0.260

F 9.40 9.60 0.370 0.378

G 1.50 n/a 0.059 n/a

H 1.50 1.60 0.059 0.062

B

C

A

E

REEL DIMENSIONS FOR 14SOICN

Metric Imperial

Code Min Max Min Max

A 329.60 330.25 12.976 13.001

B 20.95 21.45 0.824 0.844

C 12.80 13.20 0.503 0.519

D 1.95 2.45 0.767 0.096

E 98.00 102.00 3.858 4.015

F n/a 22.40 n/a 0.881

G 18.50 21.10 0.728 0.830

H 16.40 18.40 0.645 0.724

16 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

Part Marking Information

Part number IRS2453(1)D

Date code YWW ? IR logo

Pin 1 ? XXXX Lot Code

Identifier

(Prod mode –

4 digit SPN code)

? MARKING CODE

P Lead Free Released

Assembly site code

Non-Lead Free Released Per SCOP 200-002

17 www.irf.com © 2016 International Rectifier April 27, 2016

IRS2453(1)D(S)

The information provided in this document is believed to be accurate and reliable. However, International

Rectifier assumes no responsibility for the consequences of the use of this information. International

Rectifier assumes no responsibility for any infringement of patents or of other rights of third parties which

may result from the use of this information. No license is granted by implication or otherwise under any

patent or patent rights of International Rectifier. The specifications mentioned in this document are subject

to change without notice. This document supersedes and replaces all information previously supplied.

For technical support, please contact IR’s Technical Assistance Center

http://www.irf.com/technical-info/

WORLD HEADQUARTERS:

101N Sepulveda Blvd., El Segundo, California 90245

Tel: (310) 252-7105

18 www.irf.com © 2016 International Rectifier April 27, 2016

You might also like

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Datashee Irs2453tDocument18 pagesDatashee Irs2453tnildo137 SANTOSNo ratings yet

- Infineon IRS44262S DS v01 - 00 ENDocument15 pagesInfineon IRS44262S DS v01 - 00 ENniceautomation8831No ratings yet

- IRS2092 InternationalRectifier PDFDocument17 pagesIRS2092 InternationalRectifier PDFSD BappiNo ratings yet

- VO14642AT, VO14642AABTR 1 Form A Solid-State Relay: Vishay SemiconductorsDocument10 pagesVO14642AT, VO14642AABTR 1 Form A Solid-State Relay: Vishay SemiconductorsHari KiranNo ratings yet

- bd621x eDocument23 pagesbd621x eAdrienny CristinneNo ratings yet

- CBAT54Document3 pagesCBAT54SatriaWahyuEkaSaputraNo ratings yet

- Pci Express™ Clock Generator: ICS841S01Document16 pagesPci Express™ Clock Generator: ICS841S01Venoninho EtstuemeNo ratings yet

- LM324, LM324A, LM324E, LM224, LM2902, LM2902E, LM2902V, NCV2902 Operational Amplifiers, Single Supply, QuadDocument17 pagesLM324, LM324A, LM324E, LM224, LM2902, LM2902E, LM2902V, NCV2902 Operational Amplifiers, Single Supply, QuadpissoNo ratings yet

- LM324, LM324A, LM324E, LM224, LM2902, LM2902E, LM2902V, NCV2902 Operational Amplifiers, Single Supply, QuadDocument18 pagesLM324, LM324A, LM324E, LM224, LM2902, LM2902E, LM2902V, NCV2902 Operational Amplifiers, Single Supply, QuadwinoNo ratings yet

- MC33201 D 1773745 PDFDocument18 pagesMC33201 D 1773745 PDFPepit PistoleroNo ratings yet

- BUK7J1R4-40H: 1. General DescriptionDocument12 pagesBUK7J1R4-40H: 1. General DescriptioncqlNo ratings yet

- Irs 2092Document18 pagesIrs 2092Hernan Ortiz EnamoradoNo ratings yet

- Icm7555 56Document13 pagesIcm7555 56she rifNo ratings yet

- Irs 2453 DDocument18 pagesIrs 2453 DMallickarjunaNo ratings yet

- MC33201, MC33202, MC33204, NCV33202, NCV33204 Low Voltage, Rail-to-Rail Operational AmplifiersDocument18 pagesMC33201, MC33202, MC33204, NCV33202, NCV33204 Low Voltage, Rail-to-Rail Operational AmplifiersAdam SchwemleinNo ratings yet

- Bro Avag - HCPL 314jDocument14 pagesBro Avag - HCPL 314jRomusNo ratings yet

- MC33201, MC33202, MC33204, NCV33202, NCV33204 Low Voltage, Rail To Rail Operational AmplifiersDocument16 pagesMC33201, MC33202, MC33204, NCV33202, NCV33204 Low Voltage, Rail To Rail Operational AmplifiersAndres OrtizNo ratings yet

- Tda7265 (30W+30W)Document18 pagesTda7265 (30W+30W)ShiguMiku TheyNo ratings yet

- 3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD ProtectionDocument28 pages3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD ProtectioncafosokNo ratings yet

- MC14008B DDocument8 pagesMC14008B DAngela SilesNo ratings yet

- Features Product Summary: Led Buck Regulator Control IcDocument20 pagesFeatures Product Summary: Led Buck Regulator Control IcJess AJNo ratings yet

- PZTA42T1G High Voltage Transistor Surface Mount: NPN SiliconDocument7 pagesPZTA42T1G High Voltage Transistor Surface Mount: NPN SiliconYessica PerezNo ratings yet

- PZTA42T1G High Voltage Transistor Surface Mount: NPN SiliconDocument4 pagesPZTA42T1G High Voltage Transistor Surface Mount: NPN SiliconAhmed Sherif CupoNo ratings yet

- Tda 8024Document29 pagesTda 8024ВалераNo ratings yet

- Transistor 2021 Pag 3Document6 pagesTransistor 2021 Pag 3StuxnetNo ratings yet

- Hcf4069u PDFDocument11 pagesHcf4069u PDFNanang Roni WibowoNo ratings yet

- U2270B TEMICSemiconductorsDocument13 pagesU2270B TEMICSemiconductorsВячеслав ГлушакNo ratings yet

- IRS2980S: Led Driver Control Ic IC Features Product SummaryDocument15 pagesIRS2980S: Led Driver Control Ic IC Features Product SummaryElectronica Libra LibraNo ratings yet

- Stfw4N150 Stp4N150, Stw4N150: N-Channel 1500 V, 5, 4 A, Powermesh™ Power Mosfet in To-220, To-247, To-3PfDocument15 pagesStfw4N150 Stp4N150, Stw4N150: N-Channel 1500 V, 5, 4 A, Powermesh™ Power Mosfet in To-220, To-247, To-3PfSidhi SadanNo ratings yet

- Mosfet Potencia Sihlr014Document8 pagesMosfet Potencia Sihlr014Jorge Martinez PerezNo ratings yet

- TLC 1514Document40 pagesTLC 1514Hoii ClarkNo ratings yet

- 7-Channel Integrated Esd Solution For Vga Port With Integrated Level Shifter and Matching ImpedanceDocument12 pages7-Channel Integrated Esd Solution For Vga Port With Integrated Level Shifter and Matching Impedanceeisservices17No ratings yet

- An 17821A PanasonicDocument6 pagesAn 17821A PanasonicedlajaresNo ratings yet

- Safa Micro hw-1Document30 pagesSafa Micro hw-1suhailhajajjiNo ratings yet

- OC-12 SFP Transceiver Spec SheetDocument12 pagesOC-12 SFP Transceiver Spec Sheetehidalgo23No ratings yet

- High and Low Side Driver: Features Product SummaryDocument27 pagesHigh and Low Side Driver: Features Product SummaryFernando SotoNo ratings yet

- Automotive ISO 9141 Serial Link Driver: Technical DataDocument18 pagesAutomotive ISO 9141 Serial Link Driver: Technical DataP GlNo ratings yet

- DIR1703Document19 pagesDIR1703Anh NgôNo ratings yet

- Half-Bridge Driver: Features Product SummaryDocument18 pagesHalf-Bridge Driver: Features Product SummaryPE TruNo ratings yet

- Cat25020vi-G Cat25010vi-Gt3 Cat25040vi-Gt3 Cat25040vp2i-Gt3 Cat25010hu4i - GT3Document18 pagesCat25020vi-G Cat25010vi-Gt3 Cat25040vi-Gt3 Cat25040vp2i-Gt3 Cat25010hu4i - GT3Mikael LipeNo ratings yet

- ISO Serial Link Interface OrderDocument4 pagesISO Serial Link Interface Orderwramadhani65No ratings yet

- BCD Counter Chip Provides 3-Digit DisplayDocument9 pagesBCD Counter Chip Provides 3-Digit DisplayoscarNo ratings yet

- TLE7209 R InfineonDocument16 pagesTLE7209 R Infineonmobil benerNo ratings yet

- Relay Terminal Block - Rockwell Automation AB - CATALOGUEDocument13 pagesRelay Terminal Block - Rockwell Automation AB - CATALOGUEtheloniussherekNo ratings yet

- Opa365 Q11Document22 pagesOpa365 Q11Victor HernandezNo ratings yet

- Features Product Summary: Class D Audio DriverDocument16 pagesFeatures Product Summary: Class D Audio DriverbillNo ratings yet

- AL422B AverlogicTechnologiesDocument20 pagesAL422B AverlogicTechnologiescesareletNo ratings yet

- 08 Q 0 J 1 D 722 GDD 15 Joihjg 1 CiwscyDocument11 pages08 Q 0 J 1 D 722 GDD 15 Joihjg 1 Ciwscy11031974didinNo ratings yet

- Pesd5V0V1Ba Pesd5V0V1Bb Pesd5V0V1Bl: 1. Product ProfileDocument13 pagesPesd5V0V1Ba Pesd5V0V1Bb Pesd5V0V1Bl: 1. Product Profilezigmund zigmundNo ratings yet

- Terminal Block Relay Product Overview and Selection GuideDocument4 pagesTerminal Block Relay Product Overview and Selection GuideManuel Silva PainenNo ratings yet

- SN 74 Alvch 16374Document18 pagesSN 74 Alvch 16374SuBaRu GTNo ratings yet

- HCF 4013Document13 pagesHCF 4013Deepa SonaniaNo ratings yet

- 111Db 192Khz 24-Bit 2ChDocument26 pages111Db 192Khz 24-Bit 2ChPaulo Roberto s freireNo ratings yet

- PSMN1R4-40YLD: 1. General DescriptionDocument13 pagesPSMN1R4-40YLD: 1. General DescriptionLuis MarquezNo ratings yet

- Single Supply Quad Operational Amplifiers LM324, LM324A, LM324E, LM224, LM2902, LM2902E, LM2902V, NCV2902Document17 pagesSingle Supply Quad Operational Amplifiers LM324, LM324A, LM324E, LM224, LM2902, LM2902E, LM2902V, NCV2902fosavo5839No ratings yet

- Infineon IRS2153D DataSheet v01 - 00 EN PDFDocument14 pagesInfineon IRS2153D DataSheet v01 - 00 EN PDFuzenhoNo ratings yet

- Datasheet Digital 74hcDocument33 pagesDatasheet Digital 74hcСтанислав ИвановNo ratings yet

- 25 LC 1024Document28 pages25 LC 1024hyd27No ratings yet

- 1SS400T1G, NSV1SS400T1G High-Speed Switching Diode: FeaturesDocument3 pages1SS400T1G, NSV1SS400T1G High-Speed Switching Diode: FeaturesManu MathewNo ratings yet

- Fanless TL Technology Integrates AFCI and Meets NEC 2011Document2 pagesFanless TL Technology Integrates AFCI and Meets NEC 2011Gabriel CalderonNo ratings yet

- Catalogue: The Manual Is Subject To Change Without NoticeDocument31 pagesCatalogue: The Manual Is Subject To Change Without NoticeGabriel Calderon100% (1)

- Micrometal CatalogDocument72 pagesMicrometal Catalogdinu petreNo ratings yet

- Fire Sentry FS24X Flame DetectorsDocument4 pagesFire Sentry FS24X Flame DetectorsGabriel CalderonNo ratings yet

- Mazda Engine BP B6 Workshop Manual PDFDocument100 pagesMazda Engine BP B6 Workshop Manual PDFGabriel CalderonNo ratings yet

- 8kW 48V Pure Sine Wave Inverter User ManualDocument39 pages8kW 48V Pure Sine Wave Inverter User ManualGabriel CalderonNo ratings yet

- TRAXALL 700 SERIES USER MANUAL - 25 Mar 2016 - EmailDocument76 pagesTRAXALL 700 SERIES USER MANUAL - 25 Mar 2016 - EmailGabriel CalderonNo ratings yet

- PHD36N03LT: 1. Product ProfileDocument13 pagesPHD36N03LT: 1. Product ProfileGabriel CalderonNo ratings yet

- MITOCHONDRIA AS A BIOLOGICAL CELL CAPACITORDocument150 pagesMITOCHONDRIA AS A BIOLOGICAL CELL CAPACITORBhargavNo ratings yet

- Edc - Lab Manual by MadhuDocument101 pagesEdc - Lab Manual by Madhu224g1a0405No ratings yet

- SC1403 Data SheetDocument30 pagesSC1403 Data Sheetnomi_nomiNo ratings yet

- JAC Class 12 Physics Model Question 2020Document5 pagesJAC Class 12 Physics Model Question 2020Ashmit KumarNo ratings yet

- Dytran Documentation TheoryDocument35 pagesDytran Documentation TheoryGeorges KouroussisNo ratings yet

- Crystal Tester Frequency CounterDocument10 pagesCrystal Tester Frequency CounterLeonardo OuverneyNo ratings yet

- IGBT's Application Note EngDocument38 pagesIGBT's Application Note Engospidera100% (1)

- Project ReportDocument50 pagesProject ReportNaziya KosarNo ratings yet

- M3 Complete Questions Final NewDocument24 pagesM3 Complete Questions Final NewUlugh BaigNo ratings yet

- Green Life Charge: Kota KinabaluDocument29 pagesGreen Life Charge: Kota KinabaluAmirul NaimNo ratings yet

- Data SheetDocument40 pagesData SheetMohamed YuosefNo ratings yet

- Compiled Board Exam Electric Power System II KeyDocument14 pagesCompiled Board Exam Electric Power System II Keyshaito100% (1)

- AC CIRCUIT RESONANCE AND QUALITY FACTORDocument5 pagesAC CIRCUIT RESONANCE AND QUALITY FACTORRSNo ratings yet

- Oec 7600 Service Manual Руководство По ОбслуживаниюDocument110 pagesOec 7600 Service Manual Руководство По ОбслуживаниюJuriyNo ratings yet

- A Transient Performance Analysis For Vector Controlled Z-Source Inverter Fed Induction Motor DriveDocument7 pagesA Transient Performance Analysis For Vector Controlled Z-Source Inverter Fed Induction Motor DriveInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Ams 1117Document5 pagesAms 1117Sebastian BryceNo ratings yet

- SafeRing SafePlus 12-24kV May 2013 EnglishDocument88 pagesSafeRing SafePlus 12-24kV May 2013 EnglishDubravko100% (1)

- Minisilk FT: Service ManualDocument92 pagesMinisilk FT: Service ManualQuasar Laser Services, LLC.No ratings yet

- Is 14658Document62 pagesIs 14658Vinay Kumar KsNo ratings yet

- Practice Usapho E: Kevin ZhouDocument5 pagesPractice Usapho E: Kevin ZhouRandomNo ratings yet

- Power Lab Manual 7th Sem 2011 - BGSDocument109 pagesPower Lab Manual 7th Sem 2011 - BGSSumanth Sathyanarayana100% (1)

- User Manual: YX2000/3000/3300 Sensorless Vector TypeDocument172 pagesUser Manual: YX2000/3000/3300 Sensorless Vector TypeAlex VargasNo ratings yet

- LEP WebDocument244 pagesLEP WebCristhoper MeraNo ratings yet

- GEN PHY Module 3Document6 pagesGEN PHY Module 3Joshua James Sanguenza RodriguezNo ratings yet

- Prashant Tutorials: MM-64. Physics Chap 1 & 2 Time1h.30min Electric Charges and Fields Class 12 Physics McqsDocument29 pagesPrashant Tutorials: MM-64. Physics Chap 1 & 2 Time1h.30min Electric Charges and Fields Class 12 Physics McqsRitika SinghNo ratings yet

- 1.6X Linear Fan Driver with VO Fully On ControlDocument8 pages1.6X Linear Fan Driver with VO Fully On ControlRahmat YuditaNo ratings yet

- Linear IC Lab ExperimentsDocument102 pagesLinear IC Lab ExperimentsUdhayakumar SelvarajNo ratings yet

- Effects of system elements on shaft voltages and bearing currentsDocument8 pagesEffects of system elements on shaft voltages and bearing currentshamidrezaNo ratings yet

- Magnetron GeneratorDocument3 pagesMagnetron GeneratorChristopher PartingtonNo ratings yet

- Page b49 - Matsushita - PanasonicDocument1 pagePage b49 - Matsushita - PanasonicOmar OlivaresNo ratings yet