Professional Documents

Culture Documents

AL422B AverlogicTechnologies

Uploaded by

cesareletOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

AL422B AverlogicTechnologies

Uploaded by

cesareletCopyright:

Available Formats

AL422B

3M-Bits FIFO Field Memory

Datasheets

Version 1.5

© 1999~2006 by AverLogic Technologies, Corp

Doc Number: 1-D-PMK222-0001

AL422B

Amendments (Since April 2, 1999)

05-13-99 DC/AC characteristics (including current consumption) updated.

07-02-99 Pinout diagram (5.0) and DC external load (7.4) modified.

08-03-99 Description about TST pin added in sections 6.0 & 8.1.

09-02-99 8.3.2 Rewritten.

10-26-99 Capacitance provided in the AC characteristics section.

12-15-99 Remove TST pin restriction.

01-18-01 1. Revised section “8.3.2 Read Enable during Reset Cycles” to “8.3.2 The Proper

Manipulation of FIFO Access”.

2. Add section “8.3.3 Single Field Write with Multiple Read Operation”

3. Add section “8.3.4 One Field Delay Line (The Old Data Read)”

02-28-02 Address and version update

03-20-02 Correct Pin-out diagram

02-20-03 Company Contact Information updated

04-27-04 1. Revised “5V or 3.3V power supply” in section “2.0 Features”

2. Revised “+5V/+3.3 volt” in section “4.0 Ordering Information”

3. Revised “5V or 3.3V” in section “6.0 Pin Description”

4. Revised section “7.0 Electrical Characteristics”

5. Revised section “8.2 5V and 3.3V application”

05-11-04 Include PB-free package “AL422B-PBF”

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 2

AL422

AL422B 3M-Bits FIFO Field Memory

Contents:

1.0 Description _________________________________________________________________ 4

2.0 Features____________________________________________________________________ 4

3.0 A pplications ________________________________________________________________ 4

4.0 Ordering Information _________________________________________________________ 4

5.0 Pinout Diagram _____________________________________________________________ 5

6.0 Pin Description ______________________________________________________________ 6

7.0 Electrical Characteristics______________________________________________________ 6

7.1 Absolute Maximum Ratings ________________________________ __________________ 6

7.2 Recommended Operating Conditions___________________________________________ 7

7.3 DC Characteristics _________________________________________________________ 7

7.4 AC Characteristics _________________________________________________________ 7

7.5 Timing Diagrams __________________________________________________________ 10

8.0 Functional Description ______________________________________________________ 14

8.1 Memory Operation ________________________________________________________ 15

8.2 5V and 3.3V applications ____________________________________________________ 16

8.3 Restrictions ______________________________________________________________ 17

8.3.1 Irregular Read/Write _________________________________________________________________ 17

8.3.2 Read Enable during Reset Cycles _______________________________________________________ 18

9.0 Mechanical Drawing ________________________________________________________ 19

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 3

AL422

1.0 Description

The AL422 consists of 3M-bits of DRAM, and is configured as 393,216 words x 8 bit FIFO (first in first

out). The interface is very user-friendly since all complicated DRAM operations are already managed by

the internal DRAM controller.

Current sources of similar memory (field memory) in the market provide limited memory size which is only

enough for holding one TV field, but not enough to hold a whole PC video frame which normally contains

640x480 or 720x480 bytes. The AverLogic AL422 provides 50% more memory to support high

resolution for digital PC graphics or video applications. The 50% increase in speed also expands the range

of applications.

• Multimedia systems

2.0 Features • Video capture systems

• Video editing systems

• 384K (393,216) x 8 bits FIFO organization • Scan rate converters

• Support VGA, CCIR, NTSC, PAL and • TV’s picture in picture feature

HDTV resolutions • Time base correction (TBC)

• Independent read/write operations (different • Frame synchronizer

I/O data rates acceptable) • Digital video camera

• High speed asynchronous serial access • Buffer for communications systems

• Read/write cycle time: 20ns

• Access time: 15ns

• Output enable control (data skipping)

• Self refresh

• 5V or 3.3V power supply

• Standard 28-pin SOP package

3.0 Applications

4.0 Ordering Information

Part number Package Power Supply Status

AL422B 28-pin plastic SOP +5/+3.3 volt Shipping

AL422B-PBF 28-pin plastic SOP +5/+3.3 volt Shipping

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 4

AL422

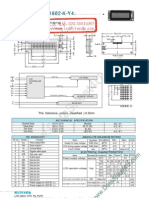

5.0 Pinout Diagram

DO0 DO1 DO2 DO3 /RE GND /OE /RRST RCK DEC DO4 DO5 DO6 DO7

28 27 26 25 24 23 22 21 20 19 18 17 16 15

AVERLOGIC

AL422B

XXXXX Lot Number

XXXX Date Code

1 2 3 4 5 6 7 8 9 10 11 12 13 14

DI0 DI1 DI2 DI3 /WE GND TST /WRST WCK VDD DI4 DI5 DI6 DI7

AL422-04 422B pinout diagram

DO0 DO1 DO2 DO3 /RE GND /OE /RRST RCK DEC DO4 DO5 DO6 DO7

28 27 26 25 24 23 22 21 20 19 18 17 16 15

AVERLOGIC

AL422B

XXXXX Lot Number

XXXX Date Code

1 2 3 4 5 6 7 8 9 10 11 12 13 14

DI0 DI1 DI2 DI3 /WE GND TST /WRST WCK VDD DI4 DI5 DI6 DI7

AL422B-PBF pinout diagram

Note: “PBF” to indicate it is Pb free package.

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 5

AL422

6.0 Pin Description

Pin name Pin # I/O type Function

DI0~DI7 1~4, 11~14 input Data input

WCK 9 Input Write clock

/WE 5 Input (active low) Write enable

/WRST 8 Input (active low) Write reset

DO0~DO7 15~18, 25~28 Output (tristate) Data output

RCK 20 Input Read clock

/RE 24 Input (active low) Read enable

/RRST 21 Input (active low) Read reset

/OE 22 Input (active low) Output enable

TST 7 Input Test pin (pulled-down)*

VDD 10 5V or 3.3V

DEC/VDD 19 Decoupling cap input

GND 6, 23 Ground

7.0 Electrical Characteristics

7.1 Absolute Maximum Ratings

Ratings

Parameter Unit

3.3V application 5V application

V DD Supply Voltage -1.0 ~ +4.5 -1.0 ~ +7.0 V

VP Pin Voltage -1.0 ~ +5.5 -1.0 ~ VDD +0.5 V

IO Output Current -20 ~ +20 -20 ~ +20 mA

TAMB Ambient Op. Temperature 0 ~ +70 0 ~ +70 °C

Tstg Storage temperature -55 ~ +125 -55 ~ +125 °C

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 6

AL422

7.2 Recommended Operating Conditions

3.3V application 5V application

Parameter Unit

Min Max Min Max

V DD Supply Voltage +3.0 +3.6 +4.5 +5.25 V

V IH High Level Input Voltage +2.0 +5.5 +3.0 V DD +0.5 V

V IL Low Level Input Voltage -1.0 +0.8 -1.0 +0.8 V

7.3 DC Characteristics

(V DD =5V or 3.3V, Vss=0V. TAMB = 0 to 70°C)

3.3V application 5V application

Parameter Unit

Min Typ Max Min Typ Max

IDD Operating Current @20MHz - 33 - - 50 - mA

IDD Operating Current @30MHz - 45 - - 66 - mA

IDD Operating Current @40MHz - 57 - - 82 - mA

IDD Operating Current @50MHz - 68 - - 97 - mA

IDDS Standby Current - 7 - - 12 - mA

V OH Hi-level Output Voltage 0.7V DD - V DD +3.0 - V DD V

V OL Lo-level Output Voltage - - +0.4 - - +0.4 V

ILI Input Leakage Current -10 - +10 -10 - +10 µA

ILO Output Leakage Current -10 - +10 -10 - +10 µA

7.4 AC Characteristics

(V DD =5V or 3.3V, Vss=0V, TAMB = 0 to 70°C)

3.3V application 5V application

Parameter Unit

Min Max Min Max

TWC WCK Cycle Time 20 1000 20 1000 ns

TWPH WCK High Pulse Width 7 - 7 - ns

TWPL WCK Low Pulse Width 7 - 7 - ns

TRC RCK Cycle Time 20 1000 20 1000 ns

TRPH RCK High Pulse Width 7 - 7 - ns

TRPL RCK Low Pulse Width 7 - 7 - ns

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 7

AL422

TAC Access Time - 15 - 15 ns

TOH Output Hold Time 4 - 4 - ns

THZ Output High-Z Setup Time 3 15 4 15 ns

TLZ Output Low-Z Setup Time 3 15 4 15 ns

TWRS /WRST Setup Time 5 - 6 - ns

TWRH /WRST Hold Time 2 - 3 - ns

TRRS /RRST Setup Time 5 - 6 - ns

TRRH /RRST Hold Time 2 - 3 - ns

TDS Input Data Setup Time 5 - 6 - ns

TDH Input Data Hold Time 2 - 3 - ns

TWES /WE Setup Time 5 - 6 - ns

TWEH /WE Hold Time 2 - 3 - ns

TWPW /WE Pulse Width 10 - 10 - ns

TRES /RE Setup Time 5 - 6 - ns

TREH /RE Hold Time 2 - 3 - ns

TRPW /RE Pulse Width 10 - 10 - ns

TOES /OE Setup Time 5 - 6 - ns

TOEH /OE Hold Time 2 - 3 - ns

TOPW /OE Pulse Width 10 - 10 - ns

TTR Transition Time 2 20 3 20 ns

CI Input Capacitance - 7 - 7 pF

CO Output Capacitance - 7 - 7 pF

• Input voltage levels are defined as VIH=3.0V and VIL=0.4V.

• The read address needs to be at least 128 cycles after the write address.

DO external load:

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 8

AL422

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 9

AL422

7.5 Timing Diagrams

Reset

cycle n cycle 0 cycle 1

cycle (s)

WCK

TT R

TWRS T WRH

/WRST

T DS T DH

DI7~0 n-1 n 0 1

AL422-05 Write Cycle Timing (Write Reset)

Reset

cycle n cycle 0 cycle 1

cycle (s)

T RPL

RCK

TRPH

TRRS TRRH

/RRST

T AC

TOH

DO7~0 n-1 n 0 0 1

AL422-07 Read Cycle Timing (Read Reset)

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 10

AL422

cycle n cycle n+1 Disable cycle (s) cycle n+2

TRPL

RCK

TRPH

T RC TRES TREH

/RE

TRPW

TAC

TOH

DO7~0 n-1 n n+1 n+2

AL422-08 Read Cycle Timing (Read Enable)

cycle n cycle n+1 cycle n+2 cycle n+3 cycle n+4

TRPL

RCK

TRPH

T RC TOES TOEH

/OE

TOPW

TAC

TOH T HZ TLZ

Hi-Z

DO7~0 n-1 n n+1 n+4

AL422-09 Read Cycle Timing (Output Enable)

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 11

AL422

cycle n cycle n+1 Disable cycle (s) cycle n+2

TW P L

WCK

TW P H

TW C TWES TWEH

/WE

TW P W

TDS TDH

DI7~0 n-1 n n+1 n+2

AL422-06 Write Cycle Timing (Write Enable)

cycle n cycle n+1 Disable cycle (s) cycle 0

TRPL

RCK

TRPH

T RC

TRRS T RRH

/RRST

T RES T REH

/RE

TRPW

T AC

TO H

DO7~0 n-1 n n+1 0

AL422-14 Read Cycle Timing (RE, RRST)

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 12

AL422

cycle n cycle n+1 Disable cycle (s) cycle 0 cycle 1

T WPL

WCK

T WPH

TW C TWRS T WRH

/WRST

TWES TWEH

/WE

TW P W

T DS T DH

DI7~0 n-1 n n+1 0 1

AL422-15 Write Cycle Timing (WE, WRST)

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 13

AL422

8.0 Functional Description

The AL422 is a video frame buffer consisting of DRAM that works like a FIFO which is long enough to

hold up to 819x480 bytes of picture information and fast enough to operate at 50MHz. The functional block

diagram is as follows:

Write 384k x8 Read

DI7~ Input Output DO7~

Data Memory Cell Data

DI0 Buffer Buffer DO0

Register Array Register

/OE

WCK RCK

Write Read

Timing Generator

/WRST Address Address /RRST

& Arbiter

Counter Counter

/WE /RE

Refresh Address

Counter AL422-03 Block Diagram

The I/O pinouts and functions are described as follows:

DI7~DI0 Data Input: Data is input on the rising edge of the cycle of WCK when /WE is pulled low

(enabled).

DO7~DO0 Data Output: Data output is synchronized with the RCK clock. Data is obtained at the rising

edge of the RCK clock when /RE is pulled low. The access time is defined from the rising edge of the RCK

cycle.

WCK Write Clock Input: The write data input is synchronized with this clock. Write data is input at the

rising edge of the WCK cycle when /WE is pulled low (enabled). The internal write address pointer is

incremented automatically with this clock input.

RCK Read Clock Input: The read data output is synchronized with this clock. Read data output at the

rising edge of the RCK cycle when /OE is pulled low (enabled). The internal read address pointer is

incremented with this clock input.

/WE Write Enable Input: /WE controls the enabling/disabling of the data input. When /WE is pulled low,

input data is acquired at the rising edge of the WCK cycle. When /WE is pulled high, the memory does not

accept data input. The write address pointer is stopped at the current position. /WE signal is fetched at the

rising edge of the WCK cycle.

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 14

AL422

/RE Read Enable Input: /RE controls the operation of the data output. When /RE is pulled low, output

data is provided at the rising edge of the RCK cycle and the internal read address is incremented

automatically. /RE signal is fetched at the rising edge of the RCK cycle.

/OE Output Enable Input: /OE controls the enabling/disabling of the data output. When /OE is pulled low,

output data is provided at the rising edge of the RCK cycle. When /OE is pulled high, data output is

disabled and the output pins remain at high impedance status. /OE signal is fetched at the rising edge of

RCK cycle.

/WRST Write Reset Input: This reset signal initializes the write address to 0, and is fetched at the rising

edge of the WCK input cycle.

/RRST Write Reset Input: This reset signal initializes the read address to 0, and is fetched at the rising

edge of the RCK input cycle.

TST Test Pin: For testing purpose only. It should be pulled low for normal applications.

DEC: Decoupling cap pin, should be connected to a 1µF or 2.2µF capacitor to ground for 5V application.

For 3.3V application, the DEC pin can be simply connected to the 3.3V power with regular 0.1µF bypass

capacitor.

8.1 Memory Operation

Initialization

Apply /WRST and /RRST 0.1ms after power on, then follow the following instructions for normal operation.

Reset Operation

The reset signal can be given at any time regardless of the /WE, /RE and /OE status, however, they still need

to meet the setup time and hold time requirements with reference to the clock input. When the reset signal is

provided during disabled cycles, the reset operation is not executed until cycles are enabled again. After

WRST and RRST signals are pulled low, the data output and input start from address 0.

Write Operation

Data input DI7~DI0 is written into the write register at the WCK input when /WE is pulled low. The write

data should meet the setup time and hold time requirements with reference to the WCK input cycle.

Write operation is prohibited when /WE is pulled high, and the write address pointer is stopped at the

current position. The write address starts from there when the /WE is pulled low again. The /WE signal

needs to meet the setup time and hold time requirements with reference to the WCK input cycle.

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 15

AL422

Read Operation

Data output DO7~DO0 is written into the read register at the RCK input when both /RE and /OE are pulled

low. The output data is ready after TAC (access time) from the rising edge of the RCK input cycle.

The read address pointer is stopped at the current position when /RE is pulled high, and starts there when

/RE is pulled low again.

/OE needs to be pulled low for read operations. When /OE is pulled high, the data outputs will be at high

impedance stage. The read address pointer still increases synchronously with RCK regardless of the /OE

status. The /RE and /OE signals need to meet the setup time and hold time requirements with reference to

the RCK input cycle.

When the new data is read, the read address should be between 128 to 393,247 cycles after the write

address, otherwise the output may not be new data.

8.2 5V and 3.3V applications

The AL422 can accept either 3.3V or 5V power with slightly different external configuration. The internal

voltage regulator can convert 5V power to 3.3V for the embedded DRAM and logic circuitry when 5V

power is applied to VDD pin (#10) only and leave the DEC pin (#19) decoup led by a capacitor of 1µF or

2.2µF to ground. The regulator can also be bypassed when 3.3V power is applied to both VDD and DEC

pins. In either case the AL422 is 5V or 3.3V I/O tolerant. The 3.3V configuration consumes less power

and is free from noise interference from the voltage regulator so may be more ideal for high-speed

applications.

Please note that using the AL422B with 5V configuration can directly replace the previous AL422V5; using

it with 3.3V configuration can directly replace the previous AL422V3. No additional modification is

required.

The 5V configuration (direct replacement of the previous AL422V5) is as follows:

5V

AL422B

VDD DEC

0.1uF 2.2uF

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 16

AL422

The 3.3V configuration (direct replacement of the previous AL422V3) is as follows:

3.3V 3.3V

AL422B

10 19

VDD DEC

0.1uF 0.1uF

8.3 Restrictions

8.3.1 Irregular Read/Write

It is recommended that the WCK and RCK are kept running at least 1MHz at all times. The faster one of

WCK and RCK is used as the DRAM refresh timing clock and has to be kept free running. When irregular

FIFO I/O control is needed, keep the clock free running and use /WE or /RE to control the I/O as follows:

WCK

Data

/WE

AL422-17 Slow Write - Correct

The following drawing shows irregular clock and should be avoided:

WCK

Data

/WE

AL422-16 Slow Write - Incorrect

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 17

AL422

8.3.2 Read Enable during Reset Cycles

/RE should never be low at the rising edge of /RRST. The following cases are acceptable:

/RRST

/RE

These cases are ok

The following cases should always be avoided:

/RRST

/RE

These cases are not ok

Please use the drawing AL422-14, Read Cycle Timing (RE, RRST) as enable/reset timing reference.

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 18

AL422

9.0 Mechanical Drawing

28 PIN PLASTIC SOP:

© 1999~2006 by AverLogic Technologies, Corp. Version 1.5 19

CONTACT INFORMATION

Averlogic Technologies, Corp.

E-mail: sales@averlogic.com.tw

URL: http://www.averlogic.com.tw

Averlogic Technologies, Inc.

E-mail: sales_usa@averlogic.com

URL: http://www.averlogic.com

You might also like

- AL422B Data SheetsDocument20 pagesAL422B Data SheetsjuenkkinNo ratings yet

- Philips CH - Qfu1.1e LaDocument227 pagesPhilips CH - Qfu1.1e Lanikola166083% (6)

- HD-R507T (A) Specification V0.1Document6 pagesHD-R507T (A) Specification V0.1DitzNo ratings yet

- Gigabyte Ga Ma770-Ds3 V1.0.Document39 pagesGigabyte Ga Ma770-Ds3 V1.0.David J. Pinto ApazaNo ratings yet

- Dip5k Enin A22Document38 pagesDip5k Enin A22Edyson91No ratings yet

- Data Sheet: VT8237R South BridgeDocument181 pagesData Sheet: VT8237R South BridgeFranklin JimenezNo ratings yet

- PCL1602 KDocument1 pagePCL1602 KEmmanuel Díaz DzulNo ratings yet

- SigmaLogic7 Compact HW ManualDocument46 pagesSigmaLogic7 Compact HW ManualAdamNo ratings yet

- Datashee Irs2453tDocument18 pagesDatashee Irs2453tnildo137 SANTOSNo ratings yet

- The Tolerance Unless Classified 0.3mm: Outline Dimension & Block DiagramDocument1 pageThe Tolerance Unless Classified 0.3mm: Outline Dimension & Block DiagramMatthias GoubertNo ratings yet

- AL440B AverlogicTechnologiesDocument35 pagesAL440B AverlogicTechnologies陳宜松No ratings yet

- Atmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetDocument20 pagesAtmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetalaitsevNo ratings yet

- 1.54inch E-Paper DatasheetDocument25 pages1.54inch E-Paper Datasheetardhya dwiNo ratings yet

- 25 LC 1024Document28 pages25 LC 1024hyd27No ratings yet

- Sigma 8-Channel Programmable Interface Jun1983Document26 pagesSigma 8-Channel Programmable Interface Jun1983Ashish SinghNo ratings yet

- AT24C1024B - DatasheetDocument25 pagesAT24C1024B - DatasheetEngin UzunNo ratings yet

- StreamCaster 4400 OEM Integration Manual v1.0Document9 pagesStreamCaster 4400 OEM Integration Manual v1.0236251457.hcNo ratings yet

- PHILIPS Chassis QV14.1E LA PDFDocument301 pagesPHILIPS Chassis QV14.1E LA PDFboroda241082% (11)

- Cat25128 DDocument18 pagesCat25128 Dalvinmpayikulu08No ratings yet

- Gigabyte Ga-78lmt-S2p Rev.5.11Document27 pagesGigabyte Ga-78lmt-S2p Rev.5.11Anth BeCaNo ratings yet

- HV320WX2-176-BOE LCD PanelDocument23 pagesHV320WX2-176-BOE LCD PanelEdwin OndoyNo ratings yet

- IN44780U Dot Matrix Liquid Crystal Display Controller & DriverDocument10 pagesIN44780U Dot Matrix Liquid Crystal Display Controller & DriverSilviu AdgjNo ratings yet

- CAT 28256 - EepromDocument20 pagesCAT 28256 - EepromTiago LeonhardtNo ratings yet

- Acer Travelmate 4150 Dunlin LA-2601 SchematicsDocument51 pagesAcer Travelmate 4150 Dunlin LA-2601 SchematicsDoru Razvan100% (1)

- BK4811B Datasheet V1.2Document37 pagesBK4811B Datasheet V1.2BradMorse50% (2)

- Features: or Modifications Due To Changes in Technical Specifications. Rev. C, Issue Date: 2009/10/13Document48 pagesFeatures: or Modifications Due To Changes in Technical Specifications. Rev. C, Issue Date: 2009/10/13Namaku rokibNo ratings yet

- RK3066 Mid PDFDocument17 pagesRK3066 Mid PDFSharon MurphyNo ratings yet

- PO-2033C LCD Panel Controller Board Support TTL & LVDS Panel For 4.3" 22" Digital LCD PanelDocument12 pagesPO-2033C LCD Panel Controller Board Support TTL & LVDS Panel For 4.3" 22" Digital LCD Panelamir rudinNo ratings yet

- EN25Q32C 32 Megabit Serial Flash Memory With 4kbyte Uniform SectorDocument62 pagesEN25Q32C 32 Megabit Serial Flash Memory With 4kbyte Uniform Sectoramir baroughNo ratings yet

- WIZ811MJ Datasheet v1.2Document13 pagesWIZ811MJ Datasheet v1.2ummonkNo ratings yet

- DRIVER InfineonDocument26 pagesDRIVER InfineonWalter Martin Paz HolguinNo ratings yet

- Compal La 1911Document57 pagesCompal La 1911stuartb52No ratings yet

- 8051 TutorialDocument47 pages8051 TutorialSumit OjhaNo ratings yet

- NL192108AC10 01D - Accessory - LVDS Converter - July 2017Document12 pagesNL192108AC10 01D - Accessory - LVDS Converter - July 2017yose06No ratings yet

- Title: HV320WXC-200 Preliminary Product Specification: Beijing Boe Display TechnologyDocument27 pagesTitle: HV320WXC-200 Preliminary Product Specification: Beijing Boe Display TechnologywerpinNo ratings yet

- Title: HV320WXC-200 Preliminary Product Specification: Beijing Boe Display TechnologyDocument27 pagesTitle: HV320WXC-200 Preliminary Product Specification: Beijing Boe Display TechnologyDouglas BeltránNo ratings yet

- Project Name: I4XIXX Platform: Montevina Merom (CPU) +cantiga (NB) +ICH9M (SB)Document37 pagesProject Name: I4XIXX Platform: Montevina Merom (CPU) +cantiga (NB) +ICH9M (SB)sousalrNo ratings yet

- Title: HV430FHB-N10 Product Specification: 拟制 审核 批准 DateDocument29 pagesTitle: HV430FHB-N10 Product Specification: 拟制 审核 批准 DateGeovanny Jose Sanjuan Bustamante100% (1)

- WMS PDFDocument35 pagesWMS PDFMuskan BhargavaNo ratings yet

- Am 640480GTMQW T00HDocument18 pagesAm 640480GTMQW T00HHelderDosSantosNo ratings yet

- Main Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDocument25 pagesMain Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDhivya NNo ratings yet

- Cambridge Audio Azur 640c Service ManualDocument34 pagesCambridge Audio Azur 640c Service ManualMartin Szathmári100% (1)

- Ecs Es10isx 15bfp8-010100 Rev+aDocument34 pagesEcs Es10isx 15bfp8-010100 Rev+aCarlosAldereteNo ratings yet

- Placa 9 - SHUTTLE A14RV08 - 71R-A14RV4-T840 - REV A0 10ABR2012Document39 pagesPlaca 9 - SHUTTLE A14RV08 - 71R-A14RV4-T840 - REV A0 10ABR2012Sergio GalliNo ratings yet

- TITLE: HV320WXC 100 TITLE: HV320WXC-100 Product Specification Rev. ADocument28 pagesTITLE: HV320WXC 100 TITLE: HV320WXC-100 Product Specification Rev. AManuelE.LeonVelezNo ratings yet

- 25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Document31 pages25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Ken AlonsoNo ratings yet

- DS26LV31T 3-V Enhanced CMOS Quad Differential Line Driver: 1 Features 3 DescriptionDocument22 pagesDS26LV31T 3-V Enhanced CMOS Quad Differential Line Driver: 1 Features 3 Descriptionnhatnam06dt1No ratings yet

- Connecting Ethernet Interface With LPC2000: Rev. 01 - 7 February 2007 Application NoteDocument21 pagesConnecting Ethernet Interface With LPC2000: Rev. 01 - 7 February 2007 Application NoteJorBS57No ratings yet

- Philips LCD 15PFL4122 - 19PFL4322 - 20PFL4122 Chassis TPS1.0E LA PDFDocument105 pagesPhilips LCD 15PFL4122 - 19PFL4322 - 20PFL4122 Chassis TPS1.0E LA PDFAouadi Abdellaziz100% (1)

- IRS2453 (1) D (S) : Features Product SummaryDocument18 pagesIRS2453 (1) D (S) : Features Product SummaryGabriel CalderonNo ratings yet

- BIG-INNO EMCP MX100 Series Datasheet PDFDocument109 pagesBIG-INNO EMCP MX100 Series Datasheet PDFSteven ChowNo ratings yet

- Manual de Service para TV LED PhilipsDocument108 pagesManual de Service para TV LED Philipstavillo1980No ratings yet

- EN25Q32B 32mbit SPI FlashDocument56 pagesEN25Q32B 32mbit SPI Flashمحمد كمالNo ratings yet

- CCTV Surveillance: Video Practices and TechnologyFrom EverandCCTV Surveillance: Video Practices and TechnologyRating: 4 out of 5 stars4/5 (1)

- Token Ring Technology ReportFrom EverandToken Ring Technology ReportNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- StarLAN Technology ReportFrom EverandStarLAN Technology ReportRating: 3 out of 5 stars3/5 (1)

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- Digital Power Electronics and ApplicationsFrom EverandDigital Power Electronics and ApplicationsRating: 3.5 out of 5 stars3.5/5 (3)

- Guide c07 733228Document58 pagesGuide c07 733228tomtang77No ratings yet

- 300G Im 20121214Document4 pages300G Im 20121214Josue Vieira OliveiraNo ratings yet

- Youtube Video Download Using PythonDocument37 pagesYoutube Video Download Using PythonVINOTH K100% (2)

- It Is Vital To Good Project Management To Be Meticulously Honest in Estimat Ing The Time Required To Complete Each of The Various Tasks Included in The Project. Note ThatDocument16 pagesIt Is Vital To Good Project Management To Be Meticulously Honest in Estimat Ing The Time Required To Complete Each of The Various Tasks Included in The Project. Note ThatSuraj SinghalNo ratings yet

- Dwi Hadianti, S.E: Mypersonal Profile Work ExperienceDocument1 pageDwi Hadianti, S.E: Mypersonal Profile Work ExperienceBumn Kuala Tungkal HebatNo ratings yet

- 29-CHT06 Honda Steering Wheel ControlDocument4 pages29-CHT06 Honda Steering Wheel Controlalexandre fleureauNo ratings yet

- Oracle® Service Fulfillment Manager: Implementation Guide Release 12.2Document148 pagesOracle® Service Fulfillment Manager: Implementation Guide Release 12.2yadavdevenderNo ratings yet

- Taitz, Hale Complaint 05 04 2009Document85 pagesTaitz, Hale Complaint 05 04 2009haneno100% (11)

- SprutCAM 1Document150 pagesSprutCAM 1Galletti DenisNo ratings yet

- ControlMaestro 2010Document2 pagesControlMaestro 2010lettolimaNo ratings yet

- Math Mammoth - 1Document113 pagesMath Mammoth - 1ramjd100% (2)

- Junos Telemetry InterfaceDocument150 pagesJunos Telemetry InterfacedeeNo ratings yet

- Architecture of Industrial Automation Systems: Unit-1 ECE361Document20 pagesArchitecture of Industrial Automation Systems: Unit-1 ECE361anuj jainNo ratings yet

- Digital DocumentationDocument5 pagesDigital DocumentationTushar DeshwalNo ratings yet

- 110PAX4 - Parts (2008)Document7 pages110PAX4 - Parts (2008)Jonathan LongNo ratings yet

- Advanced High-Capacity Synchronization Solution: Your BenefitsDocument6 pagesAdvanced High-Capacity Synchronization Solution: Your BenefitsTuan MANo ratings yet

- CE-EMC CERT SHEM1806004552IT Network Camera DS-2CD2045FWD-I 20180710Document1 pageCE-EMC CERT SHEM1806004552IT Network Camera DS-2CD2045FWD-I 20180710DaniellMargaritNo ratings yet

- Using IComparer IComparable For Sorting in WPFDocument6 pagesUsing IComparer IComparable For Sorting in WPFAbhiNo ratings yet

- Adhiraj Singh ParmarDocument2 pagesAdhiraj Singh ParmarAshok SambasivanNo ratings yet

- Industrial Safety CurriculumDocument67 pagesIndustrial Safety Curriculumrashid_siddiqi144100% (1)

- C++ Practicle FileDocument39 pagesC++ Practicle Filekhushi birlaNo ratings yet

- Amd Cpu Intel CPU Amd Cpu: Brand New Computer Packages " Super Sale at Very Very Low Prices !!! "Document2 pagesAmd Cpu Intel CPU Amd Cpu: Brand New Computer Packages " Super Sale at Very Very Low Prices !!! "Bryan BautistaNo ratings yet

- Classification Tree - Utkarsh Kulshrestha: Earn in G Is in Learnin G - Utkarsh KulshresthaDocument33 pagesClassification Tree - Utkarsh Kulshrestha: Earn in G Is in Learnin G - Utkarsh KulshresthaN MaheshNo ratings yet

- Low-Cost Dual-Band E-Shaped Patch Antenna For Energy Harvesting Applications Using Grey Wolf OptimizerDocument5 pagesLow-Cost Dual-Band E-Shaped Patch Antenna For Energy Harvesting Applications Using Grey Wolf Optimizermubeen khanNo ratings yet

- HettichDocument74 pagesHettichomkarniranjanNo ratings yet

- Access The GUI On Unity Array With No Network access-KB 501073Document3 pagesAccess The GUI On Unity Array With No Network access-KB 501073Алексей ПетраковNo ratings yet

- Footprinting and ScanningDocument16 pagesFootprinting and Scanningcrispin quadrosNo ratings yet

- C DAC Winter Project Report-7Document29 pagesC DAC Winter Project Report-7Sanchit AlekhNo ratings yet

- Manuals For Cars: Autosoft Catalog:: Chip Tuning FolderDocument165 pagesManuals For Cars: Autosoft Catalog:: Chip Tuning FolderKamyl AzariNo ratings yet

- Free Bitcoin MethodDocument7 pagesFree Bitcoin Method⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻ ⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻⸻No ratings yet