Professional Documents

Culture Documents

Comparative Study of Sense Amplifiers for SRAM

Uploaded by

Bhagyavant HanchinalOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Comparative Study of Sense Amplifiers for SRAM

Uploaded by

Bhagyavant HanchinalCopyright:

Available Formats

Special Issue - 2016 International Journal of Engineering Research & Technology (IJERT)

ISSN: 2278-0181

V-IMPACT - 2016_2 Conference Proceedings

Comparative Study of Sense Amplifiers for

SRAM

Mohammed Shafique1, Ruchi Sharma2

1 2

M. Tech Scholar Associate Professor,

Vivekananda Global University, Jaipur Department of Electronics & Communication,

Vivekananda Global University, Jaipur

Abstract:- This paper presents the comparative study of 6T SRAM WORKING: SRAM consist of six transistors in

different type of sense amplifiers. These sense amplifiers are which four transistors i.e. two cross coupled invertors as

voltage-mode sense amplifier (VMSA) and Charge transfer shown in figure1. Two NMOS transistors which are known

sense amplifiers (CTSA). The first objective of this research as access transistors were connected to this cross coupled

work is to design the sense amplifier and the next objective is

structure and bit-lines (i.e. Q & Q_b). These access

to compare and identify which design has better performance

in term of power and speed. Sense amplifiers are one of the transistors are operated by the wordline (WL). Static RAM

most essential circuits in the CMOS memories that plays an operation is done in three modes i.e. Standby, Read & write

important role to reduce the overall sensing delay and voltage. mode. In Standby mode the information stored previously

Previous voltage mode sense amplifiers sense the voltage in SRAM cell is remains indefinitely as long as power

difference at bit and bit lines bar but as the memory size supply is there. So wordline is grounded during standby

increase the capacitances of bit line and date line also mode. In read operation first of all bit-lines are pre-charged

increases. The tools used for simulation is TANNER EDA for to Vdd and then wordline (WL) is selected to turn on the

layout using 65nm technology. The results show that the access transistor. These access transistors connect the bit-

CTSA has higher speed with lower delay and low power

lines to the memory cell[2].

dissipation than VMSA. But cell size of VMSA in comparison

with CTMA is smaller. CTSA is more suitable for high speed

performance and low power circuitry and VMSA is best

suited for stability and smaller design.

Keywords: 6T SRAM, Voltage mode sense amplifier (VMSA),

Charge transfer sense amplifier (CTSA).

INTRODUCTION

SRAM stand for Static Random Access Memory, a

nonvolatile memory that can stores the information as long

as the power is applied. The sense amplifier operated only

when stored data is read from memory. Sense amplifier

(SA) is used to detect the very small difference voltage at

bit-lines and amplify the signals to its full digital voltage

swing before the signals are fully charged or discharged.

This situation causes the time taken to read the content of Figure 1: 6T SRAM

memory is shorten since the circuitry does not requires to

wait until the signals getting fully charged or discharged to Memory storing a logic value ‘0’ i.e. (a low voltage),

determine either it is '1' or '0'. The small spark or glitch at therefore the bit-line is discharged through pull-down

both bit-lines may determine its state. So the memory may transistor & access transistor so that the differential voltage

take it quickly either as 'I' or '0' rather than trying to is developed between bit-lines. This differential voltage is

calculate or wait for its voltage full swing level, thus saves sensed by the sense amplifier to show the information

time in read operation into memory[1]. stored in cell. This difference in voltage should be large

In this paper the sense amplifiers are selected is enough to detect but not extremely large, otherwise the

conventional voltage sense amplifiers and charge transfer state of the invertor will be flipped. Same as SRAM cell

sense amplifiers. These sense amplifiers are simulated at reading operation, the two bit-lines are pre-charged to

65nm technology scale. At this technology sense amplifiers VDD in a write operation. The address decoder enables the

is compared on the basis of sensing delay and power word line (WL) to turn on the access transistor. Figure

consumption at different voltages. shows a 6T SRAM cell’s initial condition before a write

The organization of this paper is done in following operation, where the cell initially stored logic “1” at node

manner i.e. initially a brief explanation of 6T SRAM and Q (HIGH) and is written with a logic “0” (Node HIGH is

conventional sense amplifiers is done. After that pulled down to ground).

comparison of both the sense amplifiers is done with graph.

Volume 4, Issue 32 Published by, www.ijert.org 1

Special Issue - 2016 International Journal of Engineering Research & Technology (IJERT)

ISSN: 2278-0181

V-IMPACT - 2016_2 Conference Proceedings

SENSE AMPLIFIERS: Sense amplifiers are the most CHARGE TRANSFER SENSE AMPLIFIER: The basic

essential circuit of SRAM which detect the voltage function of Charge Transfer Sense Amplifier is depends

different between the bit-lines and show which data value upon the charge redistribution from high bit-line

stored in the memory cell. In this paper we discuss two capacitance to the low capacitance of the nodes X and X̅ as

type of sense amplifiers i.e. Voltage Mode sense amplifiers shown in figure 3. The high speed operation of CTSA is

and Charge Transfer sense amplifier. due to to this charger distribution [5][6]. The circuit has

two parts in which P6, P9, N1 & P7, P10, N2 form

VOLTAGE MODE SENSE AMPLIFIER: The operation of common gate cascade with PMOS P6 and P7 biased at Vo.

voltage mode sense amplifier is based on the differential In the other part P12, P13, N3 and N4 form the cross-

voltage developed by the bit-lines. The circuit consist of coupled inverters[7]. CTSA is operated in two phase. In the

cross coupled inverters that converts the bit-line voltage pre-charge phase, high pre-charging of the bit-lines and all

difference at their input to full swing output figure 2 shows the intermediate nodes (A, B, C & D) is done. By keeping

the voltage mode sense amplifier circuit implementation. EN high the output of the common-gate amplifier (X and X ̅)

BL and BLB inputs are coupled to the column bit-lines of is pre discharged low. In the evaluation phase, PCH is kept

the cell. The inverters are form by P6-N1 and P7-N2 that high and SEL input is grounded to select a column. By

convert the differential voltage on the bit-lines to a full- dragging EN low CTSA is enabled. Assume the bit-line

swing at the output. The pre-charge circuitry is formed by BLB is going low. As the voltage of the BLB goes

P3, P4 and P5 which is used to pre-charge the internal immediate Vo + |VTP|, P6 goes into sub-threshold region of

nodes X, ̅X of this circuit through the bit-lines. The memory operation avoiding the output node from getting charged.

cell is connected to the sense amplifier by P1, P2 while to However, the other bit-line BL remains high and charges

enable the sense amplifier N3 is used. The internal nodes of the output node X to high.

the sense amplifier is isolated from the external load by

output inverters. The operation of voltage mode sense

amplifier is done in two phases. In the first phase i.e. pre

charge phase, the PCH is kept active low so that bit-lines

and the nodes X and ̅ X are pre-charged high. During the

evaluation phase, sense amplifier is connected to the

memory cell by pulled down the select-line (SEL). A

voltage difference is developed between bit-lines BL and

BLB due to the stored data in memory cell. If the data

stored in the memory cell is a ‘1’, voltage across BLB

decreases slightly and if the stored data in memory cell a

‘0’, voltage across BL decreases slightly. Once the required

differential voltage has been developed between bit-lines,

EN is pulled high to enable the sense amplifier. Differential

discharging of the bit-lines capacitance is used by the

VMSA for sensing the voltage difference and converts this

differential voltage at its inputs to a full swing at the

outputs[3][4].

Figure 3: Charge Transfer Sense Amplifier

SIMULATION RESULTS

The sense amplifiers given in figure. 2 and figure 3 have

been designed and analyzed on the basis of average power

consumption and sensing delay[7]. Figure 4 and figure 6

show the schematic of VMSA and CTSA respectively.

Table 1 and Table 2 shows the comparison between both

sense amplifiers. Graphical representation shown in figure

8 and figure 9 Read ‘1’ and Read ‘0’ operations have been

performed on SRAM cell. For schematic design and

simulation purpose Tanner EDA is used and technology

Figure 2: Voltage Mode Sense Amplifier used is 65nm.

Volume 4, Issue 32 Published by, www.ijert.org 2

Special Issue - 2016 International Journal of Engineering Research & Technology (IJERT)

ISSN: 2278-0181

V-IMPACT - 2016_2 Conference Proceedings

Figure 4: Schematic of VMSA Figure 6: Schematic of CTSA

Figure 5: Waveform of VMSA Figure 7: Waveform of CTSA

A. Average Power consumption:

The power is calculated for these two topologies. Average

power consumption for reading 0 & 1 operation is found to

be same. Table 1 shows that CTSA consumes least average

power in comparison to VMSA. The observation also

shows that with increase in supply voltage, there is increase

in average power consumption. Figure 8 shows the

Volume 4, Issue 32 Published by, www.ijert.org 3

Special Issue - 2016 International Journal of Engineering Research & Technology (IJERT)

ISSN: 2278-0181

V-IMPACT - 2016_2 Conference Proceedings

comparison of power supply of both sense amplifiers by

graph. Voltage v/s Delay at 65nm

160

Table 1: Comparison of average power consumption with

140

varying supply voltage.

120 VMSA

Delay (ps)

Voltage Power Consumption(µW) at 65nm 100

S. No. 80 CTSA

(Vdd) VMSA CTSA 60

1 1.2V 15.65µW 2.71µW

2 1.5V 28.15µW 10.83µW 40

3 1.8V 52.43µW 27.78µW 20

4 2.1V 154.55µW 62.56µW

5 2.4V 481.95µW 169.74µW 0

1.2 1.5 1.8 2.1 2.4

Voltage

Voltage v/s Power Consumption at Figure 9: Graphical representation of Sensing Delay

65nm

CONCLUSION:

600

In this paper SRAM with both the sense amplifiers i.e.

Power Consumption

500 Voltage Sense amplifier & Charge Transfer sense amplifier

is analyzed and discussed. The observation shows that the

400 VMSA CTSA give best results in terms of power consumption and

sensing delay in comparison to VMSA. Observation of the

300 work shows that power consumption of the sense amplifier

CTSA is increases with the increase in supply voltage whereas

200

sensing delay is decreases with increase in supply voltage.

100

In future scope more efficient sense amplifier can be

realized by improving available sense amplifiers so that

0 power consumption and delay can be reduced during

1.2 1.5 Voltage

1.8 2.1 2.4 sensing the data from memory cell.

ACKNOWLEDGEMENT:

I would like to sincerely thank Mrs. Ruchi Sharma,

Figure 8: Graphical representation of average power consumption Associate professor, Electronics & Communication,

Vivekananda Global University, Jaipur who inspired me to

B. Sensing Delay:

do this work. In addition, I would like to thank Dr. Rahul

At 50% of logic levels Sensing Delay was calculated and it

Raj Choudhary, Associate Professor, Engineering College

was observed that CTSA has the least delay in comparison

Bikaner for providing me resources to carry out my work.

to VMSA. Table 2 shows that with increase in supply

voltage, delay decreases in both VMSA and CTSA. Figure

REFERENCES

9 shows the comparison of sensing delay of both the sense

amplifiers by graph. [1] R. J. Baker, “CMOS Circuit Design, Layout & Simulation”, John

Wiley & Sons, inc., Publication, Third Edition, 2010.

Table 2: Comparison of Sensing Delay with varying [2] S. S. Chopade, R. Sharma, “Performance and area scaling of 6T

voltage supply SRAM using SOI MOSFET at 32nm node”, 2015 International

Conference on Communication, Information & Computing

Technology (ICCICT), pp: 2015

[3] N. Chandoke, N. Chitkara, A. Grover, “Comparative Analysis of

Voltage Sensing Delay at 65nm

Sense amplifier for SRAM in 65um CMOS Technology”,

S. No.

IEEEXplore, pp: 577 - 580, 2004

(Vdd) VMSA CTSA

[4] I. S. A. Halim., N. H. Basemu, S. L. M. Hassan, A. A. Rahim,

1 1.2V 151.45 ps 75.50 ps

“Comparative Study on CMOS SRAM Sense amplifier using 90um

2 1.5V 124.60 ps 37.45 ps Technology”, International Conference on Technology, Informatics,

3 1.8V 108.51 ps 27.26 ps Management, Engineering & Environment Bandung, Indonesia, pp:

4 2.1V 99.58 ps 24.66 ps 172-175, 2013.

5 2.4V 92.73 ps 22.78 ps [5] T. Na, S. H. Woo, J. Kim, H. Jeong, S. O. Jung, “Comparative Study

of Various Latch-Type Sense Amplifiers,” IEEE Transaction on

VLSI systems, Volume 22, February, 2014.

[6] K. K. Joshi, J. Kedia, “Performance Analysis of Sense Amplifiers”,

IJAERT, Volume 3, June 2015.

[7] P. Y. Chiang, “Sense amplifier power and delay characterization for

operation under low Vdd and low-voltage clock swing,” 2009 IEEE

International Symp. Circuits System, pp. 181–184, May 2009.

Volume 4, Issue 32 Published by, www.ijert.org 4

You might also like

- 6T SRAM simulationDocument9 pages6T SRAM simulationAzza FaiadNo ratings yet

- Analysis of Sense Amplifier Circuit Used in High Performance & Low Power SramDocument5 pagesAnalysis of Sense Amplifier Circuit Used in High Performance & Low Power SramGJESRNo ratings yet

- Sram StudyDocument5 pagesSram StudyAjitaSPNo ratings yet

- 6T SRAM SimulationDocument9 pages6T SRAM SimulationAzza FaiadNo ratings yet

- Design of A Low Power SRAM Cell by Tanner Tool 45 NMDocument6 pagesDesign of A Low Power SRAM Cell by Tanner Tool 45 NMEditor IJRITCCNo ratings yet

- ASIC-System On Chip-VLSI Design - SRAM Cell Design PDFDocument8 pagesASIC-System On Chip-VLSI Design - SRAM Cell Design PDFGowtham SpNo ratings yet

- Design and Analysis of 4Kb Sram Array Cell For The Development of Sram ChipDocument8 pagesDesign and Analysis of 4Kb Sram Array Cell For The Development of Sram ChipRohit KumarNo ratings yet

- EE512: Analysis of a Sense Amplifier Circuit DesignDocument2 pagesEE512: Analysis of a Sense Amplifier Circuit DesignSpidey Reddy100% (1)

- Analysis of Leakage Reduction Technique On Different SRAM CellsDocument6 pagesAnalysis of Leakage Reduction Technique On Different SRAM Cellssurendiran123No ratings yet

- A Novel Power Efficient 8T SRAM Cell: Ankush Sindwani Suman SainiDocument5 pagesA Novel Power Efficient 8T SRAM Cell: Ankush Sindwani Suman SainiBanu KiranNo ratings yet

- Column Decoder Using PTL For Memory: M.Manimaraboopathy, S.Sivasaravanababu, S.Sebastinsuresh A. RajivDocument8 pagesColumn Decoder Using PTL For Memory: M.Manimaraboopathy, S.Sivasaravanababu, S.Sebastinsuresh A. RajivInternational Organization of Scientific Research (IOSR)No ratings yet

- An 18 MV Offset 193 Ps Sensing Delay and Low Static Current Sense Amplifier For SRAMDocument4 pagesAn 18 MV Offset 193 Ps Sensing Delay and Low Static Current Sense Amplifier For SRAMchirag gargNo ratings yet

- Leakage Compensation Design For SRAM: Keerthi Sagar 180942008Document24 pagesLeakage Compensation Design For SRAM: Keerthi Sagar 180942008Keerthi SagarNo ratings yet

- Ultra-Low Leakage Static Random Access Memory DesignDocument10 pagesUltra-Low Leakage Static Random Access Memory DesignIJRES teamNo ratings yet

- Design of Low Power Sram: Presentation OnDocument31 pagesDesign of Low Power Sram: Presentation Ondhanaji pawarNo ratings yet

- Design of A Telescopic Fully Differential OTADocument7 pagesDesign of A Telescopic Fully Differential OTAUdai ValluruNo ratings yet

- EE141 Final Project: Report 4 - Barrel Shifter DesignDocument7 pagesEE141 Final Project: Report 4 - Barrel Shifter DesignCarmine MeleNo ratings yet

- A Study Into Comparison of Voltage Sense Amplifier and Charge Transfer Sense AmplifierDocument8 pagesA Study Into Comparison of Voltage Sense Amplifier and Charge Transfer Sense AmplifierHan hoNo ratings yet

- Design of Sense AmplifierDocument17 pagesDesign of Sense Amplifierpooja112No ratings yet

- Sju SRAM IP For DSPSoC ProjectsDocument50 pagesSju SRAM IP For DSPSoC Projectsraymar2kNo ratings yet

- Reduction of Leakage Power in 8T Sram Cell Using Virtual GroundDocument5 pagesReduction of Leakage Power in 8T Sram Cell Using Virtual GroundSasi Kiran SNo ratings yet

- Cmos OpampDocument3 pagesCmos OpampTànVìĐọcNo ratings yet

- Sense AmplifiersDocument6 pagesSense AmplifierskeerthiNo ratings yet

- SRAM Memory Cell Operation and ArchitectureDocument12 pagesSRAM Memory Cell Operation and ArchitectureAnimisha VermaNo ratings yet

- Aic FL MergedDocument14 pagesAic FL Mergedshashank.pg23No ratings yet

- Vlsi CadDocument138 pagesVlsi CadRaghava KatreepalliNo ratings yet

- Analytical Study of Sense AmplifierDocument5 pagesAnalytical Study of Sense Amplifiers.b.v.seshagiri1407No ratings yet

- Analysis of Low Power 6T SRAM Using 45 NM Technology: Shatrughan SinghDocument5 pagesAnalysis of Low Power 6T SRAM Using 45 NM Technology: Shatrughan SinghShruti DasNo ratings yet

- Low Power Sram Design Using Block PartitioningDocument4 pagesLow Power Sram Design Using Block PartitioningesatjournalsNo ratings yet

- Performance of Low Power SRAM Cells On SNM and Power DissipationDocument5 pagesPerformance of Low Power SRAM Cells On SNM and Power DissipationInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- SR21622171146Document4 pagesSR21622171146Kini FamilyNo ratings yet

- Ieee TfetDocument3 pagesIeee TfetNirman KhairnarNo ratings yet

- EC6601 VLSI Design Model QBDocument44 pagesEC6601 VLSI Design Model QBxperiaashNo ratings yet

- Analysis of Cmos Dynamic Comparators For Low Power and High Speed AdcsDocument7 pagesAnalysis of Cmos Dynamic Comparators For Low Power and High Speed AdcsNoReply ProgramNo ratings yet

- 9th ICCCNT Paper 169Document7 pages9th ICCCNT Paper 169reeya agrawalNo ratings yet

- Low Power SramDocument7 pagesLow Power SramRohit TiwariNo ratings yet

- Low Power 12T MTCMOS SRAM Based CAMDocument6 pagesLow Power 12T MTCMOS SRAM Based CAMmani_vlsiNo ratings yet

- Low Power SramDocument6 pagesLow Power SramSuresh BharathNo ratings yet

- A Self-Biased High Performance Folded Cascode Op-Amp: of ofDocument6 pagesA Self-Biased High Performance Folded Cascode Op-Amp: of ofBodhayan PrasadNo ratings yet

- Self Biased High Performance Folded Cascode Cmos OpampDocument6 pagesSelf Biased High Performance Folded Cascode Cmos OpampArvind MishraNo ratings yet

- ,hrfikadsz NJSDFMV M VZDocument5 pages,hrfikadsz NJSDFMV M VZpalakNo ratings yet

- IJSTE-SRAMDocument9 pagesIJSTE-SRAMpradeepkarraNo ratings yet

- IJETR032745Document3 pagesIJETR032745erpublicationNo ratings yet

- Single Stage and Two Stage OP-AMP Design in 180NM CMOS TechnologyDocument7 pagesSingle Stage and Two Stage OP-AMP Design in 180NM CMOS TechnologyIJSTE0% (1)

- 2011 IEEE Source Follower Based Track and Hold CircuitDocument4 pages2011 IEEE Source Follower Based Track and Hold CircuitMuhammad Sohail Asst. ProfessorNo ratings yet

- 5.data Convertors and PldsDocument7 pages5.data Convertors and PldsManiNo ratings yet

- Eec118s11 Lab6Document6 pagesEec118s11 Lab6vamsi krishnaNo ratings yet

- Open-Ended Lab (Design and Implementation of A Circuit That Amplifies As Well As Rectify TheDocument4 pagesOpen-Ended Lab (Design and Implementation of A Circuit That Amplifies As Well As Rectify TheNayeem HossainNo ratings yet

- 16bitSAR PDFDocument5 pages16bitSAR PDFOmar NaelNo ratings yet

- Double Tail ComparatorDocument32 pagesDouble Tail ComparatormdlogicsolutionsNo ratings yet

- Presentation - On-Chip Current Sensing Technique For Cmos Monolithic Switch-ModeDocument30 pagesPresentation - On-Chip Current Sensing Technique For Cmos Monolithic Switch-Modesohailasghar_tNo ratings yet

- PXC 3897398Document5 pagesPXC 3897398seshu bradyNo ratings yet

- High Speed Content Addressable Memory: AbstractDocument4 pagesHigh Speed Content Addressable Memory: AbstractjayachandarNo ratings yet

- Figure 1: 6T CellDocument4 pagesFigure 1: 6T CellShehryarNo ratings yet

- Low Voltage and Low Power in SRAM Read and Write Assist TechniquesDocument6 pagesLow Voltage and Low Power in SRAM Read and Write Assist TechniquesIJSTENo ratings yet

- Low Voltage and Low Power in Sram Read and Write Assist TechniquesDocument9 pagesLow Voltage and Low Power in Sram Read and Write Assist TechniquesIJSTENo ratings yet

- Low Power Ring Oscillator at 180nm CMOS Technology: Aman Shivhare M. K. GuptaDocument4 pagesLow Power Ring Oscillator at 180nm CMOS Technology: Aman Shivhare M. K. GuptaRam MNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- STEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10From EverandSTEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10No ratings yet

- Presentation No 05Document83 pagesPresentation No 05gary2ndhome2182No ratings yet

- Presentation No 05Document83 pagesPresentation No 05gary2ndhome2182No ratings yet

- Presentation No 05Document83 pagesPresentation No 05gary2ndhome2182No ratings yet

- Layout of CMOS Analog CircuitsDocument0 pagesLayout of CMOS Analog CircuitsarammartNo ratings yet

- Lecture05 Ee474 Layout PDFDocument77 pagesLecture05 Ee474 Layout PDFsridharNo ratings yet

- Introduction To Analog Layout Design SlidesDocument111 pagesIntroduction To Analog Layout Design Slidesrozelle manguiatNo ratings yet

- ECE1371 Mismatch 2Document25 pagesECE1371 Mismatch 2Gyanaranjan NayakNo ratings yet

- Layout of CMOS Analog CircuitsDocument0 pagesLayout of CMOS Analog CircuitsarammartNo ratings yet

- (Revised) MIMOS 2-Sep - SFAM Endorsement On Wafer Fabrication Front - Back End Process For Manufacturing SpecialistDocument58 pages(Revised) MIMOS 2-Sep - SFAM Endorsement On Wafer Fabrication Front - Back End Process For Manufacturing Specialistmahadzir72No ratings yet

- High-power NPN transistor for horizontal deflectionDocument1 pageHigh-power NPN transistor for horizontal deflectionJavier LongoniNo ratings yet

- SEMICONDUCTOR PARTS LISTDocument137 pagesSEMICONDUCTOR PARTS LISTOscar Orea33% (3)

- EPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 ADocument6 pagesEPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 AЕвгений ИвановNo ratings yet

- hcpl0730 PDFDocument13 pageshcpl0730 PDFgoogle manNo ratings yet

- MCFT - Electronic Material Devices, Devices and Fabrication - Parasuram SwaminathanDocument219 pagesMCFT - Electronic Material Devices, Devices and Fabrication - Parasuram Swaminathankomal udaiNo ratings yet

- CMOS VLSI Design Lecture 8 Combinational CircuitsDocument37 pagesCMOS VLSI Design Lecture 8 Combinational CircuitsNguyễn Khắc ThanhNo ratings yet

- Solutions Manual To Accompany Cmos Vlsi Design 3rd Edition 9780321149015Document36 pagesSolutions Manual To Accompany Cmos Vlsi Design 3rd Edition 9780321149015clowneryanileness.y7qst100% (51)

- Microcontroller Based Traffic Light Controller ProjectDocument11 pagesMicrocontroller Based Traffic Light Controller Projectالموعظة الحسنه chanelNo ratings yet

- Irgp 50 B 60 PD 1Document11 pagesIrgp 50 B 60 PD 1pufipufi5No ratings yet

- High-K Dielectric Materials in MicroelectronicsDocument31 pagesHigh-K Dielectric Materials in MicroelectronicsAadil ShNo ratings yet

- Features General Description: P-Channel Enhancement Mode Power MOSFETDocument6 pagesFeatures General Description: P-Channel Enhancement Mode Power MOSFETPablo AllosiaNo ratings yet

- Electronic Devices and Circuit Theory: Bipolar Junction TransistorsDocument26 pagesElectronic Devices and Circuit Theory: Bipolar Junction Transistorsallrounder1122No ratings yet

- CMOS Design Manufacturing ProcessDocument93 pagesCMOS Design Manufacturing ProcessSharan ThummalaNo ratings yet

- SMD Surface Tranzistor&Diode1Document9 pagesSMD Surface Tranzistor&Diode1bugy costyNo ratings yet

- ExperimentDocument22 pagesExperimentGourav RoyNo ratings yet

- Electronic DevicesDocument21 pagesElectronic DevicesJoshua DoctorNo ratings yet

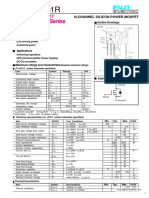

- Super FAP-G Series: Fuji Power MosfetDocument4 pagesSuper FAP-G Series: Fuji Power MosfetsaikumarNo ratings yet

- 50 TOP TRANSISTORS Questions and Answers PDFDocument8 pages50 TOP TRANSISTORS Questions and Answers PDFamadullah janNo ratings yet

- Clipping Diodes Primer and Selection GuideDocument6 pagesClipping Diodes Primer and Selection GuideChris Huss Sr.No ratings yet

- How To Use and Design Interposer PCB in Chip PackagingDocument11 pagesHow To Use and Design Interposer PCB in Chip PackagingjackNo ratings yet

- Ka5Q-Series: KA5Q0765RT/KA5Q12656RT/KA5Q1265RF/ KA5Q1565RF Fairchild Power Switch (FPS)Document16 pagesKa5Q-Series: KA5Q0765RT/KA5Q12656RT/KA5Q1265RF/ KA5Q1565RF Fairchild Power Switch (FPS)EmanuelLanNo ratings yet

- Unisonic Technologies Co., LTD: 20A, 600V N-CHANNEL Power MosfetDocument3 pagesUnisonic Technologies Co., LTD: 20A, 600V N-CHANNEL Power MosfetJuan Carlos RuizNo ratings yet

- STD9N10 STD9N10-1: N-CHANNEL 100V - 0.23 - 9A Dpak/Ipak Power Mos TransistorDocument12 pagesSTD9N10 STD9N10-1: N-CHANNEL 100V - 0.23 - 9A Dpak/Ipak Power Mos TransistorEligio VásquezNo ratings yet

- Chapter 3 Bipolar Junction Transistor BJT (Cont.)Document14 pagesChapter 3 Bipolar Junction Transistor BJT (Cont.)AyeshaNo ratings yet

- CMOS VLSI Design 92Document1 pageCMOS VLSI Design 92Carlos SaavedraNo ratings yet

- Silicon PNP Power Transistor 2SA1216 Spec SheetDocument4 pagesSilicon PNP Power Transistor 2SA1216 Spec SheetEkoAriansyahNo ratings yet

- Bill of MaterialsDocument2 pagesBill of MaterialsbillNo ratings yet

- KA1L0880B/KA1M0880B: Fairchild Power Switch (FPS)Document10 pagesKA1L0880B/KA1M0880B: Fairchild Power Switch (FPS)vetchboyNo ratings yet

- MDS3604 P-Channel Trench MOSFET -30V -11A 12.1mΩDocument6 pagesMDS3604 P-Channel Trench MOSFET -30V -11A 12.1mΩjay rNo ratings yet