Professional Documents

Culture Documents

RFP50N06: N-Channel Power MOSFET 60V, 50A, 22 M Features

Uploaded by

Mohammd EssaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

RFP50N06: N-Channel Power MOSFET 60V, 50A, 22 M Features

Uploaded by

Mohammd EssaCopyright:

Available Formats

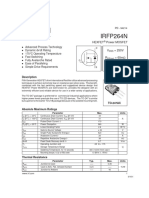

RFP50N06

Data Sheet September 2013

N-Channel Power MOSFET Features

60V, 50A, 22 mΩ • 50A, 60V

These N-Channel power MOSFETs are manufactured using

• rDS(ON) = 0.022Ω

the MegaFET process. This process, which uses feature

sizes approaching those of LSI integrated circuits gives • Temperature Compensating PSPICE® Model

optimum utilization of silicon, resulting in outstanding • Peak Current vs Pulse Width Curve

performance. They were designed for use in applications

such as switching regulators, switching converters, motor • UIS Rating Curve

drivers, and relay drivers. These transistors can be operated • 175oC Operating Temperature

directly from integrated circuits.

Symbol

Formerly developmental type TA49018.

D

Ordering Information

PART NUMBER PACKAGE BRAND G

RFP50N06 TO-220AB RFP50N06

S

Packaging

JEDEC TO-220AB

SOURCE

DRAIN

GATE

DRAIN

(FLANGE)

©2002 Fairchild Semiconductor Corporation RFP50N06 Rev. C0

RFP50N06

Absolute Maximum Ratings TC = 25oC, Unless Otherwise Specified

RFP50N06 UNITS

Drain to Source Voltage (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VDSS 60 V

Drain to Gate Voltage (RGS = 20kΩ) (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . VDGR 60 V

Gate to Source Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VGS ±20 V

Continuous Drain Current (Figure 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .ID 50 A

Pulsed Drain Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . IDM (Figure 5)

Pulsed Avalanche Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . EAS (Figure 6)

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . PD 131 W

Linear Derating Factor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.877 W/oC

Operating and Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TJ, TSTG -55 to 175 oC

Maximum Temperature for Soldering

Leads at 0.063in (1.6mm) from Case for 10s. . . . . . . . . . . . . . . . . . . . . . . . . . . . TL 300 oC

Package Body for 10s, see Techbrief 334 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Tpkg 260 oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. TJ = 25oC to 150oC.

Electrical Specifications TC = 25oC, Unless Otherwise Specified

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Drain to Source Breakdown Voltage BVDSS ID = 250µA, VGS = 0V (Figure 11) 60 - - V

Gate to Source Threshold Voltage VGS(TH) VGS = VDS, ID = 250µA (Figure 10) 2 - 4 V

Zero Gate Voltage Drain Current IDSS VDS = 60V, TC = 25oC - - 1 µA

VGS = 0V

TC = 150oC - - 50 µA

Gate to Source Leakage Current IGSS VGS = ±20V - - ±100 nA

Drain to Source On Resistance rDS(ON) ID = 50A, VGS = 10V (Figures 9) - - 0.022 Ω

Turn-On Time tON VDD = 30V, ID = 50A - - 95 ns

RL = 0.6Ω, VGS = 10V

Turn-On Delay Time td(ON) - 12 - ns

RGS = 3.6Ω

Rise Time tr (Figure 13) - 55 - ns

Turn-Off Delay Time td(OFF) - 37 - ns

Fall Time tf - 13 - ns

Turn-Off Time tOFF - - 75 ns

Total Gate Charge Qg(TOT) VGS = 0 to 20V VDD = 48V, ID = 50A, - 125 150 nC

RL = 0.96Ω

Gate Charge at 10V Qg(10) VGS = 0 to 10V - 67 80 nC

Ig(REF) = 1.45mA

Threshold Gate Charge Qg(TH) VGS = 0 to 2V (Figure 13) - 3.7 4.5 nC

Input Capacitance CISS VDS = 25V, VGS = 0V - 2020 - pF

f = 1MHz

Output Capacitance COSS - 600 - pF

(Figure 12)

Reverse Transfer Capacitance CRSS - 200 - pF

Thermal Resistance Junction to Case RθJC (Figure 3) - - 1.14 oC/W

Thermal Resistance Junction to Ambient RθJA TO-220 - - 62 oC/W

- - - - -

Source to Drain Diode Specifications

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Source to Drain Diode Voltage VSD ISD = 50A - - 1.5 V

Reverse Recovery Time trr ISD = 50A, dISD/dt = 100A/µs - - 125 ns

©2002 Fairchild Semiconductor Corporation RFP50N06 Rev. C0

RFP50N06

Typical Performance Curves Unless Otherwise Specified

1.2 60

POWER DISSIPATION MULTIPLIER

1.0 50

ID , DRAIN CURRENT (A)

0.8 40

0.6 30

0.4 20

0.2 10

0 0

0 25 50 75 100 125 150 175 25 50 75 100 125 150 175

TC , CASE TEMPERATURE (oC) TC , CASE TEMPERATURE (oC)

FIGURE 1. NORMALIZED POWER DISSIPATION vs CASE FIGURE 2. MAXIMUM CONTINUOUS DRAIN CURRENT vs

TEMPERATURE CASE TEMPERATURE

0.5

THERMAL IMPEDANCE

ZθJC, NORMALIZED

0.2

0.1 0.1 PDM

0.05

t1

0.02 t2

0.01 NOTES:

DUTY FACTOR: D = t1/t2

SINGLE PULSE PEAK TJ = PDM x ZθJC x RθJC + TC

0.01 -5

10 10-4 10-3 10-2 10-1 100 101

t1 , RECTANGULAR PULSE DURATION (s)

FIGURE 3. NORMALIZED MAXIMUM TRANSIENT THERMAL IMPEDANCE

400 103

TJ = MAX RATED

FOR TEMPERATURES ABOVE 25oC

SINGLE PULSE

TC = 25oC DERATE PEAK CURRENT

CAPABILITY AS FOLLOWS:

IDM , PEAK CURRENT (A)

100

ID , DRAIN CURRENT (A)

VGS = 20V 175 – T C

100µs I = I 25 ------------------------

150

1ms

VGS = 10V

10

OPERATION IN THIS TC = 25oC

AREA MAY BE

10ms 102

LIMITED BY rDS(ON) TRANSCONDUCTANCE

100ms MAY LIMIT CURRENT

DC IN THIS REGION

VDSS(MAX) = 60V

1 40

1 10 100 10-3 10-2 10-1 100 101 102 103 104

VDS , DRAIN TO SOURCE VOLTAGE (V) t, PULSE WIDTH (ms)

FIGURE 4. FORWARD BIAS SAFE OPERATING AREA FIGURE 5. PEAK CURRENT CAPABILITY

©2002 Fairchild Semiconductor Corporation RFP50N06 Rev. C0

RFP50N06

Typical Performance Curves Unless Otherwise Specified (Continued)

300 125

PULSE DURATION = 80µs

VGS = 10V DUTY CYCLE = 0.5% MAX

TC = 25oC

IAS, AVALANCHE CURRENT (A)

100 100 VGS = 8V

ID , DRAIN CURRENT (A)

STARTING TJ = 25oC

VGS = 7V

75

10 STARTING TJ = 150oC 50

VGS = 6V

If R = 0 VGS = 5V

tAV = (L) (IAS) / (1.3 RATED BVDSS - VDD) 25

If R ≠ 0 VGS = 4V

tAV = (L/R) ln [(IAS*R) / (1.3 RATED BVDSS - VDD) + 1]

1 0

0.01 0.1 1 10 0 1.5 3.0 4.5 6.0 7.5

tAV, TIME IN AVALANCHE (ms) VDS , DRAIN TO SOURCE VOLTAGE (V)

NOTE: Refer to Fairchild Application Notes 9321 and 9322.

FIGURE 6. UNCLAMPED INDUCTIVE SWITCHING CAPABILITY FIGURE 7. SATURATION CHARACTERISTICS

125 2.5

PULSE DURATION = 80µs -55oC 25oC PULSE DURATION = 80µs

DUTY CYCLE = 0.5% MAX DUTY CYCLE = 0.5% MAX

VDD = 15V NORMALIZED DRAIN TO SOURCE VGS = 10V, ID = 50A

ID, DRAIN CURRENT (A)

100 2.0

175oC

ON RESISTANCE

75 1.5

50 1.0

25 0.5

0 0

0 1 2 3 4 5 6 7 8 9 10 -80 -40 0 40 80 120 160 200

VGS , GATE TO SOURCE VOLTAGE (V) TJ , JUNCTION TEMPERATURE (oC)

FIGURE 8. TRANSFER CHARACTERISTICS FIGURE 9. NORMALIZED DRAIN TO SOURCE ON

RESISTANCE vs JUNCTION TEMPERATURE

2.0 2.0

VGS = VDS, ID = 250µA ID = 250µA

NORMALIZED DRAIN TO SOURCE

BREAKDOWN VOLTAGE

1.5 1.5

THRESHOLD VOLTAGE

NORMALIZED GATE

1.0 1.0

0.5 0.5

0 0

-80 -40 0 40 80 120 160 200 -80 -40 0 40 80 120 160 200

TJ , JUNCTION TEMPERATURE (oC) TJ , JUNCTION TEMPERATURE (oC)

FIGURE 10. NORMALIZED GATE THRESHOLD VOLTAGE vs FIGURE 11. NORMALIZED DRAIN TO SOURCE BREAKDOWN

JUNCTION TEMPERATURE VOLTAGE vs JUNCTION TEMPERATURE

©2002 Fairchild Semiconductor Corporation RFP50N06 Rev. C0

RFP50N06

Typical Performance Curves Unless Otherwise Specified (Continued)

4000 60 10

VGS = 0V, f = 1MHz

VDS , DRAIN TO SOURCE VOLTAGE (V)

VGS , GATE TO SOURCE VOLTAGE (V)

CISS = CGS + CGD VDD = BVDSS VDD = BVDSS

CRSS = CGD

COSS = CDS + CGD 45 7.5

C, CAPACITANCE (pF)

3000

CISS

2000 30 5.0

0.75 BVDSS 0.75 BVDSS

0.50 BVDSS 0.50 BVDSS

COSS 0.25 BVDSS 0.25 BVDSS

1000 15 2.5

RL = 1.2Ω

CRSS Ig(REF) = 1.45mA

VGS = 10V

0 0 0

Ig(REF) Ig(REF)

0 5 10 15 20 25 t, TIME (µs)

20 80

VDS , DRAIN TO SOURCE VOLTAGE (V) Ig(ACT) Ig(ACT)

NOTE: Refer to Fairchild Application Notes AN7254 and AN7260.

FIGURE 12. CAPACITANCE vs DRAIN TO SOURCE VOLTAGE FIGURE 13. NORMALIZED SWITCHING WAVEFORMS FOR

CONSTANT GATE CURRENT

Test Circuits and Waveforms

VDS

BVDSS

L tP

VDS

VARY tP TO OBTAIN IAS

+ VDD

REQUIRED PEAK IAS RG

VDD

VGS -

DUT

tP

0V IAS

0

0.01Ω

tAV

FIGURE 14. UNCLAMPED ENERGY TEST CIRCUIT FIGURE 15. UNCLAMPED ENERGY WAVEFORMS

tON tOFF

td(ON) td(OFF)

VDS

tr tf

VDS

90% 90%

RL

VGS

+ 10% 10%

VDD 0

-

DUT 90%

RGS

VGS 50% 50%

PULSE WIDTH

VGS 10%

0

FIGURE 16. SWITCHING TIME TEST CIRCUIT FIGURE 17. SWITCHING WAVEFORMS

©2002 Fairchild Semiconductor Corporation RFP50N06 Rev. C0

RFP50N06

Test Circuits and Waveforms (Continued)

VDS

RL VDD Qg(TOT)

VDS

VGS = 20V

VGS Qg(10)

+

VDD

VGS VGS = 10V

-

DUT VGS = 2V

Ig(REF) 0

Qg(TH)

Ig(REF)

0

FIGURE 18. GATE CHARGE TEST CIRCUIT FIGURE 19. GATE CHARGE WAVEFORMS

©2002 Fairchild Semiconductor Corporation RFP50N06 Rev. C0

RFP50N06

PSPICE Electrical Model

.SUBCKT RFP50N06 2 1 3

REV 2/22/93

*NOM TEMP = 25oC

CA 12 8 3.68e-9

CB 15 14 3.625e-9

CIN 6 8 1.98e-9

5 DRAIN

DBODY 7 5 DBDMOD 10 2

DBREAK 5 11DBKMOD DPLCAP LDRAIN

- RDRAIN

DPLCAP 10 5 DPLCAPMOD 6 DBREAK

ESG

8 16

+ VTO

EBREAK 11 7 17 18 64.59 - DBODY

+

EVTO MOS2

EDS 14 8 5 8 1 GATE 21

-

+

EGS 13 8 6 8 1 9 20 18 6 11 +

1 MOS1

ESG 6 10 6 8 1 8 17

LGATE RGATE EBREAK

18

EVTO 20 6 18 8 1 RIN CIN -

RSOURCE 7 LSOURCE

IT 8 17 1 8

3

S1A S2A SOURCE

LDRAIN 2 5 1e-9 12 15 RBREAK

13 14 17 18

LGATE 1 9 5.65e-9 8 13

LSOURCE 3 7 4.13e-9

S1B S2B RVTO

13

MOS1 16 6 8 8 MOSMOD M=0.99 CA CB IT 19

MOS2 16 21 8 8 MOSMOD M=0.01 + + 14 -

5

EGS 6 EDS 8 VBAT

- 8 - +

RBREAK 17 18 RBKMOD 1

RDRAIN 5 16 RDSMOD 1e-4

RGATE 9 20 0.690

RIN 6 8 1e9

RSOURCE 8 7 RDSMOD 12e-3

RVTO 18 19 RVTOMOD 1

S1A 6 12 13 8 S1AMOD

S1B 13 12 13 8 S1BMOD

S2A 6 15 14 13 S2AMOD

S2B 13 15 14 13 S2BMOD

VBAT 8 19 DC 1

VTO 21 6 0.678

.MODEL DBDMOD D (IS=9.85e-13 RS=4.91e-3 TRS1=2.07e-3 TRS2=2.51e-7 CJO=2.05e-9 TT=4.33e-8)

.MODEL DBKMOD D (RS=1.98e-1 TRS1=2.35E-4 TRS2=-3.83e-6)

.MODEL DPLCAPMOD D (CJO=1.42e-9 IS=1e-30 N=10)

.MODEL MOSMOD NMOS (VTO=3.65 KP=35 IS=1e-30 N=10 TOX=1 L=1u W=1u)

.MODEL RBKMOD RES (TC1=1.23e-3 TC2=-2.34e-7)

.MODEL RDSMOD RES (TC1=5.01e-3 TC2=1.49e-5)

.MODEL RVTOMOD RES (TC1=-5.03e-3 TC2=-5.16e-6)

.MODEL S1AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-6.75 VOFF=-2.5)

.MODEL S1BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-2.5 VOFF=-6.75)

.MODEL S2AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-2.7 VOFF=2.3)

.MODEL S2BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=2.3 VOFF=-2.7)

.ENDS

NOTE: For further discussion of the PSPICE model consult A New PSPICE Sub-Circuit for the Power MOSFET Featuring Global Temperature

Options; authors, William J. Hepp and C. Frank Wheatley.

©2002 Fairchild Semiconductor Corporation RFP50N06 Rev. C0

RFP50N06

TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not

intended to be an exhaustive list of all such trademarks.

AccuPower™ F-PFS™ Sync-Lock™

AX-CAP®* FRFET® ® tm

®*

SM ®

BitSiC™ Global Power Resource PowerTrench

Build it Now™ GreenBridge™ PowerXS™

TinyBoost®

CorePLUS™ Green FPS™ Programmable Active Droop™

® TinyBuck®

CorePOWER™ Green FPS™ e-Series™ QFET

TinyCalc™

CROSSVOLT™ Gmax™ QS™

TinyLogic®

CTL™ GTO™ Quiet Series™

TINYOPTO™

Current Transfer Logic™ IntelliMAX™ RapidConfigure™

TinyPower™

DEUXPEED® ISOPLANAR™ ™ TinyPWM™

Dual Cool™ Marking Small Speakers Sound Louder

TinyWire™

EcoSPARK® and Better™ Saving our world, 1mW/W/kW at a time™

TranSiC™

EfficentMax™ MegaBuck™ SignalWise™

TriFault Detect™

ESBC™ MICROCOUPLER™ SmartMax™

TRUECURRENT®*

® MicroFET™ SMART START™

SerDes™

MicroPak™ Solutions for Your Success™

Fairchild® MicroPak2™ SPM®

Fairchild Semiconductor ® MillerDrive™ STEALTH™

MotionMax™ SuperFET® UHC®

FACT Quiet Series™

® mWSaver ® SuperSOT™-3 Ultra FRFET™

FACT

OptoHiT™ SuperSOT™-6 UniFET™

FAST®

OPTOLOGIC ®

SuperSOT™-8 VCX™

FastvCore™

OPTOPLANAR ® SupreMOS ® VisualMax™

FETBench™

SyncFET™ VoltagePlus™

FPS™

XS™

*Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE

RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY

PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY

THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE

EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used here in:

1. Life support devices or systems are devices or systems which, (a) are 2. A critical component in any component of a life support, device, or

intended for surgical implant into the body or (b) support or sustain life, system whose failure to perform can be reasonably expected to cause

and (c) whose failure to perform when properly used in accordance with the failure of the life support device or system, or to affect its safety or

instructions for use provided in the labeling, can be reasonably effectiveness.

expected to result in a significant injury of the user.

ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation’s Anti-Counterfeiting Policy. Fairchild’s Anti-Counterfeiting Policy is also stated on our external website,

www.Fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their

parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed

application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the

proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild

Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild

Distributors are genuine parts, have full traceability, meet Fairchild’s quality standards for handing and storage and provide access to Fairchild’s full range of

up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address and

warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is

committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Datasheet contains the design specifications for product development. Specifications

Advance Information Formative / In Design

may change in any manner without notice.

Datasheet contains preliminary data; supplementary data will be published at a later

Preliminary First Production date. Fairchild Semiconductor reserves the right to make changes at any time without

notice to improve design.

Datasheet contains final specifications. Fairchild Semiconductor reserves the right to

No Identification Needed Full Production

make changes at any time without notice to improve the design.

Datasheet contains specifications on a product that is discontinued by Fairchild

Obsolete Not In Production Semiconductor. The datasheet is for reference information only.

Rev. I66

©2002 Fairchild Semiconductor Corporation RFP50N06 Rev. C0

You might also like

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- 16N06LE FairchildSemiconductorDocument7 pages16N06LE FairchildSemiconductorHarald DasselNo ratings yet

- RFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets FeaturesDocument8 pagesRFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets Featureswert1a2No ratings yet

- 6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999Document8 pages6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999rex999No ratings yet

- IRF9520Document7 pagesIRF9520Emilio QuijanoNo ratings yet

- Rfp30N06Le, Rf1S30N06Lesm: 30A, 60V, Esd Rated, 0.047 Ohm, Logic Level N-Channel Power Mosfets FeaturesDocument8 pagesRfp30N06Le, Rf1S30N06Lesm: 30A, 60V, Esd Rated, 0.047 Ohm, Logic Level N-Channel Power Mosfets Featuresfahmi1987No ratings yet

- 10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Document8 pages10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Lotfi MessaadiNo ratings yet

- IRFD9120: 1.0A, 100V, 0.6 Ohm, P-Channel Power Mosfet FeaturesDocument6 pagesIRFD9120: 1.0A, 100V, 0.6 Ohm, P-Channel Power Mosfet FeaturesJaime Enrique ValbuenaNo ratings yet

- Datasheet RFD16 N05Document8 pagesDatasheet RFD16 N05Nicolau FrançaNo ratings yet

- IRFP460: 20A, 500V, 0.270 Ohm, N-Channel Power MOSFET FeaturesDocument7 pagesIRFP460: 20A, 500V, 0.270 Ohm, N-Channel Power MOSFET FeaturesAmirNo ratings yet

- 16A, 400V, 0.300Ohm N-Channel Power MOSFETDocument6 pages16A, 400V, 0.300Ohm N-Channel Power MOSFETjjtrivedi8717No ratings yet

- Datasheet f1010Document8 pagesDatasheet f1010shobu21100% (1)

- Irf 530 NPBFDocument9 pagesIrf 530 NPBFGabiBaciuNo ratings yet

- Irf3710 PDFDocument8 pagesIrf3710 PDFJose M PeresNo ratings yet

- Advanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedwilltorNo ratings yet

- Irf1404 HEXFET (R) Power MOSFET DatasheetDocument8 pagesIrf1404 HEXFET (R) Power MOSFET DatasheetMeatheadMerlinNo ratings yet

- Buz11 DDocument6 pagesBuz11 DEmmanuel ZambranoNo ratings yet

- Infineon IRF1010E Aplication - ENDocument9 pagesInfineon IRF1010E Aplication - ENlaciNo ratings yet

- Infineon IRF1010EZPBF DatasheetDocument3 pagesInfineon IRF1010EZPBF DatasheetNdidi KennethNo ratings yet

- Irfp260n PDFDocument9 pagesIrfp260n PDFRida DTNo ratings yet

- IRFZ 34N - International RectifierDocument8 pagesIRFZ 34N - International RectifierStevenNo ratings yet

- Irf640n PDFDocument12 pagesIrf640n PDFLeonel Antonio100% (1)

- Fdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MDocument11 pagesFdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MSukandar TeaNo ratings yet

- Irf 3205Document12 pagesIrf 3205Bristhian LezanoNo ratings yet

- Datasheet PDFDocument8 pagesDatasheet PDFSaad LehlouNo ratings yet

- Irf3710 Datasheet PDFDocument8 pagesIrf3710 Datasheet PDFMiguel Gutierréz CasillasNo ratings yet

- Advanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedLiver Haro OrellanesNo ratings yet

- Mosfet Irf 2204Document10 pagesMosfet Irf 2204Milagros Mendieta VegaNo ratings yet

- Irfp150npdf 231209 185343Document9 pagesIrfp150npdf 231209 185343Denilson BonifacioNo ratings yet

- Data SheetDocument11 pagesData SheetYoscar SanchezNo ratings yet

- IRFP240: 20A, 200V, 0.180 Ohm, N-Channel Power Mosfet FeaturesDocument7 pagesIRFP240: 20A, 200V, 0.180 Ohm, N-Channel Power Mosfet FeaturesAdah BumboneNo ratings yet

- Irfz34Npbf: Hexfet Power MOSFET V 55V R 0.040 I 29ADocument9 pagesIrfz34Npbf: Hexfet Power MOSFET V 55V R 0.040 I 29Achermy025No ratings yet

- Advanced Power MOSFET IRFZ44 Spec SheetDocument2 pagesAdvanced Power MOSFET IRFZ44 Spec SheetEduRoiNo ratings yet

- IRFP054N_PowerMOSFETDocument8 pagesIRFP054N_PowerMOSFETcostelcnNo ratings yet

- Advanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedMax RenanNo ratings yet

- Irfp 260 NPBFDocument8 pagesIrfp 260 NPBFadamdwaldropNo ratings yet

- Irfp 264 NDocument8 pagesIrfp 264 Nhernan luzardoNo ratings yet

- Irfp 250 NDocument9 pagesIrfp 250 NjozzemarNo ratings yet

- IRF3710Document10 pagesIRF3710MaksumAbdullahNo ratings yet

- Automotive Mosfet: Typical ApplicationsDocument10 pagesAutomotive Mosfet: Typical ApplicationsSaikumarNo ratings yet

- Irfp250n PDFDocument9 pagesIrfp250n PDFEdison RamirezNo ratings yet

- Irf 1404Document10 pagesIrf 1404paivafrotaNo ratings yet

- Advanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDarwin Coronado AparicioNo ratings yet

- Irfp264n PDFDocument8 pagesIrfp264n PDFAdah BumbonNo ratings yet

- Irf630 IrDocument11 pagesIrf630 IrVremedSoluCionesNo ratings yet

- N-Channel JFET Low Noise Amplifier: CorporationDocument1 pageN-Channel JFET Low Noise Amplifier: CorporationmahaisenNo ratings yet

- Irf5210 100V 40aDocument9 pagesIrf5210 100V 40aReneNo ratings yet

- DatasheetDocument8 pagesDatasheetOscarito VázquezNo ratings yet

- Irfr3505Pbf Irfu3505Pbf: FeaturesDocument11 pagesIrfr3505Pbf Irfu3505Pbf: FeaturesAzizullah AlizayNo ratings yet

- FDPA Programing1231Document10 pagesFDPA Programing1231Engr. Syed Ghulam Mustafa ShahNo ratings yet

- Irfz48npbf PDFDocument8 pagesIrfz48npbf PDFAntony BurgersNo ratings yet

- Dgdlirfp2907pbf PdffileidDocument10 pagesDgdlirfp2907pbf PdffileidLeonardo NascimentoNo ratings yet

- Datasheet IRFP 9240Document7 pagesDatasheet IRFP 9240AguilaSolitariaNo ratings yet

- Advanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument9 pagesAdvanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedMilton OrtegaNo ratings yet

- Advanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche Ratedjohan elian whiteNo ratings yet

- Nvis6106Document1 pageNvis6106Mohammd EssaNo ratings yet

- GSA Report FallujahDocument3 pagesGSA Report FallujahMohammd EssaNo ratings yet

- MOS4026_MOS4033#STMDocument15 pagesMOS4026_MOS4033#STMMohammd EssaNo ratings yet

- 74LS161-3Document6 pages74LS161-3Mohammd EssaNo ratings yet

- Ultrasonic T-M mode-12EDocument1 pageUltrasonic T-M mode-12EMohammd EssaNo ratings yet

- Introduction to Digital Electronics Merged CompressedDocument71 pagesIntroduction to Digital Electronics Merged CompressedMohammd EssaNo ratings yet

- Nvis6103Document1 pageNvis6103Mohammd EssaNo ratings yet

- Nvis6006Document1 pageNvis6006Mohammd EssaNo ratings yet

- 404 ERROR PAGE NOT FOUND. OR Article Has Not  Yet Been Published/uploadedDocument1 page404 ERROR PAGE NOT FOUND. OR Article Has Not  Yet Been Published/uploadedMohammd EssaNo ratings yet

- Solar Cell - WikipediaDocument26 pagesSolar Cell - WikipediaMohammd EssaNo ratings yet

- AERB Guidelines PDFDocument7 pagesAERB Guidelines PDFAaquib Mahfuz100% (1)

- Photovoltaics ReportDocument50 pagesPhotovoltaics ReportMohammd EssaNo ratings yet

- Manual For Solar Technician: November 2015Document86 pagesManual For Solar Technician: November 2015kakagoNo ratings yet

- 1 KW Solar Power Plant Project ReportDocument3 pages1 KW Solar Power Plant Project ReportMohammd EssaNo ratings yet

- Solar CellDocument34 pagesSolar CellAbdul Shakoor sabirNo ratings yet

- Solar Powered Mobile Charging Unit A Review IJERTV10IS090014Document6 pagesSolar Powered Mobile Charging Unit A Review IJERTV10IS090014CHITTHALURI Naveen kumarNo ratings yet

- Solar CellDocument34 pagesSolar CellAbdul Shakoor sabirNo ratings yet

- 2SK3603Document4 pages2SK3603sagtvNo ratings yet

- 2SK3603Document4 pages2SK3603sagtvNo ratings yet

- Contoh Skripsi Bahasa Inggris Case StudyDocument18 pagesContoh Skripsi Bahasa Inggris Case StudyRizki Fajrita100% (14)

- 6 Thinking Hats Detailed Model - UpdatedDocument32 pages6 Thinking Hats Detailed Model - Updatedgeetanshi mittalNo ratings yet

- OTISLINE QuestionsDocument5 pagesOTISLINE QuestionsArvind Gupta100% (1)

- Microbiology - Prokaryotic Cell Biology: Bacterial Surface Structures Bacterial Cell Wall StructureDocument5 pagesMicrobiology - Prokaryotic Cell Biology: Bacterial Surface Structures Bacterial Cell Wall StructureDani AnyikaNo ratings yet

- Historical Background of The SchoolDocument2 pagesHistorical Background of The SchoolJoel Daen50% (2)

- Prob StatDocument1 pageProb StatSerenity VertesNo ratings yet

- Analysis of Security Issues in Web Applications Through Penetration TestingDocument7 pagesAnalysis of Security Issues in Web Applications Through Penetration Testingabdel_lakNo ratings yet

- Sax AltoDocument2 pagesSax AltoJohnny GervasioNo ratings yet

- Document Revision TableDocument11 pagesDocument Revision Tableseva1969No ratings yet

- V200 User ManualDocument171 pagesV200 User ManualuriahskyNo ratings yet

- FS Jack: Information GuideDocument12 pagesFS Jack: Information GuideGemma gladeNo ratings yet

- WordPress Introduction: CMS BasicsDocument21 pagesWordPress Introduction: CMS BasicsNgô Ngọc Hải phươngNo ratings yet

- Self-test on the COSO ERM frameworkDocument6 pagesSelf-test on the COSO ERM frameworkLady BirdNo ratings yet

- T e 2552674 Percy Polls Peculiar Plants Fiction Year 5 Reading Comprehension - Ver - 5Document20 pagesT e 2552674 Percy Polls Peculiar Plants Fiction Year 5 Reading Comprehension - Ver - 5mariam osamaNo ratings yet

- MathWorks Interview ProcessDocument2 pagesMathWorks Interview ProcessPawan Singh100% (1)

- African in The Modern WorldDocument18 pagesAfrican in The Modern WorldSally AnkomaahNo ratings yet

- UFD/MMC/SD Controller Flash Support Limitation and Interconnection NoteDocument5 pagesUFD/MMC/SD Controller Flash Support Limitation and Interconnection Noteمہرؤآنہ آبہرآهہيہمہNo ratings yet

- Axial Centrifugal FansDocument15 pagesAxial Centrifugal FansAhsan JavedNo ratings yet

- DEME Offshore Brochure_2022Document16 pagesDEME Offshore Brochure_2022amin32No ratings yet

- (MATH1013) (2016) (F) Midterm Wsuab 41338Document9 pages(MATH1013) (2016) (F) Midterm Wsuab 41338陳希程No ratings yet

- Arts and Crafts of Basey SamarDocument28 pagesArts and Crafts of Basey SamarTrisha MenesesNo ratings yet

- B1 UDO Trace LogDocument14 pagesB1 UDO Trace LogCh M KashifNo ratings yet

- Consumer Reports Buying Guide 2021Document227 pagesConsumer Reports Buying Guide 2021fatso68100% (1)

- Cash and Cash EquivalentsDocument2 pagesCash and Cash EquivalentsMary Jullianne Caile SalcedoNo ratings yet

- BISE Sukkur HSC Part 2 Results 2015Document12 pagesBISE Sukkur HSC Part 2 Results 2015ajayNo ratings yet

- Smart Panels - Digitized Switchboards - Blokset Desing and Assembly GuideDocument94 pagesSmart Panels - Digitized Switchboards - Blokset Desing and Assembly Guidelorentz franklinNo ratings yet

- Advanced Engineering Economics: Combining FactorsDocument19 pagesAdvanced Engineering Economics: Combining FactorsA GlaumNo ratings yet

- Main Body Recruitment Process of Human Resource Division in Brac BankDocument55 pagesMain Body Recruitment Process of Human Resource Division in Brac BankAsfia PrantyNo ratings yet

- AmboooDocument39 pagesAmboooTesfaye DegefaNo ratings yet

- Age Hardening Gold Alloys For JewelryDocument4 pagesAge Hardening Gold Alloys For JewelryReinol Eko SianturiNo ratings yet