Professional Documents

Culture Documents

Exercise 4 - Summer Semester 2019: July 2, 2019

Uploaded by

Mario PajaOriginal Title

Copyright

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentExercise 4 - Summer Semester 2019: July 2, 2019

Uploaded by

Mario PajaExercise 4 - Summer Semester 2019

July 2, 2019

This document is part of the laboratory for the exam ”Fundamentals of

IC Deign”. It is for students attending the same-named lecture organized by

the Institute for Integrated Circuits of the TUHH. All information is supplied

without liability.

During this laboratory the simulation software LTSpice by Analog Devices

will be used.

Institute for Integrated Circuits

Prof. Dr.-Ing. Matthias Kuhl

In the last exercise, the final operational amplifier has to be design in order to fulfill the

given specifications.

Task 4 Creating a Symbol

To simplify further schematics and to allow multiple instances of the same design to

be placed in higher hierarchy levels, a symbol for the operational amplifier has to be

created.

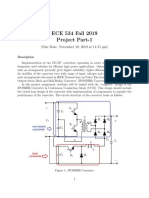

Before linking a symbol to the schematic place the transistors and compensation capacitor

for the output stage as in Fig. 1 (M15, M16, C1). Make sure that no voltage or current

sources are left in the schematic and create Input/Output pins for the following nodes:

1. Positive input V+

2. Negative input V−

3. Output voltage Vout

4. Supply voltage VDD

Figure 1: Schematic in LTSpice for which a symbol has to be created.

Next go to Hierarchy → Create a new Symbol. A new tab will appear in which the symbol

can be drawn as shown in Fig. 2.

Summer Therm 2019 Fundamentals of IC Design 2/7

Institute for Integrated Circuits

Prof. Dr.-Ing. Matthias Kuhl

Figure 2: Example for a symbol drawing for the operational amplifier.

To link the schematic pins with the corresponding pins in the symbol, pin instances have

to be placed (Right click → AddP in). Make sure, the pin-names in your symbol match the

names in the schematic and that you create a pin for VDD (A ground pin is not necessary)

as shwon in Fig. 3.

Figure 3: Example for a symbol drawing for the operational amplifier with pins assigned.

After your symbol design is finished, safe it in the same folder as the schematic with the

same name.

Summer Therm 2019 Fundamentals of IC Design 3/7

Institute for Integrated Circuits

Prof. Dr.-Ing. Matthias Kuhl

To create an instance of the amplifier open a new schematic in the same folder as the

symbol- and schematic file of your amplifier. By opening Edit → Component and changing

the top directory to the current work-directory, your amplifier appears in the list.

Task 5 Two Stage Amplifier Design

In this task, the testbenches for the simulations are explained as well as the final specifi-

cations that have to be reached by your design.

Task 5.1 Testbenches

After creating the symbol, multiple instances of your design can be placed in other

schematics in order to simulate different characteristics of the amplifier.

Task 5.1.1 Gain, Phase-Margin and Unity-Gain-Frequency

To simulate the Gain (A), Phase-Margin (PM) and the Unity-Gain-Frequency (UGF), a

testbench as shown in Fig. 4 has to be used. Due the low-pass filter in the feedback with

a pole at a very low frequency, only the common-mode voltage (VCM ) is fed back to the

negative input, hence the closed loop transfer function becomes the open loop transfer

function.

Figure 4: Testbench for Gain, PM and UGF.

Summer Therm 2019 Fundamentals of IC Design 4/7

Institute for Integrated Circuits

Prof. Dr.-Ing. Matthias Kuhl

Set up your AC simulation to run in Decade mode from 10 Hz to 10 GHz with 100 points

per decade. The final specifications have to be fulfilled for any common mode within the

specified input common mode range. To get your phase margin, measure the phase at

your unity gain frequency to obtain

P M = −180◦ − φ(U GF ) (1)

Task 5.1.2 Slew Rate

The slew rate of an amplifier can be simulated by applying a voltage step at the input of

the OPAMP in unity gain configuration as in Fig.5.

Figure 5: Testbench for the Slew Rate.

To extract the slew rate, measure the slope of the output signal between 10 % and 90 %

of the signal amplitude (Fig. 6) for both the rising and falling edge.

For the simulation use a pulse from V0 = 1V to V1 = 2V with a pulse length of 1 µs.

Summer Therm 2019 Fundamentals of IC Design 5/7

Institute for Integrated Circuits

Prof. Dr.-Ing. Matthias Kuhl

Figure 6: Slew rate simulation example.

Task 5.2 Specifications

Figure 7: Final two-stage amplifier.

In this task, you have to design you final amplifier with output stage and compensation

circuit as shown in Fig.7.

Summer Therm 2019 Fundamentals of IC Design 6/7

Institute for Integrated Circuits

Prof. Dr.-Ing. Matthias Kuhl

The specifications for the final design are:

• CLoad = 10 pF

• Unity Gain Frequency (UGF) ≥ 3.5 MHz

• Open-Loop DC Gain (ADC ) ≥ 85 dB

• Phase-Margin ≥ 60◦

• Input-Swing = 1 V → VDD − 900 mV

• Slew Rate ≥ 4 V /µs

• Maximum Power Consumption including Beta Multiplier (Pmax ) ≤ 350 µW

To reach this specification you might have to change also the design of your differential

stage again, depending on your previous design. Using only the pole splitting technique is

enough to reach the given specifications. However, feel free to apply the lead compensation

technique to reach even better performance.

Hints:

• Start by thinking about how much current you can spend for the whole operational

amplifier to stay below the given Pmax

• Calculate the compensation capacitor CC , using the Unity Gain Frequency specifi-

cation. Therefor use the simplified equation

gm1 = ωUG ∗ CC (2)

with ωUG being the Unity Gain Angular Frequency.

• If the slew rate is not high enough, think about increasing the current in the output

or differential stage of your amplifier.

ISS

SR = (3)

C

Summer Therm 2019 Fundamentals of IC Design 7/7

You might also like

- Digital LED Thermometer with Microcontroller AVR ATtiny13From EverandDigital LED Thermometer with Microcontroller AVR ATtiny13Rating: 5 out of 5 stars5/5 (1)

- Exercise 1 - Summer Semester 2019: April 17, 2019Document9 pagesExercise 1 - Summer Semester 2019: April 17, 2019Mario PajaNo ratings yet

- Exercise 3 - Summer Semester 2019Document8 pagesExercise 3 - Summer Semester 2019Mario PajaNo ratings yet

- Using Advanced Design System To Design An Mmic Amplifier: Keysight Eesof EdaDocument40 pagesUsing Advanced Design System To Design An Mmic Amplifier: Keysight Eesof EdaAbinash Singh RajputNo ratings yet

- Using Advanced Design System To Design An Mmic Amplifier: Agilent Eesof EdaDocument40 pagesUsing Advanced Design System To Design An Mmic Amplifier: Agilent Eesof EdaAgilentcomNo ratings yet

- Lab 3 - HandoutDocument7 pagesLab 3 - HandoutohmprakashNo ratings yet

- EE115C - Digital Electronic Circuits Homework #6: Due Monday, Feb 25, 4pmDocument3 pagesEE115C - Digital Electronic Circuits Homework #6: Due Monday, Feb 25, 4pmShobhit GargNo ratings yet

- Design Project: (Due: Friday, December 8, 2006, 5pm PT)Document6 pagesDesign Project: (Due: Friday, December 8, 2006, 5pm PT)Ibrahim MuhammedNo ratings yet

- E0007e Lab1Document7 pagesE0007e Lab1fabianmozart16No ratings yet

- Mmic Design by KeysightDocument45 pagesMmic Design by Keysightcolantonio.paolo69No ratings yet

- EC2 Exp2 F09Document17 pagesEC2 Exp2 F09Nurul Hanim HashimNo ratings yet

- Assignment 3Document1 pageAssignment 3Aayush ShrivastavaNo ratings yet

- 06 CSL38 Manual LDDocument68 pages06 CSL38 Manual LDSwathi N SudarshanNo ratings yet

- Klein Isaac Ee 435 Final Project ReportDocument15 pagesKlein Isaac Ee 435 Final Project Reportapi-482007969No ratings yet

- 4 Differential Amplifier With OutputDocument5 pages4 Differential Amplifier With Outputmanishkavi89No ratings yet

- Control Systems Lab STM32F4Document30 pagesControl Systems Lab STM32F4Williams OrtizNo ratings yet

- 9.2.1.3 Lab - Designing and Implementing A Subnetted IPv4 Addressing SchemeDocument26 pages9.2.1.3 Lab - Designing and Implementing A Subnetted IPv4 Addressing SchemesellysaidiNo ratings yet

- EEE 325 Laboratory On Microwave Engineering 2021/09 Week 2: Dinesh Periannan/Dr IntanDocument25 pagesEEE 325 Laboratory On Microwave Engineering 2021/09 Week 2: Dinesh Periannan/Dr IntanK Min Thit SarNo ratings yet

- Class AbDocument7 pagesClass Abdemos2011No ratings yet

- Name: - Date: - : Electronic Devices II Lab EET 323Document9 pagesName: - Date: - : Electronic Devices II Lab EET 323irfanNo ratings yet

- Experiment4 Frequency Response2122016Document10 pagesExperiment4 Frequency Response2122016Babasrinivas GuduruNo ratings yet

- PTI Section 9 Analog DigitalDocument14 pagesPTI Section 9 Analog Digitalchrist9088No ratings yet

- Lab 4 A Folded-Cascode Operational AmplifierDocument6 pagesLab 4 A Folded-Cascode Operational AmplifierJatinKumarNo ratings yet

- Eecs311 Lab06 PDFDocument28 pagesEecs311 Lab06 PDFGwenShepherdNo ratings yet

- Microwave Amplifier Design and Smith Chart Utility For Z Matching Network Using ADSDocument29 pagesMicrowave Amplifier Design and Smith Chart Utility For Z Matching Network Using ADSZeeshan AhmedNo ratings yet

- ELE341 Project OPAmpDocument4 pagesELE341 Project OPAmpbabycryyNo ratings yet

- Lab3 MPPT CVR Using Matlab-4Document7 pagesLab3 MPPT CVR Using Matlab-4Ali DurraniNo ratings yet

- ELX218 ElectronicsDocument6 pagesELX218 ElectronicsHassan IqbalNo ratings yet

- LAB 9: Final System and Circuit Simulations: ADS Fundamentals - 2009Document24 pagesLAB 9: Final System and Circuit Simulations: ADS Fundamentals - 2009Ace PraphuNo ratings yet

- Power Measurement in Cadence Spectre: AssumptionsDocument7 pagesPower Measurement in Cadence Spectre: AssumptionsnikunjNo ratings yet

- Cypress - Application Notes 26 PDFDocument6 pagesCypress - Application Notes 26 PDFsung quekNo ratings yet

- Workshop 01Document11 pagesWorkshop 01Damith ErangaNo ratings yet

- MyEMG MonitorDocument6 pagesMyEMG MonitorJoel OntiverosNo ratings yet

- Lab 03 - Inverting Amplifier: John Stenson, David Coy December 20, 2015Document5 pagesLab 03 - Inverting Amplifier: John Stenson, David Coy December 20, 2015JohnStensonNo ratings yet

- Eee 523 ProjDocument12 pagesEee 523 ProjBodhayan PrasadNo ratings yet

- PID2697681Document4 pagesPID2697681nguyentienduy1512No ratings yet

- 2018 Ee 69Document19 pages2018 Ee 69Ali MohsinNo ratings yet

- Lab 9 Layout of 1-Bit Full Adder: by Sachin B. Kadam 15ECE1022Document14 pagesLab 9 Layout of 1-Bit Full Adder: by Sachin B. Kadam 15ECE1022Rohan GaonkarNo ratings yet

- Power Systems Laboratory User Manual: Revised: July 22, 2008Document40 pagesPower Systems Laboratory User Manual: Revised: July 22, 2008prakashkmrrNo ratings yet

- EE 2201 Touch Switch Project ManualDocument5 pagesEE 2201 Touch Switch Project ManualKrishnaNo ratings yet

- Lab3.Design Project - Ee140.s12.v1Document4 pagesLab3.Design Project - Ee140.s12.v1frankongNo ratings yet

- ETIN25 - Analogue IC Design Laboratory Manual - Lab 2: Jonas Lindstrand Martin Liliebladh Markus Törmänen September 2011Document14 pagesETIN25 - Analogue IC Design Laboratory Manual - Lab 2: Jonas Lindstrand Martin Liliebladh Markus Törmänen September 2011Western777No ratings yet

- 1 2 6 P Understandinganalogdesign rng-2Document5 pages1 2 6 P Understandinganalogdesign rng-2api-287488010No ratings yet

- 4571.c2000 Oscilloscope Tech-ManualDocument21 pages4571.c2000 Oscilloscope Tech-ManualW33t7No ratings yet

- Group 2Document2 pagesGroup 2Zulqarnain KhanNo ratings yet

- Pvsyst Training and Solar Power Plant deDocument4 pagesPvsyst Training and Solar Power Plant deLuis Alberto Serrano MesaNo ratings yet

- Switch-Mode Power Supplies - SPICE Simulations and Practical Designs - EE Times3 PDFDocument7 pagesSwitch-Mode Power Supplies - SPICE Simulations and Practical Designs - EE Times3 PDFVIJAYPUTRA0% (1)

- Lab 1 Introduction and Top-SPICE DemoDocument10 pagesLab 1 Introduction and Top-SPICE Demochrisdp23No ratings yet

- Eee312 Eee282 Lab7 Spring2015Document6 pagesEee312 Eee282 Lab7 Spring2015vognarNo ratings yet

- Motor Control TI C2000Document16 pagesMotor Control TI C2000Mohammed BelkheiriNo ratings yet

- A High Performance CMOS Band - Gap Reference Circuit DesignDocument6 pagesA High Performance CMOS Band - Gap Reference Circuit DesignKhaja Mujeebuddin QuadryNo ratings yet

- Systematic Design of A 200 MSs 8-Bit Interpolating AD ConverterDocument5 pagesSystematic Design of A 200 MSs 8-Bit Interpolating AD ConverterThanos van RamNo ratings yet

- Session 2: Basic Operation and Analysis of A DC/DC ConverterDocument10 pagesSession 2: Basic Operation and Analysis of A DC/DC ConverterSanty LeónNo ratings yet

- ModelbjtDocument19 pagesModelbjtSuraj KamyaNo ratings yet

- Assignment 1 Computer-Aided Design of Analog Circuits: InstructionsDocument4 pagesAssignment 1 Computer-Aided Design of Analog Circuits: Instructionsabhishek raoNo ratings yet

- ECE 534 Project 1 F19Document6 pagesECE 534 Project 1 F19JAY CHHEDANo ratings yet

- Experiment # 3 Amplitude Modulation and Demodulation: 1 PurposeDocument9 pagesExperiment # 3 Amplitude Modulation and Demodulation: 1 PurposeGeorgeNo ratings yet

- ArcFlash Example8Document7 pagesArcFlash Example8Fabian Andres Calderon HernandezNo ratings yet

- Cadence Basic SimulationDocument10 pagesCadence Basic SimulationLarry FredsellNo ratings yet

- Course of Study Microelectronics and Microsystems (Study Cohort w18)Document1 pageCourse of Study Microelectronics and Microsystems (Study Cohort w18)Mario PajaNo ratings yet

- Circuit DesignDocument149 pagesCircuit DesignMario PajaNo ratings yet

- Solutions For Exercises: Solutions For Exercises For "Introduction To Microsystem Technology: A Guide For Students"Document39 pagesSolutions For Exercises: Solutions For Exercises For "Introduction To Microsystem Technology: A Guide For Students"Mario PajaNo ratings yet

- Problem 4: (Microstrip Transmission Line)Document1 pageProblem 4: (Microstrip Transmission Line)Mario PajaNo ratings yet

- Task 2 Beta MultiplierDocument10 pagesTask 2 Beta MultiplierMario PajaNo ratings yet

- Xilinx Analog-Digital-Converter (XADC)Document8 pagesXilinx Analog-Digital-Converter (XADC)Mario PajaNo ratings yet

- KVR16LS11 8Document2 pagesKVR16LS11 8Mario PajaNo ratings yet

- New Text DocumentDocument6 pagesNew Text DocumentMario PajaNo ratings yet

- New Text DocumentDocument1 pageNew Text DocumentMario PajaNo ratings yet

- Maintenance of Building ComponentsDocument4 pagesMaintenance of Building ComponentsIZIMBANo ratings yet

- Introduction To Montenegrin LanguageDocument15 pagesIntroduction To Montenegrin LanguageSanja MacutNo ratings yet

- Microtronics Technologies: GSM Based Vehicle Theft Detection SystemDocument3 pagesMicrotronics Technologies: GSM Based Vehicle Theft Detection Systemابراهيم الثوبريNo ratings yet

- CHAPTER 5 Work MeasurementDocument24 pagesCHAPTER 5 Work MeasurementAiman SupniNo ratings yet

- Total Spanish Course: Learn Spanish With The Michel Thomas Method: Beginner Spanish Audio Course - Michel ThomasDocument5 pagesTotal Spanish Course: Learn Spanish With The Michel Thomas Method: Beginner Spanish Audio Course - Michel Thomasguhofyki0% (1)

- FSED 1F Application Form FSEC For Building Permit Rev02Document2 pagesFSED 1F Application Form FSEC For Building Permit Rev02Angelito RegulacionNo ratings yet

- Sparkylinux 2020.05 x86 - 64 LXQT - Iso.package ListDocument64 pagesSparkylinux 2020.05 x86 - 64 LXQT - Iso.package ListshamaNo ratings yet

- Sand Cone Test ResultsDocument71 pagesSand Cone Test ResultsGayan Indunil JayasundaraNo ratings yet

- 14.victorian Era Inventions and Changes Pupils PDFDocument1 page14.victorian Era Inventions and Changes Pupils PDFSam FairireNo ratings yet

- The Baldur's Gate Series 1 - Baldur GateDocument125 pagesThe Baldur's Gate Series 1 - Baldur GateJustin MooreNo ratings yet

- Wall FootingDocument4 pagesWall FootingMunthir NumanNo ratings yet

- Models For Location SelectionDocument13 pagesModels For Location SelectionSajal ChakarvartyNo ratings yet

- Multiple Choice Questions: This Activity Contains 15 QuestionsDocument4 pagesMultiple Choice Questions: This Activity Contains 15 QuestionsRaman Kulkarni100% (1)

- Swollen EyelidsDocument4 pagesSwollen EyelidsNARENDRANo ratings yet

- 08 LCD Slide Handout 1Document5 pages08 LCD Slide Handout 1Jana Gabrielle Canonigo0% (1)

- Forward Planning DocumentDocument24 pagesForward Planning Documentapi-396981495No ratings yet

- Why Student Choose ABMDocument6 pagesWhy Student Choose ABMJhas MinNo ratings yet

- AdinaDocument542 pagesAdinaSafia SoufiNo ratings yet

- A Simple and Convenient Synthesis of Pseudo Ephedrine From N-MethylamphetamineDocument2 pagesA Simple and Convenient Synthesis of Pseudo Ephedrine From N-Methylamphetaminedh329No ratings yet

- Siop RTSG2016Document336 pagesSiop RTSG2016Mohammed HaiderNo ratings yet

- CN Mod1 Ppt-FinalDocument56 pagesCN Mod1 Ppt-FinalkkNo ratings yet

- TCS303 Pumping Station ControllerDocument17 pagesTCS303 Pumping Station ControllerNAdreaNo ratings yet

- FD72 Technical Manual 28.10.09Document74 pagesFD72 Technical Manual 28.10.09cavgsi16vNo ratings yet

- Punch Fear in The Face Escape AverageDocument12 pagesPunch Fear in The Face Escape AverageRezaBachtiarNo ratings yet

- Distress Manual PDFDocument51 pagesDistress Manual PDFEIRINI ZIGKIRIADOUNo ratings yet

- Past:: Simple Indefinite Continuous Perfect Perfect ContinuousDocument12 pagesPast:: Simple Indefinite Continuous Perfect Perfect ContinuousAhmed Abd El HafeezNo ratings yet

- FAME - Teachers' Material TDocument6 pagesFAME - Teachers' Material TBenny PalmieriNo ratings yet

- Swash Plate Leveling Tool Instructions: Trex 600 Electric & NitroDocument3 pagesSwash Plate Leveling Tool Instructions: Trex 600 Electric & NitroEdinal BachtiarNo ratings yet

- CH 7b - Shift InstructionsDocument20 pagesCH 7b - Shift Instructionsapi-237335979100% (1)

- Value For Money Analysis.5.10.12Document60 pagesValue For Money Analysis.5.10.12Jason SanchezNo ratings yet