Professional Documents

Culture Documents

Data Sheet

Uploaded by

Manuel VillarOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Data Sheet

Uploaded by

Manuel VillarCopyright:

Available Formats

SDRAM 16Mb H-die(x16) CMOS SDRAM

16Mb H-die SDRAM Specification

Revision 1.5

August 2004

Samsung Electronics reserves the right to change products or specification without notice.

Rev. 1.5 August 2004

SDRAM 16Mb H-die(x16) CMOS SDRAM

Revision History

Revision 0.0 (May, 2003)

- Target spec release.

Revision 0.1 (October, 2003)

- Modified tRDL from 1CLK to 2CLK.

Revision 0.2 (October, 2003)

- Deleted AC parameter notes 5.

Revision 0.3 (October, 2003)

- Modified tRDL & deleted speed 200MHz.

Revision 1.0 (November, 2003)

- Revision 1.0 spec. release.

Revision 1.1 (December, 2003)

- Corrected PKG dimension.

Revision 1.2 (January, 2004)

- Deleted -10(10ns) speed.

- Modified load cap 50pF -> 30pF.

- Modified DC current .

Revision 1.3 (January, 2004)

- Corrected typo

Revision 1.4 (May, 2004)

- Added Note 8. sentense of tRDL parameter.

Revision 1.5 (August, 2004)

- Modified CLK cycle time(tcc) parameter in AC Characteristics.

( If you want use of CL=2 not CL=3, the maximum operating frequency is 100MHz regardless of its speed bin.)

Rev. 1.5 August 2004

SDRAM 16Mb H-die(x16) CMOS SDRAM

512K x 16Bit x 2 Banks SDRAM

FEATURES

• 3.3V power supply

• LVTTL compatible with multiplexed address

• two banks operation

• MRS cycle with address key programs

-. CAS Latency ( 2 & 3)

-. Burst Length (1, 2, 4, 8 & full page)

-. Burst Type (Sequential & Interleave)

• All inputs are sampled at the positive going edge of the system clock

• Burst Read Single-bit Write operation

• DQM for masking

• Auto & self refresh

• 32ms refresh period (2K cycle)

GENERAL DESCRIPTION

The K4S161622H is 16,777,216 bits synchronous high data rate Dynamic RAM organized as 2 x 524,288 words by 16 bits, fabricated

with SAMSUNG′s high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/

O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable laten-

cies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

ORDERING INFORMATION

Part NO. MAX Freq. Interface Package

K4S161622H-TC55 183MHz

K4S161622H-TC60 166MHz 50pin

LVTTL

K4S161622H-TC70 143MHz TSOP(II)

K4S161622H-TC80 125MHz

Organization Row Address Column Address

1Mx16 A0~A10 A0-A7

Row & Column address configuration

Rev. 1.5 August 2004

SDRAM 16Mb H-die(x16) CMOS SDRAM

Package Physical Dimension

0~8°

#50 #26 0.25 TYP

(0.50)

11.76±0.20

10.16 ± 0.10

± 0.20

(10.76)

11.76

#1 #25

(0.50)

0.125+0.075

-0.035

20.95 ± 0.10 1.20MAX 1.00 ± 0.10

0.10MAX

[ 0.075MAX ] 0.80TYP

(0.875) 0.30 +0.10

-0.05 0.35 +0.10

-0.05

[0.80±0.08] 0.05MIN

50Pin TSOP(II) Package Dimension

Rev. 1.5 August 2004

SDRAM 16Mb H-die(x16) CMOS SDRAM

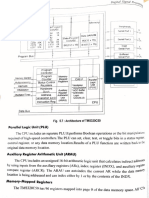

FUNCTIONAL BLOCK DIAGRAM

I/O Control

LWE

Data Input Register

Bank Select LDQM

Refresh Counter

Output Buffer

Row Decoder

Sense AMP

512K x 16

Row Buffer

DQi

Address Register

CLK 512K x 16

ADD

Column Decoder

LRAS

LCBR

Col. Buffer

Latency & Burst Length

LCKE

Programming Register

LRAS LCBR LWE LCAS LWCBR LDQM

Timing Register

CLK CKE CS RAS CAS WE L(U)DQM

* Samsung Electronics reserves the right to change products or specification without notice.

Rev. 1.5 August 2004

SDRAM 16Mb H-die(x16) CMOS SDRAM

PIN CONFIGURATION (TOP VIEW)

VDD 1 50 VSS

DQ0 2 49 DQ15

DQ1 3 48 DQ14

VSSQ 4 47 VSSQ

DQ2 5 46 DQ13

DQ3 6 45 DQ12

VDDQ 7 44 VDDQ

DQ4 8 43 DQ11

DQ5 9 42 DQ10

VSSQ 10 41 VSSQ

DQ6 11 40 DQ9

DQ7 12 39 DQ8

VDDQ 13 38 VDDQ

LDQM 14 37 N.C/RFU

WE 15 36 UDQM

CAS 16 35 CLK

RAS 17 34 CKE

CS 18 33 N.C

BA 19 32 A9

A10/AP 20 31 A8

A0 21 30 A7

A1 22 29 A6

A2 23 28 A5 50PIN TSOP (II)

A3 24 27 A4

(400mil x 825mil)

VDD 25 26 VSS

(0.8 mm PIN PITCH)

PIN FUNCTION DESCRIPTION

Pin Name Input Function

CLK System Clock Active on the positive going edge to sample all inputs.

Disables or enables device operation by masking or enabling all inputs except

CS Chip Select

CLK, CKE and L(U)DQM

Masks system clock to freeze operation from the next clock cycle.

CKE Clock Enable CKE should be enabled at least one cycle prior to new command.

Disable input buffers for power down in standby.

Row / column addresses are multiplexed on the same pins.

A0 ~ A10/AP Address

Row address : RA0 ~ RA10, column address : CA0 ~ CA7

Selects bank to be activated during row address latch time.

BA Bank Select Address

Selects bank for read/write during column address latch time.

Latches row addresses on the positive going edge of the CLK with RAS low.

RAS Row Address Strobe

Enables row access & precharge.

Latches column addresses on the positive going edge of the CLK with CAS low.

CAS Column Address Strobe

Enables column access.

Enables write operation and row precharge.

WE Write Enable

Latches data in starting from CAS, WE active.

Makes data output Hi-Z, tSHZ after the clock and masks the output.

L(U)DQM Data Input/Output Mask

Blocks data input when L(U)DQM active.

DQ0 ~ 15 Data Input/Output Data inputs/outputs are multiplexed on the same pins.

VDD/VSS Power Supply/Ground Power and ground for the input buffers and the core logic.

Isolated power supply and ground for the output buffers to provide improved noise

VDDQ/VSSQ Data Output Power/Ground

immunity.

No Connection/

N.C/RFU This pin is recommended to be left No Connection on the device.

Reserved for Future Use

Rev. 1.5 August 2004

SDRAM 16Mb H-die(x16) CMOS SDRAM

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Value Unit

Voltage on any pin relative to Vss VIN, VOUT -1.0 ~ 4.6 V

Voltage on VDD supply relative to Vss VDD, VDDQ -1.0 ~ 4.6 V

Storage temperature TSTG -55 ~ +150 °C

Power dissipation PD 1 W

Short circuit current IOS 50 mA

Note : Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

DC OPERATING CONDITIONS

Recommended operating conditions (Voltage referenced to VSS = 0V, TA = 0 to 70°C)

Parameter Symbol Min Typ Max Unit Note

Supply voltage VDD, VDDQ 3.0 3.3 3.6 V

Input logic high votlage VIH 2.0 3.0 VDDQ+0.3 V 1

Input logic low voltage VIL -0.3 0 0.8 V 2

Output logic high voltage VOH 2.4 - - V IOH = -2mA

Output logic low voltage VOL - - 0.4 V IOL = 2mA

Input leakage current ILI -10 - 10 uA 3

Note

: : 1. VIH (max) = 5.6V AC. The overshoot voltage duration is ≤ 3ns.

2. VIL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.

3. Any input 0V ≤ VIN ≤ VDDQ.

Input leakage currents include HI-Z output leakage for all bi-directional buffers with Tri-State outputs.

CAPACITANCE (VDD = 3.3V, TA = 23°C, f = 1MHz, VREF =1.4V ± 200 mV)

Pin Symbol Min Max Unit

Clock CCLK 2 4 pF

RAS, CAS, WE, CS, CKE, L(U)DQM CIN 2 4 pF

Address CADD 2 4 pF

DQ0 ~ DQ15 COUT 3 5 pF

Rev. 1.5 August 2004

SDRAM 16Mb H-die(x16) CMOS SDRAM

DC CHARACTERISTICS

(Recommended operating condition unless otherwise noted, TA = 0 to 70°C )

Version

Parameter Symbol Test Condition Unit Note

55 60 70 80

Burst Length =1

Operating Current

ICC1 tRC≥tRC(min) 120 115 105 95 mA 2

(One Bank Active)

Io = 0 mA

Precharge Standby Current in ICC2P CKE≤VIL(max), tCC = 10ns 2

mA

power-down mode ICC2PS CKE & CLK≤VIL(max), tCC = ∞ 2

CKE≥VIH(min), CS≥VIH(min), tCC = 10ns

ICC2N Input signals are changed one time during 15

Precharge Standby Current 30ns mA

in non power-down mode

CKE≥VIH(min), CLK≤VIL(max), tCC = ∞

ICC2NS 5

Input signals are stable

Active Standby Current ICC3P CKE≤VIL(max), tCC = 10ns 3

mA

in power-down mode ICC3PS CKE & CLK≤VIL(max), tCC = ∞ 3

CKE≥VIH(min), CS≥VIH(min), tCC = 10ns

Active Standby Current ICC3N Input signals are changed one time during 25 mA

in non power-down mode 30ns

(One Bank Active) CKE≥VIH(min), CLK≤VIL(max), tCC = ∞

ICC3NS 15 mA

Input signals are stable

Io = 0 mA

Operating Current

ICC4 Page Burst 2Banks Activated 155 150 140 130 mA 2

(Burst Mode)

tCCD = 2CLKs

Refresh Current ICC5 tRC≥tRC(min) 105 100 90 90 mA 3

Self Refresh Current ICC6 CKE≤0.2V 1 mA

Note : 1. Unless otherwise notes, Input level is CMOS(VIH/VIL=VDDQ/VSSQ) in LVTTL.

2. Measured with outputs open. Addresses are changed only one time during tcc(min).

3. Refresh period is 32ms. Addresses are changed only one time during tcc(min).

4. K4S161622H-TC

Rev. 1.5 August 2004

SDRAM 16Mb H-die(x16) CMOS SDRAM

AC OPERATING TEST CONDITIONS (VDD = 3.3V±0.3V, TA = 0 to 70°C)

Parameter Value Unit

Input levels (Vih/Vil) 2.4 / 0.4 V

Input timing measurement reference level 1.4 V

Input rise and fall time tr / tf = 1 / 1 ns

Output timing measurement reference level 1.4 V

Output load condition See Fig. 2

3.3V Vtt=1.4V

1200Ω 50Ω

VOH (DC) = 2.4V, IOH = -2mA

Output Output Z0=50Ω

VOL (DC) = 0.4V, IOL = 2mA

30pF 30pF

870Ω

(Fig. 1) DC Output Load Circuit (Fig. 2) AC Output Load Circuit

AC CHARACTERISTICS

(AC operating conditions unless otherwise noted)

55 60 70 80

Parameter Symbol Unit Note

Min Max Min Max Min Max Min Max

CAS Latency=3 5.5 6 7 8

CLK cycle time tCC 1000 1000 1000 1000 ns 1

CAS Latency=2 10 10 10 10

Row active to row active delay tRRD(min) 11 - 12 - 14 - 16 - ns

RAS to CAS delay tRCD(min) 16.5 - 18 - 20 - 20 - ns

Row precharge time tRP(min) 16.5 - 18 - 20 - 20 - ns

tRAS(min) 38.5 - 42 - 49 - 48 - ns

Row active time

tRAS(max) - 100 - 100 - 100 - 100 us

Row cycle time tRC(min) 55 - 60 - 69 - 70 - ns

Last data in to row precharge tRDL(min) 2 1 CLK 2,8

Last data in to new col.address delay tCDL(min) 1 CLK 2

Last data in to burst stop tBDL(min) 1 CLK 2

Col. address to col. address delay tCCD(min) 1 CLK

Mode Register Set cycle time tMRS(min) 2 CLK

Number of valid out- CAS Latency=3 2

ea 4

put data CAS Latency=2 1

Rev. 1.5 August 2004

SDRAM 16Mb H-die(x16) CMOS SDRAM

(AC operating conditions unless otherwise noted)

55 60 -70 -80

Parameter Symbol Unit Note

Min Max Min Max Min Max Min Max

CAS Latency=3 5.5 6 7 8

CLK cycle time tCC 1000 1000 1000 1000 ns 5

CAS Latency=2 10 10 10 10

CLK to valid CAS Latency=3 - 5 - 5.5 - 5.5 - 6

tSAC ns 5, 6

output delay CAS Latency=2 - 6 - 6 - 6 - 6

Output data tOH 2 - 2.5 - 2.5 - 2.5 - ns 6

CLK high pulse CAS Latency=3 2 2.5

tCH - - 3 - 3 - ns 7

width CAS Latency=2 3 3

CLK low pulse CAS Latency=3 2 2.5

tCL - - 3 - 3 - ns 7

width CAS Latency=2 3 3

CAS Latency=3 1.5 1.5 1.75

Input setup time tSS - - - 2 - ns 7

CAS Latency=2 2 2 2

Input hold time tSH 1 - 1 - 1 - 1 - ns 7

CLK to output in Low-Z tSLZ 1 - 1 - 1 - 1 - ns 6

CLK to output CAS Latency=3 - 5 - 5.5 - 5.5 - 6

tSHZ ns

in Hi-Z CAS Latency=2 - 6 - 6 - 6 - 6

Notes : 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and then

rounding off to the next higher integer. Refer to the following clock unit based AC conversion table

2. Minimum delay is required to complete write.

3. All parts allow every cycle column address change.

4. In case of row precharge interrupt, auto precharge and read burst stop.

5. Parameters depend on programmed CAS latency.

6. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

7. Assumed input rise and fall time (tr & tf)=1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

8. In 100MHz and below 100MHz operating conditions, tRDL=1CLK and tDAL=1CLK + 20ns is also supported.

SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + tRP.

Rev. 1.5 August 2004

SDRAM 16Mb H-die(x16) CMOS SDRAM

SIMPLIFIED TRUTH TABLE

COMMAND CKEn-1 CKEn CS RAS CAS WE DQM BA A10/AP A9~ A0 Note

Register Mode Register Set H X L L L L X OP CODE 1, 2

Auto Refresh H 3

H L L L H X X

Entry L 3

Refresh Self

L H H H 3

Refresh Exit L H X X

H X X X 3

Bank Active & Row Addr. H X L L H H X V Row Address

Read & Auto Precharge Disable L Column 4

Column Address H X L H L H X V Address

Auto Precharge Enable H 4, 5

Write & Auto Precharge Disable L Column 4

Column Address H X L H L L X V Address

Auto Precharge Enable H 4, 5

Burst Stop H X L H H L X X 6

Bank Selection V L

Precharge H X L L H L X X

Both Banks X H

H X X X

Clock Suspend or Entry H L X

L V V V X

Active Power Down

Exit L H X X X X X

H X X X

Entry H L X

L H H H

Precharge Power Down Mode X

H X X X

Exit L H X

L V V V

DQM H X V X 7

H X X X

No Operation Command H X X X

L H H H

(V=Valid, X=Don′t Care, H=Logic High, L=Logic Low)

Note : 1. OP Code : Operand Code

A0 ~ A10/AP, BA : Program keys. (@MRS)

2. MRS can be issued only at both banks precharge state.

A new command can be issued after 2 clock cycle of MRS.

3. Auto refresh functions are as same as CBR refresh of DRAM.

The automatical precharge without row precharge command is meant by "Auto".

Auto/self refresh can be issued only at both banks precharge state.

4. BA : Bank select address.

If "Low" at read, write, row active and precharge, bank A is selected.

If "High" at read, write, row active and precharge, bank B is selected.

If A10/AP is "High" at row precharge, BA is ignored and both banks are selected.

5. During burst read or write with auto precharge, new read/write command can not be issued.

Another bank read/write command can be issued after the end of burst.

New row active of the assoiated bank can be issued at tRP after the end of burst.

6. Burst stop command is valid at every burst length.

7. DQM sampled at positive going edge of a CLK masks the data-in at the very CLK (Write DQM latency is 0),

but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)

Rev. 1.5 August 2004

You might also like

- DEUTZ Service Engine Electronic PDFDocument2 pagesDEUTZ Service Engine Electronic PDFEdwin Alfonso Hernandez MontesNo ratings yet

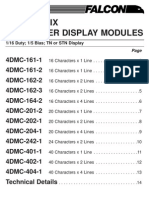

- 4 DMCDocument20 pages4 DMCapi-3700809100% (1)

- Microprocessor Architectures and Systems: RISC, CISC and DSPFrom EverandMicroprocessor Architectures and Systems: RISC, CISC and DSPRating: 4 out of 5 stars4/5 (1)

- Sb5101 Samsung UpgradeDocument14 pagesSb5101 Samsung Upgradejohnny-lawless3277No ratings yet

- K4S561632EDocument15 pagesK4S561632ELelik GhhNo ratings yet

- 256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Document14 pages256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Cường MchwNo ratings yet

- 64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632KDocument14 pages64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632KCường MchwNo ratings yet

- 64Mb H-Die (x32) SDRAM Specification: Revision 1.3 February 2004Document12 pages64Mb H-Die (x32) SDRAM Specification: Revision 1.3 February 2004Luis AntunesNo ratings yet

- 013 - k4s64xx32n - Rev111 RAM DinámicaDocument15 pages013 - k4s64xx32n - Rev111 RAM DinámicanachcratchNo ratings yet

- Iiic - CC: 128Mb K-Die SDRAM SpecificationDocument15 pagesIiic - CC: 128Mb K-Die SDRAM SpecificationTan Hung LuuNo ratings yet

- Bu 9348 KDocument3 pagesBu 9348 KbinkyfishNo ratings yet

- 100 Base-T Single Port Transformer Module: Electrical Specifications at 25Document1 page100 Base-T Single Port Transformer Module: Electrical Specifications at 25Виктор АгарковNo ratings yet

- HX426C16FB3/16 HX426C16FB3/16: Memory Module SpecificationsDocument2 pagesHX426C16FB3/16 HX426C16FB3/16: Memory Module Specificationsjesusvillegas0No ratings yet

- 10/100 PC Card LAN Magnetic Modules: MechanicalsDocument2 pages10/100 PC Card LAN Magnetic Modules: MechanicalsAbdelrhman ElsayedNo ratings yet

- HX426C16FB2K2/16 HX426C16FB2K2/16: Memory Module SpecificationsDocument2 pagesHX426C16FB2K2/16 HX426C16FB2K2/16: Memory Module SpecificationsIfrit RaynskiiNo ratings yet

- HX430C15PB3 8 PDFDocument2 pagesHX430C15PB3 8 PDFAndrei NeaguNo ratings yet

- HX426C16FB2/8 HX426C16FB2/8: Memory Module SpecificationsDocument2 pagesHX426C16FB2/8 HX426C16FB2/8: Memory Module SpecificationsПавло ОсейкоNo ratings yet

- Panasonic35864 1-2279834Document2 pagesPanasonic35864 1-2279834Americo AndresNo ratings yet

- Renesas Electronics R7F0E01xxxxxx (RE0 Series) Matching Data: SC-32S SC-20S SC-16S SC-12SDocument2 pagesRenesas Electronics R7F0E01xxxxxx (RE0 Series) Matching Data: SC-32S SC-20S SC-16S SC-12SafdgtdsghfNo ratings yet

- KVR24N17S8K2 16 PDFDocument2 pagesKVR24N17S8K2 16 PDFJuan David Gutierrez JimenezNo ratings yet

- KVR24N17S8K2/16: Memory Module Specifi CationsDocument2 pagesKVR24N17S8K2/16: Memory Module Specifi CationsJuan David Gutierrez JimenezNo ratings yet

- HX426C16FB/16 HX426C16FB/16: Memory Module SpecificationsDocument2 pagesHX426C16FB/16 HX426C16FB/16: Memory Module SpecificationsPușcă MartinNo ratings yet

- 步进电机详细参数资料Document13 pages步进电机详细参数资料Andy YouQuanTexNo ratings yet

- G2401ce PDFDocument1 pageG2401ce PDFFatih UnalNo ratings yet

- Led2 1.2Document12 pagesLed2 1.2EduardoNo ratings yet

- BP26 12Document1 pageBP26 12zakaria alhosinyNo ratings yet

- Adam27Pxx: User'S ManualDocument37 pagesAdam27Pxx: User'S ManualMihail MateiNo ratings yet

- HX432C16FB3 8Document2 pagesHX432C16FB3 8GetlozzAwabaNo ratings yet

- 14PM M201V NMBDocument1 page14PM M201V NMBCristianEnacheNo ratings yet

- RAM 32GB (3200MHz) - HX432C16PB3A - 32Document2 pagesRAM 32GB (3200MHz) - HX432C16PB3A - 32Luis Godoy FuentesNo ratings yet

- KVR667D2N5K2 2GDocument1 pageKVR667D2N5K2 2GetendardNo ratings yet

- 12GB (3X4GB) - 3SH13339R5H-12GT Features: Figure 1: Available ProfileDocument1 page12GB (3X4GB) - 3SH13339R5H-12GT Features: Figure 1: Available ProfileAyman SeaudiNo ratings yet

- Revisions: Amphenol Part Number Confuguration UE86-G1636-00X3TDocument3 pagesRevisions: Amphenol Part Number Confuguration UE86-G1636-00X3Tkkk ghgfhgfNo ratings yet

- KTLP 3616Document10 pagesKTLP 3616Ismael silvaNo ratings yet

- TS12864c-5 YGDocument13 pagesTS12864c-5 YGHéctor Eduardo Urbina UrbinaNo ratings yet

- HM Rae001Document4 pagesHM Rae001MecPlayzNo ratings yet

- Hdlx-2416 Series: Data SheetDocument17 pagesHdlx-2416 Series: Data SheetJuvenal Copa perezNo ratings yet

- KF426C16BB 8Document2 pagesKF426C16BB 8cacuNo ratings yet

- BDX 94Document1 pageBDX 94Jadi PurwonoNo ratings yet

- HX432C16FB3K2/16 HX432C16FB3K2/16: Memory Module SpecificationsDocument2 pagesHX432C16FB3K2/16 HX432C16FB3K2/16: Memory Module SpecificationsYudi Eko SaputroNo ratings yet

- ADAM27P16GDocument39 pagesADAM27P16GDaniel Alejandro Torres SanabriaNo ratings yet

- Option: 6800, SPI, I C Interface: 128x64 DotsDocument1 pageOption: 6800, SPI, I C Interface: 128x64 Dotsnildo137 SANTOSNo ratings yet

- SunonDocument4 pagesSunonEmerson Müller Juarez AvilaNo ratings yet

- HX429C15PB3A/8 HX429C15PB3A/8: Memory Module SpecificationsDocument2 pagesHX429C15PB3A/8 HX429C15PB3A/8: Memory Module SpecificationsMacraméNo ratings yet

- Midas Gen: 1. Design InformationDocument56 pagesMidas Gen: 1. Design InformationNyx Phoebe WPNo ratings yet

- KVR24N17S8/4: Memory Module Specifi CationsDocument2 pagesKVR24N17S8/4: Memory Module Specifi CationsGeepee FloresNo ratings yet

- KHX3200A 1gDocument2 pagesKHX3200A 1gOvidiu VranceanuNo ratings yet

- LA1787MDocument54 pagesLA1787MAgus BrewsNo ratings yet

- KVR24N17D8/16: Memory Module Specifi CationsDocument2 pagesKVR24N17D8/16: Memory Module Specifi CationseleptonNo ratings yet

- KTLP3616 COSMOElectronicsCorporationDocument10 pagesKTLP3616 COSMOElectronicsCorporationaltakadum78No ratings yet

- CHF190104xBF Series 800 W Power RF Flanged Chip Termination/ResistorDocument1 pageCHF190104xBF Series 800 W Power RF Flanged Chip Termination/ResistorMPIMLACNo ratings yet

- ECS RS880PM-AM Rev 1.0 СхемаDocument37 pagesECS RS880PM-AM Rev 1.0 СхемаA2139No ratings yet

- Astec DC-DC ConverterDocument2 pagesAstec DC-DC Convertercountry boyNo ratings yet

- High Performance CMOS 5 X 7 Alphanumeric Displays: Technical DataDocument16 pagesHigh Performance CMOS 5 X 7 Alphanumeric Displays: Technical DataEmanuel OanceaNo ratings yet

- Kf432c16bba 16Document2 pagesKf432c16bba 16jesusmgtz81No ratings yet

- RDamper CatalogDocument12 pagesRDamper CatalogEvandro MoreiraNo ratings yet

- WL0F0005Document9 pagesWL0F0005LIFT LIFTNo ratings yet

- MR301 NECElectronicsDocument12 pagesMR301 NECElectronicsFrancisco Palacios LópezNo ratings yet

- End of Life Product Not Recommended For New Design: RotationDocument1 pageEnd of Life Product Not Recommended For New Design: RotationEdwin David Tamayo AlzateNo ratings yet

- 2SA1015Document2 pages2SA1015Thi NguyễnNo ratings yet

- PDM360 NG Repacking 04 GBDocument6 pagesPDM360 NG Repacking 04 GBedsonbdasilvajuniorNo ratings yet

- 05-PV1800 ProDocument1 page05-PV1800 ProEla Suyapa Valladares AlvarengaNo ratings yet

- Microprocessor and Microcontroller Assignment: Physical Address Generation 8086Document9 pagesMicroprocessor and Microcontroller Assignment: Physical Address Generation 8086Manish NegiNo ratings yet

- Microcontrolador FujitsuDocument40 pagesMicrocontrolador FujitsuCarlos IbaNo ratings yet

- Samsung LN52C530F1XZA Fast Track Guide (SM)Document4 pagesSamsung LN52C530F1XZA Fast Track Guide (SM)Carlos OdilonNo ratings yet

- BRKSPG 2280Document44 pagesBRKSPG 2280ali partoviNo ratings yet

- Lab 2 RCDocument4 pagesLab 2 RCnguyenvietNo ratings yet

- Wiring Golf Jetta Bora 2.0 2.5Document739 pagesWiring Golf Jetta Bora 2.0 2.5Gerardo Frias GarciaNo ratings yet

- Buc Fet 11314LDocument2 pagesBuc Fet 11314LAltab HussainNo ratings yet

- RGBDuino ManualDocument35 pagesRGBDuino ManualEddy Sorrowful Eyes100% (1)

- Ultra Low Power Design of Full Adder Circuit Using Adiabatic Logic TechniquesDocument13 pagesUltra Low Power Design of Full Adder Circuit Using Adiabatic Logic TechniquesIJRASETPublicationsNo ratings yet

- Tms320c50 ProcessorDocument11 pagesTms320c50 ProcessorKarpagamNo ratings yet

- Embedded Firmware (Unit - Iii)Document18 pagesEmbedded Firmware (Unit - Iii)jonnyNo ratings yet

- STM32L010C6T6Document90 pagesSTM32L010C6T6Abhijit GhoshNo ratings yet

- 5 - Power TweaksDocument9 pages5 - Power TweaksLucasNo ratings yet

- Data Structures Using C++ by DR Varsha Patil: Oxford University Press © 2012Document49 pagesData Structures Using C++ by DR Varsha Patil: Oxford University Press © 2012Maria LavanyaNo ratings yet

- Basics of NetworkingDocument20 pagesBasics of Networkinglloyd jason VicenteNo ratings yet

- Coaxial Cables: Types of Computer Network CablesDocument9 pagesCoaxial Cables: Types of Computer Network CablesedrisNo ratings yet

- Lecture 15 - Radio Transmitters and ReceiversDocument15 pagesLecture 15 - Radio Transmitters and Receiversnabeel hasanNo ratings yet

- Parallel ATA Interface Reference Design Guide - V0 1 PDFDocument13 pagesParallel ATA Interface Reference Design Guide - V0 1 PDFRicardo Palafox Mejia0% (1)

- Matrix of Library EquipmentDocument3 pagesMatrix of Library EquipmentMary Joyce AbrahamNo ratings yet

- Can You Charge Bluetooth Headphones While UsingDocument6 pagesCan You Charge Bluetooth Headphones While UsingheadphoneticofficialNo ratings yet

- Net2-2-Network ភាសាខ្មែរDocument155 pagesNet2-2-Network ភាសាខ្មែរSambath MuchNo ratings yet

- What Are Diodes and What Are They Used For?: Basic KnowledgeDocument3 pagesWhat Are Diodes and What Are They Used For?: Basic KnowledgeManohar GarimellaNo ratings yet

- CCBoot Manual - Advanced Diskless Boot ClientDocument23 pagesCCBoot Manual - Advanced Diskless Boot ClientHasnan IbrahimNo ratings yet

- DVR EZ Pro Instructions PDFDocument88 pagesDVR EZ Pro Instructions PDFremeenNo ratings yet

- Oppo Xiaomi Resmi Tam: HP Bebas Sinyal - PulsaDocument1 pageOppo Xiaomi Resmi Tam: HP Bebas Sinyal - Pulsatommy peggyNo ratings yet

- Wa0076Document2 pagesWa0076Mohamad BadranNo ratings yet

- Centro de Soporte de Hpe: Hpe Proliant Servers - Hpasmcli CommandsDocument2 pagesCentro de Soporte de Hpe: Hpe Proliant Servers - Hpasmcli CommandsRAUL MORONNo ratings yet