Professional Documents

Culture Documents

128Mb K-die SDRAM Specification

Uploaded by

Tan Hung LuuOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

128Mb K-die SDRAM Specification

Uploaded by

Tan Hung LuuCopyright:

Available Formats

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

128Mb K-die SDRAM Specification

54 TSOP-II with Pb-Free & Halogen-Free

(RoHS compliant)

IIIC.CC

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,

AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,

EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL

INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar

applications where Product failure couldresult in loss of life or personal or physical harm, or any military or

defense application, or any governmental procurement to which special terms or provisions may apply.

* Samsung Electronics reserves the right to change products or specification without notice.

1 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

Table of Contents

1.0 FEATURES .................................................................................................................................... 4

2.0 GENERAL DESCRIPTION ............................................................................................................ 4

3.0 Ordering Information ................................................................................................................... 4

4.0 Package Physical Dimension ..................................................................................................... 5

5.0 FUNCTIONAL BLOCK DIAGRAM ................................................................................................ 6

6.0 PIN CONFIGURATION (Top view) ............................................................................................. 7

7.0 PIN FUNCTION DESCRIPTION .................................................................................................... 7

8.0 ABSOLUTE MAXIMUM RATINGS ............................................................................................... 8

9.0 DC OPERATING CONDITIONS .................................................................................................... 8

10.0 CAPACITANCE ........................................................................................................................... 8

11.0 DC CHARACTERISTICS (x4, x8) ............................................................................................... 9

12.0 DC CHARACTERISTICS (x16) ................................................................................................. 10

13.0 AC OPERATING TEST CONDITIONS ...................................................................................... 11

14.0 OPERATING AC PARAMETER ................................................................................................ 11

15.0 AC CHARACTERISTICS .......................................................................................................... 12

16.0 DQ BUFFER OUTPUT DRIVE CHARACTERISTICS ............................................................... 12

17.0 IBIS SPECIFICATION ............................................................................................................... 13

18.0 SIMPLIFIED TRUTH TABLE ..................................................................................................... 15

2 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

Revision History

Revision Month Year History

1.0 February 2007 - Release revision 1.0 SPEC

- Revised typo of package dimension

1.1 November 2007

- Added the comment of Halogen-free supporting

1.2 February 2008 - Added -50 bin(200MHz) DRAM

3 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

8M x 4Bit x 4 / 4M x 8Bit x 4 Banks / 2M x 16Bit x 4 Banks SDRAM

1.0 FEATURES

• JEDEC standard 3.3V power supply

• LVTTL compatible with multiplexed address

• Four banks operation

• MRS cycle with address key programs

-. CAS latency (2 & 3)

-. Burst length (1, 2, 4, 8 & Full page)

-. Burst type (Sequential & Interleave)

• All inputs are sampled at the positive going edge of the system clock.

• Burst read single-bit write operation

• DQM (x8) & L(U)DQM (x16) for masking

• Auto & self refresh

• 64ms refresh period (4K Cycle)

• 54pin TSOP II Pb-Free and Halogen-Free package

• RoHS compliant

2.0 GENERAL DESCRIPTION

The K4S280432K / K4S280832K / K4S281632K is 134,217,728 bits synchronous high data rate Dynamic RAM organized as 4 x

2,097,152 words by 4 bits / 4 x 4,194,304 words by 8 bits / 4 x 2,097,152 words by 16 bits, fabricated with SAMSUNG′s high perfor-

mance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible

on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to

be useful for a variety of high bandwidth, high performance memory system applications.

3.0 Ordering Information

Part No. Orgainization Max Freq. Interface Package

K4S280432K-U *1C/L75 32Mb x 4 133MHz (CL=3)

K4S280832K-UC/L75 16Mb x 8 133MHz (CL=3) 54pin TSOP(II)

K4S281632K-UC/L50 8Mb x 16 200MHz(CL=3) LVTTL Pb-free & Halogen-free*1

K4S281632K-UC/L60 8Mb x 16 166MHz (CL=3)

K4S281632K-UC/L75 8Mb x 16 133MHz (CL=3)

Note 1 : 128Mb K-die SDR DRAMs support Pb-free & Halogen-free package with Pb-free package code(-U).

Organization Row Address Column Address

16Mx8 A0~A11 A0-A9

8Mx16 A0~A11 A0-A8

Row & Column address configuration

4 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

4.0 Package Physical Dimension

Unit : mm

(0.80)

(0.50)

#54 #28

11.76 ± 0.20

10.16 ± 0.10

(10.76)

(10°)

(10°)

(1.50)

#1 #27

(0.80)

(0.50)

(1.50)

+0.075

0.665 ± 0.05

0.210 ± 0.05

22.22 ± 0.10 0.125 - 0.035

1.00 ± 0.10

1.20 MAX

(R

0.1 (10°)

5)

0.45 ~ 0.75

0.10 MAX

(4°)

0.05 MIN

)

[

15

(10°) [

0.

0.80TYP +0.10

0.075 MAX

(R

(0.71) [0.80 ± 0.08] 0.35 - 0.05

)

25

25

0.

0.

(R

(R

0.25TYP

NOTE

1. ( ) IS REFERENCE

2. [ ] IS ASS’Y OUT QUALITY

(0° ∼ 8°)

54Pin TSOP(II) Package Dimension

5 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

5.0 FUNCTIONAL BLOCK DIAGRAM

I/O Control

LWE

Data Input Register

LDQM

Bank Select

8M x 4 / 4M x 8 / 2M x 16

Refresh Counter

Output Buffer

Row Decoder

Sense AMP

Row Buffer

8M x 4 / 4M x 8 / 2M x 16

DQi

Address Register

8M x 4 / 4M x 8 / 2M x 16

CLK

8M x 4 / 4M x 8 / 2M x 16

ADD

Column Decoder

LRAS

LCBR

Col. Buffer

Latency & Burst Length

LCKE

Programming Register

LRAS LCBR LWE LCAS LWCBR LDQM

Timing Register

CLK CKE CS RAS CAS WE L(U)DQM

* Samsung Electronics reserves the right to change products or specification without notice.

6 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

6.0 PIN CONFIGURATION (Top view)

x16 x8 x4 x4 x8 x16

VDD VDD VDD 1 54 VSS VSS VSS

DQ0 DQ0 N.C 2 53 N.C DQ7 DQ15

VDDQ VDDQ VDDQ 3 52 VSSQ VSSQ VSSQ

DQ1 N.C N.C 4 51 N.C N.C DQ14

DQ2 DQ1 DQ0 5 50 DQ3 DQ6 DQ13

VSSQ VSSQ VSSQ 6 49 VDDQ VDDQ VDDQ

DQ3 N.C N.C 7 48 N.C N.C DQ12

DQ4 DQ2 N.C 8 47 N.C DQ5 DQ11

VDDQ VDDQ VDDQ 9 46 VSSQ VSSQ VSSQ

DQ5 N.C N.C 10 45 N.C N.C DQ10

DQ6 DQ3 DQ1 11 44 DQ2 DQ4 DQ9

VSSQ VSSQ VSSQ 12 43 VDDQ VDDQ VDDQ

DQ7 N.C N.C 13 42 N.C N.C DQ8

VDD VDD VDD 14 41 VSS VSS VSS

LDQM N.C N.C 15 40 N.C/RFU N.C/RFU N.C/RFU

WE WE WE 16 39 DQM DQM UDQM

CAS CAS CAS 17 38 CLK CLK CLK

RAS RAS RAS 18 37 CKE CKE CKE

CS CS CS 19 36 N.C N.C N.C

BA0 BA0 BA0 20 35 A11 A11 A11

BA1 BA1 BA1 21 34 A9 A9 A9

A10/AP A10/AP A10/AP 22 33 A8 A8 A8

A0 A0 A0 23 32 A7 A7 A7

A1 A1 A1 24 31 A6 A6 A6

A2 A2 A2 25 30 A5 A5 A5

A3 A3 A3 26 29 A4 A4 A4 54Pin TSOP

VDD VDD VDD 27 28 VSS VSS VSS (400mil x 875mil)

(0.8 mm Pin pitch)

7.0 PIN FUNCTION DESCRIPTION

Pin Name Input Function

CLK System clock Active on the positive going edge to sample all inputs.

Disables or enables device operation by masking or enabling all inputs except

CS Chip select

CLK, CKE and DQM

Masks system clock to freeze operation from the next clock cycle.

CKE Clock enable CKE should be enabled at least one cycle prior to new command.

Disable input buffers for power down in standby.

Row/column addresses are multiplexed on the same pins.

A0 ~ A11 Address Row address : RA0 ~ RA11,

Column address : (x4 : CA0 ~ CA9,CA11), (x8 : CA0 ~ CA9), (x16 : CA0 ~ CA8)

Selects bank to be activated during row address latch time.

BA0 ~ BA1 Bank select address

Selects bank for read/write during column address latch time.

Latches row addresses on the positive going edge of the CLK with RAS low.

RAS Row address strobe

Enables row access & precharge.

Latches column addresses on the positive going edge of the CLK with CAS low.

CAS Column address strobe

Enables column access.

Enables write operation and row precharge.

WE Write enable

Latches data in starting from CAS, WE active.

Makes data output Hi-Z, tSHZ after the clock and masks the output.

DQM Data input/output mask

Blocks data input when DQM active.

Data inputs/outputs are multiplexed on the same pins.

DQ0 ~ N Data input/output

(x4 : DQ0 ~ 3), (x8 : DQ0 ~ 7), (x16 : DQ0 ~ 15)

VDD/VSS Power supply/ground Power and ground for the input buffers and the core logic.

Isolated power supply and ground for the output buffers to provide improved noise

VDDQ/VSSQ Data output power/ground

immunity.

No connection

N.C/RFU This pin is recommended to be left No Connection on the device.

/reserved for future use

7 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

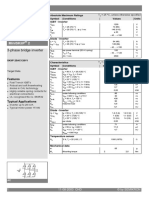

8.0 ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Value Unit

Voltage on any pin relative to Vss VIN, VOUT -1.0 ~ 4.6 V

Voltage on VDD supply relative to Vss VDD, VDDQ -1.0 ~ 4.6 V

Storage temperature TSTG -55 ~ +150 °C

Power dissipation PD 1 W

Short circuit current IOS 50 mA

Note : Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

9.0 DC OPERATING CONDITIONS

Recommended operating conditions (Voltage referenced to VSS = 0V, TA = 0 to 70°C)

Parameter Symbol Min Typ Max Unit Note

Supply voltage VDD, VDDQ 3.0 3.3 3.6 V

Input logic high voltage VIH 2.0 3.0 VDD+0.3 V 1

Input logic low voltage VIL -0.3 0 0.8 V 2

Output logic high voltage VOH 2.4 - - V IOH = -2mA

Output logic low voltage VOL - - 0.4 V IOL = 2mA

Input leakage current ILI -10 - 10 uA 3

Notes : 1. VIH (max) = 5.6V AC. The overshoot voltage duration is ≤ 3ns.

2. VIL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.

3. Any input 0V ≤ VIN ≤ VDDQ.

Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State outputs.

10.0 CAPACITANCE (VDD = 3.3V, TA = 23°C, f = 1MHz, VREF =1.4V ± 200 mV)

Pin Symbol Min Max Unit

Clock CCLK 2.5 3.5 pF

RAS, CAS, WE, CS, CKE, DQM CIN 2.5 3.8 pF

Address CADD 2.5 3.8 pF

(x4 : DQ0 ~ DQ3), (x8 : DQ0 ~ DQ7), (x16 : DQ0 ~ DQ15) COUT 4.0 6.0 pF

8 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

11.0 DC CHARACTERISTICS (x4, x8) (Recommended operating condition unless otherwise noted, TA = 0 to 70°C)

Version

Parameter Symbol Test Condition Unit Note

75

Burst length = 1

Operating current

ICC1 tRC ≥ tRC(min) 90 mA 1

(One bank active)

IO = 0 mA

Precharge standby current in ICC2P CKE ≤ VIL(max), tCC = 10ns 2

mA

power-down mode ICC2PS CKE & CLK ≤ VIL(max), tCC = ∞ 2

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

ICC2N 20

Precharge standby current in Input signals are changed one time during 20ns

mA

non power-down mode CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

ICC2NS 10

Input signals are stable

Active standby current in ICC3P CKE ≤ VIL(max), tCC = 10ns 5

mA

power-down mode ICC3PS CKE & CLK ≤ VIL(max), tCC = ∞ 5

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

Active standby current in ICC3N 30 mA

Input signals are changed one time during 20ns

non power-down mode

(One bank active) CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

ICC3NS 25 mA

Input signals are stable

Operating current IO = 0 mA

ICC4 110 mA 1

(Burst mode) Page burst

Refresh current ICC5 tRC ≥ tRC(min) 200 mA 2

C 2 mA 3

Self refresh current ICC6 CKE ≤ 0.2V

L 800 uA 4

Notes : 1. Measured with outputs open.

2. Refresh period is 64ms.

3. K4S280832K-UC

4. K4S280832K-UL

5. Unless otherwise noted, input swing IeveI is CMOS(VIH /VIL=VDDQ/VSSQ)

9 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

12.0 DC CHARACTERISTICS (x16) (Recommended operating condition unless otherwise noted, TA = 0 to 70°C)

Version

Parameter Symbol Test Condition Unit Note

50 60 75

Burst length = 1

Operating current

ICC1 tRC ≥ tRC(min) 140 130 100 mA 1

(One bank active)

IO = 0 mA

Precharge standby current in ICC2P CKE ≤ VIL(max), tCC = 10ns 2

mA

power-down mode ICC2PS CKE & CLK ≤ VIL(max), tCC = ∞ 2

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

ICC2N 20

Precharge standby current in Input signals are changed one time during 20ns

mA

non power-down mode CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

ICC2NS 10

Input signals are stable

Active standby current in ICC3P CKE ≤ VIL(max), tCC = 10ns 5

mA

power-down mode ICC3PS CKE & CLK ≤ VIL(max), tCC = ∞ 5

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

Active standby current in ICC3N 30 mA

Input signals are changed one time during 20ns

non power-down mode

(One bank active) CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞ 25

ICC3NS mA

Input signals are stable

IO = 0 mA

Operating current

ICC4 Page burst 4Banks Activated 160 150 140 mA 1

(Burst mode)

tCCD = 2CLKs

Refresh current ICC5 tRC ≥ tRC(min) 230 220 200 mA 2

C 2 mA 3

Self refresh current ICC6 CKE ≤ 0.2V

L 800 uA 4

Notes : 1. Measured with outputs open.

2. Refresh period is 64ms.

3. K4S281632K-UC

4. K4S281632K-UL

5. Unless otherwise noted, input swing IeveI is CMOS(VIH /VIL=VDDQ/VSSQ)

10 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

13.0 AC OPERATING TEST CONDITIONS (VDD = 3.3V ± 0.3V, TA = 0 to 70°C)

Parameter Value Unit

Input levels (Vih/Vil) 2.4/0.4 V

Input timing measurement reference level 1.4 V

Input rise and fall time tr/tf = 1/1 ns

Output timing measurement reference level 1.4 V

Output load condition See Fig. 2

3.3V Vtt = 1.4V

1200Ω 50Ω

VOH (DC) = 2.4V, IOH = -2mA

Output Output Z0 = 50Ω

VOL (DC) = 0.4V, IOL = 2mA

50pF 50pF

870Ω

(Fig. 1) DC output load circuit (Fig. 2) AC output load circuit

14.0 OPERATING AC PARAMETER (AC operating conditions unless otherwise noted)

Version

Parameter Symbol Unit

50 (x16 only) 60 (x16 only) 75

Row active to row active delay tRRD(min) 10 12 15 ns

RAS to CAS delay tRCD(min) 15 18 20 ns

Row precharge time tRP(min) 15 18 20 ns

tRAS(min) 40 42 45 ns

Row active time

tRAS(max) 100 us

Row cycle time tRC(min) 55 60 65 ns

Last data in to row precharge tRDL(min) 2 CLK

Last data in to Active delay tDAL(min) 2 CLK + tRP -

Last data in to new col. address delay tCDL(min) 1 CLK

Last data in to burst stop tBDL(min) 1 CLK

Col. address to col. address delay tCCD(min) 1 CLK

CAS latency=3 2

Number of valid output data ea

CAS latency=2 - 1

Notes : 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and then rounding off to the

next higher integer.

2. Minimum delay is required to complete write.

3. All parts allow every cycle column address change.

4. In case of row precharge interrupt, auto precharge and read burst stop.

5. In 100MHz and below 100MHz operating conditions, tRDL=1CLK and tDAL=1CLK + 20ns is also supported.

SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + tRP.

6. tRC =tRFC, tRDL = tWR.

11 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

15.0 AC CHARACTERISTICS (AC operating conditions unless otherwise noted)

50 (x16 only) 60 (x16 only) 75

Parameter Symbol

Min Max Min Max Min Max

CAS latency=3 5 6 7.5

CLK cycle time tCC 1000 1000 1000

CAS latency=2 - - 10

CLK to valid CAS latency=3 - 4.5 5 5.4

tSAC

output delay CAS latency=2 - - - 6

Output data CAS latency=3 2 - 2.5 3

tOH

hold time CAS latency=2 - - - 3

CLK high pulse width tCH 2 - 2.5 2.5

CLK low pulse width tCL 2 - 2.5 2.5

Input setup time tSS 1.5 - 1.5 1.5

Input hold time tSH 1 - 1 0.8

CLK to output in Low-Z tSLZ 1 - 1 1

CLK to output CAS latency=3 - 4.5 5 5.4

tSHZ

in Hi-Z CAS latency=2 - - - 6

Notes : 1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

3. Assumed input rise and fall time (tr & tf) = 1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

4. tSS applies for address setup time, clock enable setup time, commend setup time and data setup time

tSH applies for address holde time, clock enable hold time, commend hold time and data hold time

16.0 DQ BUFFER OUTPUT DRIVE CHARACTERISTICS

Parameter Symbol Condition Min Typ Max Unit Notes

Measure in linear

Output rise time trh 1.37 4.37 Volts/ns 3

region : 1.2V ~ 1.8V

Measure in linear

Output fall time tfh 1.30 3.8 Volts/ns 3

region : 1.2V ~ 1.8V

Measure in linear

Output rise time trh 2.8 3.9 5.6 Volts/ns 1,2

region : 1.2V ~ 1.8V

Measure in linear

Output fall time tfh 2.0 2.9 5.0 Volts/ns 1,2

region : 1.2V ~ 1.8V

Notes : 1. Rise time specification based on 0pF + 50 Ω to VSS, use these values to design to.

2. Fall time specification based on 0pF + 50 Ω to VDD, use these values to design to.

3. Measured into 50pF only, use these values to characterize to.

4. All measurements done with respect to VSS.

12 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

17.0 IBIS SPECIFICATION

IOH Characteristics (Pull-up) 200MHz/166MHz /133MHz Pull-up

200MHz 200MHz

0 0.5 1 1.5 2 2.5 3 3.5

166MHz 166MHz

Voltage 0

133MHz 133MHz

Min Max

(V) I (mA) I (mA) -100

3.45 -2.4

3.3 -27.3

-200

3.0 0.0 -74.1

2.6 -21.1 -129.2

mA

2.4 -34.1 -153.3 -300

2.0 -58.7 -197.0

1.8 -67.3 -226.2

-400

1.65 -73.0 -248.0

1.5 -77.9 -269.7

1.4 -80.8 -284.3 -500

1.0 -88.6 -344.5

0.0 -93.0 -502.4

-600

Voltage

IOH Min (200MHz/166MHz/133MHz)

IOH Max (200MHz/166MHz/133MHz)

IOL Characteristics (Pull-down)

200MHz/166MHz /133MHz Pull-down

200MHz 200MHz

166MHz 166MHz

Voltage 250

133MHz 133MHz

Min Max

(V) I (mA) I (mA)

200

0.0 0.0 0.0

0.4 27.5 70.2

0.65 41.8 107.5

150

0.85 51.6 133.8

mA

1.0 58.0 151.2

1.4 70.7 187.7

100

1.5 72.9 194.4

1.65 75.4 202.5

1.8 77.0 208.6

50

1.95 77.6 212.0

3.0 80.3 219.6

3.45 81.4 222.6

0

0 0.5 1 1.5 2 2.5 3 3.5

Voltage

IOH Min (200MHz/166MHz/133MHz)

IOH Max (200MHz/166MHz/133MHz)

13 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

Minimum VDD clamp current

VDD Clamp @ CLK, CKE, CS, DQM & DQ (Referenced to VDD)

VDD (V) I (mA)

20

0.0 0.0

0.2 0.0

0.4 0.0

0.6 0.0 15

0.7 0.0

0.8 0.0

0.9 0.0

1.0 0.23 10

mA

1.2 1.34

1.4 3.02

1.6 5.06

1.8 7.35 5

2.0 9.83

2.2 12.48

2.4 15.30

0

2.6 18.31

0 1 2 3

Voltage

I (mA)

Minimum VSS clamp current

VSS Clamp @ CLK, CKE, CS, DQM & DQ

-3 -2 -1 0

VSS (V) I (mA)

-2.6 -57.23 0

-2.4 -45.77

-2.2 -38.26 -10

-2.0 -31.22

-1.8 -24.58

-1.6 -18.37 -20

-1.4 -12.56

-1.2 -7.57 -30

mA

-1.0 -3.37

-0.9 -1.75

-0.8 -0.58 -40

-0.7 -0.05

-0.6 0.0 -50

-0.4 0.0

-0.2 0.0

-60

0.0 0.0

Voltage

I (mA)

14 of 15 Rev. 1.2 February 2008

K4S280432K

K4S280832K

K4S281632K Synchronous DRAM

18.0 SIMPLIFIED TRUTH TABLE (V=Valid, X=Don′t care, H=Logic high, L=Logic low)

A0 ~ A9,

Command CKEn-1 CKEn CS RAS CAS WE DQM BA0,1 A10/AP Note

A11,

Register Mode register set H X L L L L X OP code 1,2

Auto refresh H 3

H L L L H X X

Entry L 3

Refresh Self

L H H H 3

refresh Exit L H X X

H X X X 3

Bank active & row addr. H X L L H H X V Row address

Read & Auto precharge disable L Column 4

column address H X L H L H X V address

Auto precharge enable H 4,5

Write & Auto precharge disable L Column 4

column address H X L H L L X V address

Auto precharge enable H 4,5

Burst stop H X L H H L X X 6

Bank selection V L

Precharge H X L L H L X X

All banks X H

H X X X

Clock suspend or Entry H L X

L V V V X

active power down

Exit L H X X X X X

H X X X

Entry H L X

L H H H

Precharge power down mode X

H X X X

Exit L H X

L V V V

DQM H X V X 7

H X X X

No operation command H X X X

L H H H

Notes : 1. OP Code : Operand code

A0 ~ A11 & BA0 ~ BA1 : Program keys. (@ MRS)

2. MRS can be issued only at all banks precharge state.

A new command can be issued after 2 CLK cycles of MRS.

3. Auto refresh functions are as same as CBR refresh of DRAM.

The automatical precharge without row precharge command is meant by "Auto".

Auto/self refresh can be issued only at all banks precharge state.

4. BA0 ~ BA1 : Bank select addresses.

If both BA0 and BA1 are "Low" at read, write, row active and precharge, bank A is selected.

If BA0 is "High" and BA1 is "Low" at read, write, row active and precharge, bank B is selected.

If BA0 is "Low" and BA1 is "High" at read, write, row active and precharge, bank C is selected.

If both BA0 and BA1 are "High" at read, write, row active and precharge, bank D is selected.

If A10/AP is "High" at row precharge, BA0 and BA1 is ignored and all banks are selected.

5. During burst read or write with auto precharge, new read/write command can not be issued.

Another bank read/write command can be issued after the end of burst.

New row active of the associated bank can be issued at tRP after the end of burst.

6. Burst stop command is valid at every burst length.

7. DQM sampled at positive going edge of a CLK and masks the data-in at the very CLK (Write DQM latency is 0),

but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)

15 of 15 Rev. 1.2 February 2008

You might also like

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureFrom EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureRating: 1 out of 5 stars1/5 (1)

- 013 - k4s64xx32n - Rev111 RAM DinámicaDocument15 pages013 - k4s64xx32n - Rev111 RAM DinámicanachcratchNo ratings yet

- 64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632KDocument14 pages64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632KCường MchwNo ratings yet

- Ice 40 LP HX Family Data SheetDocument45 pagesIce 40 LP HX Family Data SheetPablo AquevequeNo ratings yet

- Infineon AURIX - TC37x - Addendum DataSheet v01 - 05 ENDocument11 pagesInfineon AURIX - TC37x - Addendum DataSheet v01 - 05 EN0dayNo ratings yet

- Document Title Revision History: 128Mb Synchronous DRAM Based On 2M X 4bank x16 I/ODocument13 pagesDocument Title Revision History: 128Mb Synchronous DRAM Based On 2M X 4bank x16 I/OregulateNo ratings yet

- 8051 Microcontroller DataDocument17 pages8051 Microcontroller DataTechqualcerNo ratings yet

- 135616ds k4s56xx32n Rev10Document18 pages135616ds k4s56xx32n Rev10dmitry esaulkovNo ratings yet

- Two Layers Text/Graphic LCD Controller Specification: August 4, 2005Document8 pagesTwo Layers Text/Graphic LCD Controller Specification: August 4, 2005hüseyinNo ratings yet

- DDR SDR Sdram ComparisionDocument12 pagesDDR SDR Sdram ComparisionSrinivas CherukuNo ratings yet

- LC863432CDocument18 pagesLC863432Cjose gomezNo ratings yet

- Spansion Flash Memory MBM29LV800Document58 pagesSpansion Flash Memory MBM29LV800karkeraNo ratings yet

- Atmel - 32 Bit ARM7TDMI Flash Microcontroller - SAM7X512 256 128 - DatasheetDocument662 pagesAtmel - 32 Bit ARM7TDMI Flash Microcontroller - SAM7X512 256 128 - DatasheetCAZADORDOFREALNo ratings yet

- Vestel STB: Service ManualDocument67 pagesVestel STB: Service ManualnaughtybigboyNo ratings yet

- AT24C04C AT24C08C I2C Compatible Two Wire Serial EEPROM 4 Kbit 8 Kbit 20006127ADocument46 pagesAT24C04C AT24C08C I2C Compatible Two Wire Serial EEPROM 4 Kbit 8 Kbit 20006127Anicares718No ratings yet

- AT91SAM7xXXX PDFDocument671 pagesAT91SAM7xXXX PDFsaberNo ratings yet

- dm00525510 Getting Started With stm32h7 Series SDMMC Host Controller StmicroelectronicsDocument46 pagesdm00525510 Getting Started With stm32h7 Series SDMMC Host Controller Stmicroelectronicsfaganet228No ratings yet

- Features Description: CMOS 8/16-Bit MicroprocessorDocument32 pagesFeatures Description: CMOS 8/16-Bit MicroprocessorCandido GraciaNo ratings yet

- 256 MB DDR2Document128 pages256 MB DDR2dhdeshanmugamNo ratings yet

- RTS5138 One-LUN USB 2.0 Card Reader Controller DatasheetDocument13 pagesRTS5138 One-LUN USB 2.0 Card Reader Controller Datasheetari factoryNo ratings yet

- LC 863532 CDocument17 pagesLC 863532 CHelmi HashimNo ratings yet

- Realtek Single Chip OCTAL 10/100 MBPS Fast Ethernet Transceiver RTL8208Document41 pagesRealtek Single Chip OCTAL 10/100 MBPS Fast Ethernet Transceiver RTL8208Vinicius ZanicheliNo ratings yet

- 413 05857 0 LC35256FT 70uDocument7 pages413 05857 0 LC35256FT 70uA.hNo ratings yet

- Whats New Performance Power9Document55 pagesWhats New Performance Power9mario.torresNo ratings yet

- rk3066 Datasheet v1Document46 pagesrk3066 Datasheet v1api-432313169No ratings yet

- R8M DataSheet V02Document14 pagesR8M DataSheet V02asdasdasfli.elkinNo ratings yet

- LBA Guide - 20070813Document15 pagesLBA Guide - 20070813黃江祥No ratings yet

- RenesasDocument1 pageRenesasSunitha ReddyNo ratings yet

- EG4S20 DataSheet V1.5 EnglishDocument26 pagesEG4S20 DataSheet V1.5 EnglishspamNo ratings yet

- 2Gb LPDDR4 A Die Component DatasheetDocument325 pages2Gb LPDDR4 A Die Component DatasheetSudhir SainiNo ratings yet

- IS21TF16G/32G/64G/128G IS22TF16G/32G/64G/128G: 16GB/32GB/64GB/128GB eMMCDocument52 pagesIS21TF16G/32G/64G/128G IS22TF16G/32G/64G/128G: 16GB/32GB/64GB/128GB eMMCri3admNo ratings yet

- l293 PDFDocument18 pagesl293 PDFAnkadi Sikari ReddyNo ratings yet

- L293x Quadruple Half-H Drivers: 1 Features 3 DescriptionDocument17 pagesL293x Quadruple Half-H Drivers: 1 Features 3 DescriptionJamesSmith2014No ratings yet

- L293x Quadruple Half-H Drivers: 1 Features 3 DescriptionDocument19 pagesL293x Quadruple Half-H Drivers: 1 Features 3 DescriptionNaveed ShoukatNo ratings yet

- L293x Quadruple Half-H Drivers: 1 Features 3 DescriptionDocument21 pagesL293x Quadruple Half-H Drivers: 1 Features 3 DescriptionzruscicNo ratings yet

- L293x Quadruple Half-H Drivers: 1 Features 3 DescriptionDocument18 pagesL293x Quadruple Half-H Drivers: 1 Features 3 DescriptionVaibhav JadhavNo ratings yet

- ABB - 800M Controller and Communication Interfaces - Outline of All ModulesDocument8 pagesABB - 800M Controller and Communication Interfaces - Outline of All ModulesRoger GimenesNo ratings yet

- Aml8726 MX QRM V0.9 20120117Document37 pagesAml8726 MX QRM V0.9 20120117LukášPodařilNo ratings yet

- Datasheet TransceiverDocument86 pagesDatasheet TransceiverVictor Pastor RebolloNo ratings yet

- DP83848C/I/VYB/YB PHYTER™ QFP Single Port 10/100 Mb/s Ethernet Physical Layer TransceiverDocument89 pagesDP83848C/I/VYB/YB PHYTER™ QFP Single Port 10/100 Mb/s Ethernet Physical Layer Transceiverrfernandes_20No ratings yet

- DSC Power Series 1616 1832 1864 ImanDocument64 pagesDSC Power Series 1616 1832 1864 ImancristipopanNo ratings yet

- Hardware Design Guidelines For TMS320F28xx and TMS320F28xxx DSCsDocument33 pagesHardware Design Guidelines For TMS320F28xx and TMS320F28xxx DSCs劉品賢No ratings yet

- MCF51EM256Document54 pagesMCF51EM256jocansinoNo ratings yet

- Sony Dsr-11 Ver-1.1 SMDocument173 pagesSony Dsr-11 Ver-1.1 SMsaul64No ratings yet

- SDRAMDocument86 pagesSDRAMmichaelliu123456No ratings yet

- TU00003 003 How To Generate Code For The Ezdsp F2812 Using Simulink PDFDocument18 pagesTU00003 003 How To Generate Code For The Ezdsp F2812 Using Simulink PDFkhethanNo ratings yet

- Mediatek Mt6169V RF Transceiver Partial Circuit Analysis of The Input CircuitsDocument42 pagesMediatek Mt6169V RF Transceiver Partial Circuit Analysis of The Input CircuitsMario Negro Jimarez0% (1)

- TCC8200 v0.2 20060425Document505 pagesTCC8200 v0.2 20060425Joe LuiNo ratings yet

- 1gb Ddr2 Aut U88b Addendum-3179150Document151 pages1gb Ddr2 Aut U88b Addendum-3179150ManunoghiNo ratings yet

- Getting Started With Timer/Counter Type A (Tca) : View The Atmega4809 Code Example On GithubDocument23 pagesGetting Started With Timer/Counter Type A (Tca) : View The Atmega4809 Code Example On GithubGion AndrásNo ratings yet

- At91sam7se512 AuDocument47 pagesAt91sam7se512 AuLuthfi ImaduddinNo ratings yet

- Aviat Eclipse Digital Microwave RadioDocument23 pagesAviat Eclipse Digital Microwave RadioAnsar ShafiiNo ratings yet

- rtl8208Document40 pagesrtl8208murad asadovNo ratings yet

- 128Mb Synchronous DRAM MemoryDocument13 pages128Mb Synchronous DRAM MemoryMihaela CaciumarciucNo ratings yet

- M48Z02, M48Z12: 5 V, 16 Kbit (2 KB X 8) ZEROPOWER® SRAMDocument20 pagesM48Z02, M48Z12: 5 V, 16 Kbit (2 KB X 8) ZEROPOWER® SRAMعمر الاسماعيلNo ratings yet

- MC9S08SE8Document35 pagesMC9S08SE8juan moralesNo ratings yet

- MC9S08SE8Document35 pagesMC9S08SE8juan moralesNo ratings yet

- Infineon-S25fl128p 128 Mbit 3.0 V Flash Memory-datasheet-V14 00-EnDocument44 pagesInfineon-S25fl128p 128 Mbit 3.0 V Flash Memory-datasheet-V14 00-EnAlexNo ratings yet

- jpxw10wDocument76 pagesjpxw10wTan Hung LuuNo ratings yet

- ICDocument13 pagesICDeguchi ChizuruNo ratings yet

- Eschweiler Combi - Service ManualDocument74 pagesEschweiler Combi - Service ManualMed Rachid Ziani100% (1)

- JPX-A10WDocument76 pagesJPX-A10WTan Hung LuuNo ratings yet

- Spectrafuge 6C (CLSLN-AN-1003DOC REV1)Document12 pagesSpectrafuge 6C (CLSLN-AN-1003DOC REV1)Tan Hung LuuNo ratings yet

- 16F877ADocument234 pages16F877AMarius PauletNo ratings yet

- 2SS52M Series: Digital Magnetoresistive SensorDocument2 pages2SS52M Series: Digital Magnetoresistive SensorTan Hung LuuNo ratings yet

- 2.5 V To 5.5 V, 400 Μa, Quad Voltage Output, 8-/10-/12-Bit Dacs In 16-Lead Tssop / /Document28 pages2.5 V To 5.5 V, 400 Μa, Quad Voltage Output, 8-/10-/12-Bit Dacs In 16-Lead Tssop / /Tan Hung LuuNo ratings yet

- IFU TOXM0460 Toxoplasma Gondii IgM - Capture ELISA RUO 210923 eDocument8 pagesIFU TOXM0460 Toxoplasma Gondii IgM - Capture ELISA RUO 210923 eTan Hung LuuNo ratings yet

- SD Series: Medical & Laboratory AutoclavesDocument5 pagesSD Series: Medical & Laboratory AutoclavesTan Hung LuuNo ratings yet

- Features: Intel Pentium M, 915GME/910GMLE ETX CPU ModuleDocument2 pagesFeatures: Intel Pentium M, 915GME/910GMLE ETX CPU ModuleTan Hung LuuNo ratings yet

- Self-Excited RCC Pseudo-Resonance Type AC-DC Switching Power Supply Control ICDocument14 pagesSelf-Excited RCC Pseudo-Resonance Type AC-DC Switching Power Supply Control ICTan Hung LuuNo ratings yet

- Dell Inspiron N4110quanta v02 Da0v02mb6e1 Rev 1a Uma 19012011Document44 pagesDell Inspiron N4110quanta v02 Da0v02mb6e1 Rev 1a Uma 19012011Tan Hung LuuNo ratings yet

- 64K X 16 High-Speed Cmos Static Ram With 3.3V Supply: Features DescriptionDocument17 pages64K X 16 High-Speed Cmos Static Ram With 3.3V Supply: Features DescriptionTan Hung LuuNo ratings yet

- Alsatom Su 100 MPCDocument37 pagesAlsatom Su 100 MPCTan Hung LuuNo ratings yet

- ADS5203IPFB Texas InstrumentsDocument19 pagesADS5203IPFB Texas InstrumentsTan Hung LuuNo ratings yet

- Installation Instructions For The 2SS52M Series Magnetoresistive Position SensorsDocument4 pagesInstallation Instructions For The 2SS52M Series Magnetoresistive Position SensorsTan Hung LuuNo ratings yet

- TOP-3300 Infusion Pump Technical Reference ManualDocument52 pagesTOP-3300 Infusion Pump Technical Reference ManualSkywalker_9278% (9)

- AOD425 P-Channel Enhancement Mode Field Effect Transistor: Features General DescriptionDocument6 pagesAOD425 P-Channel Enhancement Mode Field Effect Transistor: Features General DescriptionTan Hung LuuNo ratings yet

- Origin Electric Co., LTDDocument2 pagesOrigin Electric Co., LTDTan Hung LuuNo ratings yet

- Aol 1413Document6 pagesAol 1413Amang GayamNo ratings yet

- AOD425 P-Channel Enhancement Mode Field Effect Transistor: Features General DescriptionDocument6 pagesAOD425 P-Channel Enhancement Mode Field Effect Transistor: Features General DescriptionTan Hung LuuNo ratings yet

- 1N4728A - 1N4764A: ZenersDocument5 pages1N4728A - 1N4764A: ZenersTan Hung LuuNo ratings yet

- Monitor settings for ultrasound presetsDocument1 pageMonitor settings for ultrasound presetsTan Hung LuuNo ratings yet

- Parts MNL SCU080Document68 pagesParts MNL SCU080Tan Hung LuuNo ratings yet

- SD Series: Medical & Laboratory AutoclavesDocument5 pagesSD Series: Medical & Laboratory AutoclavesTan Hung LuuNo ratings yet

- Esco Class II Cabinets Airstream D Series G Series ManualDocument73 pagesEsco Class II Cabinets Airstream D Series G Series ManualNorbey Marin MorenoNo ratings yet

- Aol 1413Document6 pagesAol 1413Amang GayamNo ratings yet

- 1N4728A - 1N4764A: ZenersDocument5 pages1N4728A - 1N4764A: ZenersTan Hung LuuNo ratings yet

- Can Tha, Ngay 01 Thong 8 Nom 2021Document9 pagesCan Tha, Ngay 01 Thong 8 Nom 2021Tan Hung LuuNo ratings yet

- SMART GLASS DATA SHEET v2Document3 pagesSMART GLASS DATA SHEET v2ayham.kuwait.2018No ratings yet

- Electronic Control Unit ECUDocument14 pagesElectronic Control Unit ECUnico Nico100% (1)

- CH 4Document26 pagesCH 4Keneni AlemayehuNo ratings yet

- 2N60 Series: N-Channel Power MosfetDocument8 pages2N60 Series: N-Channel Power MosfetMarcos PrestesNo ratings yet

- SolidStateDesignForTheRadioAmateur PDFDocument262 pagesSolidStateDesignForTheRadioAmateur PDFRodrigo LimaNo ratings yet

- Daikin RXC-B (R32) Manual ServiceDocument128 pagesDaikin RXC-B (R32) Manual ServiceMaurizio DumitracheNo ratings yet

- 3-Phase Brushless Fan Motor DriverDocument30 pages3-Phase Brushless Fan Motor DriverAravind Prasad Sounder RajNo ratings yet

- Product Family February EfficiencyDocument4 pagesProduct Family February Efficiencysitam_nitj4202No ratings yet

- Research Areas in Signal ProcessingDocument6 pagesResearch Areas in Signal ProcessingSri KrishnaNo ratings yet

- Mk10A Factsheet EnglishDocument6 pagesMk10A Factsheet Englishabhi_akNo ratings yet

- Declaration: Synchronization of Multiple Motors in Industries " Is ADocument10 pagesDeclaration: Synchronization of Multiple Motors in Industries " Is Acity cyberNo ratings yet

- Manual TB6560Document16 pagesManual TB6560erickmoraesNo ratings yet

- P22x EN TDS B44Document46 pagesP22x EN TDS B44Paneendra KumarNo ratings yet

- Datasheet Hal 502 New AplicacionDocument22 pagesDatasheet Hal 502 New AplicacionGeraldin PuertoNo ratings yet

- Magnetron LG 2M214Document6 pagesMagnetron LG 2M214Srce AsNo ratings yet

- Skiip 25Ac126V1: Miniskiip 2Document4 pagesSkiip 25Ac126V1: Miniskiip 2Max TeleNo ratings yet

- A Quick Guide To Resistor Sizes and PackagesDocument8 pagesA Quick Guide To Resistor Sizes and PackagesAmbachew2006No ratings yet

- Hardgrove Grindability Manual-1Document3 pagesHardgrove Grindability Manual-1Milos RadojevicNo ratings yet

- Operating Damages of Bushings in Power TransformersDocument5 pagesOperating Damages of Bushings in Power TransformersRoedy SoewardijantoNo ratings yet

- Technical Specifications Lifting and TransportDocument1 pageTechnical Specifications Lifting and TransportObet Ralo NautikaNo ratings yet

- Lecture 2Document41 pagesLecture 2trongnhansuper1No ratings yet

- AdU Illumination Problem Set 1Document1 pageAdU Illumination Problem Set 1Andrew NibungcoNo ratings yet

- W78E58B/W78E058B Data Sheet 8-Bit Microcontroller: Table of ContentsDocument36 pagesW78E58B/W78E058B Data Sheet 8-Bit Microcontroller: Table of Contentskeyboard2014No ratings yet

- RENR81310001Document11 pagesRENR81310001Guido VillafuerteNo ratings yet

- ATV212 Quick Start Annex S1A73476 05Document4 pagesATV212 Quick Start Annex S1A73476 05ksNo ratings yet

- Substation 2Document26 pagesSubstation 2Jahirul QuaimNo ratings yet

- Modernizing Classical Physics Experiments with Sensors and MicrocontrollersDocument24 pagesModernizing Classical Physics Experiments with Sensors and MicrocontrollersAnonymous mMc1M4g5BHNo ratings yet

- Control System Design White PaperDocument29 pagesControl System Design White PaperShravani ThombreNo ratings yet

- EVO FryersDocument14 pagesEVO FryersFaziNo ratings yet

- UART Communication Protocol ExplainedDocument17 pagesUART Communication Protocol ExplainedR INI BHANDARINo ratings yet