Professional Documents

Culture Documents

Question Paper Code: 10662: Reg - No

Uploaded by

selvakumargeorg17220 ratings0% found this document useful (0 votes)

4 views2 pagesaf

Original Title

EC8095 VLSI IAT1 QP2

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentaf

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

4 views2 pagesQuestion Paper Code: 10662: Reg - No

Uploaded by

selvakumargeorg1722af

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 2

Reg.

No:

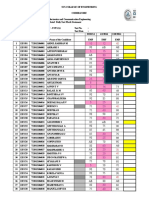

Question Paper Code: 10662

B.E DEGREE INTERNAL EXAMINATIONS, APRIL 2022

INTERNAL ASSESSMENT TEST-1

Sixth Semester

Department of Electronics and Communication Engineering

EC 8095 VLSI DESIGN

Time: 2 Hours Maximum marks: 70

Answer ALL questions

Q.N PART - A (10x2=20 marks)

CO K

o

1 Define Logical Effort. CO1 K1

2 What is channel length modulation? CO1 K1

Define Moore’s Law CO1

3 K1

4 Define Noise Margin. CO1 K1

5 Infer body effect. CO1 K2

6 What is Critical path? CO2 K1

7 Infer bubble pushing. CO2 K2

8 Define Ratioed Circuits. CO2 K1

Q.No PART - B (5x13=65 marks)

CO K

9(a) Inspect the following:

i) CMOS process enhancements (8) CO1 K4

ii) Layout design rules. (5)

Or

(b) Examine and derive the DC Transfer characteristics of CMOS inverter for the

CO1 K4

various regions of operation. (13)

10(a) Compare the scaling techniques which improves the circuit performance (13) CO1 K3

Or

(b) Develop three Capacitance and Voltage characteristics models for a MOS

CO1 K3

transistor. (13)

11(a) Contrast asymmetric and skewed gates used for Static CMOS optimization

process CO2 K4

(13)

Or

(b) Analyze pseudo nMOS and Ganged CMOS Logic for designing Ratioed Circuits. CO2

K4

(13)

Q.No PART - C (1x15=15 marks) CO K

12(a) Determine CMOS Logic for the following equations.

(i) Y=( A . B )+ ( A . C )+(B . D) (7) CO1 K5

(ii) Y=( A . B )+(C . D) (8)

Or

(b) Determine the delay using RC Delay and Linear delay model.

CO1 K5

(15)

Staff In-Charge HOD/ECE

You might also like

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- EC8095 VLSI IAT1 KeyDocument2 pagesEC8095 VLSI IAT1 Keyselvakumargeorg1722No ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Question Paper Code: 10662: Reg - NoDocument2 pagesQuestion Paper Code: 10662: Reg - Noselvakumargeorg1722No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Question Paper Code: 10682: (1x15 15 Marks)Document2 pagesQuestion Paper Code: 10682: (1x15 15 Marks)selvakumargeorg1722No ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- NMOS and PMOS Transistors: S N T B R / P N N - C D TDocument1 pageNMOS and PMOS Transistors: S N T B R / P N N - C D Tselvakumargeorg1722No ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Gate Marks 2022Document3 pagesGate Marks 2022selvakumargeorg1722No ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Syllabus For Electronics and Communication Engineering (EC) : Linear AlgebraDocument3 pagesSyllabus For Electronics and Communication Engineering (EC) : Linear Algebraapi-273759951No ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- SeminarDocument10 pagesSeminarselvakumargeorg1722No ratings yet

- Je SyllabusDocument5 pagesJe Syllabusselvakumargeorg1722No ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Department of Electronics and Communication Engineering: Naac Infrastructural Area Total No Total AreaDocument1 pageDepartment of Electronics and Communication Engineering: Naac Infrastructural Area Total No Total Areaselvakumargeorg1722No ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- 03.8.18 Daily Attendance II B.e.ece A & BDocument78 pages03.8.18 Daily Attendance II B.e.ece A & Bselvakumargeorg1722No ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Je SyllabusDocument5 pagesJe Syllabusselvakumargeorg1722No ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Asaignment QuestionsDocument4 pagesAsaignment Questionsselvakumargeorg1722No ratings yet

- SVS College of Engineering Discrete Time Systems and Signal Processing NotesDocument24 pagesSVS College of Engineering Discrete Time Systems and Signal Processing Notesselvakumargeorg1722No ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Ge6162.1 Ge6162.2 Ge6162.3 Ge6162.4 Ge6162.5Document12 pagesGe6162.1 Ge6162.2 Ge6162.3 Ge6162.4 Ge6162.5selvakumargeorg1722No ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- 03.8.18 Daily Attendance II B.e.ece A & BDocument2 pages03.8.18 Daily Attendance II B.e.ece A & Bselvakumargeorg1722No ratings yet

- SI (Tech) Information BrochureDocument19 pagesSI (Tech) Information BrochureAravindNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- .9.18 Daily Attendance II B.e.ece A & BDocument102 pages.9.18 Daily Attendance II B.e.ece A & Bselvakumargeorg1722No ratings yet

- Viva QestionsDocument4 pagesViva Qestionsselvakumargeorg1722No ratings yet

- Communication Engineering Daily Test-1Document1 pageCommunication Engineering Daily Test-1selvakumargeorg1722No ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Ee 6403 - Discrete Time Systems and Signal Processing (April/ May 2017) Regulations 2013Document4 pagesEe 6403 - Discrete Time Systems and Signal Processing (April/ May 2017) Regulations 2013selvakumargeorg1722No ratings yet

- 7.7.18 Daily Attendance II B.e.ece A & BDocument41 pages7.7.18 Daily Attendance II B.e.ece A & Bselvakumargeorg1722No ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- TET Paper 2 Exam Pattern: 30 MCQs Each on CDP, Language I, Language II & 60 MCQs on Subject SpecializationDocument1 pageTET Paper 2 Exam Pattern: 30 MCQs Each on CDP, Language I, Language II & 60 MCQs on Subject Specializationselvakumargeorg1722No ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 03.8.18 Daily Attendance II B.e.ece A & BDocument78 pages03.8.18 Daily Attendance II B.e.ece A & Bselvakumargeorg1722No ratings yet

- ECE A Daily TestDocument4 pagesECE A Daily Testselvakumargeorg1722No ratings yet

- Bus Ticket To VelankaniDocument1 pageBus Ticket To Velankaniselvakumargeorg1722No ratings yet

- Article On 6gDocument13 pagesArticle On 6gselvakumargeorg1722No ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- EdDocument3 pagesEdselvakumargeorg1722No ratings yet

- 2017 10 Not Eng Ccs II G2a Non OtDocument29 pages2017 10 Not Eng Ccs II G2a Non OtMOHAN RAJNo ratings yet

- 2017 10 Not Eng Ccs II G2a Non OtDocument29 pages2017 10 Not Eng Ccs II G2a Non OtMOHAN RAJNo ratings yet

- Lazos de 4-20ma 2Document1 pageLazos de 4-20ma 2sanchez2328No ratings yet

- Teshmont BrochureDocument30 pagesTeshmont BrochureMurugan100% (1)

- Wake-Up Latencies For Processor Idle States On Current x86 ProcessorsDocument9 pagesWake-Up Latencies For Processor Idle States On Current x86 ProcessorskrishnaNo ratings yet

- A Product Line of Diodes Incorporated: Totally Lead-Free Rohs Compliant (Notes 1 & 2)Document22 pagesA Product Line of Diodes Incorporated: Totally Lead-Free Rohs Compliant (Notes 1 & 2)PhilipNo ratings yet

- Tempfet BTS 132: FeaturesDocument11 pagesTempfet BTS 132: FeaturesSasa MitrovicNo ratings yet

- CAPASITORDocument3 pagesCAPASITORFery YelyantoNo ratings yet

- Ti OSO4Document4 pagesTi OSO4Liz AfanadorNo ratings yet

- DatachetDocument24 pagesDatachetmoisesdogorNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Electrical Characteristics of MOS Devices: V + "Metal" Oxide V +Document36 pagesElectrical Characteristics of MOS Devices: V + "Metal" Oxide V +mohandossNo ratings yet

- Dictionary of Pure and Applied PhysicsDocument383 pagesDictionary of Pure and Applied PhysicsInam Ul HaqNo ratings yet

- Performance Analysis of Low Power 6T SRAM Cell in 180nm and 90nmDocument7 pagesPerformance Analysis of Low Power 6T SRAM Cell in 180nm and 90nmDeepika kNo ratings yet

- Solution-Processed Solar Cells Based On Environmentally Friendly AgBiS2 NanocrystalsDocument6 pagesSolution-Processed Solar Cells Based On Environmentally Friendly AgBiS2 Nanocrystalsandres granadosNo ratings yet

- OPTO Electronics 2Document19 pagesOPTO Electronics 2rethwanfNo ratings yet

- Automatic RailwayDocument26 pagesAutomatic RailwayAshish SethiNo ratings yet

- Circuit of Power Audio Amplifier With Ic Tda2003 For 10 WattDocument7 pagesCircuit of Power Audio Amplifier With Ic Tda2003 For 10 WattMiguel AngelNo ratings yet

- Cat24c32 DDocument18 pagesCat24c32 DmegatornadoNo ratings yet

- DAVANGERE University Syllabus 2016 BCADocument14 pagesDAVANGERE University Syllabus 2016 BCAMunavalli Matt K S71% (7)

- A192-AE-W6-R, XC & Z - RC circuit-SV-PKPDocument47 pagesA192-AE-W6-R, XC & Z - RC circuit-SV-PKPMuhammad Nurazin Bin RizalNo ratings yet

- Equivalencia MfetDocument1 pageEquivalencia Mfetosvaldo matiasNo ratings yet

- 1GHz Active Differential Probe - Daniel Kramnik's Project LogDocument14 pages1GHz Active Differential Probe - Daniel Kramnik's Project LogSergioNo ratings yet

- SC2 PaperCraft: Illuminate ACU 2Document5 pagesSC2 PaperCraft: Illuminate ACU 2ali kararNo ratings yet

- Lab 3Document8 pagesLab 3Mohamed AhmedNo ratings yet

- Restricted Earth Fault Application GuideDocument12 pagesRestricted Earth Fault Application GuidementongNo ratings yet

- Lect - 8 - Thyristor - Turn On MethodsDocument13 pagesLect - 8 - Thyristor - Turn On MethodsVishal MeghwarNo ratings yet

- Organo - Met.chem: PDF Generated At: Tue, 28 Dec 2010 12:28:45 UTCDocument35 pagesOrgano - Met.chem: PDF Generated At: Tue, 28 Dec 2010 12:28:45 UTCdandinystNo ratings yet

- Agenda: Body Effect Model Reverse and Forward Body BiasDocument6 pagesAgenda: Body Effect Model Reverse and Forward Body Biashamsa gNo ratings yet

- Modern Electrical Power Production, Delivery and its Key ComponentsDocument25 pagesModern Electrical Power Production, Delivery and its Key ComponentskgskgmNo ratings yet

- Electronic TubesDocument7 pagesElectronic TubesAndré LuizNo ratings yet

- TDA2822Document6 pagesTDA2822josetantonioNo ratings yet