Professional Documents

Culture Documents

EC8095 VLSI IAT1 Key

Uploaded by

selvakumargeorg1722Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EC8095 VLSI IAT1 Key

Uploaded by

selvakumargeorg1722Copyright:

Available Formats

B.

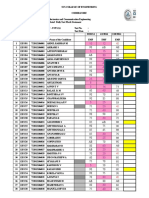

E DEGREE INTERNAL EXAMINATIONS, APRIL 2022

INTERNAL ASSESSMENT TEST-1

Department of Electronics and Communication Engineering

EC 8095 VLSI DESIGN

Time: 2 Hours Maximum marks: 70

Answer ALL questions

PART - A (8x2=16 marks)

1. Define Logical Effort

Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter

delivering the same output current.

2. What is channel length modulation?

Channel length modulation (CLM) is a shortening of the length of the

inverted channel region with increase in drain bias for large drain biases. The result of CLM is an

increase in current with drain bias and a reduction of output resistance.

3. Define Moore’s Law

Gordon Moore found that transistor count doubles for every 18 months . This observation is called

as Moore’s Law.

4. Define Noise Margin.

Noise margin is a measure of design margins to ensure circuits functioning properly within

specified conditions.

NML = |VIL max – VOL max|

NMH = |VOH min – VIH min|

5. What is body effect?

Body effect refers to the change in the threshold voltage of the device when there is a difference

between substrate(body) and source voltages.

6. What is Critical path?

The critical path is defined as the path between an input and an output with the maximum delay.

Once the circuit timing has been computed by one of the techniques listed below, the critical

path can easily be found by using a traceback method.

7. Infer bubble pushing.

Change the logic gate (AND to OR and OR to AND).

Add bubbles to the inputs and outputs where there were none, and remove the original bubbles.

8. Define Ratioed Circuits.

Ratioed circuits use weak pull-up and stronger pull-down networks. ... Ratioed circuits dissipate

static power and must be used sparingly. The pull-up network for ratioed CMOS (pseudo-nMOS)

uses a single pMOS. whose gate terminal is grounded (device is always on).

PART - B (3*13=39 marks)

9. Inspect the following:

i) CMOS process enhancements (8)

manufacturing of an IC (8)

ii) Layout design rules. (5)

Micron Rules (3)

Lambda Rules (2)

(or)

(b). Examine and derive the DC Transfer characteristics of CMOS inverter for the various regions

of operation. (13)

Circuit (1 mark)

Conditions (1 mark)

Different regions and its behavior (10 marks)

DC curve (2 marks)

10. (a) Compare the scaling techniques which improves the circuit performance. (13)

Introduction ( 2 marks)

Constant field scaling ( 3 marks)

Constant voltage scaling ( 3 marks)

Limits of scaling ( 5 marks)

b. Develop three Capacitance and Voltage characteristics models for a MOS transistor.

(13)

Simple MOS capacitance Model (5 marks)

Detailed MOS Gate capacitance model (4 marks)

Detailed MOS diffusion capacitance model (5 marks)

11. (a)Contrast asymmetric and skewed gates used for Static CMOS optimization process. (13)

Asymmetric gates (6)

skewed gates (7) (or)

(b) Analyze pseudo nMOS and Ganged CMOS Logic for designing Ratioed Circuits. (13)

pseudo nMOS (6)

Ganged CMOS (7)

PART - C (1x15=15 marks)

12. Determine CMOS Logic for the following equations.

(i) Y=( A . B )+ ( A . C )+( B . D) (7)

Realization using NMOS,PMOS (3)

Realization Using CMOS Logic(4)

(ii) Y=( A . B )+(C . D) (8)

Realization using NMOS,PMOS (4)

Realization Using CMOS Logic(4)

(or)

(b) Determine the delay using RC Delay and Linear delay model. (15)

Logical Effort , RC delay(8)

Linear delay(7)

Subject In charge Verified By HOD/ECE

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Logical Effort Designing Fast Cmos CircuitsDocument17 pagesLogical Effort Designing Fast Cmos CircuitsNishant MittalNo ratings yet

- Question Paper Code: 10662: Reg - NoDocument2 pagesQuestion Paper Code: 10662: Reg - Noselvakumargeorg1722No ratings yet

- Question Paper Code: 10662: Reg - NoDocument2 pagesQuestion Paper Code: 10662: Reg - Noselvakumargeorg1722No ratings yet

- Question Paper Code: 10682: (1x15 15 Marks)Document2 pagesQuestion Paper Code: 10682: (1x15 15 Marks)selvakumargeorg1722No ratings yet

- NMOS and PMOS Transistors: S N T B R / P N N - C D TDocument1 pageNMOS and PMOS Transistors: S N T B R / P N N - C D Tselvakumargeorg1722No ratings yet

- Gate Marks 2022Document3 pagesGate Marks 2022selvakumargeorg1722No ratings yet

- Syllabus For Electronics and Communication Engineering (EC) : Linear AlgebraDocument3 pagesSyllabus For Electronics and Communication Engineering (EC) : Linear Algebraapi-273759951No ratings yet

- SeminarDocument10 pagesSeminarselvakumargeorg1722No ratings yet

- Je SyllabusDocument5 pagesJe Syllabusselvakumargeorg1722No ratings yet

- Department of Electronics and Communication Engineering: Naac Infrastructural Area Total No Total AreaDocument1 pageDepartment of Electronics and Communication Engineering: Naac Infrastructural Area Total No Total Areaselvakumargeorg1722No ratings yet

- 03.8.18 Daily Attendance II B.e.ece A & BDocument78 pages03.8.18 Daily Attendance II B.e.ece A & Bselvakumargeorg1722No ratings yet

- Je SyllabusDocument5 pagesJe Syllabusselvakumargeorg1722No ratings yet

- Asaignment QuestionsDocument4 pagesAsaignment Questionsselvakumargeorg1722No ratings yet

- SVS College of Engineering Discrete Time Systems and Signal Processing NotesDocument24 pagesSVS College of Engineering Discrete Time Systems and Signal Processing Notesselvakumargeorg1722No ratings yet

- Ge6162.1 Ge6162.2 Ge6162.3 Ge6162.4 Ge6162.5Document12 pagesGe6162.1 Ge6162.2 Ge6162.3 Ge6162.4 Ge6162.5selvakumargeorg1722No ratings yet

- 03.8.18 Daily Attendance II B.e.ece A & BDocument2 pages03.8.18 Daily Attendance II B.e.ece A & Bselvakumargeorg1722No ratings yet

- SI (Tech) Information BrochureDocument19 pagesSI (Tech) Information BrochureAravindNo ratings yet

- .9.18 Daily Attendance II B.e.ece A & BDocument102 pages.9.18 Daily Attendance II B.e.ece A & Bselvakumargeorg1722No ratings yet

- Viva QestionsDocument4 pagesViva Qestionsselvakumargeorg1722No ratings yet

- Communication Engineering Daily Test-1Document1 pageCommunication Engineering Daily Test-1selvakumargeorg1722No ratings yet

- Ee 6403 - Discrete Time Systems and Signal Processing (April/ May 2017) Regulations 2013Document4 pagesEe 6403 - Discrete Time Systems and Signal Processing (April/ May 2017) Regulations 2013selvakumargeorg1722No ratings yet

- 7.7.18 Daily Attendance II B.e.ece A & BDocument41 pages7.7.18 Daily Attendance II B.e.ece A & Bselvakumargeorg1722No ratings yet

- TET Paper 2 Exam Pattern: 30 MCQs Each on CDP, Language I, Language II & 60 MCQs on Subject SpecializationDocument1 pageTET Paper 2 Exam Pattern: 30 MCQs Each on CDP, Language I, Language II & 60 MCQs on Subject Specializationselvakumargeorg1722No ratings yet

- 03.8.18 Daily Attendance II B.e.ece A & BDocument78 pages03.8.18 Daily Attendance II B.e.ece A & Bselvakumargeorg1722No ratings yet

- ECE A Daily TestDocument4 pagesECE A Daily Testselvakumargeorg1722No ratings yet

- Bus Ticket To VelankaniDocument1 pageBus Ticket To Velankaniselvakumargeorg1722No ratings yet

- Article On 6gDocument13 pagesArticle On 6gselvakumargeorg1722No ratings yet

- EdDocument3 pagesEdselvakumargeorg1722No ratings yet

- 2017 10 Not Eng Ccs II G2a Non OtDocument29 pages2017 10 Not Eng Ccs II G2a Non OtMOHAN RAJNo ratings yet

- 2017 10 Not Eng Ccs II G2a Non OtDocument29 pages2017 10 Not Eng Ccs II G2a Non OtMOHAN RAJNo ratings yet

- 16 Logical Effort and Transistor Sizing 31-08-2020 (31 Aug 2020) Material - I - 31 Aug 2020 - Logical - EffortDocument28 pages16 Logical Effort and Transistor Sizing 31-08-2020 (31 Aug 2020) Material - I - 31 Aug 2020 - Logical - EffortParth VijayNo ratings yet

- Chap4 Lect11 Logical EffortDocument19 pagesChap4 Lect11 Logical EffortCherryShiNo ratings yet

- VLSI Design Study MaterialDocument14 pagesVLSI Design Study MaterialvenkateshNo ratings yet

- Asic Library DesignDocument12 pagesAsic Library DesignS RAVINo ratings yet

- ECE 546 - VLSI Systems Design Lecture 10: Ratioed Logic, Pass Transistor LogicDocument32 pagesECE 546 - VLSI Systems Design Lecture 10: Ratioed Logic, Pass Transistor LogicveereshnicolyteNo ratings yet

- Cmos - Vlsi - Jan 2023Document2 pagesCmos - Vlsi - Jan 20231ms21ec132No ratings yet

- VLSI AssignDocument5 pagesVLSI AssignSrideviasokanNo ratings yet

- Topic 11 - Logical EffortsDocument17 pagesTopic 11 - Logical EffortsAnshul JainNo ratings yet

- Sill HSpice Tutorial FinalDocument106 pagesSill HSpice Tutorial FinalSharan Kumar GoudNo ratings yet

- VLSI Ch4 DelayDocument27 pagesVLSI Ch4 Delayជើងកាង ភូមិNo ratings yet

- Ec6601 Vlsi DesignDocument12 pagesEc6601 Vlsi DesignKalai OmprakashNo ratings yet

- Hybrid Logical Effort For Hybrid Logic Style Full Adders in Multistage Structures HareeshDocument1 pageHybrid Logical Effort For Hybrid Logic Style Full Adders in Multistage Structures HareeshRajni ParasharNo ratings yet

- h3 f06 PDFDocument5 pagesh3 f06 PDFDevaraj SubrmanayamNo ratings yet

- Digital Microelectronic Circuits (: Pass Transistor LogicDocument52 pagesDigital Microelectronic Circuits (: Pass Transistor LogicPrìñçé ÅsîfNo ratings yet

- Introduction To Cmos Vlsi Design: Circuit FamiliesDocument34 pagesIntroduction To Cmos Vlsi Design: Circuit FamiliesMasud SarkerNo ratings yet

- SRAM Access Delay and SRAM SizeDocument11 pagesSRAM Access Delay and SRAM SizenobinmathewNo ratings yet

- VLSI Design Lecture NotesDocument117 pagesVLSI Design Lecture NotesRaji SharmiNo ratings yet

- Sjsu Scholarworks Sjsu ScholarworksDocument101 pagesSjsu Scholarworks Sjsu ScholarworksRishav YadavNo ratings yet

- Course Plan - Vlsi DesignDocument12 pagesCourse Plan - Vlsi DesignPRABHAVATHY SNo ratings yet

- 3 To 8 Decoder in NGSPICEDocument14 pages3 To 8 Decoder in NGSPICEJaydip FadaduNo ratings yet

- EC6601 VLSI Design Question BankDocument11 pagesEC6601 VLSI Design Question BankThahsin ThahirNo ratings yet

- Vlsi Module-3Document129 pagesVlsi Module-3Phanindra ReddyNo ratings yet

- Design of Novel Address Decoders and Sense Amplifier for SRAMDocument54 pagesDesign of Novel Address Decoders and Sense Amplifier for SRAMVikas JainNo ratings yet

- Logical EffortDocument223 pagesLogical Effortgmahajan0100% (6)

- mt2 SolutionDocument18 pagesmt2 Solutiontony starkNo ratings yet

- Digital Integrated Circuits Lecture 5: Logical Effort and Delay EstimationDocument71 pagesDigital Integrated Circuits Lecture 5: Logical Effort and Delay EstimationProf. Vikas BalikaiNo ratings yet

- EC6601-VLSI DesignDocument11 pagesEC6601-VLSI Designmaheshwarivikas19820% (1)