Professional Documents

Culture Documents

Booth algorithm binary multiplication

Uploaded by

Moses DianOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Booth algorithm binary multiplication

Uploaded by

Moses DianCopyright:

Available Formats

Multiplication for binary integers in signed-2's complement

representation

or

Booth Multiplication Algorithm

• Multiplication M x 14, where M is the multiplicand and 14 the multiplier, can be done as

M x 24 - M X 21 •

• Because +14 can be represented in binary as 001110. It has a string of 1's in the

from bit weight 2k to weight 2m and it is equivalent to 2k+1 - 2m.

• So, the number 14 can be represented as 2k+ l - 2m = 24 - 21 = 16 -2 = 14.

• Thus, the product can be obtained by shifting the binary multiplicand M four times to the

left and subtracting M shifted left once.

• Booth algorithm is based on the above said fact.

• Booth algorithm requires examination of the multiplier bits and shifting of the partial

product.

• Prior to the shifting, the multiplicand may be added to the partial product, subtracted

from the partial product, or left unchanged according to the following rules:

1. The multiplicand is subtracted from the partial product upon facing the first least

significant 1 in a string of 1's in the multiplier. i.e. Qn=1, Qn+1=0.

2. The multiplicand is added to the partial product upon facing the first 0 (provided that

there was a previous 1) in a string of O's in the multiplier. i.e. Qn=0, Qn+1=1

3. The partial product does not change when the multiplier bit is identical to the

previous multiplier bit. i.e. Qn=0, Qn+1=0 or i.e. Qn=1, Qn+1=1.

• The algorithm works for both positive or negative multipliers in 2's complement

representation.

• For example, a multiplier equal to - 14 is represented in 2's complement as 110010 and is

treated as - 24 + 22 - 21 = - 14.

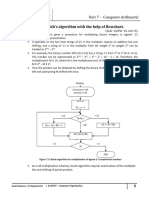

Hardware implementation of Booth algorithm:

• We use 3 registers namely AC, BR, and QR.

• Accumulator AC is used for storing partial product along with QR register.

• Multiplicand and multiplier are stored in BR and QR respectively.

• Qn indicates the least significant bit of the multiplier in register QR.

• An extra flip-flop Qn+1, is appended to QR to facilitate a double bit inspection of the

multiplier.

• Sequence counter SC is set to a number n equal to the number of bits in the multiplier.

• The hardware implementation of Booth algorithm is shown in the following figure.

Hardware for Booth algorithm

• AC register and appended bit Qn+1 are initially cleared to 0.

• The two bits of the multiplier in Qn and Qn+1 are inspected.

• If the two bits are equal to 10, it means, it requires a subtraction of the

multiplicand from the partial product in AC. i.e. first 1 in a string of 1' s has

been encountered.

• If the two bits are equal to 01, it means, it requires the addition of the

multiplicand to the partial product in AC. i.e. first 0 in a string of 0' s has

been encountered.

• When the two bits are equal, the partial product does not change.

• An overflow cannot occur because the addition and subtraction of the

multiplicand follow each other.

• As a consequence, the two numbers that are added always have opposite

signs, a condition that avoid an overflow.

• Next step is to shift right the partial product and the multiplier in AC and

QR (including bit Qn+1).

• This is an arithmetic shift right(ashr) operation which shifts AC and QR to

the right and leaves the sign bit in AC unchanged.

• The sequence counter is decremented and the computational loop is

repeated n times.

• A numerical example of Booth algorithm is shown in the following table for n = 5.

• It shows the step-by-step multiplication of (- 9) x (- 13) = + 117.

• Note that the multiplier in QR is negative and that the multiplicand in BR is also

negative.

• The 10-bit product appears in AC and QR and is positive.

• The final value of Qn+1 is the original sign bit of the multiplier and should not be taken

as part of the product.

You might also like

- CH-2.Multiplication AlgorithmDocument11 pagesCH-2.Multiplication AlgorithmDevanshi GudsariyaNo ratings yet

- Lectures On Computer Arithmetic: Unit 7Document20 pagesLectures On Computer Arithmetic: Unit 7viihaanghtrivediNo ratings yet

- Lectures On Lectures On Computer Arithmetic: Unit 7Document20 pagesLectures On Lectures On Computer Arithmetic: Unit 7viihaanghtrivediNo ratings yet

- CH 10Document5 pagesCH 10utkarsh.shrivastava.ug21No ratings yet

- Multiplier Bits and Shifting of The Partial Product. Prior To The Shifting, TheDocument4 pagesMultiplier Bits and Shifting of The Partial Product. Prior To The Shifting, TheMAHESH SNo ratings yet

- Booth AlgorithmDocument25 pagesBooth AlgorithmSanvi Singh ChauhanNo ratings yet

- Mod 1Document29 pagesMod 1Abin KurianNo ratings yet

- Unit-3 PPT CoDocument24 pagesUnit-3 PPT CobrsreddyNo ratings yet

- Arithmetic Processor: 10-2 Addition and SubtractionDocument9 pagesArithmetic Processor: 10-2 Addition and SubtractionSarbesh ChaudharyNo ratings yet

- Coa Module 3 Part 2Document28 pagesCoa Module 3 Part 2Ajith Bobby RajagiriNo ratings yet

- Computer Arithmetic Operations GuideDocument25 pagesComputer Arithmetic Operations GuideRoopa NNo ratings yet

- Computer Organization and Architecture: UNIT-2Document29 pagesComputer Organization and Architecture: UNIT-2CloudNo ratings yet

- MultiplicationDocument18 pagesMultiplicationApurv MauryaNo ratings yet

- KTU - CST202 - Arithmetic Algorithms and Booth's MultiplicationDocument30 pagesKTU - CST202 - Arithmetic Algorithms and Booth's MultiplicationBasithNo ratings yet

- FALLSEM2019-20 EEE4024 TH VL2019201001067 Reference Material I 02-Aug-2019 Computer ArithmeticDocument45 pagesFALLSEM2019-20 EEE4024 TH VL2019201001067 Reference Material I 02-Aug-2019 Computer ArithmetickripaNo ratings yet

- COA Unit 2Document25 pagesCOA Unit 2Shivam KumarNo ratings yet

- SSCE Shift MultDocument4 pagesSSCE Shift MultDhinesh DhamodarNo ratings yet

- PPTDocument9 pagesPPTsindhuvindhya100% (1)

- Report on Booth's Multiplication AlgorithmDocument10 pagesReport on Booth's Multiplication AlgorithmRaj MajiNo ratings yet

- Module-2 - Lecture 2: Alu - Signed Addition/SubtractionDocument44 pagesModule-2 - Lecture 2: Alu - Signed Addition/SubtractionWINORLOSENo ratings yet

- 10-Floating Point Representation With IEEE Standards and Algorithms For Common Arithmetic operations-30-Jul-2019Material - IDocument34 pages10-Floating Point Representation With IEEE Standards and Algorithms For Common Arithmetic operations-30-Jul-2019Material - Ividhi agarwalNo ratings yet

- FALLSEM2019-20 CSE2001 TH VL2019201000585 Reference Material I 13-Aug-2019 Data Representation and Computer Arithmetic 2019 2010Document34 pagesFALLSEM2019-20 CSE2001 TH VL2019201000585 Reference Material I 13-Aug-2019 Data Representation and Computer Arithmetic 2019 2010Puneeth SaiNo ratings yet

- COA Module 3 UpdatedDocument93 pagesCOA Module 3 UpdatedB G JEEVANNo ratings yet

- Arithmetic Logic Unit (ALU): Inside the CPU's CalculatorDocument13 pagesArithmetic Logic Unit (ALU): Inside the CPU's CalculatorShubham KumarNo ratings yet

- Computer Arithmetic 1. Addition and Subtraction of Unsigned NumbersDocument19 pagesComputer Arithmetic 1. Addition and Subtraction of Unsigned NumbersSai TrilokNo ratings yet

- Unit - 3 of Computer ArchitectureDocument59 pagesUnit - 3 of Computer ArchitectureShweta mauryaNo ratings yet

- Unit - 5 Computer Arithmetic: 5.1 Addition and SubtractionDocument16 pagesUnit - 5 Computer Arithmetic: 5.1 Addition and SubtractionKeshav NaganathanNo ratings yet

- COA Module 2 MCQs and Division Algorithms ExplainedDocument10 pagesCOA Module 2 MCQs and Division Algorithms ExplainedLalitha GuruswaminathanNo ratings yet

- Running Addition ON Partial-Products (Multiplication)Document16 pagesRunning Addition ON Partial-Products (Multiplication)Niel Roel VelascoNo ratings yet

- Booth'S Algorithm: MultiplicationDocument6 pagesBooth'S Algorithm: MultiplicationNipun JainNo ratings yet

- Arithmetic Operations and Binary Multiplication TechniquesDocument30 pagesArithmetic Operations and Binary Multiplication TechniquesadddataNo ratings yet

- Addition and subtraction of signed binary numbers using 2's complementDocument53 pagesAddition and subtraction of signed binary numbers using 2's complementArunPrasadNo ratings yet

- BoothDocument28 pagesBoothAnshul JainNo ratings yet

- Truncated Multiplication With Correction ConstantDocument9 pagesTruncated Multiplication With Correction ConstantAnonymous 05HygKNo ratings yet

- CSC232 - Chp4 Computer ArithmeticDocument71 pagesCSC232 - Chp4 Computer ArithmeticHassan HassanNo ratings yet

- Chapter10-Computer ArithmaticDocument25 pagesChapter10-Computer ArithmaticGeorgian ChailNo ratings yet

- Unit 1 (1) Physics EngineeringDocument26 pagesUnit 1 (1) Physics EngineeringShiny ShinyNo ratings yet

- Listening To Booth’s Algorithm using Rust and OrcaDocument17 pagesListening To Booth’s Algorithm using Rust and OrcaMuhammad Areeb KazmiNo ratings yet

- Addition and subtraction of signed-magnitude binary numbers using hardwareDocument2 pagesAddition and subtraction of signed-magnitude binary numbers using hardwareRajesh AdhikariNo ratings yet

- Multiplication & Division AlgorithmsDocument27 pagesMultiplication & Division AlgorithmsPramod SrinivasanNo ratings yet

- Fixed PT MultiplicationDocument12 pagesFixed PT MultiplicationSitaNo ratings yet

- Eee 122 CH 6 CountersDocument26 pagesEee 122 CH 6 Countersjayacomp100% (1)

- Arithmetic & Logic UnitDocument58 pagesArithmetic & Logic Unitakbisoi1No ratings yet

- Addition and Subtraction With Signed 2s ComplementDocument3 pagesAddition and Subtraction With Signed 2s ComplementMoses DianNo ratings yet

- Digital Electronics 1-Sequential Circuit CountersDocument20 pagesDigital Electronics 1-Sequential Circuit CountersSatyam GuptaNo ratings yet

- Amortized Analysis of A Binary Counter: Andreas KlappeneckerDocument9 pagesAmortized Analysis of A Binary Counter: Andreas KlappeneckerTarun vermaNo ratings yet

- 4 Bit Adder SubtractorDocument32 pages4 Bit Adder SubtractorPunetNo ratings yet

- A Modified Booth Algorithm For High Radix Fixed-Point MultiplicationDocument3 pagesA Modified Booth Algorithm For High Radix Fixed-Point MultiplicationNarayana Rao LatchupatulaNo ratings yet

- Counters and Decoders: PurposeDocument7 pagesCounters and Decoders: Purposepraritlamba25No ratings yet

- Computer Arithmetic-1Document46 pagesComputer Arithmetic-1Bam NoiceNo ratings yet

- Binary Ripple Counter: How it WorksDocument11 pagesBinary Ripple Counter: How it WorksThiriveedhi SubbarayuduNo ratings yet

- Digital Electronics: Key Concepts of Binary Number Representation and ArithmeticDocument6 pagesDigital Electronics: Key Concepts of Binary Number Representation and Arithmeticakshaykamath123No ratings yet

- CST131 Tutorial 3: Computer ArithmeticDocument5 pagesCST131 Tutorial 3: Computer ArithmeticLim ScNo ratings yet

- Ee188 Final Batu PlazaDocument16 pagesEe188 Final Batu Plazameytz102No ratings yet

- Mulitpliers Dividers Supp4 PDFDocument15 pagesMulitpliers Dividers Supp4 PDFavichalNo ratings yet

- Svit - Module 4Document30 pagesSvit - Module 4gjtuyNo ratings yet

- Digital Arithmetic: Operations and Circuits: Chapter-6Document44 pagesDigital Arithmetic: Operations and Circuits: Chapter-6Samina TohfaNo ratings yet

- Fundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsFrom EverandFundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsNo ratings yet

- EgovDocument3 pagesEgovMoses DianNo ratings yet

- Cache MemoryDocument7 pagesCache MemoryMoses DianNo ratings yet

- Addition and Subtraction With Signed 2s ComplementDocument3 pagesAddition and Subtraction With Signed 2s ComplementMoses DianNo ratings yet

- Array or Binary MultiplierDocument2 pagesArray or Binary MultiplierMoses DianNo ratings yet

- Mount Zion College of Engineering & Technology Question Bank for Computer NetworksDocument2 pagesMount Zion College of Engineering & Technology Question Bank for Computer NetworksMoses DianNo ratings yet

- Question Bank - Unit VDocument2 pagesQuestion Bank - Unit VMoses DianNo ratings yet

- Mount Zion College OS Question BankDocument2 pagesMount Zion College OS Question BankMoses DianNo ratings yet

- Question Bank - Unit IDocument2 pagesQuestion Bank - Unit IMoses DianNo ratings yet

- Question Bank - Unit IIDocument2 pagesQuestion Bank - Unit IIMoses DianNo ratings yet

- Arithmetic and Logic InstructionsDocument67 pagesArithmetic and Logic InstructionsHashim Omar AbukarNo ratings yet

- Topmark MaximDocument164 pagesTopmark Maxim55583550% (2)

- AS Level Computer Science - Number SystemsDocument25 pagesAS Level Computer Science - Number SystemsAryan MaheshwariNo ratings yet

- 3 - Arithmetic For ComputersDocument59 pages3 - Arithmetic For ComputersUtkarsh PatelNo ratings yet

- DSD Lab 8 HandoutDocument9 pagesDSD Lab 8 HandoutMuhammad AnasNo ratings yet

- Digital Field Tape Format Standards - SEG-DDocument36 pagesDigital Field Tape Format Standards - SEG-DLiavon SokalNo ratings yet

- Paper Title Should Be Written Here: Author'S Name, Co-Author'S NameDocument4 pagesPaper Title Should Be Written Here: Author'S Name, Co-Author'S NameSanjeev BansalNo ratings yet

- 8085 Programs ListDocument112 pages8085 Programs ListSHIVANI SHARMANo ratings yet

- Computer Arithmetic TechniquesDocument48 pagesComputer Arithmetic TechniquesNagendraNo ratings yet

- Binary PDFDocument2 pagesBinary PDFcr4ck3d0utNo ratings yet

- 241 CSM-4-Digital Logic-Lecture 5Document51 pages241 CSM-4-Digital Logic-Lecture 5ahmedNo ratings yet

- Unit 04 English Sentence To Boolean EquationsDocument30 pagesUnit 04 English Sentence To Boolean EquationsJhill-Jhill Jimenez Dela PeñaNo ratings yet

- Rajshahi University of Engineering and TechnologyDocument13 pagesRajshahi University of Engineering and TechnologysafinjunaedNo ratings yet

- Lecture-3 (Microprocessor Internal Architectres - Flag) NOTESDocument12 pagesLecture-3 (Microprocessor Internal Architectres - Flag) NOTESLHKNo ratings yet

- CS302 Quiz Solved For MID TERM PDFDocument25 pagesCS302 Quiz Solved For MID TERM PDFattiqueNo ratings yet

- MICROCONTROLLER IV SEMESTER ASSEMBLY PROGRAMSDocument10 pagesMICROCONTROLLER IV SEMESTER ASSEMBLY PROGRAMSAnkita VermaNo ratings yet

- Number System in Computer Science and IPV4 StructureDocument18 pagesNumber System in Computer Science and IPV4 Structureakashtech137No ratings yet

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument129 pagesDLD GTU Question Bank: Chapter-1 Binary Systemnirav34No ratings yet

- Number Systems, Operations, and CodesDocument35 pagesNumber Systems, Operations, and CodesMohamed SaadNo ratings yet

- LE3u 56MR ManualDocument17 pagesLE3u 56MR ManualJoão ArtilheiroNo ratings yet

- MySQL Data TypesDocument3 pagesMySQL Data TypesAnonymous VNu3ODGavNo ratings yet

- DIGITAL CIRCUITS EXERCISESDocument3 pagesDIGITAL CIRCUITS EXERCISESshreykumartyagiNo ratings yet

- Labview Data StoringDocument14 pagesLabview Data StoringEmil VicaiNo ratings yet

- Bit manipulation to control devices using flagsDocument1 pageBit manipulation to control devices using flagsBlack NightNo ratings yet

- Implementation of IEEE 754 Compliant Single Precision Floating-Point Adder Unit Supporting Denormal Inputs On Xilinx FPGADocument5 pagesImplementation of IEEE 754 Compliant Single Precision Floating-Point Adder Unit Supporting Denormal Inputs On Xilinx FPGAJan SpockNo ratings yet

- Report Error CorrectionDocument3 pagesReport Error Correctionhrhodge100% (1)

- DLCA - Practical No 2Document16 pagesDLCA - Practical No 204 Tushar Bhadrike100% (1)

- Shift and Rotate InstructionsDocument10 pagesShift and Rotate InstructionsAmeer HamzaNo ratings yet

- MCS-51 Instructions SetDocument17 pagesMCS-51 Instructions SetajoaomvNo ratings yet

- Digital ElectronicsDocument7 pagesDigital ElectronicsAlakaaa PromodNo ratings yet