Professional Documents

Culture Documents

5V / 3.3V Manchester Encoder / Decoder: General Description Features

Uploaded by

Andrei MucenicaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

5V / 3.3V Manchester Encoder / Decoder: General Description Features

Uploaded by

Andrei MucenicaCopyright:

Available Formats

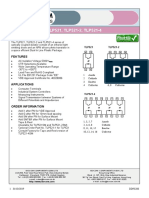

HI-15530

September 2013 5V / 3.3V Manchester Encoder / Decoder

GENERAL DESCRIPTION FEATURES

The HI-15530 is a high performance CMOS integrated ! MIL-STD-1553 compatible

circuit designed to meet the requirements of MIL-STD-1553

and similar Manchester II encoded, time division ! 5V or 3.3V operation

multiplexed serial data protocols. The HI-15530 contains

both an Encoder and Decoder, which operate ! Interfaces to HI-1567 Transceiver Family

independently.

! Small footprint 24-pin plastic SSOP package

The HI-15530 is fully compatible with either 5V or 3.3V logic

option

and transceivers.

The device generates MIL-STD-1553 sync pulses, parity ! Direct replacement for:

bits as well as the Manchester II encoding of the data bits. Harris/Intersil HD15530

The decoder recognizes and identifies sync pulses, GEC Plessey Semiconductors MAS15530

decodes data bits, and performs parity checking. Aeroflex ACT15530

The HI-15530 supports the 1Mbit/s data rate of MIL-STD- ! 1.25 Mbit/s Maximum Data Rate

1553 over the full temperature and voltage range.

! Manchester II Encode and Decode

For applications requiring small footprints and low cost, the

HI-15530 is available in a 24-pin plastic SSOP package.

! Sync identification and Lock-in

Ceramic DIP and LCC packages are also available to

achieve the highest level of reliability and to provide drop-in

! High Temperature -55 C to +200 C option

o o

replacements for obsolete parts from other manufacturers.

PIN CONFIGURATION (Top View)

APPLICATIONS VALID WORD 1 24 VDD

ENCODER SHIFT CLK 2 23 ENCODER CLK

! MIL-STD-1553 Interfaces TAKE DATA 3 22 SEND CLK IN

SERIAL DATA OUT 4 21 SEND DATA

! Smart Munitions DECODER CLK 5 20 SYNC SELECT

BIPOLAR ZERO IN 6 HI-15530PSI 19 ENCODER ENABLE

! Stores Management HI-15530PST

BIPOLAR ONE IN 7 18 SERIAL DATA IN

HI-15530PSM

! Sensor Interfaces UNIPOLAR DATA IN 8 17 BIPOLAR ONE OUT

DECODER SHIFT CLK 9 16 OUTPUT INHIBIT

! Instrumentation COMMAND / DATA SYNC 10 15 BIPOLAR ZERO OUT

DECODER RESET 11 14 ¸ 6 OUT

GND 12 13 MASTER RESET

24 Pin SSOP package

(Additional package pin configurations shown inside data sheet)

HOLT INTEGRATED CIRCUITS

(DS15530 Rev. K) www.holtic.com 09/13

HI-15530

PIN DESCRIPTIONS

SIGNAL SECTION FUNCTION DESCRIPTION

VALID WORD DECODER OUTPUT A high output signals the receipt of a valid word

ENCODER SHIFT CLOCK ENCODER OUTPUT Shifts data into the encoder on a low to high transition

TAKE DATA DECODER OUTPUT Output is high during receipt of data after identification of a Sync

Pulse and two valid Manchester data bits.

SERIAL DATA OUT DECODER OUTPUT Received Data output in NRZ format

DECODER CLOCK DECODER INPUT 12x the data rate. Clock for the transition finder and synchronizer,

which generates the internal clock for the remainder of the decoder

BIPOLAR ZERO IN DECODER INPUT A high input indicates the 1553 bus is in its negative state.

This pin must be held high when the Unipolar input is used

BIPOLAR ONE IN DECODER INPUT A high input indicates the 1553 bus is in the positive state.

This pin must be held low when the Unipolar input is used

UNIPOLAR DATA IN DECODER INPUT Input for unipolar data to the transition finder. Must be held low when

Not in use

DECODER SHIFT CLOCK DECODER OUTPUT Provides the DECODER CLOCK divided by 12, synchronized by the

recovered serial data

COMMAND / DATA SYNC DECODER OUTPUT A high on this pin occurs during the output of decoded data which

was preceded by a Command (or Status) synchronizing character. A

low output indicates a Data synchronizing character

DECODER RESET DECODER INPUT A high applied to this pin during a DECODER SHIFT CLOCK rising

edge resets the bit counter

GND BOTH POWER 0V supply

MASTER RESET BOTH INPUT A high on this pin clears the 2:1 counters in both Encoder and

Decoder and resets the divide-by-6 circuit

¸6 OUT ENCODER OUTPUT Provides ENCODER CLOCK divided by 6

BIPOLAR ZERO OUT ENCODER OUTPUT An active low output intended to drive the zero or negative sense of

a MIL-STD-1553 Line Driver

OUTPUT INHIBIT ENCODER INPUT A low inhibits the BIPOLAR ZERO OUT and BIPOLAR ONE OUT by

forcing them to inactive high states

BIPOLAR ONE OUT ENCODER OUTPUT An active low output intended to drive the one or positive sense on a

MIL-STD-1553 Line Driver

SERIAL DATA IN ENCODER INPUT Accepts serial data at the rate of the ENCODER SHIFT CLOCK

ENCODER ENABLE ENCODER INPUT A high on this pin initiates the encode cycle. (Subject to the

preceeding cycle being complete)

SYNC SELECT ENCODER INPUT Actuates a Command Sync for an input high and a Data Sync for a

low

SEND DATA ENCODER OUTPUT An active high output which enables the external source of serial

Data

SEND CLOCK IN ENCODER INPUT Clock input at 2 times the Data rate, usually driven by ¸6 OUT

ENCODER CLOCK ENCODER INPUT Input to the divide by 6 circuit. Normal frequency is Data rate x12

VDD BOTH POWER 3.0 V to 5.5 V power supply pin

HOLT INTEGRATED CIRCUITS

2

HI-15530

ENCODER OPERATION

The Encoder requires a single clock with a frequency of To abort the Encoder transmission a positive pulse must be

twice the desired data rate applied at the SEND CLOCK applied at MASTER RESET. Anytime after or during this

input. An auxiliary divide-by-six counter is provided on chip pulse, a low to high transition on SEND CLOCK clears the

which can be utilized to produce the SEND CLOCK by internal counters and initializes the Encoder for a new

dividing the ENCODER CLOCK. word.

The Encoder's cycle begins when ENCODER ENABLE is

high during a falling edge of ENCODER SHIFT CLOCK (1).

MASTER RESET

This cycle lasts for one word length or twenty ENCODER OUTPUT

INHIBIT

SHIFT CLOCK periods. At the next low-to-high transition of

SEND CLK IN

the ENCODER SHIFT CLOCK, a high at SYNC SELECT BIPOLAR

input actuates a command sync or a low will produce a ONE OUT

¸ 6 OUT

data sync for that word (2). When the Encoder is ready to ¸2

accept data, the SEND DATA output will go high and Character

remain high for sixteen ENCODER SHIFT CLOCK periods ¸6

Former BIPOLAR

ZERO OUT

(3). During these sixteen periods the data should be ENCODER CLK

clocked into the SERIAL DATA IN input with every low-to-

high transition of the ENCODER SHIFT CLOCK (3) - (4).

After the sync and the Manchester II coded data are

Bit

transmitted through the BIPOLAR ONE and BIPOLAR Counter

ZERO outputs, the Encoder adds on an additional bit which SYNC

SELECT

is the parity for that word (5). If ENCODER ENABLE is held

SERIAL

high continuously, consecutive words will be encoded SEND

DATA

DATA

IN

without an interframe gap. ENCODER ENABLE must go ENCODER ENCODER

low by time (5) as shown to prevent a consecutive word SHIFT ENABLE

CLK

from being encoded. At any time a low on the OUTPUT

INHIBIT input will force both bipolar outputs to a high state FIGURE 1. ENCODER

but will not affect the Encoder in any other way.

TIMING 0 1 2 3 4 5 6 7 15 16 17 18 19

SEND CLK

ENCODER

SHIFT CLK

ENCODER

DON’T CARE

ENABLE

SYNC SELECT VALID DON’T CARE

SEND DATA

SERIAL

15 14 13 12 11 10 3 2 1 0

DATA IN

BIPOLAR SYNC SYNC 15 14 13 12 11 3 2 1 0 P

ONE OUT

BIPOLAR SYNC SYNC 15 14 13 12 11 3 2 1 0 P

ZERO OUT

(1) (2) (3) (4) (5)

FIGURE 2. ENCODER OPERATION

HOLT INTEGRATED CIRCUITS

3

HI-15530

DECODER OPERATION

The Decoder requires a single clock with a frequency of 12 looking for a new sync character to start another output

times the desired data rate applied at the DECODER sequence. VALID WORD will go low approximately 20

CLOCK input. The Manchester II coded data can be DECODER SHIFT CLOCK periods after it goes high if not

presented to the Decoder in one of two ways. The reset low sooner by a valid sync and two valid Manchester

BIPOLAR ONE and BIPOLAR ZERO inputs will accept bits as shown (1). At any time in the above sequence, a

data from a comparator sensed transformer coupled bus as high input on DECODER RESET during a low-to-high

specified in MIL-STD-1553. The UNIPOLAR DATA input transition of DECODER SHIFT CLOCK will abort

can only accept non-inverted Manchester II coded data transmission and initialize the Decoder to start looking for a

(e.g. from BIPOLAR ZERO OUT of an Encoder). The new sync character.

Decoder is free running and continuously monitors its data

input lines for a valid sync character and two valid UNIPOLAR TAKE DATA

Manchester data bits to start an output cycle. When a valid DATA IN

sync is recognized (1), the type of sync is indicated on BIPOLAR TRANSITION CHARACTER

COMMAND/DATA SYNC output. If the sync character was ONE IN FINDER IDENTIFIER

COMMAND/DATA

a command sync, this output will go high (2) and remain BIPOLAR

SYNC

high for sixteen DECODER SHIFT CLOCK periods (3), ZERO IN

otherwise it will remain low. The TAKE DATA output will go SERIAL DATA

high and remain high (2) - (3) while the Decoder is OUT

transmitting the decoded data through SERIAL DATA OUT.

The decoded data available at SERIAL DATA OUT is in an BIT

VALID

WORD

DECODER PARITY

NRZ format. The DECODER SHIFT CLOCK is provided so CLK

SYNCHRONIZER RATE

CLK

CHECK

that the decoded bits can be shifted into an external register MASTER DECODER

SHIFT CLK

on every low-to-high transition of this clock (2) - (3). After all RESET

sixteen decoded bits have been transmitted (3) the data is DECODER BIT

checked for odd parity. A high on VALID WORD output (4) RESET COUNTER

indicates a successful reception of a word without any

Manchester or parity errors. At this time the Decoder is FIGURE 3. DECODER

TIMING 0 1 2 3 4 5 6 7 8 16 17 18 19

DECODER

SHIFT CLK

BIPOLAR SYNC SYNC 15 14 13 12 11 10 2 1 0 P

ONE IN

BIPLOAR SYNC SYNC 15 14 13 12 11 10 2 1 0 P

ZERO IN

TAKE DATA

COMMAND /

DATA SYNC

SERIAL UNDEFINED 15 14 13 12 4 3 2 1 0

DATA OUT

VALID WORD May be high from previous reception

(1)(2) (3) (4)

FIGURE 4. DECODER OPERATION

HOLT INTEGRATED CIRCUITS

4

HI-15530

TIMING DIAGRAMS

SEND CLK

t E1

ENCODER

SHIFT CLK

t E2 t E3

SERIAL DATA IN VALID VALID

SEND CLK

t E1

ENCODER

SHIFT CLK

t E4 t E6

ENCODER ENABLE

t E5

SYNC SELECT VALID

t E7

ENCODER

SHIFT CLK t E8

SEND DATA

SEND CLK

t E9

BIPOLAR ONE OUT or

BIPOLAR ZERO OUT

ENCODER TIMING

DECODER SHIFT CLK

t D6

COMMAND / DATA SYNC

t D7

TAKE DATA

DECODER SHIFT CLK

t D8

SERIAL DATA OUT DATA BIT

DECODER SHIFT CLK

t D9

COMMAND / DATA SYNC

t D10

TAKE DATA

t D11

VALID WORD

DECODER SHIFT CLK

t DRH

t DR

DECODER RESET

t DRS

DECODER TIMING

HOLT INTEGRATED CIRCUITS

5

HI-15530

TIMING DIAGRAMS (cont.)

BIT PERIOD BIT PERIOD BIT PERIOD

BIPOLAR ONE IN

t D1 t D3 t D3

t D2

BIPOLAR ZERO IN

t D1

t D2

COMMAND SYNC

BIPOLAR ONE IN t D1

t D3 t D3

BIPOLAR ZERO IN

t D1

t D2 t D2

DATA SYNC

BIPOLAR ONE IN

t D1 t D1

t D3 t D3 t D3

t D3 t D3

BIPOLAR ZERO IN

t D1 t D1

t D4 t D5 t D5 t D4

ONE ZERO ONE

t D2

UNIPOLAR IN

t D2

COMMAND SYNC

t D2

UNIPOLAR IN

t D2

DATA SYNC

t D5 t D4

UNIPOLAR IN

t D4 t D5 t D4

ONE ZERO ONE

DECODER TIMING

Bit Period 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

SYNC TERMINAL ADDRESS R/T SUBADDRESS DATA WORD P

Command Word SYNC

/ MODE COUNT

SYNC DATA WORD P

Data Word SYNC

SYNC TERMINAL ADDRESS ME CODE FOR FAILURE MODES TF P

Status Word SYNC

MIL-STD-1553 WORD FORMATS

HOLT INTEGRATED CIRCUITS

6

HI-15530

ABSOLUTE MAXIMUM RATINGS

Supply Voltage VDD -0.3V to +7V Power Dissipation at 25°C

Plastic SSOP 1.5 W, derate10mW/°C

Ceramic DIP 1.0 W, derate 7mW/°C

Voltage at any pin -0.3V to Vcc +0.3V DC Current Drain per pin ±10mA

Operating Temperature Range: Storage Temperature Range: -65°C to +150°C

Industrial -40°C to +85°C

Extended -55°C to +125°C

Hi-Temp -55°C to +200°C

NOTE: Stresses above those listed under "Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings

only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not

implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

DC ELECTRICAL CHARACTERISTICS

VDD = 3.0 V to 5.5 V, GND = 0V, TA = Operating Temperature Range (unless otherwise specified).

LIMITS

PARAMETER SYMBOL CONDITIONS UNIT

MIN TYP MAX

Input Voltage Input Voltage HI VIH 70% VDD V

Input Voltage LO VIL 30% VDD V

Clock Input Voltage Input Voltage HI VIHC VDD-0.5 V

Input Voltage LO VILC 0.5V V

Input Leakage Current Input Sink IIH 1.0 µA

Input Source IIL -1.0 µA

Output Voltage Logic “1” Output Voltage VOH1 VDD=5V±10%, IOH=-3mA 2.4 V

VOH2 VDD=3.3V±10%, IOH=-1mA 90% VDD V

Logic “0” Output Voltage VOL1 VDD=5V±10%, IOL=1.8mA 0.4 V

VOL2 VDD=3.3V±10%, IOH=1mA 10% VDD V

Standby Supply Current IDDSB VIN=VDD, Outputs Open 2.0 mA

Operating Supply Current IDD f=1MHz, Outputs Open 10.0 mA

Input Capacitance CIN 7.0 pF

Output Capacitance COUT 10.0 pF

HOLT INTEGRATED CIRCUITS

7

HI-15530

AC ELECTRICAL CHARACTERISTICS

VDD = 3.0V to 5.5V, GND = 0V, TA = Operating Temperature Range, CL=50pF

LIMITS

PARAMETER SYMBOL UNITS

MIN TYP MAX

Encoder Timing

Encoder Clock Frequency fEC 0 15 MHz

Send Clock Frequency fESC 0 2.5 MHz

Encoder Clock Rise Time tECR 8 ns

Encoder Clock Fall Time tECF 8 ns

Encoder Data Rate fED 0 1.25 MHz

Master Reset Pulse Width tMR 150 ns

Shift Clock Delay tE1 125 ns

Serial Data Setup Time tE2 75 ns

Serial Data Hold Time tE3 75 ns

Enable Setup Time tE4 90 ns

Enable Pulse Width tE5 80 ns

Sync Setup Time tE6 55 ns

Sync Pulse Width tE7 150 ns

Send Data Delay tE8 0 50 ns

Bipolar Output Delay tE9 130 ns

Enable Hold Time tE10 10 ns

Sync Hold Time tE11 95 ns

Decoder Timing

Decoder Clock Frequency fDC 0 15 MHz

Decoder Clock Rise Time tDCR 8 ns

Decoder Clock Fall Time tDCF 8 ns

Decoder Data Rate fDD 0 1.25 MHz

Decoder Reset Pulse Width tDR 150 ns

Decoder Reset Setup Time tDRS 75 ns

Decoder Reset Hold Time tDRH 10 ns

Master Reset Pulse Width tMR 150 ns

Bipolar Data Pulse Width tD1 tDC+10 ns

Sync Transition Span tD2 18tDC ns

One-Zero Overlap tD3 tDC-10 ns

Short Data Transition Span tD4 6tDC ns

Long Data Transition Span tD5 12tDC ns

Sync Delay (On) tD6 -20 110 ns

Take Data Delay (On) tD7 0 110 ns

Serial Data Out Delay tD8 80 ns

Sync Delay (Off) tD9 0 110 ns

Take Data Delay (Off) tD10 0 110 ns

Valid Word Delay tD11 0 110 ns

HOLT INTEGRATED CIRCUITS

8

HI-15530

ADDITIONAL PIN CONFIGURATIONS (See data sheet page 1 for 24-Pin Small Outline SSOP)

ENCODER SHIFT CLK

SERIAL DATA OUT

ENCODER CLK

SEND CLK IN

VALID WORD

TAKE DATA

VDD

VALID WORD 1 24 VDD 4 3 2 1 28 27 26

ENCODER SHIFT CLK 2 23 ENCODER CLK DECODER CLK 5 25 SEND DATA

TAKE DATA 3 22 SEND CLK IN N/C 6 24 N/C

SERIAL DATA OUT 4 21 SEND DATA N/C 7 HI-15530CLI 23 N/C

DECODER CLK 5 20 SYNC SELECT BIPOLAR ZERO IN 8 HI-15530CLT 22 SYNC SELECT

BIPOLAR ZERO IN 6

HI-15530CDI

19 ENCODER ENABLE BIPOLAR ONE IN 9 HI-15530CLM 21 ENCODER ENABLE

HI-15530CDT

BIPOLAR ONE IN 7 HI-15530CDM 18 SERIAL DATA IN UNIPOLAR DATA IN 10 20 SERIAL DATA IN

UNIPOLAR DATA IN 8 17 BIPOLAR ONE OUT DECODER SHIFT CLOCK 11 19 BIPOLAR ONE OUT

DECODER SHIFT CLK 9 16 OUTPUT INHIBIT 12 13 14 15 16 17 18

COMMAND / DATA SYNC 10 15 BIPOLAR ZERO OUT

COMMAND / DATA SYNC

DECODER RESET

GND

MASTER RESET

¸ 6 OUT

BIPOLAR ZERO OUT

OUTPUT INHIBIT

DECODER RESET 11 14 ¸ 6 OUT

GND 12 13 MASTER RESET

24 - Pin Ceramic Side-Brazed DIP

28 - Pin Ceramic LCC

ORDERING INFORMATION

HI - 15530PS x x (Plastic)

PART LEAD

NUMBER FINISH

Blank Tin / Lead (Sn / Pb) Solder

F 100% Matte Tin (Pb-free, RoHS compliant)

PART TEMPERATURE BURN

FLOW

NUMBER RANGE IN

I -40°C TO +85°C I No

T -55°C TO +125°C T No

M -55°C TO +125°C M Yes

PART PACKAGE

NUMBER DESCRIPTION

15530PS 24 PIN PLASTIC SSOP (24HS)

See next page for Ceramic package style Ordering Information

HOLT INTEGRATED CIRCUITS

9

HI-15530

ORDERING INFORMATION (cont.)

HI - 15530Cx x (Ceramic)

PART TEMPERATURE BURN LEAD

FLOW

NUMBER RANGE IN FINISH

I -40°C TO +85°C I No Gold (Pb-free, RoHS compliant)

T -55°C TO +125°C T No Gold (Pb-free, RoHS compliant)

M -55°C TO +125°C M Yes Tin / Lead (Sn / Pb) Solder

H -55°C TO +200°C H No Gold (Pb-free, RoHS compliant), DIP only

PART PACKAGE

NUMBER DESCRIPTION

15530CD 24 PIN CERAMIC SIDE BRAZED DIP (24C)

15530CL 28 PIN CERAMIC LEADLESS CHIP CARRIER (28S)

HOLT INTEGRATED CIRCUITS

10

HI-15530

REVISION HISTORY

Revision Date Description of Change

DS15530 Rev. J 10/16/08 Corrected package height in Package Dimension drawing for 24-pin ceramic side-brazed

DIP and clarified temperature ranges.

Rev. K 09/18/13 Added HI-15530CDH high temperature option.

HOLT INTEGRATED CIRCUITS

11

HI-15530 PACKAGE DIMENSIONS

24-PIN PLASTIC SSOP inches (millimeters)

Package Type: 24HS

.323 ± .012

(8.20 ± .30) .06

typ

(0.15)

.307 ± .016 .209 ± .012

(7.80 ± .40) (5.30 ± .30)

See Detail A

.012

typ

(.30)

.073 ± .0055

(1.86 ± .14)

0° to 8° .005 ± .001

(0.13 ± .08)

.026

BSC .030 ± .008

BSC = “Basic Spacing between Centers” (.650)

(0.75 ± .20) Detail A

is theoretical true position dimension and

has no tolerance. (JEDEC Standard 95)

24-PIN CERAMIC SIDE-BRAZED DIP inches (millimeters)

Package Type: 24C

1.220

max

(30.988)

.610 ±.010 .595 ±.010

(15.494 ±.254) (15.113 ±.254)

.050

typ

(1.270) .600 ±.010

.085 ±.009 (15.240 ±.254)

.200 (2.159 ±.229)

max

(5.080)

.125 .010 +.002/-.001

min (.254 +.051/-.025)

(3.175) .018 .100

typ BSC

BSC = “Basic Spacing between Centers” (.457) (2.54)

is theoretical true position dimension and

has no tolerance. (JEDEC Standard 95)

HOLT INTEGRATED CIRCUITS

12

HI-15530 PACKAGE DIMENSIONS

28-PIN CERAMIC LEADLESS CHIP CARRIER inches (millimeters)

Package Type: 28S

.020 .080 ±.020

(.508)

INDEX (2.032 ±.508)

PIN 1 PIN 1

.050 ±.005

(1.270 ±.127)

.451 ±.009

(11.455 ±.229) .050

BSC

SQ. (1.270)

.008R ± .006 .025 ±.003

(.203R ±.152) (.635 ±.076)

.040 x 45° 3PLS

(1.016 x 45° 3PLS)

BSC = “Basic Spacing between Centers”

is theoretical true position dimension and

has no tolerance. (JEDEC Standard 95)

HOLT INTEGRATED CIRCUITS

13

You might also like

- 2085 Hart MoDem DatasheetDocument8 pages2085 Hart MoDem DatasheetHPC HartNo ratings yet

- Donald McLean-Automatic-Flight-Control-Systems-1-62 PDFDocument62 pagesDonald McLean-Automatic-Flight-Control-Systems-1-62 PDFAndrei MucenicaNo ratings yet

- IPC Training and Reference Guide - DRM-18HDocument19 pagesIPC Training and Reference Guide - DRM-18HLane MedaNo ratings yet

- Bimos Ii 8-Bit Serial-Input, Latched Drivers: Absolute Maximum Ratings at 25 C Free-Air TemperatureDocument7 pagesBimos Ii 8-Bit Serial-Input, Latched Drivers: Absolute Maximum Ratings at 25 C Free-Air TemperatureAlexNo ratings yet

- Features Description: CMOS Manchester Encoder-DecoderDocument14 pagesFeatures Description: CMOS Manchester Encoder-DecoderKaty KimberlynNo ratings yet

- Safa Micro hw-1Document30 pagesSafa Micro hw-1suhailhajajjiNo ratings yet

- WD1772Document28 pagesWD1772alfa95139No ratings yet

- TLC 5615Document25 pagesTLC 5615Muhammad Ahsan AkramNo ratings yet

- 8-Channel GND/Open or Supply/Open Sensor With Programmable Thresholds and SPI InterfaceDocument21 pages8-Channel GND/Open or Supply/Open Sensor With Programmable Thresholds and SPI InterfaceWilliam WhiteNo ratings yet

- FPS110, FPS110B, FPS110E: Features ApplicationsDocument17 pagesFPS110, FPS110B, FPS110E: Features ApplicationsFrancisco HurtadoNo ratings yet

- AN82527 Intel CorporationDocument22 pagesAN82527 Intel CorporationJorge LuisNo ratings yet

- LMH1982 Preliminary DSDocument17 pagesLMH1982 Preliminary DSMartinNo ratings yet

- Hi 3110 - V Rev KDocument54 pagesHi 3110 - V Rev KÁlvaro Eduardo López LimaNo ratings yet

- Icl7135c - TLC7135CDocument11 pagesIcl7135c - TLC7135CCarlos PosadaNo ratings yet

- 74HC573Document7 pages74HC573hochman9443100% (2)

- DMG85480F050 01WTC-WTCZ01-WTCZ02 数据手册 (DataSheet)Document21 pagesDMG85480F050 01WTC-WTCZ01-WTCZ02 数据手册 (DataSheet)wramadhani65No ratings yet

- Khtek Da1196H: 24bit, 192Khz 6-Channel Digital To Audio ConverterDocument11 pagesKhtek Da1196H: 24bit, 192Khz 6-Channel Digital To Audio ConvertervetchboyNo ratings yet

- Chip Dolby DecoderDocument90 pagesChip Dolby Decoderjr1234No ratings yet

- HI 3593 ARINC 429 3.3V Dual Receiver, Single Transmitter With SPI Evaluation Board Users GuideDocument25 pagesHI 3593 ARINC 429 3.3V Dual Receiver, Single Transmitter With SPI Evaluation Board Users GuideAbbas HassanpourNo ratings yet

- SAK-C167CR-LC Infineon Elenota - PLDocument22 pagesSAK-C167CR-LC Infineon Elenota - PLpiotreNo ratings yet

- Point IoDocument46 pagesPoint IoUday NanamcharlaNo ratings yet

- BuR X20 HardwareDocument14 pagesBuR X20 HardwarecelinNo ratings yet

- Data Sheet: Dual 16-Bit DACDocument12 pagesData Sheet: Dual 16-Bit DACFetrian IvanNo ratings yet

- Samsung DVD Mini Component Max-945dDocument70 pagesSamsung DVD Mini Component Max-945dRicardo CardenasNo ratings yet

- Data Sheet: 74HC/HCT259Document11 pagesData Sheet: 74HC/HCT259kennyfernandezNo ratings yet

- 318 Series of Decoders: Comprehensive Guide to Features and SpecificationsDocument14 pages318 Series of Decoders: Comprehensive Guide to Features and SpecificationsHarshit DuaNo ratings yet

- Hi 8382Document9 pagesHi 8382bambuga07No ratings yet

- PDF/ROSSLARE ACD32 ManualDocument17 pagesPDF/ROSSLARE ACD32 ManualCristian MartinezNo ratings yet

- ICL7135Document16 pagesICL7135JIGNESHNo ratings yet

- HI 3593 ARINC V Dual Receiver, Single Transmitter With SPI Evaluation Board Quick Start Guide June 14, 2012Document9 pagesHI 3593 ARINC V Dual Receiver, Single Transmitter With SPI Evaluation Board Quick Start Guide June 14, 2012Abbas HassanpourNo ratings yet

- Ds1302 Datasheet PDFDocument14 pagesDs1302 Datasheet PDFarturoNo ratings yet

- SN74LS175 Quad D Flip-Flop: LOW Power SchottkyDocument8 pagesSN74LS175 Quad D Flip-Flop: LOW Power SchottkyDita RanantaNo ratings yet

- Features: 4-Channel Wideband and Video MultiplexerDocument6 pagesFeatures: 4-Channel Wideband and Video Multiplexerserrano.flia.coNo ratings yet

- Max1112 Max1113Document21 pagesMax1112 Max1113pedropumaNo ratings yet

- M XyzsvyuDocument40 pagesM XyzsvyuHossein AskaripoorNo ratings yet

- TDA9210 150 MHz Pixel Video ControllerDocument19 pagesTDA9210 150 MHz Pixel Video Controllerzerquera3000No ratings yet

- 900 Controledge Remote Termination Panel (RTP) ForDocument30 pages900 Controledge Remote Termination Panel (RTP) ForAnonymous NwnJNONo ratings yet

- Infineon TLE6209R DS v03 02 enDocument30 pagesInfineon TLE6209R DS v03 02 enRoger SegoNo ratings yet

- M54/M74HC190 M54/M74HC191: 4 Bit Synchronous Up/Down CountersDocument14 pagesM54/M74HC190 M54/M74HC191: 4 Bit Synchronous Up/Down Countersroshan kumarNo ratings yet

- Multiple Choices Huawei HCIADocument16 pagesMultiple Choices Huawei HCIAAugusto LimeraNo ratings yet

- Imcp Ht32Sx - Sip SigfoxDocument16 pagesImcp Ht32Sx - Sip SigfoxMarcelBortolotiNo ratings yet

- WM8740 v4.4Document27 pagesWM8740 v4.4AldoszxNo ratings yet

- Installation Guide Bcd10 r0cDocument16 pagesInstallation Guide Bcd10 r0cElevator & Escalator EngineeringNo ratings yet

- Rega DAC ManualDocument8 pagesRega DAC ManualetomeneNo ratings yet

- Centero VN220 HW Integration Application NoteDocument46 pagesCentero VN220 HW Integration Application NoteraytangclNo ratings yet

- Datasheet ECM 3508 Interface 4pgv1 A80401 PressDocument4 pagesDatasheet ECM 3508 Interface 4pgv1 A80401 Presslgreilly4No ratings yet

- 24-Bit, High Performance 192Khz Stereo Dac: Description FeaturesDocument27 pages24-Bit, High Performance 192Khz Stereo Dac: Description FeaturesikhsanaeNo ratings yet

- DMG80480F043 01WN 数据手册 (DataSheet)Document18 pagesDMG80480F043 01WN 数据手册 (DataSheet)ankadaNo ratings yet

- Encoder To Microprocessor Interface Chip Chip: Features: DescriptionDocument6 pagesEncoder To Microprocessor Interface Chip Chip: Features: DescriptionserviciobsasNo ratings yet

- WEG CFW500 IOR Plug in Module 10002046570 Installation Guide en Es PT PDFDocument24 pagesWEG CFW500 IOR Plug in Module 10002046570 Installation Guide en Es PT PDFTiago FernandesNo ratings yet

- 100V/2A Peak, Low Cost, High Frequency Half Bridge Driver FeaturesDocument13 pages100V/2A Peak, Low Cost, High Frequency Half Bridge Driver FeaturescarcavaNo ratings yet

- Pmodad2 RMDocument2 pagesPmodad2 RMsergioNo ratings yet

- PDIUSBD12Document35 pagesPDIUSBD12Engin UzunNo ratings yet

- Upgrading to HDCD: Installation Guide for Arcam CD72 to CD92 ModuleDocument49 pagesUpgrading to HDCD: Installation Guide for Arcam CD72 to CD92 ModuleLimbo67No ratings yet

- 7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 FeaturesDocument29 pages7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 Featureswtn2013No ratings yet

- DB en Ib Il 24 Do 16 5559 en 04Document9 pagesDB en Ib Il 24 Do 16 5559 en 04Gergő FaragóNo ratings yet

- X0020Document32 pagesX0020cakristofNo ratings yet

- Cio 116 Data Sheet 4921240524 UkDocument10 pagesCio 116 Data Sheet 4921240524 UkSergio Andres MurilloNo ratings yet

- Digital Sound Processor IC with 64K SRAMDocument12 pagesDigital Sound Processor IC with 64K SRAMJaPan LifeNo ratings yet

- Features: Dual, Low Power CMOS Operational AmplifiersDocument9 pagesFeatures: Dual, Low Power CMOS Operational AmplifiersDibya DeyNo ratings yet

- Bus 65153 130WDocument40 pagesBus 65153 130WAndrei MucenicaNo ratings yet

- Fully Integrated MIL-STD-1553 BC/RT/MT HI-6200, HI-6202 FamiliesDocument78 pagesFully Integrated MIL-STD-1553 BC/RT/MT HI-6200, HI-6202 FamiliesAndrei MucenicaNo ratings yet

- ARINCTutorialDocument29 pagesARINCTutorialshamsul_samsudin_2No ratings yet

- New Microsoft Word Document PDFDocument2 pagesNew Microsoft Word Document PDFAndrei MucenicaNo ratings yet

- TacanDocument10 pagesTacanKasidit ThanetoNo ratings yet

- TacanDocument10 pagesTacanKasidit ThanetoNo ratings yet

- ARINCTutorialDocument29 pagesARINCTutorialshamsul_samsudin_2No ratings yet

- Micro ControllerDocument221 pagesMicro ControllerkammoNo ratings yet

- TacanDocument10 pagesTacanKasidit ThanetoNo ratings yet

- TacanDocument10 pagesTacanKasidit ThanetoNo ratings yet

- ARINCTutorialDocument29 pagesARINCTutorialshamsul_samsudin_2No ratings yet

- Serial Control Documentation V2.13-Vx.35 PDFDocument11 pagesSerial Control Documentation V2.13-Vx.35 PDFAndrei MucenicaNo ratings yet

- Prototyping A Low-Cost Embedded Airspeed System: Razvan-Viorel MIHAI, Alexandru RADU, Ovidiu TABANDocument8 pagesPrototyping A Low-Cost Embedded Airspeed System: Razvan-Viorel MIHAI, Alexandru RADU, Ovidiu TABANAndrei MucenicaNo ratings yet

- Serial Control Documentation V2.13-Vx.35 PDFDocument11 pagesSerial Control Documentation V2.13-Vx.35 PDFAndrei MucenicaNo ratings yet

- Tablas AtmosferaDocument10 pagesTablas AtmosferaJonathanNo ratings yet

- ARINCTutorialDocument29 pagesARINCTutorialshamsul_samsudin_2No ratings yet

- W167 E1 04A+CxxP+Installation GuideDocument95 pagesW167 E1 04A+CxxP+Installation GuideAdrian GarciaNo ratings yet

- Features: Slls115E - October 1980 - Revised October 2007Document27 pagesFeatures: Slls115E - October 1980 - Revised October 2007Iván GissiNo ratings yet

- Overview of Electronic Packaging EvolutionDocument2 pagesOverview of Electronic Packaging EvolutionAllen SuNo ratings yet

- Pic 16c5xxDocument220 pagesPic 16c5xxshishir_2895No ratings yet

- IA70CX0: 8-Bit MicrocontrollerDocument2 pagesIA70CX0: 8-Bit MicrocontrollerDimitar PetrovNo ratings yet

- GMLAB RONDO' DIGITAL STRING MACHINE GUIDEDocument14 pagesGMLAB RONDO' DIGITAL STRING MACHINE GUIDEJames SpadavecchiaNo ratings yet

- DAC80 CB1 V DatasheetDocument10 pagesDAC80 CB1 V DatasheetsunhuynhNo ratings yet

- Linear Analog Products Cross Reference Texas - TIDocument69 pagesLinear Analog Products Cross Reference Texas - TIGerardo MediabillaNo ratings yet

- D9127 POPIT Modules Installation Manual EnUS 2538282507Document2 pagesD9127 POPIT Modules Installation Manual EnUS 2538282507Rodolfo CardenasNo ratings yet

- Guide to Installing and Maintaining Rolling DoorsDocument16 pagesGuide to Installing and Maintaining Rolling DoorsKim hassoNo ratings yet

- DG211, DG212: SPST 4-Channel Analog Switches FeaturesDocument7 pagesDG211, DG212: SPST 4-Channel Analog Switches Featuresjuan perezNo ratings yet

- "Wba Units": JCM Products Quick Reference GuideDocument16 pages"Wba Units": JCM Products Quick Reference GuideDan KollanderNo ratings yet

- HCPL 3120 HCPL J312 HCNW3120 25 Amp Output Current IGBT Gate Drive OptocouplerDocument24 pagesHCPL 3120 HCPL J312 HCNW3120 25 Amp Output Current IGBT Gate Drive OptocouplerMaikel MenkeNo ratings yet

- Honeywell 4219 Install GuideDocument2 pagesHoneywell 4219 Install GuideAlarm Grid Home Security and Alarm MonitoringNo ratings yet

- Chapter 4: Input/Output Programming of 8051 CPUDocument7 pagesChapter 4: Input/Output Programming of 8051 CPUIsmailNo ratings yet

- Gold PicDocument6 pagesGold PicBalbalaManiukNo ratings yet

- Cross Reference Atmel Vs XilinxDocument14 pagesCross Reference Atmel Vs XilinxjassadNo ratings yet

- MachXO3L StarterKit UGDocument28 pagesMachXO3L StarterKit UGDavid ParkerNo ratings yet

- Atmel 24C02Document24 pagesAtmel 24C02chichedemorenoNo ratings yet

- Sevice Manual HAPJDocument380 pagesSevice Manual HAPJSidney Manoel100% (1)

- Store Price ListDocument126 pagesStore Price ListKrishna MalhotraNo ratings yet

- 27c322 Reproduction PCB Instructions V3Document6 pages27c322 Reproduction PCB Instructions V3jondvalNo ratings yet

- Datasheet Search Site PDFDocument192 pagesDatasheet Search Site PDFALEXSAHDRNo ratings yet

- Part 2 - RFM12 Hardware InterfaceDocument4 pagesPart 2 - RFM12 Hardware InterfacechouanaNo ratings yet

- JSSStandards JSS 52300 1992Document68 pagesJSSStandards JSS 52300 1992khanjrkhanNo ratings yet

- CM8870/70C CMOS Integrated DTMF Receiver: California Micro DevicesDocument8 pagesCM8870/70C CMOS Integrated DTMF Receiver: California Micro DevicesEdwinBeNo ratings yet

- Lab07 DLD 18BMDocument5 pagesLab07 DLD 18BMSadaf RasheedNo ratings yet

- User Manual 1374484Document12 pagesUser Manual 1374484gutierkNo ratings yet

- TLP521, TLP521-2, TLP521-4: DescriptionDocument18 pagesTLP521, TLP521-2, TLP521-4: DescriptionİSMAİL TUNCANo ratings yet