Professional Documents

Culture Documents

Features: 4-Channel Wideband and Video Multiplexer

Uploaded by

serrano.flia.coOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Features: 4-Channel Wideband and Video Multiplexer

Uploaded by

serrano.flia.coCopyright:

Available Formats

DATASHEET

HI-524 FN3148

4-Channel Wideband and Video Multiplexer Rev 3.00

April 2002

The HI-524 is a 4-Channel CMOS analog multiplexer designed Features

to process single-ended signals with bandwidths up to 10MHz.

The chip includes a 1 of 4 decoder for channel selection and an • Crosstalk (10MHz) . . . . . . . . . . . . . . . . . . . . . . . .< -60dB

enable input to inhibit all channels (chip select). • Fast Access Time . . . . . . . . . . . . . . . . . . . . . . . . . 150ns

Three CMOS transmission gates are used in each channel, • Fast Settling Time . . . . . . . . . . . . . . . . . . . . . . . . . 200ns

as compared to the single gate in more conventional CMOS

• TTL Compatible

multiplexers. This provides a double barrier to the unwanted

coupling of signals from each input to the output. In addition,

Dielectric Isolation (DI) processing helps to insure the

Applications

Crosstalk is less than -60dB at 10MHz. • Wideband Switching

The HI-524 is designed to operate into a wideband buffer • Radar

amplifier such as the Intersil HA-2541. The multiplexer chip • TV Video

includes two “ON” switches in series, for use as a feedback

element with the amplifier. This feedback resistance • ECM

matches and tracks the channel ON resistance, to minimize

the amplifier VOS and its variation with temperature.

Functional Diagram

The HI-524 is well suited to the rapid switching of video and IN1 FB (IN)

other wideband signals in telemetry, instrumentation, radar

and video systems.

SIG GND

Ordering Information IN2

PART TEMP. RANGE

NUMBER (oC) PACKAGE PKG. NO. FB (OUT)

SIG GND

HI1-0524-5 0 to 75 18 Ld CERDIP F18.3 IN3 OUTPUT

Pinout

HI-524 (CERDIP) SIG GND

TOP VIEW IN4

+V 1 18 FB (IN) 1 OF 4

DECODER

OUT 2 17 -V SIG GND

SIG GND

SIG GND 3 16 FB (OUT)

1

SIG GND 4 15 SIG GND -15V SUP +15V EN A0 A1

GND

IN4 5 14 IN2

SIG GND 6 13 SIG GND

TRUTH TABLE

IN3 7 12 IN1

A1 A0 EN ON CHANNEL

SUPPLY GND 8 11 EN

X X L None

A1 9 10 A0

L L H 1 (Note)

L H H 2

H L H 3

H H H 4

NOTE: Channel 1 is shown selected in the Functional Diagram.

FN3148 Rev 3.00 Page 1 of 6

April 2002

HI-524

Absolute Maximum Ratings Thermal Information

V+ to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33V Thermal Resistance (Typical, Note 1) JA (oC/W) JC (oC/W)

Digital Input Voltage (VEN, VA) . . . . . . . . . . . . . . . . . . . . -6V to +6V CERDIP Package. . . . . . . . . . . . . . . . . 75 20

Analog Signal (VIN, VOUT) . . . . . . . . . . . . . . . . (V-) -2V to (V+) +2V Maximum Junction Temperature

Either Supply to Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16.5V Ceramic Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175oC

Maximum Storage Temperature. . . . . . . . . . . . . . . . -65oC to 150oC

Operating Conditions Maximum Lead Temperature (Soldering, 10s). . . . . . . . . . . . 300oC

Temperature Range

HI-524-5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0oC to 75oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. JA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications Supplies = +15V, -15V; VAH (Logic Level High) = 2.4V, VAL (Logic Level Low) = 0.5V; VEN = 2.4V,

Unless Otherwise Specified

-5

TEST TEMP

PARAMETER CONDITIONS (oC) MIN TYP MAX UNITS

DYNAMIC CHARACTERISTICS

Access Time, tA Note 5 25 - 150 300 ns

Break-Before-Make Delay, tOPEN Note 5 25 - 20 - ns

Enable Delay (ON), tON (EN) RL = 500 25 - 180 - ns

Enable Delay (OFF), tOFF (EN) RL = 500 25 - 180 - ns

Settling Time (Note 5) To 0.1% 25 - 200 - ns

To 0.01% 25 - 600 - ns

Crosstalk Note 6 25 - -65 - dB

Channel Input Capacitance, CS(OFF) 25 - 4 - pF

Channel Output Capacitance, CD(OFF) 25 - 10 - pF

Digital Input Capacitance, CA 25 - 5 - pF

DIGITAL INPUT SPECIFICATIONS

Input Low Threshold (TTL), VAL Full - - 0.8 V

Input High Threshold (TTL), VAH Full 2.4 - - V

Input Leakage Current (High), IAH Full - 0.05 1 A

Input Leakage Current (Low), IAL Full - - 25 A

ANALOG CHANNEL SPECIFICATIONS

Analog Signal Range, VlN Full -10 - +10 V

On Resistance, rON Note 2 25 - 700 -

Full - - 1.5 k

Off Input Leakage Current, IS (OFF) Note 3 25 - 0.2 - nA

Full - - 50 nA

Off Output Leakage Current, ID (OFF) Note 3 25 - 0.2 - nA

Full - - 50 nA

On Channel Leakage Current, ID (ON) Note 3 25 - 0.7 - nA

Full - - 50 nA

-3dB Bandwidth Note 4 25 - 8 - MHz

FN3148 Rev 3.00 Page 2 of 6

April 2002

HI-524

Electrical Specifications Supplies = +15V, -15V; VAH (Logic Level High) = 2.4V, VAL (Logic Level Low) = 0.5V; VEN = 2.4V,

Unless Otherwise Specified (Continued)

-5

TEST TEMP

PARAMETER CONDITIONS (oC) MIN TYP MAX UNITS

POWER SUPPLY CHARACTERISTICS

Power Dissipation, PD Full - - 750 mW

Current, I+ Note 7 Full - - 25 mA

Current, I- Note 7 Full - - 25 mA

NOTES:

2. VlN = 0V; lOUT = 100A (See Test Circuit section).

3. VO = 10V; VIN = 10V. (See Test Circuit section).

4. MUX output is buffered with HA-5033 amplifier.

5. 6V Step, 3V to 3V, See Test Circuit section.

6. VIN = 10MHz, 3VP-P on one channel, with any other channel selected. (Worst case is channel 3 selected with input on channel 4.) MUX output

is buffered with HA-2541 as shown in Applications section. Terminate all channels with 75.

7. Supply currents vary less than 0.5mA for switching rates from DC to 2MHz.

Test Circuits and Waveforms TA = 25oC, VSUPPLY = 15V, VAH = 2.4V, VAL = 0.8V, Unless Otherwise Specified

IOUT 100A

V2

IN OUT

V2

VIN rON =

100A

FIGURE 1A. TEST CIRCUIT

1,000 1,000

VIN = 0V

125oC

900

800 900

25oC

rON ()

rON ()

700

600 800

-55oC

500

400 700

-10 -8 -6 -4 -2 0 2 4 6 8 10 9 10 11 12 13 14 15

VIN (V) SUPPLY VOLTAGE (V)

FIGURE 1B. ON RESISTANCE vs ANALOG INPUT VOLTAGE FIGURE 1C. ON RESISTANCE vs SUPPLY VOLTAGE

FIGURE 1. ON RESISTANCE

FN3148 Rev 3.00 Page 3 of 6

April 2002

HI-524

Test Circuits and Waveforms TA = 25oC, VSUPPLY = 15V, VAH = 2.4V, VAL = 0.8V, Unless Otherwise Specified (Continued)

LEAKAGE CURRENT (nA)

ID(ON)

1.0

EN 0.8V

OUT

IS(OFF)

A ID(OFF)

ID(OFF)

10V 10V

0.1

0 25 50 75 100 125 150

TEMPERATURE (oC)

FIGURE 2A. LEAKAGE CURRENT vs TEMPERATURE FIGURE 2B. ID(OFF) TEST CIRCUIT (NOTE 8)

OUT OUT

A IS(OFF) 0.8V

EN

EN A ID(ON)

A0 A1

10V 10V

10V 10V

+2.4V

FIGURE 2C. IS(OFF) TEST CIRCUIT (NOTE 8) FIGURE 2D. ID(ON) TEST CIRCUIT (NOTE 8)

FIGURE 2. LEAKAGE CURRENTS

HA-524

IN1

3V

VAH = 2.4V

HA-2541 ADDRESS DRIVE (VA)

IN2 2 1.6V

+ OUTPUT

18

- VAL = 0.8V

20pF 75

IN3 +3V

16 (NOTE 10)

ACCESS TIME, tA

IN4 SETTLING TIME, tS

3V

A0 A1 EN

HA-2541 10%

5V OUTPUT -3V

VA 50 0.1% OF FULL SCALE

(OR 0.01%)

FIGURE 3A. TEST CIRCUIT FIGURE 3B. MEASUREMENT POINTS

FIGURE 3. SETTLING TIME, ACCESS TIME, BREAK-BEFORE-MAKE DELAY (NOTE 9)

NOTES:

8. Two measurements per channel: 10V and 10V. (Two measurements per device for ID(OFF) 10V and 10V.)

9. The Break-Before-Make test requires inputs 1 and 4 at the same voltage.

10. Capacitor value may be selected to optimize AC performance.

FN3148 Rev 3.00 Page 4 of 6

April 2002

HI-524

Test Circuits and Waveforms TA = 25oC, VSUPPLY = 15V, VAH = 2.4V, VAL = 0.8V, Unless Otherwise Specified (Continued)

5V/DIV.

VA INPUT

S1 ON S4 ON 1V/DIV.

OUTPUT

50ns/DIV.

FIGURE 4. ACCESS TIME WAVEFORMS

Application Information

Often it is desirable to buffer the Hl-524 output, to avoid loading Note that the on-chip feedback element between pins 16 and

errors due to the channel “ON” resistance: 18 includes two switches in series, to simulate a channel

HA-524 resistance. These switches open for VEN = Low. This allows

two or more Hl-524s to operate into one HA-2541, with their

12

CH1 feedback elements connected in parallel. Thus, only the

selected multiplexer provides feedback, and the amplifier

75

remains stable.

HA-2541 All Hl-524 pins labeled ‘SlG GND’ (pins 3, 4, 6, 13, 15) should

14 2

CH2 + BUFFERED be externally connected to signal ground for best crosstalk

18

- OUTPUT

75 performance.

20pF (NOTE)

Bypass capacitors (0.1F to 1F) are recommended from each

16

CH3

7 HI-524 supply pin to power ground (pins 1 and 17 to pin 8).

Locate the buffer amplifier near the Hl-524 so the two

75 capacitors may bypass both devices.

If an analog input 1V or greater is present when supplies are

5

CH4 off, a low resistance is seen from that input to a supply line.

75

(For example, the resistance is approximately 160 for an

input of -3V.) Current flow may be blocked by a diode in each

supply line, or limited by a resistor in series with each channel.

NOTE: Capacitor value may be selected to optimize AC performance.

The best solution, of course, is to arrange that no digital or

analog inputs are present when the power supplies are off.

FIGURE 5.

The buffer amplifier should offer sufficient bandwidth and slew

rate to avoid degradation of the anticipated signals. For video

switching, the HA-5033 and HA-2542 offer good performance

plus 100mA output current for driving coaxial cables. For

general wideband applications, the HA-2541 offers the

convenience of unity gain stability plus 90ns settling (to 0.1%)

and 10V output swing. Also, the Hl-524 includes a feedback

resistance for use with the HA-2541. This resistance matches

and tracks the channel “ON” resistance, to minimize offset

voltage due to the buffer's bias currents.

FN3148 Rev 3.00 Page 5 of 6

April 2002

HI-524

Die Characteristics

DIE DIMENSIONS: PASSIVATION:

2250m x 3720m x 485m Type: Nitride Over Silox

Nitride Thickness: 3.5kÅ 1kÅ

METALLIZATION:

Silox Thickness: 12kÅ 2kÅ

Type: CuAl

Thickness: 16kÅ 2kÅ WORST CASE CURRENT DENSITY:

1.58 x 105 A/cm2

Metallization Mask Layout

HI-524

SUPPLY

EN AO A1 GND

IN1 IN3

SIG SIG

GND GND

IN2 IN4

SIG SIG

GND GND

FB (OUT) SIG

GND

-V FB (IN) +V OUT

© Copyright Intersil Americas LLC 2002. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN3148 Rev 3.00 Page 6 of 6

April 2002

You might also like

- GSSF L1Document20 pagesGSSF L1Jeanpierre H. AsdikianNo ratings yet

- CV512H-U42 Service ManualDocument41 pagesCV512H-U42 Service Manualعاطف شعلانNo ratings yet

- AR-701B-X Fit 35mm DIN Rail or Mount Directly: CN1 CN2 CN3Document6 pagesAR-701B-X Fit 35mm DIN Rail or Mount Directly: CN1 CN2 CN3trisatriabNo ratings yet

- TV/VCR Tuner Ic With DC/DC Converter: FeaturesDocument21 pagesTV/VCR Tuner Ic With DC/DC Converter: FeaturesEdsel SilvaNo ratings yet

- ROLPSB SIR745F DS T811036 en CDocument4 pagesROLPSB SIR745F DS T811036 en CVertrauen EngenhariaNo ratings yet

- Specification of Control Board: (Data Sheet / Version 1.4)Document14 pagesSpecification of Control Board: (Data Sheet / Version 1.4)sme_2010No ratings yet

- PCB Diagram: 9-1 Main BoardDocument4 pagesPCB Diagram: 9-1 Main BoardTony SalvianoNo ratings yet

- PCB DiagramDocument4 pagesPCB Diagramgilberto gutierrezNo ratings yet

- Overview Data Sheets: F 3222: 8 Fold Input ModuleDocument2 pagesOverview Data Sheets: F 3222: 8 Fold Input ModulemohamadziNo ratings yet

- Data Sheet HM 9270Document10 pagesData Sheet HM 9270Ivan RomeroNo ratings yet

- R2S15901SP: Digital Delay IC For "Lip Sync"Document8 pagesR2S15901SP: Digital Delay IC For "Lip Sync"ahmedNo ratings yet

- Specification Nta92cDocument6 pagesSpecification Nta92cRajeshNo ratings yet

- Series/Parallel Equivalent Circuits in Excel: Summer CircuitscollectionDocument1 pageSeries/Parallel Equivalent Circuits in Excel: Summer CircuitscollectionPablo Diego Cecere CasadoNo ratings yet

- Hi 3110 - V Rev KDocument54 pagesHi 3110 - V Rev KÁlvaro Eduardo López LimaNo ratings yet

- Video Switch (IC201) Adc/ Pre-AMP/PLL (IC300) Scaling Engine (IC406) TFT LCD (Panel) Tmds (IC601)Document7 pagesVideo Switch (IC201) Adc/ Pre-AMP/PLL (IC300) Scaling Engine (IC406) TFT LCD (Panel) Tmds (IC601)luiz carlos de souzaNo ratings yet

- L6234 3 Fazlı Motor SürücüDocument10 pagesL6234 3 Fazlı Motor SürücüEngin UzunNo ratings yet

- Matsushita FP PLC Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualDocument2 pagesMatsushita FP PLC Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualryoNo ratings yet

- DatasheetDocument16 pagesDatasheetAndres GuerreroNo ratings yet

- DatasheetDocument12 pagesDatasheetAsad AhmedNo ratings yet

- Mitsubish Fx/Fx2N PLC Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualDocument2 pagesMitsubish Fx/Fx2N PLC Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualryoNo ratings yet

- BuR X20 HardwareDocument14 pagesBuR X20 HardwarecelinNo ratings yet

- Kdfi V1.4: User Manual (English)Document12 pagesKdfi V1.4: User Manual (English)MATT WILDNo ratings yet

- 5V / 3.3V Manchester Encoder / Decoder: General Description FeaturesDocument13 pages5V / 3.3V Manchester Encoder / Decoder: General Description FeaturesAndrei MucenicaNo ratings yet

- Technical Service Manual: Q19/L90DPDocument48 pagesTechnical Service Manual: Q19/L90DPMcbborbaNo ratings yet

- Overview Data Sheets: F 3223: 4 Fold Input ModuleDocument4 pagesOverview Data Sheets: F 3223: 4 Fold Input ModulemohamadziNo ratings yet

- Model No. LCD-42K30-HD Service Manual LCD Television File NoDocument41 pagesModel No. LCD-42K30-HD Service Manual LCD Television File NoWee Chuan PoonNo ratings yet

- Model No. LCD-42K30-HD Service Manual LCD Television File NoDocument60 pagesModel No. LCD-42K30-HD Service Manual LCD Television File NoWee Chuan PoonNo ratings yet

- Grundig gmm1100-stf55-1001 t2s08 Chassis (ET)Document23 pagesGrundig gmm1100-stf55-1001 t2s08 Chassis (ET)Simion VictorasNo ratings yet

- 7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetDocument32 pages7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetMecaSoftwareNo ratings yet

- M56710Document8 pagesM56710Roberto SanchezNo ratings yet

- TDA7377 Fiches TechniqueDocument8 pagesTDA7377 Fiches TechniqueOuahid AdaNo ratings yet

- TB67H451FNG: PWM Chopper Type DC Brushed Motor DriverDocument21 pagesTB67H451FNG: PWM Chopper Type DC Brushed Motor Drivermalak na3eemNo ratings yet

- D D D D D D D: LF411 Jfet-Input Operational AmplifierDocument12 pagesD D D D D D D: LF411 Jfet-Input Operational AmplifierKavyashruthi BharanidharanNo ratings yet

- Datasheet4u (4) lf411Document4 pagesDatasheet4u (4) lf411JaviNo ratings yet

- Training Material of MS09A and MS09L ChassisDocument47 pagesTraining Material of MS09A and MS09L Chassisبوند بوندNo ratings yet

- DAEWOO Dal 22v1wcDocument61 pagesDAEWOO Dal 22v1wcMarco Antonio100% (2)

- LCD TV Service Manual: Konka Group Co, LTDDocument16 pagesLCD TV Service Manual: Konka Group Co, LTDpedroNo ratings yet

- Adio Ontrolli: RC-CC1101-SPI-434 Rc-Rhcs-4ChDocument3 pagesAdio Ontrolli: RC-CC1101-SPI-434 Rc-Rhcs-4Chdamian orlowskiNo ratings yet

- ATS177 Hall Effect DatasheetDocument10 pagesATS177 Hall Effect DatasheetAnonymous oyUAtpKNo ratings yet

- Electronic: Programming Terminal PT-100-NDocument2 pagesElectronic: Programming Terminal PT-100-NnisseNo ratings yet

- rt913a_richtekDocument11 pagesrt913a_richtekRagavan RagavanNo ratings yet

- Multi-Channel Power Supply IC For Car Audio Systems: DatasheetDocument44 pagesMulti-Channel Power Supply IC For Car Audio Systems: DatasheetPaulo Roberto s freireNo ratings yet

- Appendix B Communication SettingsDocument2 pagesAppendix B Communication SettingsryoNo ratings yet

- Features: Dual, Low Power CMOS Operational AmplifiersDocument9 pagesFeatures: Dual, Low Power CMOS Operational AmplifiersDibya DeyNo ratings yet

- Service Manual TV GenesisDocument19 pagesService Manual TV GenesisTecniksNo ratings yet

- 300mA Dual LDO Regulator with PORDocument12 pages300mA Dual LDO Regulator with PORTitán SotoNo ratings yet

- Galaxy Dimension 2-Way Audio SystemDocument4 pagesGalaxy Dimension 2-Way Audio SystemLlorenç Alomar LlompartNo ratings yet

- Ti 278910340 HTL Geber WK 4 2 4 680 Ohm en 4016 ScreenDocument4 pagesTi 278910340 HTL Geber WK 4 2 4 680 Ohm en 4016 Screenolivier.bigouretNo ratings yet

- TDA8753A PhilipsSemiconductorsDocument20 pagesTDA8753A PhilipsSemiconductorsDaanNo ratings yet

- MST6M182VG-V6 TopTechDocument11 pagesMST6M182VG-V6 TopTechDairo de jesus Vanegas galloNo ratings yet

- Data Sheet: Dual 16-Bit DACDocument12 pagesData Sheet: Dual 16-Bit DACFetrian IvanNo ratings yet

- Data Sheet: 74HC/HCT238Document7 pagesData Sheet: 74HC/HCT238Andrew S OlmosnNo ratings yet

- Data Sheet: 74HC/HCT238Document7 pagesData Sheet: 74HC/HCT238RudyXPNo ratings yet

- PCB DiagramDocument6 pagesPCB Diagramfreitastsp9166No ratings yet

- LG Master-K Cnet Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualDocument2 pagesLG Master-K Cnet Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualryoNo ratings yet

- 4 / Digit, BCD Output, A/D Converter Features: Data Sheet August 28, 2007Document15 pages4 / Digit, BCD Output, A/D Converter Features: Data Sheet August 28, 2007Erasmo Franco SNo ratings yet

- Toyota CsDocument48 pagesToyota CsSonny De GuzmanNo ratings yet

- Using de Series ADCDocument20 pagesUsing de Series ADCAshish SharmaNo ratings yet

- Lab4 Using - DE - Series - ADCDocument20 pagesLab4 Using - DE - Series - ADCNguyên Trịnh Vũ Đăng0% (1)

- N-Channel Power MOSFET (2A, 600VoltsDocument8 pagesN-Channel Power MOSFET (2A, 600Voltsserrano.flia.coNo ratings yet

- ST 2 N 3904Document6 pagesST 2 N 3904buzzrdNo ratings yet

- 1N5221 To 1N5267: Vishay SemiconductorsDocument7 pages1N5221 To 1N5267: Vishay SemiconductorsJuan RojasNo ratings yet

- 1PS76SB21 BAT721 Series: 1. Product ProfileDocument12 pages1PS76SB21 BAT721 Series: 1. Product Profileserrano.flia.coNo ratings yet

- STD1LNK60Z-1 06 PDFDocument14 pagesSTD1LNK60Z-1 06 PDFRogerio E. SantoNo ratings yet

- Zeners 1n746a-759aDocument3 pagesZeners 1n746a-759aPelotaDeTrapoNo ratings yet

- 1 N 5400Document4 pages1 N 5400Irfan Indra KurniawanNo ratings yet

- Vishay General Semiconductor: FeaturesDocument4 pagesVishay General Semiconductor: FeaturesAdah BumboneNo ratings yet

- Environment Control - Low Pin Count Input / Output (Ec - LPC I/O)Document199 pagesEnvironment Control - Low Pin Count Input / Output (Ec - LPC I/O)Виталий МорозовNo ratings yet

- 1n4148 DiodeDocument4 pages1n4148 DiodeAdela RodriguezNo ratings yet

- Tk12a50d5 Tk12a50d5 Tk12a50d5 Tk12a50d5Document9 pagesTk12a50d5 Tk12a50d5 Tk12a50d5 Tk12a50d5171 171No ratings yet

- It8718f S PDFDocument191 pagesIt8718f S PDFJohnnyKerissonNo ratings yet

- Vishay General Semiconductor: FeaturesDocument4 pagesVishay General Semiconductor: Featurestommy99No ratings yet

- Vishay General Semiconductor: FeaturesDocument4 pagesVishay General Semiconductor: Featurestommy99No ratings yet

- Fan 7601Document12 pagesFan 7601Walter AlvarengaNo ratings yet

- TK11A50D: Switching Regulator ApplicationsDocument6 pagesTK11A50D: Switching Regulator Applicationsserrano.flia.coNo ratings yet

- AO4816 Dual N-Channel Enhancement Mode Field Effect TransistorDocument4 pagesAO4816 Dual N-Channel Enhancement Mode Field Effect TransistorSmail BachirNo ratings yet

- Charge, BAT PCH: LPC Gpio LPC GpioDocument1 pageCharge, BAT PCH: LPC Gpio LPC Gpioserrano.flia.coNo ratings yet

- FAN7530 Critical Conduction Mode PFC Controller: Features DescriptionDocument20 pagesFAN7530 Critical Conduction Mode PFC Controller: Features DescriptionArun GuptaNo ratings yet

- Bu3 8718 IT8718 K V0.8.2 Web 012209Document18 pagesBu3 8718 IT8718 K V0.8.2 Web 012209Luciano LucasNo ratings yet

- FAN7530 Critical Conduction Mode PFC Controller: Features DescriptionDocument20 pagesFAN7530 Critical Conduction Mode PFC Controller: Features DescriptionArun GuptaNo ratings yet

- HP 2000 Inventec 6050A2498701-MB-A02 AMD SchematicsDocument45 pagesHP 2000 Inventec 6050A2498701-MB-A02 AMD SchematicsMarcos NunfioNo ratings yet

- HP 1000 Inventec 6050A2493101-MB-A02 UMA DIS Rev X01 Pavilion G4-2000 Presario CQ35-701tu CQ45-2000 SchematicDocument57 pagesHP 1000 Inventec 6050A2493101-MB-A02 UMA DIS Rev X01 Pavilion G4-2000 Presario CQ35-701tu CQ45-2000 SchematicYenco Barliza Diaz100% (2)

- HP 15-G Series AMD Compal LA-A996P ZSO51 ULC DIS Beema Kabini REV 4.0 SchematicsDocument47 pagesHP 15-G Series AMD Compal LA-A996P ZSO51 ULC DIS Beema Kabini REV 4.0 Schematicsserrano.flia.coNo ratings yet

- Aspire 4349 UnlockedDocument35 pagesAspire 4349 UnlockedMhon Adenip LloquironNo ratings yet

- HP 1000 Inventec 6050A2493101-MB-A02 UMA DIS Rev X01 Pavilion G4-2000 Presario CQ35-701tu CQ45-2000 SchematicDocument57 pagesHP 1000 Inventec 6050A2493101-MB-A02 UMA DIS Rev X01 Pavilion G4-2000 Presario CQ35-701tu CQ45-2000 SchematicYenco Barliza Diaz100% (2)

- LCD TV User Manual for HL19KN1/HL22KN1 ModelsDocument26 pagesLCD TV User Manual for HL19KN1/HL22KN1 Modelsserrano.flia.coNo ratings yet

- Acer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHDocument67 pagesAcer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHWilgen GarciaNo ratings yet

- Acer Aspire 4251 4551 Emachines d440 d640 d640g - Wistron Hm42-Dn Je40-Dn - Rev - 3Document63 pagesAcer Aspire 4251 4551 Emachines d440 d640 d640g - Wistron Hm42-Dn Je40-Dn - Rev - 3chatmarNo ratings yet

- Acer Aspire 8530 Wistron Big - Bear2A Rev-1 SchematicDocument54 pagesAcer Aspire 8530 Wistron Big - Bear2A Rev-1 Schematicserrano.flia.coNo ratings yet

- 27 C 256Document13 pages27 C 256Jose M PeresNo ratings yet

- Using The Circuitmaster 4000M Precision Active Oscilloscope For Circuit AnalysisDocument8 pagesUsing The Circuitmaster 4000M Precision Active Oscilloscope For Circuit AnalysisAnonymous LJTck8PNo ratings yet

- Dismantling Old MCC Panels and Mounting New OnesDocument8 pagesDismantling Old MCC Panels and Mounting New OnesAlinaIordacheNo ratings yet

- Aeros Combat 2 Combat LDocument77 pagesAeros Combat 2 Combat LsebastiaanNo ratings yet

- Silicon NPN Power Transistors: Inchange Semiconductor Product SpecificationDocument3 pagesSilicon NPN Power Transistors: Inchange Semiconductor Product SpecificationSebastian CorreaNo ratings yet

- Synchronization Meters for Manual or Semiautomatic SynchronizingDocument2 pagesSynchronization Meters for Manual or Semiautomatic SynchronizingRobiNo ratings yet

- Electrical Hazards: Eng. Ameen QuranDocument19 pagesElectrical Hazards: Eng. Ameen QuranOmar NaimatNo ratings yet

- CAT24WC256: 256K-Bit I C Serial Cmos EepromDocument10 pagesCAT24WC256: 256K-Bit I C Serial Cmos EepromAntonio ManuelNo ratings yet

- Multisim Software Familiarization LabDocument11 pagesMultisim Software Familiarization LabsharedNo ratings yet

- 13 Ec 558Document1 page13 Ec 558Siva KumarNo ratings yet

- ST26 Parts CatalogDocument26 pagesST26 Parts CatalogdesechableNo ratings yet

- Premium LED Drivers: The Best Cost-Performance SeriesDocument108 pagesPremium LED Drivers: The Best Cost-Performance SeriesXFBCDBVGFBNNo ratings yet

- Cover Letter For Electromotives PVT LTDDocument1 pageCover Letter For Electromotives PVT LTDhamza aslamNo ratings yet

- Medium-Voltage Switchgear: Type 8DA Extendable Fixed-Mounted Circuit-Breaker Switchgear Up To 40.5 KVDocument146 pagesMedium-Voltage Switchgear: Type 8DA Extendable Fixed-Mounted Circuit-Breaker Switchgear Up To 40.5 KVManohar PotnuruNo ratings yet

- The Basics of Variable-Frequency DrivesDocument4 pagesThe Basics of Variable-Frequency DrivesRobertoHerediaJacoboNo ratings yet

- TeSys K contactor data sheetDocument3 pagesTeSys K contactor data sheetAlexandru Octavian GrosuNo ratings yet

- Wire Loop Breaking Alarm System: Given By: G.Lakshmikanth P.Rajashekar N.Anil Reddy Y.NareshDocument14 pagesWire Loop Breaking Alarm System: Given By: G.Lakshmikanth P.Rajashekar N.Anil Reddy Y.NareshNaresh KNo ratings yet

- IP78T05CT IP78T05ACT: FeaturesDocument4 pagesIP78T05CT IP78T05ACT: FeaturesRyn YahuFNo ratings yet

- SF50 - PohDocument624 pagesSF50 - PohAdrien Art'ic Chevaleyre100% (7)

- TLP591B Datasheet en 20170607Document4 pagesTLP591B Datasheet en 20170607Sugeng HariadiNo ratings yet

- A Novel Axial Flux Permanent-Magnet Machine For Flywheel Energy Storage System - Design and AnalysisDocument11 pagesA Novel Axial Flux Permanent-Magnet Machine For Flywheel Energy Storage System - Design and AnalysisedumacerenNo ratings yet

- Service Manual: SSW-10 Subwoofer Infinitesimal IV Subwoofer Servo Controlled Subwoofer RS SubwooferDocument2 pagesService Manual: SSW-10 Subwoofer Infinitesimal IV Subwoofer Servo Controlled Subwoofer RS SubwooferRajoo RamaneyahNo ratings yet

- 4/2 and 4/3 Directional Control Valve Technical SpecsDocument4 pages4/2 and 4/3 Directional Control Valve Technical SpecsVito LaudicinaNo ratings yet

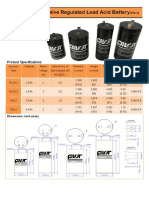

- PILOT Valve Regulated Lead Acid Battery (VRLA) 2v ValveDocument4 pagesPILOT Valve Regulated Lead Acid Battery (VRLA) 2v Valvepenguking_113236970No ratings yet

- Jsisfotek 2021 3 1 034-040Document7 pagesJsisfotek 2021 3 1 034-040RachmanSyahNo ratings yet

- FT-2500M ServDocument76 pagesFT-2500M ServLuis BagarelliNo ratings yet

- Cable On The Reel: Section 13Document20 pagesCable On The Reel: Section 13BolboNo ratings yet

- Holiday Detector Operating InstructionsDocument7 pagesHoliday Detector Operating InstructionsBhavani PrasadNo ratings yet

- SEMIKRON Technical Explanation SKiiP4 F-Option EN 2017-08-30 Rev-02Document21 pagesSEMIKRON Technical Explanation SKiiP4 F-Option EN 2017-08-30 Rev-02mastechNo ratings yet

- ETP4860-B1A2 Embedded Power User ManualDocument93 pagesETP4860-B1A2 Embedded Power User ManualElisvan Jordan Guzman Espinoza100% (1)