Professional Documents

Culture Documents

EEE-489 L4T2 16eee Class-1

Uploaded by

Anurag OviOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EEE-489 L4T2 16eee Class-1

Uploaded by

Anurag OviCopyright:

Available Formats

Level-4, Term-2 (‘16th Batch)

EEE-489: VLSI Technology

Introduction

Dr. Sampad Ghosh

Assistant Professor

Department of Electrical and Electronic Engineering

Faculty of Electrical and Computer Engineering

Chittagong University of Engineering and Technology (CUET)

March 22, 2021

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET)

KYUSHU UNIVERSITY

Syllabus

EEE 489: VLSI Technology (Credit 3.0)

Introduction to MOS devices: design of inverters, static and dynamic

logic circuits, Domino and zipper logic, Custom, semi-custom and cell library

based design, Design of analog building backs, Effect of device scaling on

circuit performance. Overview of IC Technology and its requirements.

Unit steps used in IC Technology: Wafer cleaning, photo-lithography, wet

and dry etching, oxidation and diffusion, ion implantation, CVD and LPCVD

techniques for deposition of poly silicon, silicon nitride and silicon di-oxide,

Metallization and passivation.

Special techniques for modern processes: self-aligned silicides, shallow

junction formation, nitride oxides etc. Process flows for CMOS and bipolar IC

processes. Introduction to process, device, circuit logic and timing

simulation, Hardware description languages for high level design.

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 2

Reference books

1. Gary S. May and Simon M. Sze, Fundamentals of Semiconductor

Fabrication, John Wiley & Sons Inc.

2. Sung-Mo Kang and Yusuf Leblebici, CMOS Digital Integrated

Circuits: Analysis and Design, 3rd ed., McGraw-Hill.

3. James D. Plummer, Silicon VLSI Technology: Fundamentals,

Practice and Modeling, Pearson Education.

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 3

Topics Reference

Introduction

Semiconductor materials, Semiconductor process

S.M. Sze

technology, Basic fabrication steps

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 4

What is Semiconductors?

❑ Semiconductors are materials which have a conductivity between conductors

(e.g., metals) and nonconductors or insulators (e.g., ceramics).

o Semiconductors can be pure elements (e.g., silicon or germanium), or compounds

(e.g., gallium arsenide or cadmium selenide).

❑ Advantages

o Doping provision

o Ability to conduct electrical current

o Regulated conductivity

❑ Si is most widely used

o Can be obtained very easily

❑ Early developments semiconductor – 1600s to 1800s.

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 5

Semiconductor Process Technology

❑ Many important semiconductor technologies have been derived from

processes invented centuries ago.

o Growth of metallic crystals in a furnace was pioneered by Africans living on the

western shores of Lake Victoria more than 2000 years ago.

o Lithography process was invented in 1798 (Originally the pattern or image was

transferred from a stone plate or litho).

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 6

Semiconductor Process Technology…

❑ Technologies applied for the 1st time to semiconductor processing for device

fabrication.

Sl. Year Technology 1. Czochralski technique is used to grow most of

1 1918 Czochralski crystal growth the Si crystal wafers.

2 1925 Bridgman crystal growth 2. Bridgman process used for growth of gallium

3 1952 III-V compounds

arsenide and related compound semiconductor

4 1952 Diffusion

crystals.

5 1957 Lithographic photoresist

3. Welker proved gallium arsenide and III-V

compounds are semiconductor.

4. Basic diffusion theory was considered by Fick in 1855. Alter the type of conductivity using

diffusion was patented by Pfann.

5. Andrus used photosensitive polymer for pattern transfer.

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 7

Semiconductor Process Technology…

Sl. Year Technology 6. Frosch and Derrick found an oxide layer can

6 1957 Oxide masking prevent most impurity atoms from diffusing

7 1957 Epitaxial CVD growth through it.

8 1958 Ion implantation 7. Sheftal et al. describes a technique to form thin

9 1959 Monolithic IC layer of semiconductor materials.

10 1960 Planar process 8. Ion implantation was introduced by Shockley.

9. Noyce proposed monolithic IC by fabricating all devices in a single semiconductor substrate and

connecting devices by Al metallization.

10. In planar process developed by Hoemi, an oxide layer is formed on a semiconductor surface.

With the help of lithography process, portions of the oxide can be removed and windows cut in

the oxide. Impurity atoms will diffuse only through the exposed surface and p-n junctions will

form in the oxide window areas.

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 8

Semiconductor Process Technology…

Sl. Year Technology 11. As the complexity of IC increased, technology

11 1963 CMOS moved from MOSFET to CMOS, and it’s proposed

12 1969 Polysilicon self-aligned gate by Wanlass and Sah. It consumes less power and

13 1971 Dry etching the dominant technology for advanced ICs.

14 1971 Molecular beam epitaxy 12. To improve device performance, polysilicon self-

15 1993 Copper interconnect aligned gate was proposed by Kerwin et al. It

improved device reliability and reduced parasitic

capacitance.

13. As device dimensions were reduced, dry etching technique was developed by Irving et al. to

replace wet etching.

14. MBE by Cho used for vertical control of composition and doping down to atomic dimensions.

15. Cu interconnect introduced by Paraszczak et al. to replace Al for minimum feature lengths

(100nm).

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 9

Basic Fabrication Steps

❑ Today, planar technology is used extensively for IC fabrication.

❑ There are more than 200 processing steps. Major steps are:

✓ Oxidation

✓ Photolithography

✓ Etching

✓ Diffusion and Ion Implantation

✓ Metallization

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 10

Basic Fabrication Steps…

❑ Oxidation

o Development of high quality SiO2 helped to establish the dominance of Si in the

production of commercial ICs.

o SiO2 functions as an insulator in a number of device structures or as a barrier to

diffusion or implantation during device fabrication.

❑ Two methods

1. Dry oxidation 2. Wet oxidation

Cleaned Si wafer

o Dry O2 is used o Water vapor is used

o Used to form thin oxides o Used for thicker layers

because of its good Si-SiO2 because of its higher

interface characteristics growth rate

After oxidation

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 11

Basic Fabrication Steps…

❑ Photolithography

o Used to define the desired geometry.

o After formation of SiO2, wafer is coated with UV light sensitive

polymer (photoresist). Application of resist

o Wafer baked at 80°C to 100°C to evaporate solvent and to

harden resist for improved adhesion.

o Exposed region of photoresist coated wafer undergoes a

chemical reaction depending on type of resist.

o Area exposed to light becomes polymerized and difficult to

remove in an etchant. Resist exposure via mask

o Polymerized region remains when wafer placed in developer,

and unexposed region dissolves and washes away.

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 12

Basic Fabrication Steps…

❑ Etching

o Wafer is again baked at 120°C to 180°C to enhance adhesion and improve resistance

to the subsequent etching process.

o Etching is used to remove materials from the wafer.

o An etch using BHF acid removes unprotected SiO2 surface.

o Resist is stripped away by a chemical solution or O2 plasma system.

Wafer after development After SiO2 removal After resist removal

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 13

Basic Fabrication Steps…

❑ Diffusion and Ion Implantation

o Both are used for adding impurities to the wafer.

o In diffusion method, wafer surface not protected by oxide is exposed to a source with a

high concentration of opposite type impurity. Dopant gas or

accelerated impurity ions

o Impurity moves into wafer crystal by solid state diffusion.

o In ion implantation, impurities introduced by accelerating impurity

ions to a high energy level and then implanting the ions in wafer.

o SiO2 layer serves as barrier to impurity diffusion or ion

implantation.

o Due to lateral diffusion of impurities or lateral straggle of Diffusion or ion

Implantation process

implanted ions, width of p-region slightly wider than window

opening.

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 14

Basic Fabrication Steps…

❑ Metallization

o Used to form ohmic contacts and interconnections.

o Metal films can be formed by physical vapor deposition

(PVD) or chemical vapor deposition (CVD).

o Here, photolithography technique is used to define front

After metallization

contact.

o Similarly back contact formed without using lithography

process.

o A low temperature (≤500°C) anneal also performed to

promote low resistance contact between metal layers and

semiconductor.

PN junction after

complete process

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 15

Summary

❑ Described key semiconductor technologies

❑ Introduced with basic fabrication steps

CHITTAGONG UNIVERSITY OF ENGINEERING AND TECHNOLOGY (CUET) 16

You might also like

- Ee2254 Lica QBDocument0 pagesEe2254 Lica QBnjparNo ratings yet

- Chapter 6 Thermal Oxidation - I Bo CuiDocument23 pagesChapter 6 Thermal Oxidation - I Bo CuisbotacondNo ratings yet

- Fabricating P-N Junction DiodesDocument4 pagesFabricating P-N Junction DiodesRishav SainiNo ratings yet

- EE2254 LIC 2marks 2013Document16 pagesEE2254 LIC 2marks 2013sivagamiNo ratings yet

- Unit 1Document66 pagesUnit 1srgperumalNo ratings yet

- EE6303-Linear Integrated Circuits and Applications Q&ADocument24 pagesEE6303-Linear Integrated Circuits and Applications Q&AY RohitNo ratings yet

- EC1313 Two Marks Linear Integrated CircuitsDocument11 pagesEC1313 Two Marks Linear Integrated Circuitsmoney_kandan2004No ratings yet

- Feynman's Prediction of Storing Encyclopedia on Pin HeadDocument7 pagesFeynman's Prediction of Storing Encyclopedia on Pin HeadGopinath ChakrabortyNo ratings yet

- M Group: Linear Integrated Circuits (Ec1313) IC FabricationDocument17 pagesM Group: Linear Integrated Circuits (Ec1313) IC Fabricationscribdm100% (1)

- CM - MEMS - TWO MARKS Five UNITSDocument7 pagesCM - MEMS - TWO MARKS Five UNITSSandhiyaNo ratings yet

- Chapter 4fabricationofICDocument20 pagesChapter 4fabricationofICManikandan RadhakrishnanNo ratings yet

- Samsung Electronics and Semiconductors ProductionDocument55 pagesSamsung Electronics and Semiconductors ProductionDovah KiinNo ratings yet

- Integrated CircuitsDocument4 pagesIntegrated CircuitsGurjeet ChahalNo ratings yet

- Processing of DevicesDocument31 pagesProcessing of DevicesBituNo ratings yet

- In Order For Silicon To Turn Into A Semiconductor ChipDocument5 pagesIn Order For Silicon To Turn Into A Semiconductor ChipultrasonicdochNo ratings yet

- Introduction To Integrated Circuit TechnologyDocument45 pagesIntroduction To Integrated Circuit TechnologyShrikant JagtapNo ratings yet

- 219 - EE8451, EE6303 Linear Integrated Circuits and Applications LICA - 2 Marks With AnswersDocument8 pages219 - EE8451, EE6303 Linear Integrated Circuits and Applications LICA - 2 Marks With AnswersBALAKRISHNANNo ratings yet

- All Lect MergedDocument685 pagesAll Lect MergedRanjit YewaleNo ratings yet

- Dr. MD Mahfuzur Rahman Assistant Professor, Dept. of IPE: IPE-425: Micromanufacturing (3 Credit Hours)Document21 pagesDr. MD Mahfuzur Rahman Assistant Professor, Dept. of IPE: IPE-425: Micromanufacturing (3 Credit Hours)Nafisa AnikaNo ratings yet

- Ee6303 - Linear Integrated CircuitsDocument13 pagesEe6303 - Linear Integrated CircuitsSaran ArunNo ratings yet

- Cap III-Advanced Materials - 2021 - Shi - Wide Bandgap Oxide Semiconductors From Materials Physics To Optoelectronic DevicesDocument30 pagesCap III-Advanced Materials - 2021 - Shi - Wide Bandgap Oxide Semiconductors From Materials Physics To Optoelectronic Devicessalvador monsalvoNo ratings yet

- Thin Dielectric Layers Characterization Using Corona-Oxide-Semiconductor Measurement TechniqueDocument54 pagesThin Dielectric Layers Characterization Using Corona-Oxide-Semiconductor Measurement TechniqueTejpreet Singh BediNo ratings yet

- Micromanufacturing and Fabrication of Microelectronic DevicesDocument26 pagesMicromanufacturing and Fabrication of Microelectronic DevicesDinie Zulhusni ArsadNo ratings yet

- Micromanufacturing and Fabrication of Microelectronic DevicesDocument26 pagesMicromanufacturing and Fabrication of Microelectronic DevicesDinie Zulhusni ArsadNo ratings yet

- VLSI Fabrication Process PDFDocument6 pagesVLSI Fabrication Process PDFMagotra 9301No ratings yet

- Electrical Study of Si/Ps/Zno:In Solar Cell Structure: SciencedirectDocument7 pagesElectrical Study of Si/Ps/Zno:In Solar Cell Structure: SciencedirectAhmed Sherif CupoNo ratings yet

- Unit-I Ic Fabrication: Part-ADocument32 pagesUnit-I Ic Fabrication: Part-Asanthosh sekarNo ratings yet

- Introduction To IC Fabrication Techniques-1Document5 pagesIntroduction To IC Fabrication Techniques-1gezaegebre1No ratings yet

- Topic#1 Introduction To Semiconductors IndustryDocument28 pagesTopic#1 Introduction To Semiconductors IndustryRio PerezNo ratings yet

- Fundamentals of Integrated Circuit Fabrication StepsDocument55 pagesFundamentals of Integrated Circuit Fabrication Stepsselvi0412No ratings yet

- Tec CmosDocument27 pagesTec Cmosgovind01No ratings yet

- IC FabricationDocument27 pagesIC FabricationJohn PaulNo ratings yet

- Three CMOS Fabrication VideosDocument5 pagesThree CMOS Fabrication VideosPhola PatulinNo ratings yet

- Chapter 6 Thermal OxDocument22 pagesChapter 6 Thermal OxheNo ratings yet

- Material Science: Development TeamDocument12 pagesMaterial Science: Development TeamTejinder SinghNo ratings yet

- EE6303 Linear Integrated Circuits QuestionsDocument7 pagesEE6303 Linear Integrated Circuits QuestionsBALAKRISHNANNo ratings yet

- Silicon Integrated Circuits: Advances in Materials and Device ResearchFrom EverandSilicon Integrated Circuits: Advances in Materials and Device ResearchDawon KahngNo ratings yet

- Fundamentals of Integrated Circuit Fabrication: DR - Debashis de Associate Professor West Bengal University of TechnologyDocument55 pagesFundamentals of Integrated Circuit Fabrication: DR - Debashis de Associate Professor West Bengal University of TechnologySharan ThapaNo ratings yet

- Linear Integrated Circuits GuideDocument47 pagesLinear Integrated Circuits Guidemanoj kumarNo ratings yet

- Lec 4 CMOS Technology ICFabricationDocument46 pagesLec 4 CMOS Technology ICFabricationMainak TarafdarNo ratings yet

- EC1401 VLSI - Question Bank (N.shanmuga Sundaram)Document35 pagesEC1401 VLSI - Question Bank (N.shanmuga Sundaram)Dr. N.Shanmugasundaram50% (2)

- Write A Note On Classification of IC and IC Packages. (Dec 2017)Document60 pagesWrite A Note On Classification of IC and IC Packages. (Dec 2017)5060 Karthikeyan. MNo ratings yet

- Week 4_EMIDocument10 pagesWeek 4_EMIMuhammad ShahzaibNo ratings yet

- Unit I Ic FabricationDocument23 pagesUnit I Ic FabricationBhuvana VaradharajNo ratings yet

- VLSI MID SEM-1 NotesDocument3 pagesVLSI MID SEM-1 NotesAryanSinghNo ratings yet

- Sharma Rao2Document6 pagesSharma Rao2ER Publications, IndiaNo ratings yet

- Chapter 5 Fabrication of Microelectronic DevicesDocument35 pagesChapter 5 Fabrication of Microelectronic Devicesmuhamadsaidi60% (5)

- Integrated Circuit Fabrication ProcessDocument14 pagesIntegrated Circuit Fabrication ProcessSanthosh DheerajNo ratings yet

- SedraSmith6e Appendix ADocument17 pagesSedraSmith6e Appendix Anehalem650No ratings yet

- The Mainstreaming of SOI: G. K. Celler and Andrew WittkowerDocument4 pagesThe Mainstreaming of SOI: G. K. Celler and Andrew WittkowerMarco Aurélio DonatoNo ratings yet

- Course Title: VLSI Technology Course No.: EEE 489Document24 pagesCourse Title: VLSI Technology Course No.: EEE 489Rubel RiadNo ratings yet

- Presentation 1 LicDocument28 pagesPresentation 1 LicreporterrajiniNo ratings yet

- Unit - IDocument69 pagesUnit - IsaravananNo ratings yet

- Lec 3 Thermal OxidationDocument21 pagesLec 3 Thermal OxidationVikram MeenaNo ratings yet

- Applied Solid State Science: Advances in Materials and Device ResearchFrom EverandApplied Solid State Science: Advances in Materials and Device ResearchRaymond WolfeNo ratings yet

- Plasma Etching Processes for Interconnect Realization in VLSIFrom EverandPlasma Etching Processes for Interconnect Realization in VLSINicolas PossemeNo ratings yet

- Assa Abloy MCCDocument2 pagesAssa Abloy MCCAndrey SummNo ratings yet

- McMahon, Morgan E. - Vintage RadioDocument265 pagesMcMahon, Morgan E. - Vintage RadioMichael M. StarkeNo ratings yet

- Caterpillar C11-C13 Engine SchematicDocument4 pagesCaterpillar C11-C13 Engine SchematicMikeas Yaz75% (4)

- Ta Kmsw500Document24 pagesTa Kmsw500Orangzeb Khan0% (1)

- H S ™ PHC P H C: Ypertherm Ensor Lasma Eight OntrolDocument58 pagesH S ™ PHC P H C: Ypertherm Ensor Lasma Eight OntrolCRISTIANNo ratings yet

- PDF d7024 Manual EspañolDocument80 pagesPDF d7024 Manual EspañolCésar JcNo ratings yet

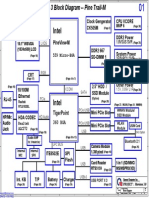

- Lenovo Ideapad S10-3 Schematic - Quanta Mariana 3.0 Pine Trail-M Schematic - FL5 Motherboard PDFDocument40 pagesLenovo Ideapad S10-3 Schematic - Quanta Mariana 3.0 Pine Trail-M Schematic - FL5 Motherboard PDFachyouth50% (2)

- MC2000™ Advanced Deskset: Tone Control L3216 Operator and Installation ManualDocument112 pagesMC2000™ Advanced Deskset: Tone Control L3216 Operator and Installation ManualAlex Gomez50% (2)

- Description: Mechanical DataDocument2 pagesDescription: Mechanical Datadip461No ratings yet

- Unit Oscillators: StructureDocument16 pagesUnit Oscillators: StructuremcamhkNo ratings yet

- TCPST (Thyristor Control Phase Shifting Transformer) Impact On Power QualityDocument6 pagesTCPST (Thyristor Control Phase Shifting Transformer) Impact On Power Qualitykelifa reshidNo ratings yet

- D D D D D D D D D D: DescriptionDocument25 pagesD D D D D D D D D D: DescriptionSofywka SofaNo ratings yet

- Lecture 6Document45 pagesLecture 6eng fourmNo ratings yet

- 3LD25667UB01 Datasheet enDocument8 pages3LD25667UB01 Datasheet enlllNo ratings yet

- Fortnightly Test Series For 11 JEE (Main) - 2024 Test - 01Document1 pageFortnightly Test Series For 11 JEE (Main) - 2024 Test - 01PARTH SARTHINo ratings yet

- Samsung ML 1650schematic Diagram PDFDocument22 pagesSamsung ML 1650schematic Diagram PDFcataroxiNo ratings yet

- Ua 723Document21 pagesUa 723roozbehxoxNo ratings yet

- Ats A Ne11000Th Gx1 ResonatorDocument7 pagesAts A Ne11000Th Gx1 Resonatorba3jarNo ratings yet

- SFRA - Theory and Method - Standards - 120911Document207 pagesSFRA - Theory and Method - Standards - 120911gnpr_10106080100% (5)

- FTV2.3 Power Supply Repair Method: Chapter 09 PageDocument25 pagesFTV2.3 Power Supply Repair Method: Chapter 09 Pageabousalman63No ratings yet

- Common Implementations of Interfaces for Serial and Parallel Data ExchangeDocument5 pagesCommon Implementations of Interfaces for Serial and Parallel Data Exchangeyagnasree_s100% (1)

- Intel Desktop Board D848PMB Product Guide: Order Number: C54219-002Document88 pagesIntel Desktop Board D848PMB Product Guide: Order Number: C54219-002daniNo ratings yet

- L700 Antenna DescriptionDocument4 pagesL700 Antenna DescriptionPoobalan MurugeyaNo ratings yet

- Relay Automotive Catalog 0212Document150 pagesRelay Automotive Catalog 0212nubercard6111No ratings yet

- DGP848 Ep09Document52 pagesDGP848 Ep09Vochin LiviuNo ratings yet

- Energy Power Generation Using Foot Step Method - P.balaji - II EEEDocument4 pagesEnergy Power Generation Using Foot Step Method - P.balaji - II EEEShishir Kant SinghNo ratings yet

- Automatic Alternator Synchronisig by 8085mycroprocessorDocument20 pagesAutomatic Alternator Synchronisig by 8085mycroprocessorSHYAMAL PARIANo ratings yet

- Equip. SpecificationDocument31 pagesEquip. SpecificationSandro Omar Lizano GuzmanNo ratings yet

- Disjuntor Siemens SBDocument98 pagesDisjuntor Siemens SBjoaoNo ratings yet

- dm00237416 stm32f7 Series and stm32h7 Series Cortexm7 Processor Programming Manual Stmicroelectronics PDFDocument254 pagesdm00237416 stm32f7 Series and stm32h7 Series Cortexm7 Processor Programming Manual Stmicroelectronics PDFBraiyan Alex-ander HurtadoNo ratings yet