Professional Documents

Culture Documents

Chapter 5

Uploaded by

Mana LuCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chapter 5

Uploaded by

Mana LuCopyright:

Available Formats

Chapter 5

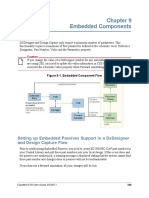

Product Integration

This chapter describes the integration that has been established to carry information between

Expedition™ PCB and other products.

If you want to:

Learn about IDF Information on page 247

Learn about DXF Information on page 250

Learn about IFF Information on page 254

Learn about ICX Information on page 256

Learn about Schematic Integration Information on page 256

Learn about Project Integration Information on page 257

Learn about DX Designer Information on page 273

Learn about Design Architect Information on page 276

Learn about Cross Probe Configuration Information on page 278

Learn about Variant Manager Information on page 282

Learn about OBDG Interface Information on page 282

Learn about OBD++ Information on page 284

Learn about Enterprise 3000 Information on page 290

Learn about Scepter Information on page 290

Learn about OrCAD Information on page 290

Learn about HyperLynx Information on page 291

Learn about XTK/QE Information on page 292

IDF

The Intermediate Data Format (IDF) allows the exchange of mechanical information between

the PCB design environment and a mechanical design environment that supports IDF

Import/Export. IDF Import only imports those items which are supported by IDF Export. IDF

versions 2.0 or 3.0 can be imported into the PCB environment.

IDF supports only through via obstructs and no layer specific information is present for via

obstruct in the IDF exported file, therefore, any via obstructs are imported to ALL layers. Any

Expedition PCB User’s Guide, EE2007.1 247

Product Integration

IDF

warning messages display in the IDFImport.txt log file. By using IDF files, PCB mechanical

features can be moved into the mechanical design environment, where interference checking

can be performed to ensure that the design can be built.

Figure 5-1. Import IDF

If mechanical interference problems are found, elements can be moved in the mechanical

environment and then these changes can be integrated back into the design environment by

importing the modified IDF file.

Note

Design rule violations are not prevented during IDF import. Parts are moved to their new

locations without regard to what may already be in that area of the board. The board file

places / replaces the following elements in the design file.

Table 5-1. IDF and Expedition PCB Elements

IDF Name Expedition PCB Name

Part Placement Parts

Board outline Board outline

Board outline (cutout option) Contours

Drilled holes Mounting holes

Route outline Route border

Route keepout Route obstruct

Place keepout Placement obstructs

Place region Rooms

248 Expedition PCB User’s Guide, EE2007.1

Product Integration

IDF

Note

Parts that were placed in the design in PCB are moved to any new XY locations defined

in the IDF file. However, if the part was not previously placed but is in the IDF file, it will

NOT be placed from the library into the design.

The IDF board file does not contain netlines, traces and/or vias. The library file contains

information that defines each part in the design. Electrical and mechanical parts are defined. We

do not support the specification of properties for electrical parts.

The Library file contains the following information.

Table 5-2. IDF and Expedition PCB Library File

IDF Name Expedition PCB Name

Geometry Name Package Cell name

Part number Part number

Units definition (mm or thou) Units definition (mm or thou)

Part height Height

Part outline Placement outline

In Export IDF, nested mechanical cells are not exported to IDF separately. Only the package

cell is exported with an outline which includes the nested mechanical cells. The default value

for Board thickness is .062 inches. The default height for part height is .100 inches. The default

part height is only assigned to those parts that do not have a part height assignment in the part

entry or the cell database. The order in which a height is checked is:

In the Part Editor

In the cell database

The default on the dialog.

Buried cells are not exported to IDF, they are ignored. Test points placed with the Place Test

Point command are not exported to the IDF file. Only schematic test points placed with the

Place Part command are exported to the IDF file.

Route obstructs, built within cells and padstacks, are exported and they are written out as if they

were board level objects. Route obstructs by layer are also exported to IDF.

Expedition PCB User’s Guide, EE2007.1 249

Product Integration

DXF

Figure 5-2. Export IDF

A Mechanical Verification log file, IDFExport_out.txt, and an ECAD / MCAD Name

Correspondence file, ecad_hint.map are created. The Mechanical Verification log file contains

the IDF version number and any information regarding objects which could not be exported.

The final line of the log file states whether the process was successful and reports the total

number of warnings. The ECAD / MCAD Name Correspondence file is only used by Pro-

Engineer. Previous versions of the IDF translator used ecadhint.map as the filename, however,

the underscore must be present in the filename for Pro-Engineer to recognize the file.

A correspondence does not always exist between the elements found in the PCB design file and

the IDF file. In cases where an IDF record is necessary but the particular attribute is not found in

the PCB design file, default settings are used.

DXF

DXF (Drawing Interchange) is a file format created by AutoDesk, Inc. which you can use to

exchange data between Expedition PCB and many CAD and graphical applications. Expedition

PCB supports R14 DXF ASCII files. DXF data is only allowed to be imported into user defined

layers. DXF Import creates a DXF cell of all the data that is imported, stores that data in the cell

library and the DXFCell is placed on the board.

Note

DXF data is only allowed to be imported onto Expedition PCB User Layers.

250 Expedition PCB User’s Guide, EE2007.1

Product Integration

DXF

Figure 5-3. DXF Import

Once the dxf file is imported, the original extents (min/max x/y) display in the dialog. These

extents cannot be edited.

Multiple DXF cells reside in the local cell library after import completes. The Place Parts and

Cells dialog should be used to place the DXF cells within a single layout design. DXF cell types

are listed as drawing cells. You can select individual components of the DXF cells in Draw

Mode. Place Mode will allow you to move DXF cells to a different location. To differentiate the

DXF cells from other drawing cells the name must be prefixed with "DXF_".

It is important not to change the object type of DXF imported elements, you should make a copy

of the element and then change those properties. If a DXF file is placed in a design and then the

elements are moved from user-layer to another object, it is not possible to carry out an ASCII

Export then ASCII Import on the layout.hkp file because of errors that the drawing cell may not

contain the other objects' keyword.

If the DXF Cell Name field is blank, the Import mode is New. This allows a new DXF file to be

created in the local library. If an existing DXF filename is selected the Import Mode displays

the following options:

Append Cell - Adds selected information to existing selected DXF cell. The orientation

and location of the cell, within the layout design, stays the same.

Expedition PCB User’s Guide, EE2007.1 251

Product Integration

DXF

Overwrite Cell - Completely overwrites the original cell. The orientation and location of

the cell, within the layout design, stays the same.

Overwrite Layers only - Overwrites existing selected cell layer.

When the Custom Pads and Drill Symbols tab is active in the Padstack Editor, the Padstack

Editor’s File pulldown allows you to display the Import DXF dialog that allows you to append

or overwrite data on DXF layer names.

Figure 5-4. DXF Import From Padstack Editor

This dialog has limited functionality from the one accessed from within Expedition PCB, you

cannot map DXF layer names to User Layers and font Mapping is not available. DXF files

created in Expedition PCB contain no electrical intelligence. This version of DXF is only

graphical.

In DXF Export there is a 255 character string limitation in the DXF Export Layer Name field,

however the DXF file format only allows 31 characters for Layer Name.

Although there are no restrictions other than spaces for the layer names, AutoCAD only allows

characters A-Z, 0-9, $, _, and -. If any of the layer names contain characters other than these and

you plan to import this DXF file into AutoCAD, you will want to edit the layer names to remove

the other characters.

Schemes to use with export DXF can be created for future use and can be selected from this

pulldown.

252 Expedition PCB User’s Guide, EE2007.1

Product Integration

DXF

Figure 5-5. DXF Export

When writing out DXF data, the only DXF element types written are:

DXF Line - used for all lines

DXF Arc - Used for all arcs

DXF Polyline - Used for all closed shapes. Arcs have to be stroked.

DXF Text - Used for all text.

DXF Circle - Used for all circles.

DXF Solid - Used to represent a filled rectangle placed at 0, 90, 180 or 270 degrees.

DXF Hatch - Used to fill circles and closed polylines. (Note: the DXF Hatch element is

not supported by Microstation SE.)

MicroStation will truncate layer names to 16 characters, but will put the full layer name in a

comment field. If this DXF file is to be imported into MicroStation and the truncation will be a

problem, you will need to edit the default DXF Layer Names to be 16 characters or less.

Expedition PCB User’s Guide, EE2007.1 253

Product Integration

IFF

IFF

IFF (Intermediate File Format) is a file format created by Agilent Technologies ADS tool which

you can use to exchange data from Expedition PCB into many CAD and graphical applications.

The imported data is a flat graphical object within Expedition PCB. If an ADS layer is not

mapped, the data associated with that layer is not imported.

Note

Import / Export IFF should not be used for round trips between Expedition PCB and

ADS. Each of these functions are independent of each other and should be used

independently.

Figure 5-6. IFF Import

The integration is performed using .iff files and when the .iff file is imported into Expedition

PCB, the local part is populated with the part number and cell information needed for the RF

circuit and it is fixed to prevent modification to any conductive layer, however all layers can be

moved and rotated as a block.

You can also use the Cell Editor to adjust port pins, padstacks, parts and/or cells to improve the

design's routing.

254 Expedition PCB User’s Guide, EE2007.1

Product Integration

IFF

The IFF Export dialog allows you to modify the IFF output filename, select the layers to be

exported, change the IFF layer name(s) to be used and optionally select the area of the design to

be exported.

Figure 5-7. IFF Export

You can export the entire design or a portion of a design to an (.iff) file located in the ../output

directory for the current design. This file can then be imported into the Agilent Advanced

Design System (ADS) tool for analyst / simulation.

A port-mapping file is also produced in the ../output directory, with a .txt extension. This file

contains properties for the pins and ports exported to the IFF file.

The IFF Layer Name field has a 255 character string limitation, however the IFF file format

only allows 31 characters for Layer Name. A warning dialog appears if you have more than 31

characters and /or spaces in the Layer Name. Although there are no restrictions other than

spaces for the layer names, the only characters allowed are A-Z, 0-9 and _(underbar). If a layer

is specified, all of the above elements are written out, however, if only Layer 1 is specified and

the vias go from layer 1 to layer 2, only the layer 1 via pad is written. Elements which may be

included in the output file are:

Expedition PCB User’s Guide, EE2007.1 255

Product Integration

ICX

Traces

Pads

Vias

Pins

Component outlines

Area fills (plane data)

ICX

The Import from ICX interface was developed to extract the necessary data within ICX® and

create an Expedition database. When you are finished using the ICX application, you use the

ICX to Expedition interface to get IS data into Expedition format. The ICX to Expedition

Interface gives you the ability to:

Export all, or a partial set of trace and via definitions from an open IS design.

Export all, or a partial set of component placement definitions from an open IS design.

The Export to ICX option allows the exchange of high speed information from PCB to the

Mentor Graphics Interconnect Synthesis (IS) environment. This provides a single integrated

environment for electrical rules entry, signal integrity and delay analysis, crosstalk analysis and

rules checking.

The files necessary to launch the IS tools are created and are stored in the <jobs>/output/icx

subdirectory and, if required, these data files can be moved to a UNIX based environment.

When all the files have been created, IS automatically displays with the data files loaded.

Schematic Integration

Back Annotation and Forward Annotation are the methods used to pass data between the

schematic databases and Expedition PCB. Forward Annotation is run from within Expedition

PCB and loads the schematic’s logic data into the board. Batch Annotation takes any logic

changes made on the board and sends this information back to the schematic databases. Back

Annotation from PCB layout to the schematic is accomplished automatically when you perform

a save. Back Annotation is performed interactively using the Project Integration Back

Annotation icon and from the ECO Back Annotation command in PCB layout. All commands

that require a back annotation to the schematic can be deactivated by deselecting the Back

Annotation option in the Project Integration dialog in PCB layout or in the PCB Integration

dialog in Design Capture.

Use Forward Annotation if there have been changes made to the schematic since the last

compiled database. As with Back Annotation, using the PCB Integration dialog in the schematic

capture package can prevent Forward Annotation. This status may be set to prevent extraction if

256 Expedition PCB User’s Guide, EE2007.1

Product Integration

Project Integration

the schematic designer is making changes to the schematic and does not want data to be

extracted from the database until it is ready.

Project Integration

The Project Integration command is used to establish a link between a schematic, CES and a

PCB design and to designate how the flow of information between the two is to be handled;

either through Back Annotation or Forward Annotation. This association enables you to see

which functions of integration are available by the colored buttons displayed in the Schematic

status settings.

Figure 5-8. Project Integration

If a DXDesigner, Design Architect, CAE, Keyin, or Foreign iCDB netlist is going to be used,

this dialog allows you to edit the project file by associating the foreign netlist.

Expedition PCB User’s Guide, EE2007.1 257

Product Integration

Project Integration

If the design will be using schematic data from Design Capture, the project file should be placed

so its location is relative to both the schematic and PCB jobs. Design Capture also provides an

interface to allow creation and editing of the project file.

Project Indicator Light in Layout

Indicator lights display in the Status Bar area as shown below:

Figure 5-9. Project Indicator Lights

The indicator lights show the status of the connectivity and constraint data between the front-

end and back-end central database.

The lights are green when Forward Annotation is not required; there are no available pending

Schematic CES changes and no available pending PCB CES changes.

Caution

Caution: If all lights are green this does not necessarily mean that everything is in sync. It

simply means that there are no outstanding changes on the front-end to be pulled into the

PCB and there are no outstanding PCB CES changes to be loaded.

The lights flash amber when there is data on the schematic that needs to be forward annotated or

loaded (in the case of CES constraints) into the PCB.

(1) This light is for Connectivity and it indicates if Forward Annotation is needed based on

schematic changes. Clicking on this indicator invokes ECO > Forward Annotation.

If Red:

Schematic connectivity changes are pending.

Forward Annotation is disabled in Schematic.

If Amber

Schematic connectivity changes are pending.

Click to run Forward Annotation.

If Green

Schematic connectivity and board in sync.

258 Expedition PCB User’s Guide, EE2007.1

Product Integration

Project Integration

(2) This light is for schematic CES constraints and it indicates that CES changes have been

made in the schematic and need to be loaded into the PCB. Clicking on the this indicator, loads

the schematic CES constraints into the PCB.

If Amber

Schematic CES changes are pending.

Click to pull schematic constraint changes into board.

If Green

There are no pending schematic CES changes to be pulled into board.

(3) This light is for the PCB CES constraints and it indicates that CES changes have been made

but have not yet been loaded into PCB. Clicking on this indicator, loads the PCB CES

constraints into PCB.

f Amber

PCB CES changes are pending.

Click to load PCB CES constraint changes into the board.

If Green

There are no pending PCB CES changes to be loaded into the board.

Schematic Connectivity and Constraint Status Section

These buttons indicate the status and also, when pressed, perform the associated function. There

are four different areas that allow synchronization in the PCB design:

Front-end changes - connectivity.

Front-end CES changes.

Back-end CES changes.

Back-end changes ñ gate and pin swaps, renumber reference designators, etc.

When the front-end or back-end are not in synch, the buttons are amber, indicating that you can

select those buttons and synchronize the data. If back annotation or forward annotation has been

prevented by settings in the schematic, and the data is out of synch, then the buttons are red and

you cannot synchronize by pressing the button. When you press a red button, an informative

dialog displays explaining why you cannot synchronize the data.

When there is no specific action to be taken, all the indicators appear green. However, that fact

that the indicators are green does not indicate that all the data in the front end and back end are

synchronized.

Expedition PCB User’s Guide, EE2007.1 259

Product Integration

Project Integration

Loading PCB CES Data

When you press the Load pending CES changes into PCB indicator, the CES changes are

loaded and the Back Annotation required indicator is changed to Amber or Red, depending on

whether Back annotation is prevented or allowed. This acts as a reminder that a Back

Annotation is necessary to ensure that PCB CES changes are synchronized with the Schematic

CES data.

Synchronization Options

There will be times when all four different areas that allow synchronization need to be

synchronized. When this situation occurs, some rules are applied to stop the changes

overwriting.

Forward and Back Annotation Order

When forward and back annotation changes exist, a back annotation must be run before a

forward annotation. The rules to be following during a back annotation and forward annotation

process are defined in the project file. The rule definition basically tells whether a front-end or

back end change wins, when the information has been changed on both sides.

If you select the Front-end changes button first, back-annotation is automatically run so you

cannot do things in the wrong order.

Load pending schematic CES changes into PCB

When this option is selected, any CES data that can be loaded into PCB is loaded. There are

times when there may be nets available in the schematic that are not yet available in the PCB. If

the schematic nets have constraints on them and those nets are not yet in the PCB, we cannot

push those constraints into PCB CES. Therefore, to make absolutely sure that all CES data is

synchronized, we recommend you run forward and back annotation because connectivity will

always match at that point.

Disabled Forward Annotation / Back Annotation - DxDesigner

Flow

You can allow or prevent forward and backward annotation from occurring in a design project

by setting the appropriate options in the DxDesigner Design Configuration dialog. When

forward or backward annotation is disabled in this dialog, information is presented explaining

why the front-end and back-end cannot be synchronized.

When the annotation is disabled and annotation is required due to changes in the schematic or

PCB, the Project Integration status buttons are displayed in red and continue to display the

appropriate status. However, when you press the forward or back annotation required buttons, a

warning dialog is displayed.

260 Expedition PCB User’s Guide, EE2007.1

Product Integration

Project Integration

Forward /Back Annotation is required to synchronize the schematic and PCB

data. However, forward / back annotation is displayed in the DXDesigner

Design Configurations dialog. Enable forward / back annotation in

DXDesigner and then try again.

Additionally, when an annotation is disabled but annotation is not required, the indicators are

green. No annotation is necessary, however, because the indicator is green, there is no clear

indication that annotation is prevented because of settings in the schematic. In order to clearly

communicate the status of the annotation, warning dialogs are displayed when the green

indicator is pressed.

Forward Annotation was requested but forward annotation is disabled in the

DXDesigner Design Configurations dialog. If you want to run forward

annotation, enable forward annotation in DXDesigner and try again.

Back Annotation was requested but back annotation is disabled in the PCB Project Integration

dialog or in the DXDesigner Design Configurations dialog. If you want to run back annotation,

enable back annotation in the PCB or schematic and try again.

Disabled Forward Annotation / Back Annotation - DC Flow

You can allow or prevent forward and backward annotation from occurring in a design project

by setting the appropriate options in the Design Capture / Design View PCB Integration dialog.

The same messages display referencing the design Capture / Design View PCB Integration

dialog. These messages only apply when the indicator is red.

Forward /Back Annotation is required to synchronize the schematic and PCB

data. However, forward / back annotation is displayed in the PCB

Integration dialog. Enable forward / back annotation in Design Capture or

Design View and then try again.

Additionally, when an annotation is disabled but annotation is not required, the indicators are

green. No annotation is necessary, however, because the indicator is green, there is no clear

indication that annotation is prevented because of settings in the schematic. In order to clearly

communicate the status of the annotation, warning dialogs are displayed when the green

indicator is pressed.

Forward Annotation was requested but forward annotation is disabled in the Design Capture or

Design View PCB Project Integration dialog. If you want to run forward annotation, enable

forward annotation in Design Capture or Design View and try again.

Back Annotation was requested but back annotation is disabled in the PCB

Project Integration dialog or in the Design Capture or Design View PCB

Project Integration dialog. If you want to run back annotation, enable

back annotation in the PCB or schematic and try again.

Library Extraction Section

The library extraction options allow you to:

Expedition PCB User’s Guide, EE2007.1 261

Product Integration

Project Integration

Only extract missing library data

Update local libraries with newer Central Library data

Rebuild local library data; preserve locally built data. Anything that was built locally for

the design is preserved, but all part, cells, etc., built through the Central Library are

updated from what is currently in the Central Library.

Delete local data; then rebuild all library data. Removes everything (built locally and

through the Central Library) and extracts everything from the Central Library.

Select to allow Forward Annotation to respect alpha-only reference designators. If this is

option is not checked, all reference designators are changed to alpha-numerics.

Trace Removal Options

The trace removal options allow you to:

Select to remove floating traces and vias.

Select to remove hangers.

Select to allow Forward Annotation to assign nets to unused pins; this enables fanout

and facilitates routing.

Select to allow any reference designator changes in the schematic to be annotated to the

output file.

Back Annotation Options

You can disable back annotation in the AutoActive environment by selecting the Disable

commands that create Back Annotation changes option. Another way to prevent back

annotation is to modify the project file and set the prevent back annotation flag.

Back Annotation to the Schematic

Back Annotation compares the design file with the current schematic database. Back

Annotation must be executed when changes, not reflected in the schematic database, are made

to the board design. Back Annotation is automatically performed during the save, after you

execute the following commands:

Place -> Automatic -> Swap by Part Number

Route -> Swap -> Pins

Route -> Swap -> Gates

ECO -> Renumber Ref. Des.

262 Expedition PCB User’s Guide, EE2007.1

Product Integration

Project Integration

Route -> Planes -> Routed Plane Pins

Setup -> Editor Control (Rooms and Clusters Tab)

These commands do not require a back annotation but are sent back to the schematic database

on a save:

Setup -> Setup Parameters

Setup -> Net Class & Clearances

Setup -> Net Properties

Route -> Netline Order

The design entry tools control whether the data is back annotated into the schematic. The

automation of these steps is controlled by the design entry tools and the Project Integration

command, therefore certain commands which need to be back annotated are disabled until the

schematic engineer allows Back Annotation into the schematic.

Table 5-3. Back Annotation Schematic Information

DX Designer The NetpropsBack.hkp (optional), expedition.cfg and the

expedition.cns (constraint definition) files are created in the

DXDesigner component directory. These files are

processed by DXDesigner to apply changes to the design

viewpoint.

If changes have been made in PCB and are to be back-

annotated to DXDesigner, you may receive a message that

states that the process was successful. However, it is wise to

check the dxdbck.txt file in the ../LogFiles directory to

check that there were no errors.

Closing and opening the schematic ensures that the changes

are seen in DXDesigner.

Design Architect An ASCII backannotation file (expbackanno.txt) is created

in the Design Architect component directory. This file is

processed by Design Viewpoint Editor to apply changes to

the design viewpoint.

Design Capture After an iCDB compile is performed by Design Capture,

the "Schematic and PCB Design database synchronized"

indicator in PCB layout turns red indicating a change on the

Design Capture side. The layout engineer should run

Forward Annotation (after the iCDB has been compiled) to

synchronize the schematic and PCB layout databases.

Expedition PCB User’s Guide, EE2007.1 263

Product Integration

Project Integration

Forward Annotation - Database Load and Netload

Forward Annotation prepares the board for layout based on the logic contained in the schematic

tools and attached Central Library. Database Load compiles the netlist source (Design Capture

iCDB, DXDesigner, Design Architect, Keyin Netlist, CAE Netlist, or GDB) into a binary

format and builds databases that can be accessed by PCB layout. The database includes

information extracted from the netlist and the attached Central Library. Database Load

automatically creates a local Parts Database and local cell library using paths to the Parts

Databases and cell libraries found in the Central Library.

For DC > CES designs, if there have been any connectivity changes in the schematic (renaming

nets), and the new foreign integrated common database is exported, when the pcb job is opened

in the back-end, a warning message is displayed.

Warning: Some of the layout data for this design conflicts with data being

loaded from CES. Some constraints may not be loaded properly. See the

logfile ces_load.txt for details.

Running Forward Annotation will update the changes in layout and back-end CES.

Forward Annotation is the mechanism to provide integration between design entry schematics

and PCB design files. When invoked from the ECO pulldown, the settings defined in the Project

Integration dialog are used.

Note

Packager is used for Forward Annotation, therefore, any changes made to the local library

in the Part Editor must be transferred to the Central library before Forward Annotate is

run.

If the schematic is ready for Forward Annotation, (the LED is green on the Project Integration

dialog and the Forward Annotation option on the ECO pulldown is sensitive), the Database

Load and Netload commands are automatically run.

Database Load provides integration between design entry schematics and PCB design files.

Database Load translates the CAE input into a binary format and builds a database that can be

accessed by PCB layout. The database includes information extracted from the iCDB, the Parts

Database, and the cell library. Database Load automatically creates a local Parts Database and

local cell library using paths to the Parts Databases and cell libraries found in the Central

Library.

Netload runs after Database Load and is used to update the design based on any changes that

have been made since the last Forward Annotation has been run. This includes changing cells,

nets, optionally removing parts that are no longer used in the schematic and traces that conflict

with the new schematic’s logic.

If the Net Classes and Clearances or Setup Parameters dialog changes in Design Capture,

opening the same dialog from Expedition PCB will ask you to copy over the newer Design

264 Expedition PCB User’s Guide, EE2007.1

Product Integration

Project Integration

Capture database into Expedition PCB. These two commands do not require a forward

annotation. However, a change to the Net Properties dialog in Design Capture does require a

forward annotation.

If there are any errors during Forward Annotation, a dialog appears directing you to view the

files using File Viewer. If there are any errors during the Database Load portion of Forward

Annotation, Netload is not run. Correct any errors and re-run Forward Annotation.

Requirements

If the pin name of a component, especially in terms of BGAs are in lower-case (m10, n10), this

causes a problem if you are using the KEYIN.netlist in the .KYN format. The file is not forward

annotated unless the entries are in upper-case (M10, N10).

Any changes made to the Cluster and Room definitions (within Editor Control) and the Routed

Plane Pin command must be Back Annotated so the data is not lost during the next Forward

Annotation.

If you change any of the Component Properties for a part in the Part Editor, you are required to

run the Reset option in the ECO > Replace Cell command before running Forward Annotation.

This ensures that the correct Component Properties are attached to the part in the Database.

CES Integration

CES synchronization works in this manner to provide more opportunities for constraint

alignment in all of its flows. Because both forward annotation and back annotation result in full

constraint synchronization, overall design state is less of an issue for update purposes.

For example, when your DxDesigner data is changing less frequently as you move toward

manufacturing start, forward annotating to PCB gives you more opportunities to acquire

constraint changes made in PCB-CES. Due to the large volume of design changes that can occur

in the back-end at the end of the PCB creation cycle, forward annotating to get back-end

constraint changes saves time because there are few or no schematic changes to communicate to

your layout design.

Load Pending Schematic Changes into PCB using the Project Integration

Dialog

When this option is selected, any CES data that can be loaded into PCB is loaded into PCB and

the schematic and PCB CES data are synchronized.

Sometimes, there may be nets available in the schematic that are not yet available in the PCB. If

the schematic nets have constraints on them and those nets are not yet in the PCB, those

constraints cannot be pushed into PCB CES; therefore, the data cannot be fully synchronized.

To make sure that all CES data is synchronized it is recommended to run forward and back

annotation because connectivity will always match at that point.

Expedition PCB User’s Guide, EE2007.1 265

Product Integration

Netlist Types

Save in CES

CES immediately updates the central database with every change, so there is no longer a Save

capability in CES. The indicator buttons alert you to CES changes and allow you to pull them

into the layout database.

Roll Back Constraint Changes Warning

You can selectively roll back constraint changes made at any time during your current CES

session. This includes all commands for which undo/redo is supported. For example, modifying

constraint classes and net classes, adding clearance rules, and creating differential pairs.

Caution

When rolling back constraint changes made in CES, the forward and back annotation

indicator lights for your design flow do not reflect these undo actions. For example, after

you make a single change in back-end CES and then rollback that change, your back-end

system will still indicate that you need to perform back annotation.

Netlist Types

Expedition PCB supports different types of schematic input; Schematic iCDB, Foreign iCDB,

DXDesigner, Design Architect (DA), Keyin Netlist, CAE Netlist, and GDB Netlist.

Schematic iCDB

This is created by Design Capture. The following is how the project file indicators behave when

an Expedition PCB and Design Capture are using the same project file.

Forward Annotation allowed - This indicator will always be green except when Back

Annotation needs to be run or Design Capture has selected the option to not allow Forward

Annotation.

Schematic and Layout databases synchronized - This indicator will be red anytime the

information has changed on the board or in the schematic that causes the job to become out of

sync.

Back Annotation Allowed - This indicator is only red when the Disable commands that create

Back Annotation changes checkbox is selected and when Forward Annotation is required.

The following are the commands that respect the Back Annotation Allowed project file

indicator:

Place -> Automatic -> Swap by Part Number

266 Expedition PCB User’s Guide, EE2007.1

Product Integration

Netlist Types

Route -> Swap -> Pins

Route -> Swap -> Gates

ECO -> Renumber Ref. Des.

Setup -> Editor Control (Rooms/Clusters Tab)

Route -> Planes -> Routed Plane Pins

The following are the commands that will run even if back annotation is NOT allowed:

Setup -> Net Properties

Setup -> Setup Parameters

Setup -> Net Class & Clearances

Route -> Netline Order

Foreign iCDB

This is created by Design Capture. This is the same database used when Design Capture and

Expedition PCB are integrated to the same project file but this iCDB is used when the

Expedition PCB and Design Capture are not sharing the same project file. The following is how

the project file indicators behave when a Foreign iCDB is used as the schematic netlist:

Forward Annotation allowed - This indicator is always green except when the project file

does not point to a iCDB Foreign Netlist.

Schematic and Layout databases synchronized - This indicator will be red anytime the

information has changed on the board that needs to be manually sent back to Design Capture.

Since Forward Annotation updates the Net Properties database, this indicator will be red as soon

as Forward Annotation is run.

Back Annotation Allowed - This indicator is only red when the Disable commands that create

Back Annotation changes checkbox is selected.

The following are the commands that respect the Back Annotation Allowed project file

indicator:

Place -> Automatic -> Swap by Part Number

Route -> Swap -> Pins

Route -> Swap -> Gates

Expedition PCB User’s Guide, EE2007.1 267

Product Integration

Netlist Types

ECO -> Renumber Ref. Des.

Setup -> Net Properties

Setup -> Editor Control (Rooms/Clusters Tab)

Setup -> Setup Parameters

Setup -> Net Classes & Clearances

Route -> Planes -> Routed Plane Pins

Route -> Netline Order

If you want to keep all the netline ordering, delay formulas and parallel rules which are created

when using Net Properties and you are running a foreign iCDB, you must manually copy the

following files from the Expedition PCB \logic\CDBBAM directory to the Design Capture

schematics \CDB\Layout directory:

iCDBBackAnno.bam

JobPrefsDB.jpf

NetClassDB.ncl

NetPropsDB.npr

PadstackDB.psk

RtdPlane.caf

Once these files are copied, you must run Back Annotation from the Design Capture Other

Utilities dialog on the iCDBBackAnno.bam file. If Back Annotation is required and you run

Forward Annotation a message appears stating that Back Annotation changes will be lost if you

continue.

Keyin Netlist

User keyin of the schematic connectivity using an ASCII Text editor typically creates the Keyin

Netlist. The following is how the project file indicators should behave when a Keyin Netlist is

used as the schematic netlist:

Forward Annotation allowed - This indicator is always green as soon as the Keyin netlist is

attached to the job.

268 Expedition PCB User’s Guide, EE2007.1

Product Integration

Netlist Types

Schematic and Layout databases synchronized - This indicator will be red anytime the

"logic\ NetlistBackAnno.txt" file exists with data. This file contains the changes made to the

schematic since the last Forward Annotation.

Back Annotation Allowed - This indicator is only red when the "Disable commands that create

Back Annotation changes" checkbox is selected.

The following are the commands that respect the Back Annotation Allowed project file

indicator:

Place->Automatic->Swap by Part Number

Route->Swap->Pins

Route->Swap->Gates

ECO->Renumber Ref. Des.

Setup->Editor Control (Rooms & Clusters Tab)

Route->Planes->Routed Plane Pins

The following commands are allowed to run even if back annotation is NOT allowed:

Setup->Setup Parameters

Setup->Net Classes & Clearances

Setup->Net Properties

Route->Netline Order

CAE Netlist

A program to represent the connectivity of a schematic creates this Netlist. This ASCII file is

the same format as a Keyin Netlist except it has a %symbol section. The following is how the

project file indicators should behave when a CAE Netlist is used as the schematic netlist:

Forward Annotation allowed - This indicator is always green as soon as the CAE netlist is

attached to the project.

Schematic and Layout databases synchronized - This indicator is red anytime the "logic\

NetlistBackAnno.txt" file contains changed. This file is used to update the schematic source of

the CAE Netlist. It contains the changes since the last forward annotation.

Back Annotation Allowed - This indicator is only red when the "Disable commands that create

Back Annotation changes" checkbox is selected.

Expedition PCB User’s Guide, EE2007.1 269

Product Integration

Netlist Types

The following are the commands that respect the Back Annotation Allowed project file

indicator:

Place->Automatic->Swap by Part Number

Route->Swap->Pins

Route->Swap->Gates

ECO->Renumber Ref. Des.

Setup->Editor Control (Rooms & Clusters Tab)

Route->Planes->Routed Plane Pins

The following commands are run even if back annotation is NOT allowed:

Setup->Setup Parameters

Setup->Net Classes & Clearances

Setup->Net Properties

Route->Netline Order

These results of the previous commands do not require a back annotation when a CAE Netlist is

used as schematic input.

DXDesigner

This is created by DXDesigner. This is the same database used when DXDesigner and

Expedition PCB are integrated to the same project file. The following is how the project file

indicators behave when a DXDesigner netlist is used as the schematic netlist:

Forward Annotation allowed - This indicator is always green except when the project file

does not point to a DXDesigner Netlist.

Schematic and Layout databases synchronized - This indicator will always be greyed out

(inactive).

Back Annotation Allowed - This indicator is only red when the Disable commands that create

Back Annotation changes checkbox is selected.

The following are the commands that respect the Back Annotation Allowed project file

indicator:

Route -> Swap -> Pins

270 Expedition PCB User’s Guide, EE2007.1

Product Integration

Netlist Types

Route -> Swap -> Gates

ECO -> Renumber Ref. Des.

Setup -> Net Classes and Clearances

Setup -> Net Properties

The DxDesigner/Expedition PCB interface will support limited electrical net property passing.

This functionality will be implemented through the ePD 3.0 DxDesigner constraint interface,

which includes DxDesigner constraint entry, electrical net class creation, and forward and back

annotation of electrical net properties. These net properties will be passed through the

Expedition Net Properties file.

Table 5-4. Supported Electrical Net Properties

Constraint Description

Diff Pairs Pairing of two nets to be routed as a differential pair

Max Length/Delay Maximum length of a net, in time or distance

Matched Length Matches the length a group of nets within a specified tolerance

Max Crosstalk Maximum voltage caused by crosstalk, mV(Ignored if Parallelism

Rules assigned)

Parallelism Rules Maximum distance/length parallelsim rules for nets related to all

other nets.(Overrides Max Crosstalk)

Max Parallelism Maximum length a net may be routed parallel to another

Max Stub Length Maximum length of a trace branch on an ordered net

Max Vias Maximum number of vias allowed on a net

Supply voltage Voltage level of a signal net

The Max Crosstalk constraint will be written to the NetProps file. If there are parallelism rules

defined they will be written to the Parallelism Rules file (ParallelRules.txt). This file causes the

Crosstalk tab of the Net Properties dialog to be disabled and all rules are then taken from the

rules file. In the event that both Max Crosstalk and Parallelism Rules are assigned to a net, the

DxDesigner forward annotation process (pcbfwd) will report a warning.

If Back Annotation is required and you run Forward Annotation a message appears stating that

Back Annotation changes will be lost if you continue.

Multiple PCB Designs in DXDesigner Project

Additional checking is performed when a project is selected in the Project Integration dialog

because DXDesigner projects may contain multiple PCB designs.

Expedition PCB User’s Guide, EE2007.1 271

Product Integration

Netlist Types

By default, when a DXDesigner project is selected in the Project Integration dialog, it is

evaluated to determine if the project contains a properly named PCB design. By default, the

PCB design name in the project should match the name of the active PCB design.

If no matching PCB design name is in the project, a warning dialog appears and you can select

the PCB design name to be used in the active project.

Once the desired PCB design is selected and OK is selected, the associated project file is

accepted and the Project Integration dialog is again active.

If you select a DXDesigner project that does not contains a PCB design, you cannot use that

project. In this case, a warning dialog displays and are forced to return to the Project Integration

dialog and select a valid project name. Upon return to the Project Integration dialog the Project

file input field is blank (to clearly show you had a problem) and you must browse (or keyin) to a

valid project file.

Design Architect

This is created by Design Architect. This is the same database used when Design Architect and

Expedition PCB are integrated to the same project file. The following is how the project file

indicators behave when a Design Architect netlist is used as the schematic netlist:

Forward Annotation allowed - This indicator is always green except when there is updated

PCB data that needs to be Back Annotated to the schematic.

Schematic and Layout databases synchronized - This indicator will always be greyed out

(inactive).

272 Expedition PCB User’s Guide, EE2007.1

Product Integration

DXDesigner Flow

Back Annotation Allowed - This indicator is always green except when there is updated

schematic data that needs to be Forward Annotated to the PCB or the Disable commands that

create Back Annotation changes checkbox is selected.

The following are the commands that respect the Back Annotation Allowed project file

indicator:

Route -> Swap -> Pins

Route -> Swap -> Gates

ECO -> Renumber Ref. Des.

Setup -> Net Classes and Clearances

Setup -> Net Properties

If Back Annotation is required and you run Forward Annotation a message appears stating that

Back Annotation changes will be lost if you continue.

DXDesigner Flow

1. In Dashboard:

a. Set the project as the active project.

b. Invoke DxDesigner from Dashboard ->Toolboxes -> Board-level (PCB) Design

Folder.

2. In DxDesigner:

a. Open Design Roots in the ProjectNavigator Tree.

b. Select the source schematic.

c. Select Tools -> Create PCB Netlist from the pulldown menu.

d. On the Basic tab:

For Design Name - browse for source schematic.

For Netlist Format - choose Expedition.

For PCB Configuration File - browse for ../\ePD\3.0\standard\expedition.cfg.

For Process to Run - choose Create Netlist for Layout…

e. Select Run.

f. Correct any errors, verify any warnings and then save the schematic.

3. Adding Net Properties in DxDesigner for use in Expedition PCB:

Expedition PCB User’s Guide, EE2007.1 273

Product Integration

DXDesigner Flow

a. Select a net.

b. In the Attributes Editor, choose Expedition Constraints for Assignment.

c. Enter the required constraints.

d. Repeat steps c and d from the above Step 2.

4. In Library Manager:

a. Create a new Central Library.

b. Create entries for all the parts in the design:

Padstacks - physical pads for footprints.

Cells - physical footprints.

Parts - part name pin mapping.

5. PCB Job Creation Options

a. ViewPCB.

i. During Create Netlist For Layout process, select “Run command line after

processing” check box in the Processing Options section of the Basic tab.

ii. Select Run.

iii. Select the Create new PCB design option.

iv. Browse for Central Library.

v. Select a layout template.

vi. Enter the directory where you want the new Expedition pcb job to be created.

vii. Select OK.

viii. The new job will be created and Expedition will be invoked on the new job.

OR

b. Job Management Wizard:

i. Create a new PCB job.

ii. Enter a new project file, for example: Demo.prj.

iii. Select NO to schematic message.

iv. Select OK to Central Library message.

v. Browse for the Central Library.

vi. For Netlist, choose "DxDesigner".

274 Expedition PCB User’s Guide, EE2007.1

Product Integration

DXDesigner Flow

vii. Browse for the DxDesigner Project directory.

viii. Select a PCB Layout Template.

ix. Complete the job creation.

6. In Expedition PCB:

a. Open the new <project name>.pcb file.

b. Invoke Setup -> Project Integration.

c. If you have part and net properties information to import use Additional Options.

d. Run Forward Annotate, verify successful.

e. Invoke Place -> Place Parts and Cells and place all unplaced parts within the board

outline.

f. If necessary, run Route -> Swap -> Gates.

g. If desired, run ECO -> Renumber Ref Des.

h. Invoke Setup -> Project Integration.

i. Run Back Annotate, verify successful.

j. Save PCB design.

7. In DXDesigner

a. Select Tools->Create PCB Netlist from the pulldown menu.

b. On the Basic tab:

i. or Design Name - browse for source schematic.

ii. For Netlist Format - choose Expedition.

iii. For Process to Run - choose Back Annotate Information From Layout To

Schematic.

iv. Select Run.

v. Correct any errors and verify any warnings.

vi. The changes from PCB should now be present in the schematic.

To complete the round-trip between DxDesigner and Expedition PCB insuring that the

data is in-sync you must perform the following steps.

8. In DxDesigner:

a. Select Tools -> Create PCB Netlist from the pulldown menu.

b. On the Basic tab:

Expedition PCB User’s Guide, EE2007.1 275

Product Integration

Design Architect Flow

For Design Name - browse for the source schematic.

For Netlist Format - choose Expedition.

For Process to Run - choose Create Netlist for Layout...

c. Select Run. If the “Run command line after processing” option is set you can use the

DxDesigner To Expedition menu to launch Expedition if it is not already running.

d. Correct any errors and verify any warnings.

e. Save schematic.

9. In Expedition PCB:

a. Invoke Setup -> Project Integration.

b. Run Forward Annotate, verify successful.

c. Save the PCB design.

Design Architect Flow

In order to minimize the disruption of the existing DA/BA process flow, a copy of Package

(EN2002.2 or later) will be required. Set the following environment variable:

MGC_PKG_XINFO=1

This will enable PACKAGE to provide additional information that is needed by Expedition to

deal with heterogeneous components.

Steps to translate a DA schematic to Expedition PCB

1. In DA schematic:

a. Set the PCB Design Viewpoint.

b. Exit.

2. In Package:

a. Run Check Build, verify no errors.

b. Run Build, verify no errors.

c. Exit Package with a Save.

3. In Library Manager:

a. Create a new Central Library.

b. Create entries for all the parts in the design:

276 Expedition PCB User’s Guide, EE2007.1

Product Integration

Design Architect Flow

Padstacks - physical pads for footprints.

Cells - physical footprints.

Parts - part name pin mapping.

4. In Job Management Wizard:

a. Create a new PCB job.

b. Enter a new project file, for example; Demo.prj.

c. Select NO to schematic message.

d. Select OK to Central Library message.

e. Browse for the Central Library.

f. For Netlist choose "Design Architect".

g. Browse for the Design Architect Component directory.

h. Select a PCB Layout Template.

i. Complete the job creation.

5. In Expedition PCB:

a. Open the new <project name>.pcb file.

b. Invoke Setup -> Project Integration.

c. Run Forward Annotate, verify successful.

d. Invoke Place -> Place Parts and Cells.

e. Place all unplaced parts within the board outline.

f. If necessary run Route -> Swap -> Gates.

g. If desired run ECO -> Renumber Ref Des.

h. Invoke Setup -> Project Integration.

i. Run Back Annotate, verify successful.

j. Save PCB design.

6. In DVE:

a. Set the PCB Design Viewpoint.

b. Run Import ASCII BA, browse for /<jobname>/expbackanno.txt.

c. Verify changes from PCB are present in the schematic.

d. Exit DVE with a Save.

Expedition PCB User’s Guide, EE2007.1 277

Product Integration

Cross Probe Configuration

To complete the round-trip between Design Architect and Expedition PCB insuring that

the data is in-sync you must perform the following steps.

7. In Package:

a. Run Check Build, verify no errors.

b. Run Build, verify no errors.

c. Exit Package with a Save.

8. In Expedition PCB:

a. Invoke Setup -> Project Integration.

b. Run Forward Annotate, verify successful.

c. Save the PCB design.

Cross Probe Configuration

Cross Probe is the communication link between Expedition PCB and design entry tools and

CES. This allows selection of nets, parts, and pins within the schematic, board or simulator to be

communicated between products.

After you enable cross probing in the appropriate design systems, you can cross select design

objects. When cross probing from DxDesigner, for example, selecting a net in DxDesigner

causes Expedition PCB to highlight its view of the same net. When cross probing is enabled in

all design systems, selecting a design object in one tool cross probes to the other two design

tools. For example, selecting a design object in CES cross probes to both DxDesigner

Enabling Cross Probing Between Design Views

You can enable cross probing between DxDesigner, CES, and Expedition PCB to perform cross

selection of design objects in multiple design views. For example, after enabling cross probing

from DxDesigner to CES, clicking a design object in DxDesigner results in CES highlighting its

view of the same design object.

This design flow supports the following types of cross probing between tools:

DxDesigner to CES - Selecting a design object in DxDesigner results in CES

highlighting the corresponding object in its spreadsheet.

Expedition PCB to CES - Selecting a design object in Expedition PCB results in CES

highlighting the corresponding object in its spreadsheet.

CES to DxDesigner or Expedition PCB - Selecting a design object in CES results in a

selection in schematic entry or PCB layout, depending on the design view from which

you launched CES.

278 Expedition PCB User’s Guide, EE2007.1

Product Integration

Cross Probe Configuration

DxDesigner to Expedition PCB (uni and bi-directional) - Selecting a design object in

DxDesigner highlights the corresponding object in Expedition PCB. Choosing a design

object in Expedition PCB results in DxDesigner highlighting its view of the object. You

can turn off cross probing from one design view (e.g. DxDesigner to Expedition PCB) to

provide just uni-directional cross probing from the other design view.

One to all - Selecting a design object in DxDesigner, CES, or Expedition PCB

highlights the corresponding object in all other design systems.

DXDesigner (Cross Probe)

You can select a top level DxDesigner schematic and launch DxDesigner from the dialog. If the

root schematic is set in the project file then this value is pre-loaded and you can launch or

connect to an already running instance of DxDesigner passing it the selected root schematic. If

the root schematic is not defined in the dialog, DxDesigner opens with the project directory

specified as the input source.

The Connect Button launches or connects to an already running instance of DxDesigner

passing it the selected root schematic. This button is not enabled if a schematic has not been

chosen.

Using Cross Probing

1. In DxDesigner, enable the Cross Probe window by going to View -> Other Windows

and selecting Cross Prober.

2. In the Cross Prober window select the “Enable cross probing for design” check box.

3. From the “Layout system” drop down list select Expedition

4. In the “Layout document” field enter the path to the Expedition .pcb file or use the

browse button “…” to locate the file.

5. If Expedition is not currently running, the button at the end of the “Layout system” field

will show Launch. If Expedition is running then it will say Connect. Select the button

in either case. If Expedition is not running this should start the program. If Expedition is

running this should connect to that instance of Expedition.

Note

If an Expedition job other than the existing project is already open, the “Layout

document” path will update to point to it. You will need to exit Expedition and reset the

“Layout document” path.

6. To see the best results set the two Select boxes at the bottom of the Cross Probe window

to “Zoom to Selected”.

Expedition PCB User’s Guide, EE2007.1 279

Product Integration

Xplore (Cross Probe)

Note

In Expedition there is a Setup -> Cross Probe -> DxDesigner menu item. This will display

a dialog that can be used to launch DxDesigner. DxDesigner will only launch if the

schematic in this menu matches the data for the currently active project selected in

Dashboard.

Using Setup -> Cross Probe -> DxDesigner only starts DxDesigner. You will still need to

follow the steps listed under Using Cross Probing to initiate cross probing between

Expedition and DxDesigner.

Xplore (Cross Probe)

The Xplore Tool Module dialog lists all the registered Xplore tool modules. You can use the

dialog to select the schematic tool to which you want to cross probe.

Invoking from Expedition

1. Invoke Setup -> Cross Probe -> XPlore.

2. Select the appropriate schematic module from the list of tool modules, then select the

Connect button.

3. On the Connect Tool Module dialog make sure the Schematic design is correct, select

OK. If the schematic module is not open, select the Launch tool checkbox and then

select OK.

4. Select a component, net or pin in graphics and the corresponding item should select and

fit view in the schematic tool.

5. Select a instance, net or pin in the schematic tool and the corresponding item should

select and fit view in graphics..

6. To discontinue cross probing, on the XPlore Server dialog, select Disconnect for PCB

Design File.

7. Choose whether to close the PCB application.

8. Select the schematic module from the list of tool modules, then select Disconnect.

Connect Tool Module

The Connect Tool Module dialog is used to gather information needed for cross probing. When

opened, the Tool module selected in the Xplore dialog displays.

1. Select the path to the schematic tool directory if not already displayed.

280 Expedition PCB User’s Guide, EE2007.1

Product Integration

Xplore (Cross Probe)

2. Select the Launch Tool check box if you want the schematic tool to be launched on the

selected schematic design directory. If this option is chosen, you are prompted to select a

design viewpoint by using a browse dialog.

3. Select OK.

Invoking from Design Architect

1. Open the viewpoint of the design you want to use for cross probing.

2. Enter into session scope by selecting the SESSION button.

3. Select Setup -> Cross Probe -> Setup Crossprobe. Browse to the Mentor product

directory and locate the Xplore.exe program. To keep from having to enter this path

more than once create a $HOME/mgc/userware/xprobe_da directory. The path to the

XPlore program will be saved in a file called da_session.startup. See Design Architect

Commands below for additional information.

4.

5. Select Setup -> Cross Probe -> Invoke XploreServer.

6. On the XPlore Cross Probe Server dialog, browse to the .pcb file.

7. Choose Expedition PCB from the drop down list.

8. Select the Connect button or select the Connect to running instance if possible

checkbox, then Connect.

9. Select a instance, net or pin in DA and the corresponding item should select and fit view

in graphics.

10. Select a component, net or pin in graphics and the corresponding item should select and

fit view in DA.

11. To discontinue Cross Probing, on the XPlore Server dialog, select Disconnect for PCB

Design File, choose whether or not to close Expedition PCB. Next, select Design

Architect from the list of tool modules, then select Disconnect.

Design Architect Commands

Enable Crossprobe

Used to open the communication pipe. Use this command when Expedition is already up

and has Design Architect cross probing turned on. If you need to launch Expedition

from Design Architect use the Invoke XploreServer command.

Disable Crossprobe

Used to close the communication pipe.

Expedition PCB User’s Guide, EE2007.1 281

Product Integration

Variant Manager

Setup Crossprobe

Used to define the location of the Xplore server. This program is used to communicate

with Expedition.

Invoke XploreServer

Used to launch the Xplore server. The Xplore server handles the communication

between Design Architect and Expedition. The server can also be used to launch

Expedition. If Expedition is already up and cross probing has been enabled you should

use the Enable Crossprobe command to initiate cross probing.

Unselect All

Used to unselect all selected items in Design Architect.

Xplore Cross Probe Server

When you are finished cross probing, you need to disconnect all tool modules and

Expedition PCB before the Exit button will be enabled.

Variant Manager

A variant of a PCB board is a subset of a Master PCB that uses the same bare board as the

master PCB board. The variation consists of removing components and/or replacing

components with other components that fit in the same space as the original component. Variant

Manager can communicate with our other tools by using cross probe highlighting and this

communication can be bi-directional.

The Variant database is based on a database scheme. As new features are added to the Variant

Manager, this scheme may change in order to accommodate the new functionality. The Variant

Manager allows you to upgrade a database from an older database scheme to the current

database scheme.

The library information for the Expedition tools is maintained in a Central Library. This library

contains all information on parts, cell, symbols, etc. Variant manager needs the information

contained in the parts database partitions to determine which parts are available when replacing

components. To optimize the search speed for parts and to be able to create Report Writer

databases, Variant Manager stores the parts database information in a different structure inside

the Central Library. An automated tool to execute this task is supplied with Variant Manager. It

is called the Variant Manager Central Library Data creator.

OBDG Interface

The OBDG interface is used to provide a link to the ODBG family of tools. This is

accomplished by generating an ODB++ Gateway (ODBG) file. The created output filename is

<pcbname>.odb and it is placed in the ../output directory.

282 Expedition PCB User’s Guide, EE2007.1

Product Integration

OBDG Interface

ODBG to ODB++ Conversions

From the Installation or SupportNet you can download a translator that converts the ODBG

output into the ODB++ format. This is sometimes needed if the vendor you provide data to can

only accept the ODB++ version of the data.

If this program is installed on the same machine as the software, the ODBG dialog displays two

new options. The output from both options will be in the ../output directory.

Launch ODB++ Launches the GW2ODB program which converts the

Convertor ODBG output into the ODB++ format. The output from the

GW2ODB program is a directory structure that is named

<job name>_dir.odb.

Compress Output Only available if the Launch ODB++ Convertor option is

selected. This option causes the output of the GW2ODB

program to be a single compressed file instead of the

directory structure and the output is a single file named <job

name>.tgz.

To run ODBG to ODB++ on UNIX

After selecting the ODBGateway to ODB++ product during installs, a variable needs to be set to

run the interface on a UNIX machine.

The variable should be defined as below:

Solaris setenv GW2ODB_DIR $SDD_HOME/odbpp/sunos5/

HP setenv GW2ODB_DIR $SDD_HOME/odbpp/ux11/

Linux Not Available

For the Valor Gateway converter to run in standalone mode (on command prompt) an additional

variable IPLHOME needs to be set and point to the ODBG converter installation directory; by

default; $SDD_HOME/odbpp/iplhome.

To Define ODBG Output

1. Select the output options; Part numbers, Assembly layers, Generated Silkscreen layer

and Drill Drawing layer.

2. Select a Package Outline Layer from the drop-down field.

3. Check the User Layers option and then select the appropriate user layer and assign the

appropriate mapping layer(s).

4. To select a mapping layer, click on the layer and a drop-down appears allowing you to

select one or multiple mapping layers to the user-layer.

Expedition PCB User’s Guide, EE2007.1 283

Product Integration

OBD++

Requirement: If a User Layer is selected, one or more mapping layers must be

assigned. If a mapping layer is not defined, a warning message displays. If the layer is

mapped to DOCUMENT then a documentation layer with the same name as the user

layer is created in the output file.

When the OK button is selected, an ODBGInterface.txt file is created in the ../logfiles

job directory containing information based on the options that were selected in the

dialog. This file can be viewed using File Viewer.

OBD++

The OBD++ interface allows you to generate the data directly in ODB++ format, removing the

necessity of the Valour converter unlike the Output > OBD++ Interface which outputs the data

in ODB format (as defined by Valor) and then uses the Valor Converter to convert the data to

ODB++. The created output filename is <pcbname>.ocf and it is placed in the ../config

directory.

ODB++ is an ASCII open format, which captures all CAD/EDA database, assembly and PCB

fabrication knowledge in one single, unified database. This structure allows you to attach

attributes to individual features and save them within the database as the need arises, further

expanding the applicability of ODB++ to suit any purpose.

The ODB++ format represents the complete layout design for interfacing with Valor assembly

and manufacturing tools and other third party applications that accept ODB++.

ODB++ describes a board as steps (panels, boards, and coupons) composed of layers. These

layers consist of positive or negative features with several entities linking features to

components and nets. Data can be easily changed, whether on a localized basis or across the

board. There is no longer any need to deal with complicated definitions: shaves and teardrops

are made of negative and positive lines and cross-hatched areas are drawn as they appear. In

addition, electrical entities are included in the data so the netlist is accurate, apertures and full

electrical attributes are identified and route profiles created.

You can select to Compress the output ODB++ job which is made up of several files describing

the output. If selected, the compression creates a single tar’d and zipped file. The default is

unselected (not compressed).

For all platforms (Windows and Linux), packaging format is gtar followed by gzip utilities. On

Windows these utilities are shipped with the installation CDs and on Linux they are packaged

with the operating system.

If the ODB++ output fails, extraction failure, unable to find gtar/gzip executables, file access

issues or the process generation is cancelled, a dialog is displayed informing you to view the log

file for details.

284 Expedition PCB User’s Guide, EE2007.1

Product Integration

OBD++

To Define the Output Options

1. Select an existing ODB++ Setup file or create a new definition. By default, these files

are created within your jobs ../config sub-directory with the extension ".ocf".

2. To select an existing file, select the browse button then browse to a directory that

contains this file.

3. To create a new file, select the browse button and keyin the new ODB++ setup filename

in the displayed dialog. The filename cannot contain the following characters, \

(backslash), ! (bang), : (colon), * (asterisk), > (less than), ? (question mark) or ( )

(parenthesis).

4. Select or browse for the output path. By default this path is the job's ../output directory.

5. Select the ODB++ output job name. By default, this is the name of the job with "odb"

appended. You may overwrite this default by keying in a new name.

6. Select or browse for the log file path. By default this is the job's ../LogFiles directory. A

new log file (odblog_xxx.txt) is created for each translation where xxx is incremented in

by 1 for each translation.

7. Select the Append check box to add the log messages to the latest defined log file.

To Define the Basic Export Options

1. Select the Export Mode: Full, Fab or Assy.

Full (Default) All ODB++ job data is represented.

Fab Only fabrication data is represented.

Assy Only assembly data is represented.

The following elements are output to ODB++"

Comp/Pkg + logical nets Outputs ODB++ components, packages and

logical nets which represent a logical connection

between component pins.

Outer layer copper pads Outputs all outer signal layers with data

regarding pads only (not traces or surfaces).

Mask/Paste/Screen Layers Outputs all data on soldermask, solderpaste and

silkscreen layers.

Drill/Route layers Drill and Route layers are output.

Doc layers Documentation layers are output.

Physical Nets Outputs netlist data which is used in the netlist

analyzer of Trilogy / Enterprise.

Expedition PCB User’s Guide, EE2007.1 285

Product Integration

OBD++

Outer copper layers non- Outputs the data on the outer copper layers; pads,

pads vias, traces, surfaces, etc.

Inner layers Outputs the inner layers.

Raw data files All files that are not essential to the design are

located in the ODB++ format under: checklists,

user, input, forms, flows, etc.

2. Select the Remove EDA data check box if you do not want to export nets, components

and packages information to the ODB++ job. Uncheck to export EDA elements. Default

is unselected.

3. Select the Neutralize nets check box to assign random names to nets. Default is

unselected.

4. Select the Generated Silkscreen data option to allow silkscreen data using the Silkscreen

Generator to be exported to the ODB++ job. If this option is not selected, regular

silkscreen data is exported.

5. Select the Part Numbers option to allow the part numbers to be exported to the ODB++

job.

To Define the Additional Parameters

1. Select the Read DRC features check box to export DRC data (DRC Window, Insertion

Outline, Placement Obstruct, Plane Obstruct, Route Obstruct (Trace, via and both),

Testpoint Obstruct, Route Border) into the ODB++ job. When this is checked, a DRC

button displays. Clicking the DRC button allows you to select the DRC feature and its

ODB++ DRC Layer name. The default is unchecked.

2. Select the Round Corners check box to create round corner surfaces, according to fill

brush or the traces file description. The default is unchecked.

3. Select the Read net0 information check box to allow you to enable read in net0

information.

4. Select the Read in unplated check box to builds padstacks for unplated holes. The

default is checked.

5. Select the Ignore component layout check box to disregard the

Component_Layout_Type property that affects the .comp_mount_type attribute of a

ODB++ component. The default is unchecked.

To Define the Pins, Pads, Via and Package Options

The non-functional pad removal options enable padstack optimization of unused pins and pins

with no net.

286 Expedition PCB User’s Guide, EE2007.1

Product Integration

OBD++

1. Select a Pins option from the pulldown.

None (Default) There is no removal of non-functional pads.

Unused Pins Removes isolated pads not connected to any

other copper pad, trace or surface.

Pins with No Net Removes pads in net $NONE.

The following rules are applied:

a. Pads are removed on signal layers only.

b. Pads are not removed for external signal layers of the padstack span.

c. SMD pins are not processed.

d. Only isolated pads (not connected to any other copper pad, trace or surface) are

removed.

e. Each modified padstack is assigned with the attribute .pf_optimized on the pad in the

matching drill layer. This enables the identification of layers where padstack

optimization, the removal of pads, has taken place.

f. In case Pins with No Net option is selected, rules b and d are ignored.

2. Select a Vias option from the pulldown. This enables padstack optimization of unused

vias. The rules are the same as described above. Rule f is not applicable.

None (Default) There is no removal of non-functional pads.

Unused Vias Removes isolated pads not connected to any

other copper pad, trace or surface.

3. Select the appropriate package outline layer. The options are:

Placement Outline

Assembly Outline

Insertion Outline

Silkscreen Outline

Default User Layer

Any User Layers

Cell Graphics

Edge Copper

Plating Layer

Dimension Layer

Expedition PCB User’s Guide, EE2007.1 287

Product Integration

OBD++

Panel Layer (Only displays in FabLink XE in a Panel design)