Professional Documents

Culture Documents

Data Sheet

Uploaded by

zakie wahyuCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Data Sheet

Uploaded by

zakie wahyuCopyright:

Available Formats

uP8801S

3A Ultra Low Dropout Linear Regulator

General Description Features

The uP8801S is a 3A ultra low dropout linear regulator Works with 1.2V~5.5V VIN

specifically designed for motherboard, notebook and graphic Adjustable Output Voltage, Down to 0.8V

card applications. This device works with dual supplies, a

1.5% Initial Accuracy

control input for the control circuitry and a power input as

low as 1.2V for providing current to output. The uP8801S Excellent Line and Load Regulation

delivers high-current and ultra-low-drop output voltage as 3A Guaranteed Output Current

low as 0.8V for applications where VOUT is very close to 300mV @ 3A Dropout Voltage

VIN.

Very Low On-Resistance

The uP8801S features comprehensive control and 100mΩ Ω typical

protection functions: a power on reset (POR) circuit for

VOUT Pull Low Resistance when Disabled

monitoring both control and power inputs for proper

operation; an EN input for enabling or disabling the device, VOUT Power OK Signal

a power OK with time delay for indicating the output voltage Fast Transient Response

status, a foldback current limit function, and a thermal Low External Component Count

shutdown function.

Low Cost and Easy to Use

The uP8801S is available in PSOP - 8L or WDFN3x3 - 10L

Over Current and Over Temperature Protection

packages with very low thermal resistance.

RoHS Compliant and Halogen Free

Applications

Ordering Information

Desktop PCs, Notebooks, and Workstations

Graphic Cards Order Number Package Top Marking

Low Voltage Logic Supplies uP8801SSW8 PSOP-8L uP8801S

Microprocessor and Chipset Supplies

uP8801SDDA WDFN3x3-10L uP8801S

Split Plane Microprocessor Supplies

Advanced Graphics Cards Supplies Note:

SoundCards and Auxiliary Power Supplies (1) Please check the sample/production availability with

uPI representatives.

SMPS Post Regulators (2) uPI products are compatible with the current IPC/JEDEC

J-STD-020 requirement. They are halogen-free, RoHS

compliant and 100% matte tin (Sn) plating that are suitable

for use in SnPb or Pb-free soldering processes.

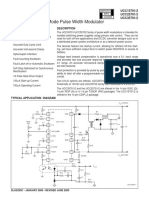

Pin Configuration & Typical Application Circuit

5VCC

POK 1 8 GND

R4 CNTL

EN 2 7 FB 10R 4

GND EN POK

VIN 3 6 VOUT 2 1

CNTL 4 5 NC R3

10K VOUT

VIN VIN VOUT

PSOP-8L 3 6

C1 R2 C4

1uF 12.5K option

VOUT 1 10 CNTL FB

NC 5 7

VOUT 2 9 VIN R1 C3

C2 100uF

22uF

9 10K

VOUT 3 GND 8 VIN

GND

FB 4 7 VIN

POK 5 6 EN

WDFN3x3-10L

uP8801S-DS-F0000, Dec. 2014 1

www.upi-semi.com

uP8801S

Functional Pin Description

Pin No.

Name Pin Function

SSW8 SDDA

Pow er OK Indication. This pin is an open-drain output and is set high impedance once

1 5 POK

VOUT reaches 92% of its rating voltage.

Enable Input. Pulling this pin below 0.4V turns the regulator off, reducing the quiescent

2 6 EN current to a fraction of its operating value. If this pin is left floating, the regulator will enter

shutdown mode.

Input Voltage. This is the drain input to the power device that supplies current to the

output pin. Large bulk capacitors with low ESR should be placed physically close to this

3 7, 8, 9 VIN pin o prevent the input rail from dropping during large load transient. A 4.7uF ceramic

capacitor is recommended at this pin. VIN cannot be forced higher than VCNTL otherwise

the current limit function may be false triggered and disable the output voltage.

Supply Input for Control Circuit. This pin provides bias voltage to the control circuitry

and driver for the pass transistor.The driving capability of output current is proportioned

4 10 CNTL to the VCNTL. For the device to regulate, the voltage on this pin must be at least 1.5V

greater than the output voltage, and no less than VCNTL_MIN. VCNTL input voltage must be

ready before VN I input voltage.

5 -- NC Not Internally Connected.

Output Voltage. This pin is power output of the device. A pull low resistance exists

when the device is disabled by pulling low the EN pin. To maintain adequate transient

6 1, 2, 3 VOUT response to large load change, typical value of 1000uF Al electrolytic capacitor with

10uF ceramic capacitors are recommended to reduce the effects of current transients

on VOUT.

Feedback Voltage. This pin is the inverting input to the error amplifier. A resistor divider

7 4 FB from the output to GND is used to set the regulation voltage as VOUT = 0.8x(R1+R2)/R1

(V)

8 -- GND Ground.

Ground. The exposed pad acts the dominant power dissipation path and should be

Exposed Pad soldered to well desi gned PC B pads as descri bed i n the Appl i cati on Inform ati ons

Chapter.

2 uP8801S-DS-F0000, Dec. 2014

www.upi-semi.com

uP8801S

Functional Block Diagram

EN CNTL VIN

Power On

Thermal Limit

Reset

Softstart &

Current Limit

Control Logic

FB

0.8V

VOUT

Delay

90% VREF

POK GND

uP8801S-DS-F0000, Dec. 2014 3

www.upi-semi.com

uP8801S

Functional Description

Definitions Output Voltage Programming

Some important terminologies for LDO are specified below. Figure 1 shows a typical application of 2.5V to 1.8V

conversion with a 5.0V control supply. The output voltage

Dropout Voltage

is sensed through a voltage divider and regulated to internal

The input/output voltage differential at which the regulator reference voltage VREF. The output voltage is programmed

output no longer maintains regulation against further as:

reductions in input voltage. Measured when the output drops

VOUT = VREF x (R1+R2) / R1 = 0.8V x (22.5k/10k) = 1.8V

2% below its nominal value. Dropout voltage is affected by

junction temperature, load current and minimum input It’s recommended to maintain 50-100uA through the output

supply requirements. divider network for a tight load and line regulation. The

internal voltage reference is VREF = 0.8V with 1.5% initial

Line Regulation

accuracy. This commands the use of 0.5% or better

The change in output voltage for a change in input voltage. accuracy resistors to build a precision power supply.

The measurement is made under conditions of low

5VCC

dissipation or by using pulse techniques such that average

R4

chip temperature is not significantly affected. 10R

CNTL

4

EN POK

Load Regulation 2 1

The change in output voltage for a change in load current R3

10K

VIN VIN VOUT VOUT

at constant chip temperature. The measurement is made 3 6

under conditions of low dissipation or by using pulse R2 C4

C1

12.5K option

techniques such that average chip temperature is not 1uF FB

NC 5 7

significantly affected. C2 R1 C3

9 10K 100uF

22uF

Maximum Power Dissipation GND

The maximum total device dissipation for the regulator will

operate within specifications.

Figure 1. Typical application of 2.5V to 1.8V conversion

Quiescent Bias Current with a 5.0V control supply

Current which is used to operate the regulator chip is not Over Current and Short Circuit Protection

delivered to the load.

The uP8801S features a foldback over current protection

The quiescent current IQ is defined as the supply current function as shown in Figure 2. The current limit threshold

used by the regulator itself that does not pass into the level is proportional to VOUT/VNOM and is typically 4A when

load. It typically includes all bias currents required by the VOUT = VNOM, where VNOM is the target output voltage. If the

LDO and any drive current for the pass transistor. output continuously demands more current than the

Initialization maximum current, output voltage will eventually drops below

its nominal value. This, in turns, will lower its OCP threshold

The uP8801S automatically initiates upon the receipt of level. This will limit power dissipation in the device when

supply voltage and power voltage. A power on reset circuit

over current limit happens.

continuously monitors VIN and CNTL pins voltages with

rising threshold levels of 0.6V and 2.7V respectively. When output short circuit occurs, the uP8801S will try to

rebuild the output voltage with maximum allowable current

Chip Enable and Soft Start as shown if Figure 3. The duty cycle is about 10% and the

The uP8801S features an enable pin for enable/disable averaged short circuit current is about 400mA.

control of the chip. Pulling VEN lower than 0.4V disables

the chip and reduces its quiescent current down to 20uA.

When disabled, an internal MOSFET of 50Ω RDS(ON) turns

on to pull output voltage to ground. Pulling VEN higher than

1.4V enables the output voltage, providing POR is

recognized. The uP8801S features soft start function that

limits inrush current for charging the output capacitors. The

soft start time is typically 1ms.

4 uP8801S-DS-F0000, Dec. 2014

www.upi-semi.com

uP8801S

Functional Description

VIN (1V/Div)

Output Voltage (V)

2.0V

1.5V

VOUT (20mV/Div)

1.0V

0.5V

0V IIN (2A/Div)

0A 1A 2A 3A 4A 5A

Output Current (A)

Time : 2ms/Div

Figure 2. Current Limit Behavior Figure 3. Output Short Circuit Protection

uP8801S-DS-F0000, Dec. 2014 5

www.upi-semi.com

uP8801S

Absolute Maximum Rating

(Note 1)

Control Input Voltage VCNTL ------------------------------------------------------------------------------------------------------------- -0.3V to +7V

Power Input Voltage VIN ------------------------------------------------------------------------------------------------------------------ -0.3V to +7V

Other Pins ----------------------------------------------------------------------------------------------------------------------- -0.3V to (VCNTL + 0.3V)

Storage Temperature Range ----------------------------------------------------------------------------------------------------------- -65OC to +150OC

Junction Temperature ------------------------------------------------------------------------------------------------------------------------------------ 150OC

Lead Temperature (Soldering, 10 sec) ------------------------------------------------------------------------------------------------------------ 260OC

ESD Rating (Note 2)

HBM (Human Body Mode) --------------------------------------------------------------------------------------------------------------------- 2kV

MM (Machine Mode) ----------------------------------------------------------------------------------------------------------------------------- 200V

Thermal Information

Package Thermal Resistance (Note 3/4)

PSOP - 8L θJA ---------------------------------------------------------------------------------------------------------------------------- 47OC/W

PSOP - 8L θJC ------------------------------------------------------------------------------------------------------------------------- 17.9OC/W

WDFN3x3 - 10L θJA --------------------------------------------------------------------------------------------------------------------- 68OC/W

WDFN3x3 - 10L θJC ---------------------------------------------------------------------------------------------------------------------- 6OC/W

Power Dissipation, PD @ TA = 25OC

PSOP - 8L ------------------------------------------------------------------------------------------------------------------------------------------- 2.13W

WDFN3x3 - 10L ----------------------------------------------------------------------------------------------------------------------------------- 1.47W

Recommended Operation Conditions

(Note 5)

Operating Junction Temperature Range ------------------------------------------------------------------------ -40OC to +125OC

Operating Ambient Temperature Range -------------------------------------------------------------------------------------- -40OC to +85OC

Supply Input Voltage, VCNTL ------------------------------------------------------------------------------------------------------------ +3.0V to +5.5V

Power Input Voltage, VIN ------------------------------------------------------------------------------------------------------------ +1.0V to VCNTL

Electrical Characteristics

(VCNTL = 5V, TA = 25OC, unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Units

Supply Input Voltage

Control Input Voltage VCNTL VOUT = VREF 2.9 -- 6 V

POR Threshold VCNTLRTH 2.5 2.7 2.9 V

POR Hysteresis VCNTLHYS 0.1 0.2 -- V

Power Input Voltage VIN VOUT = VREF 1.0 -- VCNTL V

Control Input Current in

ICNTL_SD VCNTL = VIN = 5.0V, IOUT = 0A, VEN = 0V -- 20 30 uA

Shutdown

Control Input Current ICNTL VCNTL = VIN = VEN = 5.0V, IOUT = 0A, VOUT = VREF -- 0.3 0.6 mA

Quiescent Current IQ VCNTL = VIN = VEN = 5.0V, IOUT = 0A, VOUT = VREF -- 0.3 0.6 mA

Feedback Voltage

Reference Voltage VREF VCNTL = VIN = VEN = 5.0V, IOUT = 0A, VOUT = VREF 0.788 0.8 0.812 V

Feedback Input Current IFB -- 20 -- nA

1.2V < VIN < 5.0V, VCNTL = VEN = 5.0V, IOUT = 0A,

VIN Line Regulation VREF(LINE) -- 0.01 0.1 %/V

VOUT = VREF

VCNTL Line Regulation VREF(CNTL) 3.0V < VCNTL < 5.0V,VIN = 1.2V, IOUT = 0A, VOUT = VREF -- 0.01 0.1 %/V

6 uP8801S-DS-F0000, Dec. 2014

www.upi-semi.com

uP8801S

Electrical Characteristics

Parameter Symbol Test Conditions Min Typ Max Units

Feedback Voltage

0mA < IOUT < 3.0A, VCNTL = VEN = 5.0V,

Load Regulation (Note6) VREF(LOAD) -- 0.8 1.5 %/A

VIN = VOUT+0.5V

On Resistance RDS(ON) IOUT = 100mA, VCNTL = VEN = 5.0V, VOUT = 1.6V -- 100 160 mΩ

IOUT = 3A, VCNTL = VEN = 5.0V,

Dropout Voltage (Note7) VDROP -- 300 500 mV

VIN = VOUT,NOMINAL-100mV

VOUT Pull Low Resistance VCNTL = VIN = 5.0V, VEN = 0V, -- 50 -- Ω

Enable

Enable High Level V EN 1.4 -- -- V

Disable Low Level V SD -- -- 0.4 V

EN Input Impedance ZEN -- 500 -- kΩ

Output Voltage Ramp Up

-- 1 -- ms

Time

PWROK

FB Power OK Threshold VPOKTH IOUT = 0A, VCNTL = VIN = VEN = 5.0V, VOUT = VREF -- 92 -- %

Power OK Hysteresis VPOKHYS IOUT = 0A, VCNTL = VIN = VEN = 5.0V, VOUT = VREF -- 8 -- %

POK Delay Time From VOUT > 92% VNOM to POK rising -- 1 -- ms

Over Current Protection

OCP Threshold Level

IOCP VCNTL = VIN = VEN = 5.0V, VOUT = VREF 3.6 4 6 A

(Note8)

Averaged Output Short

ISC VCNTL = VIN = VEN = 5.0V, VOUT = 0V 100 440 -- mA

Circuit Current

Thermal Protection

Thermal Shutdown O

TSD IOUT = 0A, VCNTL = VIN = VEN = 5.0V, VOUT = VREF -- 170 -- C

Temperature

Thermal Shutdown O

TSDHYS IOUT = 0A, VCNTL = VIN = VEN = 5.0V, VOUT = VREF -- 30 -- C

Hysteresis

Note 1. Stresses listed as the above Absolute Maximum Ratings may cause permanent damage to the device.

These are for stress ratings. Functional operation of the device at these or any other conditions beyond those

indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum

rating conditions for extended periods may remain possibility to affect device reliability.

Note 2. Devices are ESD sensitive. Handling precaution recommended.

Note 3. θJA is measured in the natural convection at TA = 25OC on a low effective thermal conductivity test board of

JEDEC 51-5 thermal measurement standard.

Note 4. The case temp location for measuring θJC is on the top of the package.

Note 5. The device is not guaranteed to function outside its operating conditions.

Note 6. This test item is tested under constant junction temperature which does not exceed absolute maximum

ratings. In this test, a 5ms current pulse is applied at the output for measuring required data without

exceeding junction temperature AMR.

Note 7. This test item is tested under constant junction temperature which does not exceed absolute maximum

ratings. In this test, the dropout voltage is measured as VIN-VOUT where VIN equals VOUT,NOMINAL-100mV, and

VOUT decreases lower than VOUT,NOMINAL due to IR drop.

Note 8. OCP threshold level is not guaranteed to function outside its linear region.

uP8801S-DS-F0000, Dec. 2014 7

www.upi-semi.com

uP8801S

Typical Operation Characteristics

Power On from VCNTL Power On from VIN

VCNTL (2V/Div)

VIN

(2V/Div)

VOUT (1V/Div) POK (2V/Div) VOUT (1V/Div)

POK (2V/Div)

IIN (2A/Div)

IIN (2A/Div)

Time : 1ms/Div Time : 400us/Div

VCNTL = 5V, VIN = 3.3V, COUT = 470uF, No Load VCNTL = 5V, VIN = 3.3V, COUT = 470uF, No Load

Power Off from VCNTL Power Off from VIN

VCNTL (2V/Div)

VIN (2V/Div)

POK (2V/Div)

VOUT (1V/Div) VOUT (1V/Div)

POK (2V/Div)

IIN (1A/Div) IIN (1A/Div)

Time : 20ms/Div Time : 10ms/Div

VCNTL = 5V, VIN = 3.3V, COUT = 470uF, RL = 11Ω VCNTL = 5V, VIN = 3.3V, COUT = 470uF, RL = 11Ω

Turn On Waveform Turn Off Waveforms

EN (2V/Div) EN (2V/Div)

POK (2V/Div) POK

VOUT (1V/Div) (2V/Div) VOUT (1V/Div)

IIN (2A/Div) IIN (1A/Div)

Time : 400us/Div Time : 4ms/Div

VCNTL = 5V, VIN = 3.3V, COUT = 470uF, No Load VCNTL = 5V, VIN = 3.3V, COUT = 470uF, RL = 11Ω

8 uP8801S-DS-F0000, Dec. 2014

www.upi-semi.com

uP8801S

Typical Operation Characteristics

Load Transient Response Dropout Voltage vs. Output Current

300mV

VOUT (50mV/Div)

Dropout Voltage (mV)

250mV

200mV

150mV

IOUT (1A/Div) 100mV

50mV

0mV

0A 0.5A 1.0A 1.5A 2.0A 2.5A 3.0A

Time : 2us/Div Output Current (A)

VCNTL = 5V, VIN = 3.3V, COUT = 4.7uF, IOUT = 0A to 1.6A

Quiescent Current vs. Input Voltage Enable/Disable Threshold vs. Input Voltage

500 0.90

450

Enable/Disable Threshold (V)

0.85

400

Quiescent Current (uA)

0.80

350

Enable

300 0.75

250 0.70 Disable

200 0.65

150

0.60

100

50 0.55

0 0.50

2.5 3.0 3.5 4.0 4.5 5.0 5.5 2.5 3.0 3.5 4.0 4.5 5.0 5.5

VIN = VCNTL (V) VIN = VCNTL (V)

VOUT = VREF VOUT = VREF

Output Voltage Line Regulation Output Voltage Load Regulation

1.00 1.0

0.80 0.8

Output Voltage Variation (%)

Output voltage Variation (%)

0.60 0.6

0.40 0.4

0.20 0.2

0.00 0.0

-0.20 -0.2

-0.40 -0.4

-0.60 -0.6

-0.80 -0.8

-1.00 -1.0

2.5 3.0 3.5 4.0 4.5 5.0 5.5 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

VIN = VCNTL (V) Output Current (A)

VOUT = VREF VCNTL = 5V, VOUT = 0.8V

uP8801S-DS-F0000, Dec. 2014 9

www.upi-semi.com

uP8801S

Typical Operation Characteristics

On Resistance vs. Temperature Output Voltage vs. Temperature

160 1.00

150

Output Voltage Variation (%)

0.50

140

On Resistance (mΩ)

130 0.00

120

-0.50

110

100 -1.00

90

-1.50

80

70 -2.00

-40 -20 0 20 40 60 80 100 120 140 160 -40 -20 0 20 40 60 80 100 120 140 160

Temperature (OC) Temperature (OC)

VOUT = 1.8V

10 uP8801S-DS-F0000, Dec. 2014

www.upi-semi.com

uP8801S

Application Information

The uP8801S is a high performance linear regulator This allows for the device being some distance from any

specifically designed to deliver up to 3A output current with bulk capacitance on the rail. Additionally, bulk capacitance

very low input voltage and ultra low dropout voltage. With may be added closely to the input supply pin of the

dual-supply configuration, the uP8801S operates with a uP8801S to ensure that VIN does not sag, improving load

wide input voltage VIN range from 1.2V to 5.5V and is ideal transient response.

for applications where VOUT is very close to VIN . Output capacitor: A minimum bulk capacitance of 10uF,

Supply Voltage for Control Circuit VCNTL along with a 0.1uF ceramic decoupling capacitor is

Unlike other linear regulators that use a P-Channel recommended. Increasing the bulk capacitance will improve

MOSFET as the pass transistor, the uP8801S uses an N- the overall transient response. The use of multiple lower

Channel as the pass transistor. N-Channel MOSFET value ceramic capacitors in parallel to achieve the desired

provides lower on-resistance and better stability meeting bulk capacitance will not cause stability issues. Although

stringent requirements of current generation designed for use with ceramic output capacitors, the

microprocessors and other sensitive electronic devices. uP8801S is extremely tolerant of output capacitor ESR

The drain of N-Channel MOSFET is connected to VIN and values and thus will also work comfortably with tantalum

the source is connected to VOUT. This requires that the output capacitors.

supply voltage VCNTL for control circuit is at least 1.5V higher Thermal Consideration

than the output voltage to provide enough overdrive capability The uP8801S integrates internal thermal limiting function

for the pass transistor thus to achieve low dropout and fast to protect the device from damage during fault conditions.

transient response. It is highly recommended to bias the However, continuously keeping the junction near the thermal

device with 5V voltage source if available. shutdown temperature may remain possibility to affect

Use a minimum 1uF ceramic capacitor plus a 10Ω resistor device reliability. It is highly recommended to keep the

to locally bypass the control voltage. junction temperature below the recommended operation

Input/Output Capacitor Selection condition 125OC for maximum reliability.

The uP8801S has a fast transient response that allows it Power dissipation in the device is calculated as:

to handle large load changes associated with high current PD = (VIN - VOUT) x IOUT + VCNTL x ICNTL

applications. Proper selection of the output capacitor and It is adequate to neglect power loss with respective to

its ESR value determines stable operation and optimizes control circuit VCNTL x ICNTL when considering thermal

performance. The typical application circuit shown in Figure management in uP8801S Take the following moderate

1 was tested with a wide range of different capacitors. The operation condition as an example: VIN = 3.3V, VOUT =

circuit was found to be unconditionally stable with capacitor 1.5V, IOUT = 1A, the power dissipation is:

values from 10uF to 1000uF and ESR ranging from 0.5mΩ

to greater then 75mΩ. PD = (3.3V- 1.5V) x 1A = 1.8W

This power dissipation is conducted through the package

5VCC into the ambient environment, and, in the process, the

R4 CNTL

temperature of the die (TJ) rises above ambient. Large power

10R

EN

4

POK

dissipation may cause considerable temperature raise in

2 1 the regulator in large dropout applications. The geometry

R3 of the package and of the printed circuit board (PCB) greatly

10K VOUT

VIN VIN VOUT

3 6

influences how quickly the heat is transferred to the PCB

R2 C4

and away from the chip. The most commonly used thermal

C1

1uF FB

12.5K option metrics for IC packages are thermal resistance from the

NC 5 7

R1 C3 chip junction to the ambient air surrounding the package

C2 100uF

22uF

9

GND

10K (θJA):

θJA = ( TJ -TA ) / PD

θJA specified in the Thermal Information section is measured

Figure 1. Typical Application Circuit in the natural convection at TA = 25OC on a high effective

thermal conductivity test board (4 Layers, 2S2P) of JEDEC

Input capacitor: A minimum of 4.7uF ceramic capacitor

51-7 thermal measurement standard. The case point of

is recommended to be placed directly next to the VIN pin.

θJC is on the exposed pad for PSOP-8L package.

uP8801S-DS-F0000, Dec. 2014 11

www.upi-semi.com

uP8801S

Application Information

Given power dissipation PD, ambient temperature and

thermal resistance θ JA, the junction temperature is

calculated as:

TJ = TA + ∆TJA = TA + PD x θJA 70mm 2

To limit the junction temperature within its maximum rating,

the allowable maximum power dissipation is calculated

as:

Figure 4. Copper Area of Thermal Pad = 70mm2 ,

PD(MAX) = ( TJ(MAX) -TA ) /θJA θJA = 45OC/W

where T J(MAX) is the maximum operation junction Figure 4 shows a 70mm2 copper on a standard JEDEC 51-

temperature 125OC, TA is the ambient temperature and the 5 (4 layers, 2S2P+Via) high effective thermal conductivity

θJA is the junction to ambient thermal resistance. θJA of test board. θJA of PSOP-8L package is 45OC/W. The

PSOP-8 packages is 75OC/W on JEDEC 51-7 (4 layers, maximum power dissipation depends on thermal shutdown

2S2P) thermal test board with minimum copper area. The temperature TJ(MAX) = 170OC and thermal resistance θJA =

maximum power dissipation at TA = 25OC can be calculated 45OC/W at TA = 25OC can be calculated as:

as:

PD(MAX) = (170OC - 25OC) / 45OC/W = 3.22W

PD(MAX) = (125OC - 25OC) / 75OC/W = 1.33W

However, it is highly recommended to keep the junction

The thermal resistance θJA highly depends on the PCB temperature below the recommended operation condition

design. Copper plane under the exposed pad is an effective 125OC for maximum reliability.

heatsink and is useful for improving thermal conductivity.

Figure 5 illustrates the recommended PCB layout for best

Figure 3 show the relationship between thermal resistance

thermal performance.

θJA vs. copper area on a standard JEDEC 51-7 (4 layers,

2S2P) thermal test board at TA = 25OC. A 50mm2 copper

VOUT

GND

plane reduces θJA from 75OC/W to 52OC/W and increases

NC

FB

maximum power dissipation from 1.33W to 1.9W.

8

7

3 GND 6

5

100

9

90

1

2

4

Thermal Resistance θJA (OC/W)

VIN

80

CNTL

POK

EN

70

Figure 5. Recommended PCB Layout.

60 Layout Consideration

1. Place a local bypass capacitor as closed as possible

50 to the VIN pin. Use short and wide traces to minimize

parasitic resistance and inductance.

40

2. The exposed pad should be soldered on GND plane

with maximum area and with multiple vias to inner layer

30

0 10 20 30 40 50 60 70 of ground place for improving thermal performance.

Copper Area (mm2)

3. Connect voltage divider directly to the point where

Figure 3. Thermal Resistance θJA vs. Copper Area regulation is required. Place voltage divider close to

the device.

12 uP8801S-DS-F0000, Dec. 2014

www.upi-semi.com

uP8801S

Package Information

PSOP-8L

0.10 - 0.25

4.80 - 5.00

2.60 - 3.40

5.79 - 6.20

3.80 - 4.00

1.90 - 2.55

0.40 - 1.27

1

1.27 BSC 0.31 - 0.51

1.70 MAX

0.00 - 0.15

Note

1.Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

2.Dimensions in Millimeters.

3.Drawing not to scale.

4.These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

uP8801S-DS-F0000, Dec. 2014 13

www.upi-semi.com

uP8801S

Package Information

WDFN3x3-10L

2.90 - 3.10 0.30 - 0.50 2.20 - 2.70

6 10

1.40 - 1.80

2.90 - 3.10

5 1

0.50 BSC 0.18 - 0.30

0.70 - 0.80

0.20 REF 0.00 - 0.05

Note

1.Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

2.Dimensions in Millimeters.

3.Drawing not to scale.

4.These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

14 uP8801S-DS-F0000, Dec. 2014

www.upi-semi.com

uP8801S

Important Notice

uPI and its subsidiaries reserve the right to make corrections, modifications, enhancements, improvements, and other

changes to its products and services at any time and to discontinue any product or service without notice. Customers

should obtain the latest relevant information before placing orders and should verify that such information is current and

complete.

uPI products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment.

However, no responsibility is assumed by uPI or its subsidiaries for its use or application of any product or circuit; nor

for any infringements of patents or other rights of third parties which may result from its use or application, including but

not limited to any consequential or incidental damages. No uPI components are designed, intended or authorized for

use in military, aerospace, automotive applications nor in systems for surgical implantation or life-sustaining. No license

is granted by implication or otherwise under any patent or patent rights of uPI or its subsidiaries.

COPYRIGHT (C) 2014, UPI SEMICONDUCTOR CORP.

uPI Semiconductor Corp. uPI Semiconductor Corp.

Headquarter Sales Branch Office

9F.,No.5, Taiyuan 1st St. Zhubei City, 12F-5, No. 408, Ruiguang Rd. Neihu District,

Hsinchu Taiwan, R.O.C. Taipei Taiwan, R.O.C.

TEL : 886.3.560.1666 FAX : 886.3.560.1888 TEL : 886.2.8751.2062 FAX : 886.2.8751.5064

uP8801S-DS-F0000, Dec. 2014 15

www.upi-semi.com

You might also like

- First-Order System: Transient Response of A Thermocouple To A Step Temperature ChangeDocument3 pagesFirst-Order System: Transient Response of A Thermocouple To A Step Temperature ChangeAnand RajNo ratings yet

- uPI Confidential: 3A Ultra Low Dropout Linear RegulatorDocument13 pagesuPI Confidential: 3A Ultra Low Dropout Linear RegulatorLEONNo ratings yet

- 3A Ultra Low Dropout Linear Regulator: General Description FeaturesDocument11 pages3A Ultra Low Dropout Linear Regulator: General Description FeaturesdejanNo ratings yet

- Up 7704Document13 pagesUp 7704Delwar HossainNo ratings yet

- 1707S uPISemiconductorDocument13 pages1707S uPISemiconductordulah kemprohNo ratings yet

- 1Mhz, 2.0A, High-Efficiency Synchronous-Rectified Buck ConverterDocument16 pages1Mhz, 2.0A, High-Efficiency Synchronous-Rectified Buck ConverterFuNn FFNo ratings yet

- uPI Semiconductor Up1735 Synchronous-Rectified Buck Converter DatasheetDocument13 pagesuPI Semiconductor Up1735 Synchronous-Rectified Buck Converter DatasheetSultan SinghNo ratings yet

- 5V/12V Synchronous Buck PWM DC-DC Controller: Features General DescriptionDocument17 pages5V/12V Synchronous Buck PWM DC-DC Controller: Features General DescriptionLuis Dark-passengerNo ratings yet

- 3A, 1Mhz, Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 1Mhz, Synchronous Step-Down Converter: General Description FeatureskiryanoffNo ratings yet

- Synchronous-Rectified Buck MOSFET Drivers: Features General DescriptionDocument5 pagesSynchronous-Rectified Buck MOSFET Drivers: Features General DescriptionTeles SilvaNo ratings yet

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesAbdul MuhidNo ratings yet

- 8T Rt5768aDocument12 pages8T Rt5768aVISHALNo ratings yet

- FR9886Document12 pagesFR9886abrkNo ratings yet

- FR9888 FR9886 RT8296A RT8282 Step Down DC DC Converter Buck Ic Nguon Gan Giong Act 4523 PDFDocument11 pagesFR9888 FR9886 RT8296A RT8282 Step Down DC DC Converter Buck Ic Nguon Gan Giong Act 4523 PDFdinh vinh nguyenNo ratings yet

- Up1605 uPISemiconductorDocument23 pagesUp1605 uPISemiconductorRBN HMNo ratings yet

- UP1962SDocument14 pagesUP1962Stechgamebr85No ratings yet

- 500ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatorDocument13 pages500ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatorRenato HernandezNo ratings yet

- Synchronous-Rectified Buck MOSFET Drivers: General Description FeaturesDocument11 pagesSynchronous-Rectified Buck MOSFET Drivers: General Description FeaturesDaniel Norberto DemariaNo ratings yet

- 2A, 23V, 1.2Mhz Synchronous Step-Down Converter: General Description FeaturesDocument14 pages2A, 23V, 1.2Mhz Synchronous Step-Down Converter: General Description FeaturesHaroldo VieiraNo ratings yet

- 500ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatorDocument13 pages500ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatoreugeneNo ratings yet

- 300ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatorDocument11 pages300ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatordinhdtdNo ratings yet

- Complete DDR3/ DDR4 Memory Power Solution Controller: General Description FeaturesDocument15 pagesComplete DDR3/ DDR4 Memory Power Solution Controller: General Description FeaturesIgor LabutinNo ratings yet

- APL5932A/B/C/D: Features General DescriptionDocument21 pagesAPL5932A/B/C/D: Features General DescriptionAku KudupiknikNo ratings yet

- RT8015 2A 2MHz Synchronous Step-Down RegulatorDocument15 pagesRT8015 2A 2MHz Synchronous Step-Down RegulatorPedrolaura BethencourtNo ratings yet

- 5V/12V Synchronous Buck PWM DC-DC and Linear Power ControllerDocument18 pages5V/12V Synchronous Buck PWM DC-DC and Linear Power Controllerraed hasaniaNo ratings yet

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesJuan Carlos SrafanNo ratings yet

- RT8290: 3A, 23V, 340kHz Synchronous Step-Down ConverterDocument12 pagesRT8290: 3A, 23V, 340kHz Synchronous Step-Down ConverterMarcius RodriguesNo ratings yet

- AOZ2023PIDocument11 pagesAOZ2023PIjuliocunachiNo ratings yet

- 3A, 2Mhz, Synchronous Step-Down Converter: General Description FeaturesDocument13 pages3A, 2Mhz, Synchronous Step-Down Converter: General Description FeaturesKavinda Jayasinghege DonNo ratings yet

- 500mA Peak, Thermal Folded Back CMOS LDO RegulatorDocument12 pages500mA Peak, Thermal Folded Back CMOS LDO RegulatorpeternewsNo ratings yet

- 6A, 23V Synchronous Step-Down Converter With 3.3V/5V LDO: RT6256B/CDocument20 pages6A, 23V Synchronous Step-Down Converter With 3.3V/5V LDO: RT6256B/CkiryanoffNo ratings yet

- 2A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument14 pages2A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesGioVoTamNo ratings yet

- Ic rt9214Document17 pagesIc rt9214Franklin JimenezNo ratings yet

- RT8296A RichtekDocument14 pagesRT8296A Richtektecnicown eletricaNo ratings yet

- RT8204-DS8204-06 Single Synchronous Buck With LDO ControllerDocument19 pagesRT8204-DS8204-06 Single Synchronous Buck With LDO ControllerMaks ProstNo ratings yet

- 1.2Mhz, 3.0A, High-Efficiency Synchronous-Rectified Buck ConverterDocument12 pages1.2Mhz, 3.0A, High-Efficiency Synchronous-Rectified Buck ConverterKrasimir MalamovNo ratings yet

- RT9011Document12 pagesRT9011Bijan AmiriNo ratings yet

- Ds8204a 05Document19 pagesDs8204a 05marcelo Chiu LeonNo ratings yet

- RT8068AZQWDocument13 pagesRT8068AZQWTaller 62No ratings yet

- RT8057Document11 pagesRT8057antonio carlos clementino cruzNo ratings yet

- Tps 61197Document22 pagesTps 61197Sahaly RandNo ratings yet

- Ds8295a 04Document14 pagesDs8295a 04Bsm GwapuNo ratings yet

- uP6103 Synchronous Buck Controller Datasheet SummaryDocument15 pagesuP6103 Synchronous Buck Controller Datasheet SummarySelmar CavalcantiNo ratings yet

- 5A, 36V, 500Khz Step-Down Converter: General Description FeaturesDocument14 pages5A, 36V, 500Khz Step-Down Converter: General Description FeaturesHitesh GambhavaNo ratings yet

- Datasheet - HK lp6253 8406861Document11 pagesDatasheet - HK lp6253 8406861Boban CvetkovicNo ratings yet

- Advanced Voltage Mode Pulse Width Modulator: Description FeaturesDocument24 pagesAdvanced Voltage Mode Pulse Width Modulator: Description Featuresvanhuong87No ratings yet

- rt913a_richtekDocument11 pagesrt913a_richtekRagavan RagavanNo ratings yet

- DS8510 07Document12 pagesDS8510 07CALINo ratings yet

- 300mA Dual LDO Regulator with PORDocument12 pages300mA Dual LDO Regulator with PORTitán SotoNo ratings yet

- Apl5930 PDFDocument20 pagesApl5930 PDFanthony loboNo ratings yet

- Slusck3 PDFDocument40 pagesSlusck3 PDFGlauco Borges BrumNo ratings yet

- Synchronous-Rectified Buck MOSFET Drivers: General Description FeaturesDocument12 pagesSynchronous-Rectified Buck MOSFET Drivers: General Description FeaturesFlavianoSilvaNo ratings yet

- Single-Channel Power Distribution Switch: Description FeaturesDocument16 pagesSingle-Channel Power Distribution Switch: Description FeaturessandrolafaieteNo ratings yet

- DATASHEET Up1542rDocument17 pagesDATASHEET Up1542rjoao doisssNo ratings yet

- Rt9008ge Apl5611aci-Trg Apl5611 9008ge 9008 La04 La12 La13 La14 La15 La16 La17 La0 La1Document9 pagesRt9008ge Apl5611aci-Trg Apl5611 9008ge 9008 La04 La12 La13 La14 La15 La16 La17 La0 La1laptophaianhNo ratings yet

- FAN7380 Half-Bridge Gate Driver: Features DescriptionDocument12 pagesFAN7380 Half-Bridge Gate Driver: Features Descriptionflo72afNo ratings yet

- DatasheetDocument12 pagesDatasheetWAN MOZESNo ratings yet

- DS9030 05Document10 pagesDS9030 05Jois LanzaNo ratings yet

- Datasheet 4Document2 pagesDatasheet 4zakie wahyuNo ratings yet

- Datasheet 3Document34 pagesDatasheet 3zakie wahyuNo ratings yet

- APL5932A/B/C/D: Features General DescriptionDocument21 pagesAPL5932A/B/C/D: Features General DescriptionAku KudupiknikNo ratings yet

- 9960GM SiliconStandardDocument6 pages9960GM SiliconStandardzakie wahyuNo ratings yet

- 60V P-Channel MOSFET Product SummaryDocument5 pages60V P-Channel MOSFET Product Summarydario defazyNo ratings yet

- AO4484Document4 pagesAO4484waluyo128No ratings yet

- OMN Tapes Labels Release Coatings PSDocument2 pagesOMN Tapes Labels Release Coatings PSdhruvrakeshNo ratings yet

- Laminar Flow Table: Name: Animesh Phatowali Roll No: 17AE30005 Group: 6 Experiment:7Document7 pagesLaminar Flow Table: Name: Animesh Phatowali Roll No: 17AE30005 Group: 6 Experiment:7Animesh PhatowaliNo ratings yet

- SupportsDocument6 pagesSupportsDana GuerreroNo ratings yet

- Simulation of Thermoplastic Prepreg Thermoforming Based On A Viscohyperelastic Model and A Thermal HomogenizationDocument38 pagesSimulation of Thermoplastic Prepreg Thermoforming Based On A Viscohyperelastic Model and A Thermal Homogenizationddumas83No ratings yet

- Body Electrical Diagnosis: Quick Training Guide - QT611ADocument10 pagesBody Electrical Diagnosis: Quick Training Guide - QT611AThang TongNo ratings yet

- Base Plate Design CapacitiesDocument4 pagesBase Plate Design CapacitiesSrishti Project Consultants0% (1)

- MATS2001 Physical Properties of Materials: Some Preliminary Aspects of Quantum PhysicsDocument7 pagesMATS2001 Physical Properties of Materials: Some Preliminary Aspects of Quantum PhysicsMeekey KhantNo ratings yet

- Fundamentals of Multiferroic MaterialsDocument39 pagesFundamentals of Multiferroic Materialsdapper otaku662No ratings yet

- Preventing and Correcting Rutting in Asphalt PavementsDocument5 pagesPreventing and Correcting Rutting in Asphalt PavementsJean Claude EidNo ratings yet

- Concept: Understanding SingularitiesDocument2 pagesConcept: Understanding SingularitiesPraveen SreedharanNo ratings yet

- Combined Footing NUNNA Bldg. R0Document6 pagesCombined Footing NUNNA Bldg. R0prabhat_iitdNo ratings yet

- Piezo Ceramic TutorialsDocument51 pagesPiezo Ceramic TutorialsCarlos BustamanteNo ratings yet

- Jee 2014 Booklet7 HWT Magnetism & MatterDocument12 pagesJee 2014 Booklet7 HWT Magnetism & MattervarunkohliinNo ratings yet

- Torsional Shear StrengthDocument7 pagesTorsional Shear Strengthkc olidan0% (1)

- Photo Electric Effect by Dr. BCS TewariDocument22 pagesPhoto Electric Effect by Dr. BCS TewariAdity ANo ratings yet

- Process Line Sizing Task and Solution PDFDocument4 pagesProcess Line Sizing Task and Solution PDFKamalNo ratings yet

- Behaviour of Geopolymer Concrete Under Static and Cyclic LoadDocument11 pagesBehaviour of Geopolymer Concrete Under Static and Cyclic LoadAsif Hameed100% (1)

- Design Base Plate For I Beam - Bottom BracketDocument1 pageDesign Base Plate For I Beam - Bottom BracketCon CanNo ratings yet

- Experimental and Numerical Investigations on the Behaviour of Geosynthetic Encased Stone ColumnsDocument5 pagesExperimental and Numerical Investigations on the Behaviour of Geosynthetic Encased Stone ColumnsSajid Iqbal100% (1)

- Smirnov 2017 IOP Conf. Ser. Mater. Sci. Eng. 177 012130Document8 pagesSmirnov 2017 IOP Conf. Ser. Mater. Sci. Eng. 177 012130senthilNo ratings yet

- DAL ChromisingDocument3 pagesDAL ChromisingJais JohnNo ratings yet

- ConversionesDocument6 pagesConversionesjose juan ramirezNo ratings yet

- Reinforced Concrete Design FlowchartsDocument29 pagesReinforced Concrete Design FlowchartsRomulo TindoyNo ratings yet

- Boiler Tube FailuresDocument15 pagesBoiler Tube FailuresBIRANCHINo ratings yet

- Heat TreatmentDocument33 pagesHeat TreatmentColeNo ratings yet

- Poroelastic Backus Averaging For Anisotropic Layered Fluid-And Gas-Saturated SedimentsDocument12 pagesPoroelastic Backus Averaging For Anisotropic Layered Fluid-And Gas-Saturated SedimentsImam GazaliNo ratings yet

- Structural Design: Module inDocument11 pagesStructural Design: Module inkangkongNo ratings yet

- 47-Manuscript (манускрипт) -53-1-10-20180705Document13 pages47-Manuscript (манускрипт) -53-1-10-20180705Dr. Anoop A.D.No ratings yet

- SBBSBDocument130 pagesSBBSBRam KumarNo ratings yet